Dynamic Single-Electron Transistor Modeling for High-Frequency Capacitance Characterization

Abstract

:Featured Application

Abstract

1. Introduction

2. Method of Modeling

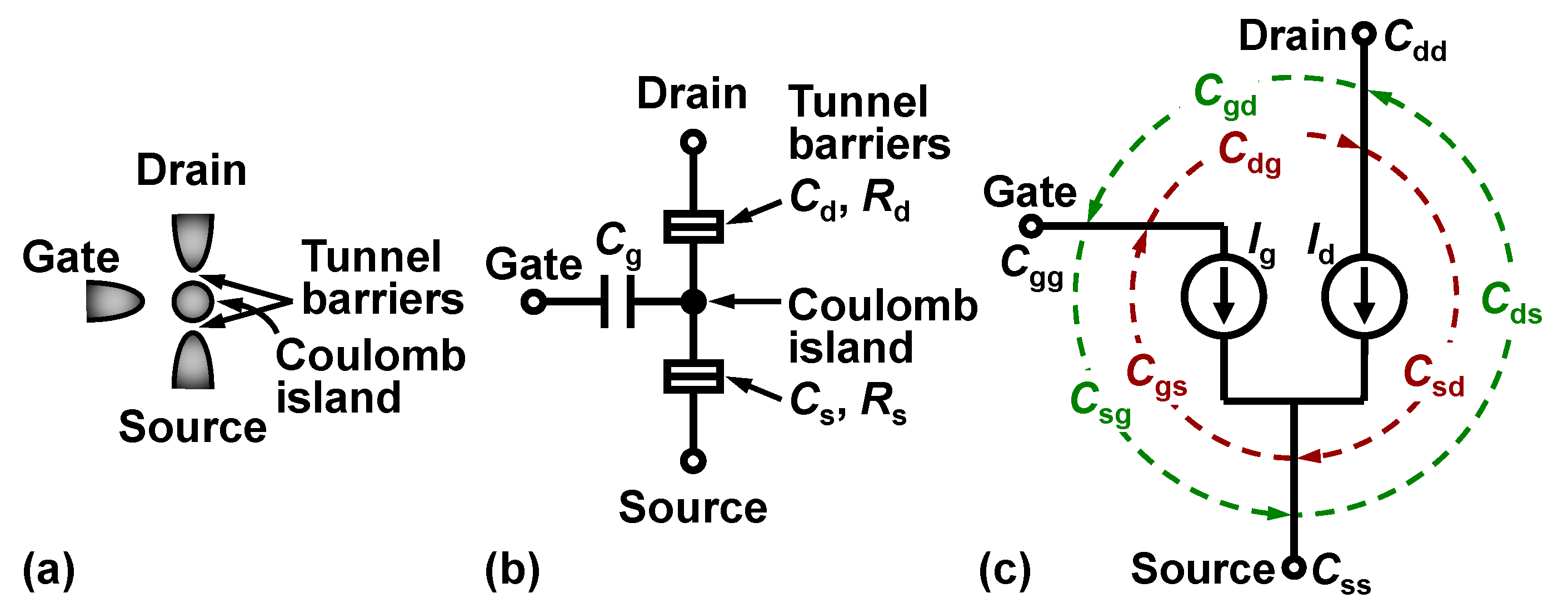

2.1. Proposed Model

2.2. Accuracy of the Model

2.3. Extraction of Capacitance Components

3. Simulation Results

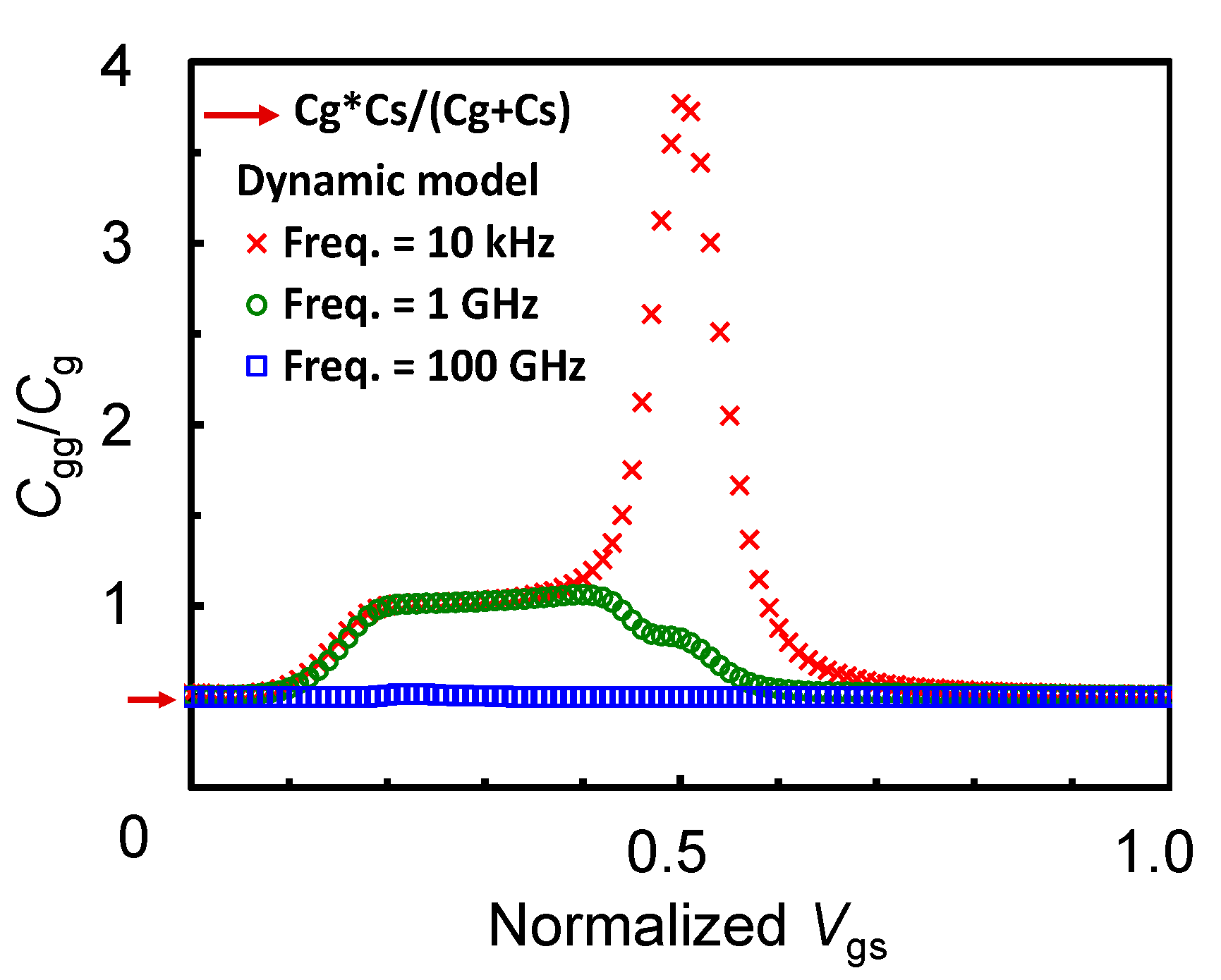

3.1. Gate Bias Dependence of Capacitances

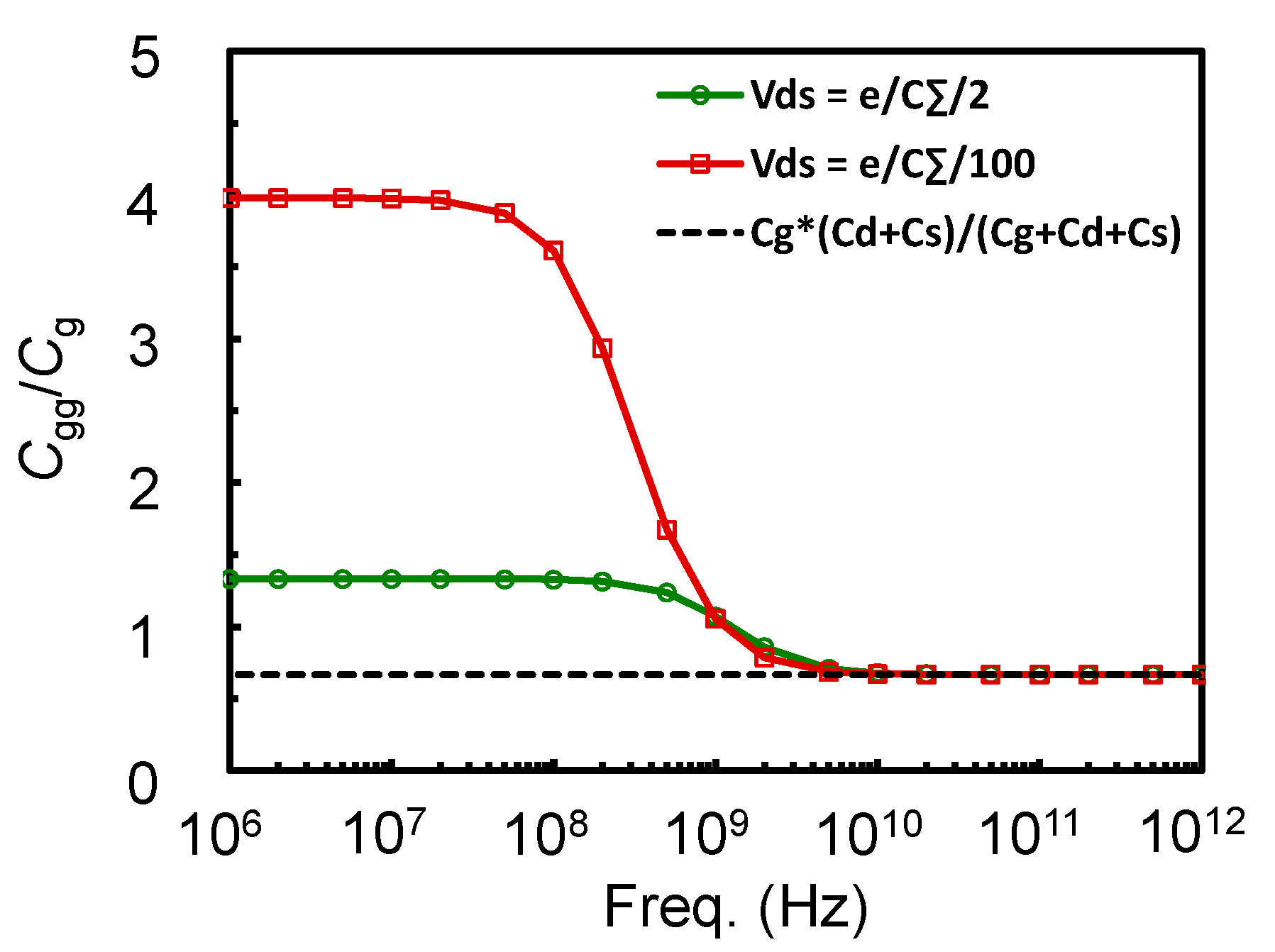

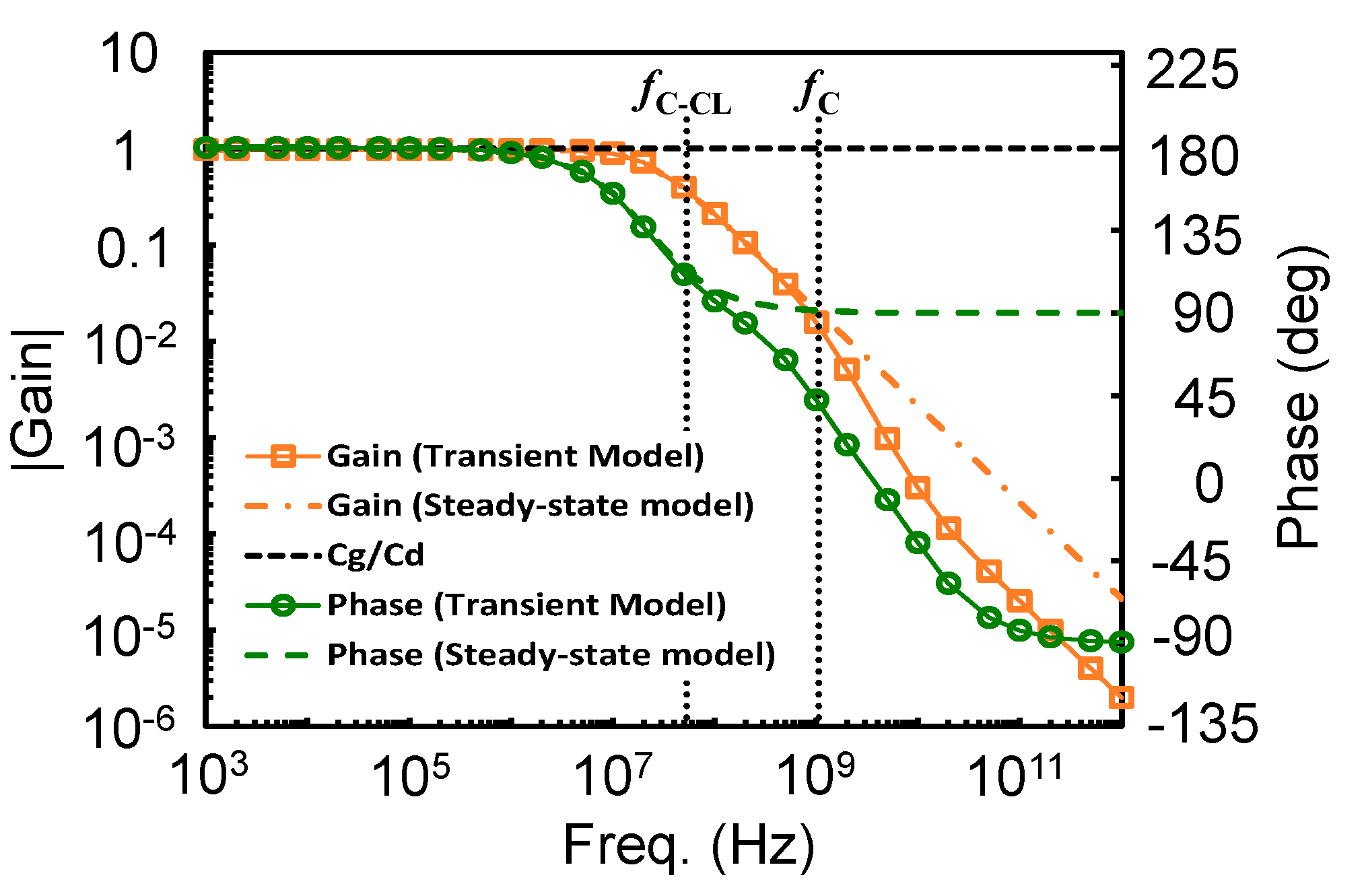

3.2. Frequency Dependence of Capacitances

3.3. Temperature Dependence of Capacitances

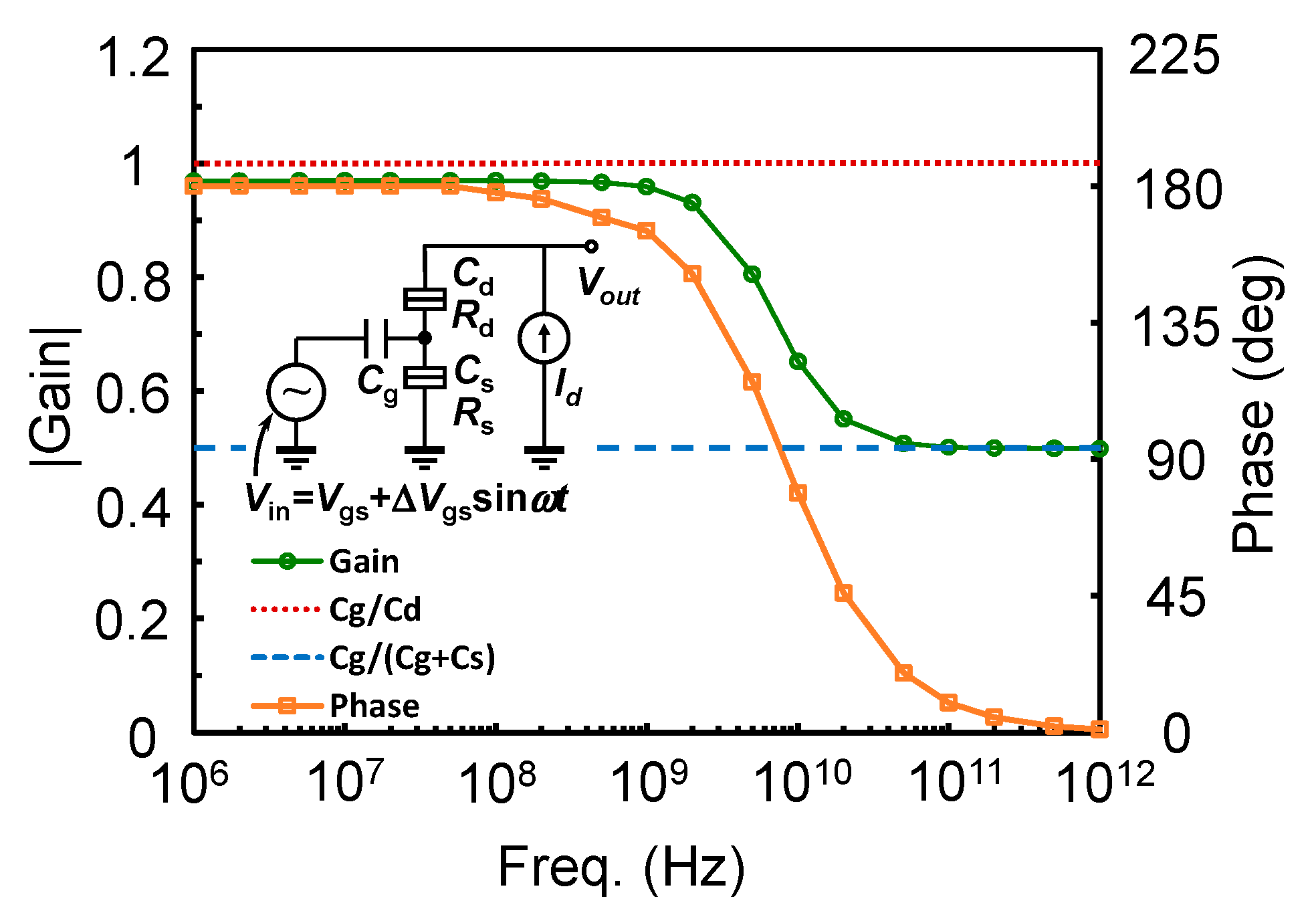

3.4. Characteristics of the SET-Based Amplifier

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Kano, S.; Azuma, Y.; Kanehara, M.; Teranishi, T.; Majima, Y. Room-Temperature Coulomb Blockade from Chemically Synthesized Au Nanoparticles Stabilized by Acid–Base Interaction. Appl. Phys. Exp. 2010, 3, 105003. [Google Scholar] [CrossRef]

- Suzuki, R.; Nozue, M.; Saraya, T.; Hiramoto, T. Experimental Observation of Quantum Confinement Effect in <110> and <100> Silicon Nanowire Field-Effect Transistors and Single-Electron/Hole Transistors Operating at Room Temperature. Jpn. J. Appl. Phys. 2013, 52, 104001. [Google Scholar] [CrossRef]

- Nakajima, A. Application of Single-Electron Transistor to Biomolecule and Ion Sensors. Appl. Sci. 2016, 6, 94. [Google Scholar] [CrossRef]

- Tucker, J.R. Complementary digital logic based on the “Coulomb blockade”. J. Appl. Phys. 1992, 72, 4399–4413. [Google Scholar] [CrossRef]

- Mooij, J.E. Single Electrons: Status and Prospects. In Proceedings of the 1993 International Conference on Solid State Devices and Materials, Chiba, Japan, 29 August–1 September 1993; pp. 339–340. [Google Scholar] [CrossRef]

- Razavi, B. Design of Analog CMOS Integrated Circuits; McGraw-Hill: New York, NY, USA, 2001; pp. 166–169. [Google Scholar]

- Colless, J.I.; Mahoney, A.C.; Hornibrook, J.M.; Doherty, A.C.; Lu, H.; Gossard, A.C.; Reilly, D.J. Dispersive Readout of a Few-Electron Double Quantum Dot with Fast rf Gate Sensors. Phys. Rev. Lett. 2013, 110, 046805. [Google Scholar] [CrossRef] [PubMed]

- Gonzalez-Zalba, M.F.; Barraud, S.; Ferguson, A.J.; Betz, A.C. Probing the limits of gate-based charge sensing. Nat. Commun. 2015, 6, 6084. [Google Scholar] [CrossRef]

- Ahmed, I.; Haigh, J.A.; Schaal, S.; Barraud, S.; Zhu, Y.; Lee, C.-M.; Amado, M.; Robinson, J.W.A.; Rossi, A.; Morton, J.J.L.; et al. Radio-Frequency Capacitive Gate-Based Sensing. Phys. Rev. Appl. 2018, 10, 014018. [Google Scholar] [CrossRef]

- Schaal, S.; Rossi, A.; Ciriano-Tejel, V.N.; Yang, T.-Y.; Barraud, S.; Morton, J.J.L.; Gonzalez-Zalba, M.F. A CMOS dynamic random access architecture for radio-frequency readout of quantum devices. Nat. Electron. 2019, 2, 236–242. [Google Scholar] [CrossRef]

- Fujishima, M.; Amakawa, S.; Hoh, K. Circuit Simulators Aiming at Single-Electron Integration. Jpn. J. Appl. Phys. 1998, 37, 1478–1482. [Google Scholar] [CrossRef]

- Uchida, K.; Matsuzawa, K.; Koga, J.; Ohba, R.; Takagi, S.-I.; Toriumi, A. Analytical Single-Electron Transistor (SET) Model for Design and Analysis of Realistic SET Circuits. Jpn. J. Appl. Phys. 2000, 39, 2321–2324. [Google Scholar] [CrossRef]

- Inokawa, H.; Takahashi, Y. A compact analytical model for asymmetric single-electron tunneling transistors. IEEE Trans. Electron Devices 2003, 50, 455–461, Erratum in IEEE Trans. Electron Devices 2003, 50, 862–862. . [Google Scholar] [CrossRef]

- Mahapatra, S.; Vaish, V.; Wasshuber, C.; Banerjee, K.; Ionescu, A. Analytical modeling of single electron transistor for hybrid CMOS-SET analog IC design. IEEE Trans. Electron Devices 2004, 51, 1772–1782. [Google Scholar] [CrossRef]

- Miyaji, K.; Saitoh, M.; Hiramoto, T. Compact analytical model for room-temperature-operating silicon single-electron transistors with discrete quantum energy levels. IEEE Trans. Nanotechnol. 2006, 5, 167–173. [Google Scholar] [CrossRef]

- Pruvost, B.; Mizuta, H.; Oda, S. Voltage-limitation-free analytical single-electron transistor model incorporating the effects of spin-degenerate discrete energy states. J. Appl. Phys. 2008, 103, 054508. [Google Scholar] [CrossRef]

- Klupfel, F.J. A Compact Model Based on Bardeen’s Transfer Hamiltonian Formalism for Silicon Single Electron Transistors. IEEE Access 2019, 7, 84053–84065. [Google Scholar] [CrossRef]

- dos Santos Pês, B.; Oroski, E.; Guimarães, J.G.; Bonfim, M.J. A Hammerstein–Wiener Model for Single-Electron Transistors. IEEE Trans. Electron Devices 2018, 66, 1092–1099. [Google Scholar] [CrossRef]

- Yu, Y.S.; Lee, H.S.; Hwang, S.W. MacroModeling of single electron transistors for efficient circuit simulation. IEEE Trans. Electron Devices 1999, 46, 1667–1671. [Google Scholar]

- Korotkov, N.; Chen, R.H.; Likharev, K. Possible Performance of Capacitively Coupled Single-Electron Transistors in Digital Circuits. J. Appl. Phys. 1995, 78, 2520–2530. [Google Scholar] [CrossRef]

- Chen, R.H.; Korotkov, A.N.; Likharev, K.K. Single-electron transistor logic. Appl. Phys. Lett. 1996, 68, 1954–1956. [Google Scholar] [CrossRef]

- Wasshuber, C.; Kosina, H.; Selberherr, S. SIMON-A simulator for single-electron tunnel devices and circuits. IEEE Trans. Comput. Des. Integr. Circuits Syst. 1997, 16, 937–944. [Google Scholar] [CrossRef]

- Zimmerman, N.M.; Keller, M.W. Dynamic input capacitance of single-electron transistors and the effect on charge-sensitive electrometers. J. Appl. Phys. 2000, 87, 8570–8574. [Google Scholar] [CrossRef]

- Fonseca, L.R.C.; Korotkov, A.N.; Likharev, K.K.; Odintsov, A.A. A numerical study of the dynamics and statistics of single electron systems. J. Appl. Phys. 1995, 78, 3238–3251. [Google Scholar] [CrossRef]

- Kirihara, M.; Nakazato, K.; Wagner, M. Hybrid Circuit Simulator Including a Model for Single Electron Tunneling Devices. Jpn. J. Appl. Phys. 1999, 38, 2028–2032. [Google Scholar] [CrossRef]

- Nagel, L.W. SPICE2: A Computer Program to Simulate Semiconductor Circuits. Ph.D. Dissertation, University of California, Berkeley, CA, USA, 9 May 1975. Available online: http://www2.eecs.berkeley.edu/Pubs/TechRpts/1975/ERL-m-520.pdf (accessed on 16 December 2021).

- LTspice IV Version 4.231. Analog Devices, Inc. 2016. Available online: https://www.analog.com/en/design-center/design-tools-and-calculators/ltspice-simulator.html (accessed on 8 April 2022).

- Amat, E.; Bausells, J.; Parez-Murano, F. Exploring the Influence of Variability on Single-Electron Transistos into SET-Based Circuits. IEEE Trans. Electron Devices 2017, 64, 5172–5180. [Google Scholar] [CrossRef]

- Ingold, G.L.; Nazarov, Y.V. Charge Tunneling Rates in Ultrasmall Junctions. In NATO ASI Series B, Single Charge Tunneling; Grabert, H., Devoret, M.H., Eds.; Springer: Boston, MA, USA, 1992; Volume 294, pp. 77–80. [Google Scholar]

- Stewart, M.; Zimmerman, N. Stability of Single Electron Devices: Charge Offset Drift. Appl. Sci. 2016, 6, 187. [Google Scholar] [CrossRef]

- Yamamura, K.; Kuroki, W.; Okuma, H.; Inoue, Y. Path Following Circuit--SPICE-Oriented Numerical Methods Where Formulas are Described by Circuits. IEICE Trans. Fundam. Electron. Commun. Comput. Sci. 2005, E88-A, 825–831. [Google Scholar] [CrossRef]

- Du, S.; Yoshida, K.; Zhang, Y.; Hamada, I.; Hirakawa, K. Terahertz dynamics of electron–vibron coupling in single molecules with tunable electrostatic potential. Nat. Photon. 2018, 12, 608–612. [Google Scholar] [CrossRef]

|

Gate, drain and source capacitances CgCd = Cs | 1 aF |

|

Tunneling resistances RdRs = Rt | 25 MΩ |

|

Cutoff frequency fc | 1 GHz |

|

Gate—source voltage

Vgs | 0~162 mV [0~1] |

|

Drain—source voltage

Vds | 0.534 mV [0.01], 26.7 mV [0.5] |

|

Temperature

T | 15.5 K [0.05] except for Figure 6. |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Singh, A.; Nishimura, T.; Satoh, H.; Inokawa, H. Dynamic Single-Electron Transistor Modeling for High-Frequency Capacitance Characterization. Appl. Sci. 2022, 12, 8139. https://doi.org/10.3390/app12168139

Singh A, Nishimura T, Satoh H, Inokawa H. Dynamic Single-Electron Transistor Modeling for High-Frequency Capacitance Characterization. Applied Sciences. 2022; 12(16):8139. https://doi.org/10.3390/app12168139

Chicago/Turabian StyleSingh, Alka, Tomoki Nishimura, Hiroaki Satoh, and Hiroshi Inokawa. 2022. "Dynamic Single-Electron Transistor Modeling for High-Frequency Capacitance Characterization" Applied Sciences 12, no. 16: 8139. https://doi.org/10.3390/app12168139

APA StyleSingh, A., Nishimura, T., Satoh, H., & Inokawa, H. (2022). Dynamic Single-Electron Transistor Modeling for High-Frequency Capacitance Characterization. Applied Sciences, 12(16), 8139. https://doi.org/10.3390/app12168139