Energy-Efficient Amplifiers Based on Quasi-Floating Gate Techniques

Abstract

1. Introduction

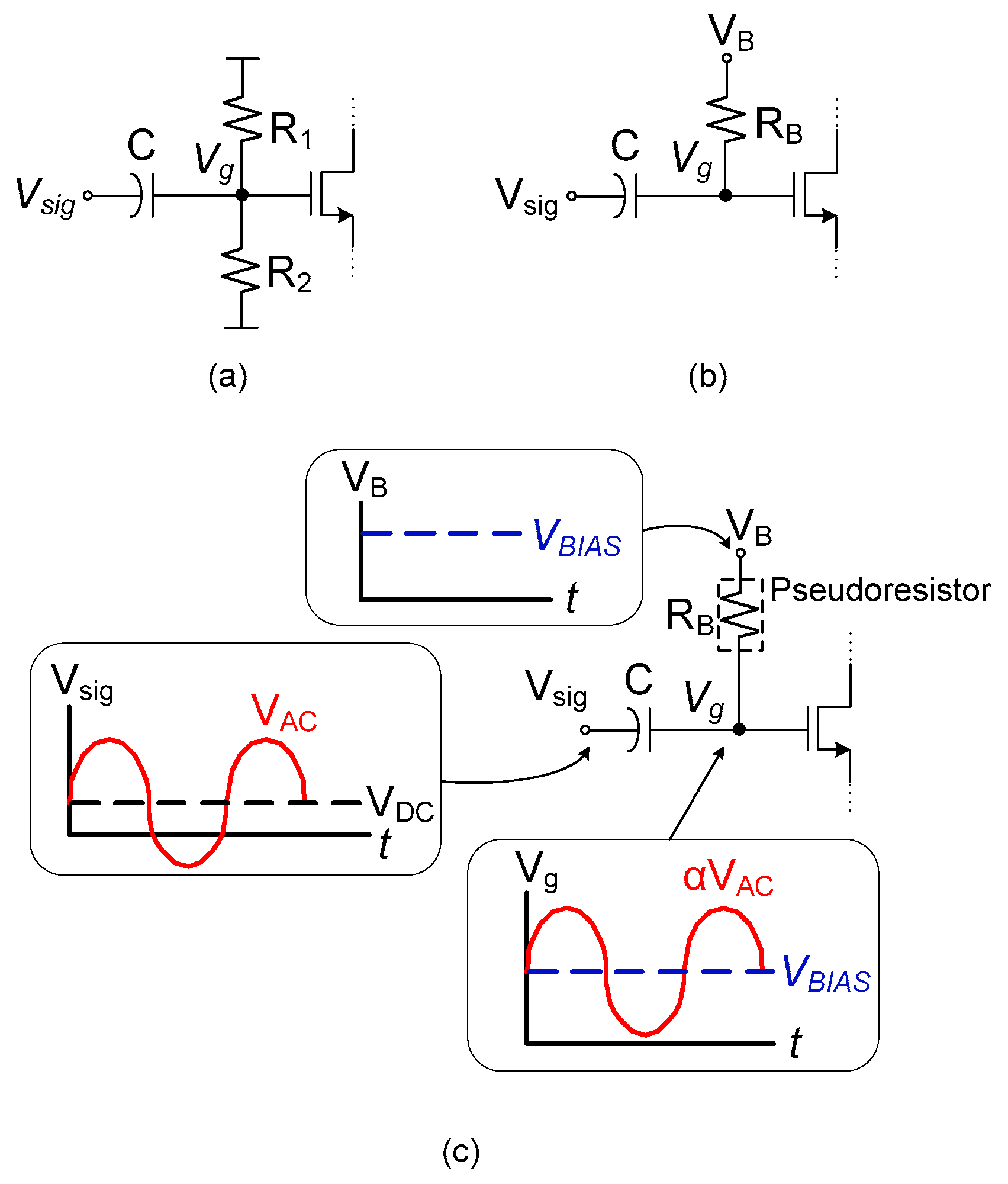

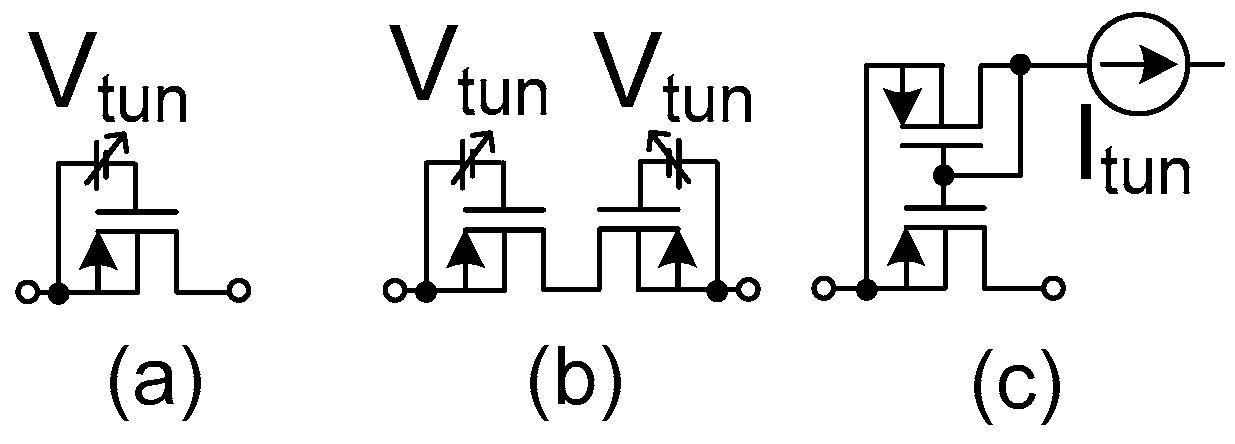

2. Quasi-Floating Gate Transistors

2.1. Wideband Capacitive Coupling Using Quasi-Floating Gate Transistors

2.2. Application of QFG Transistors to Energy-Efficient Amplifier Design

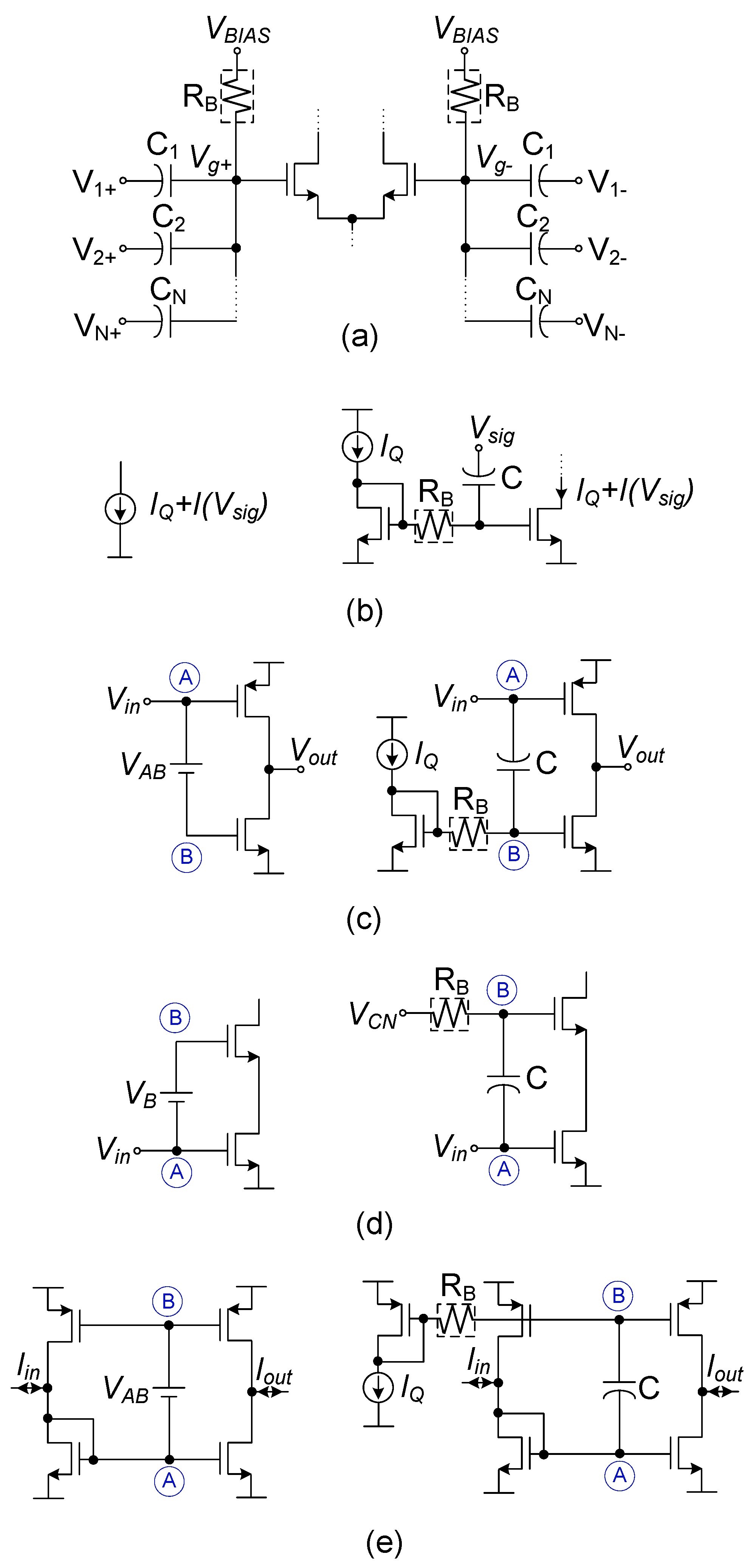

2.2.1. QFG Input Differential Pair

2.2.2. Adaptive Bias Current Source

2.2.3. Class AB Output Stage

2.2.4. Dynamic Cascode Biasing

2.2.5. Class AB Current Mirrors

3. Energy-Efficient Amplifiers Based on QFG Techniques

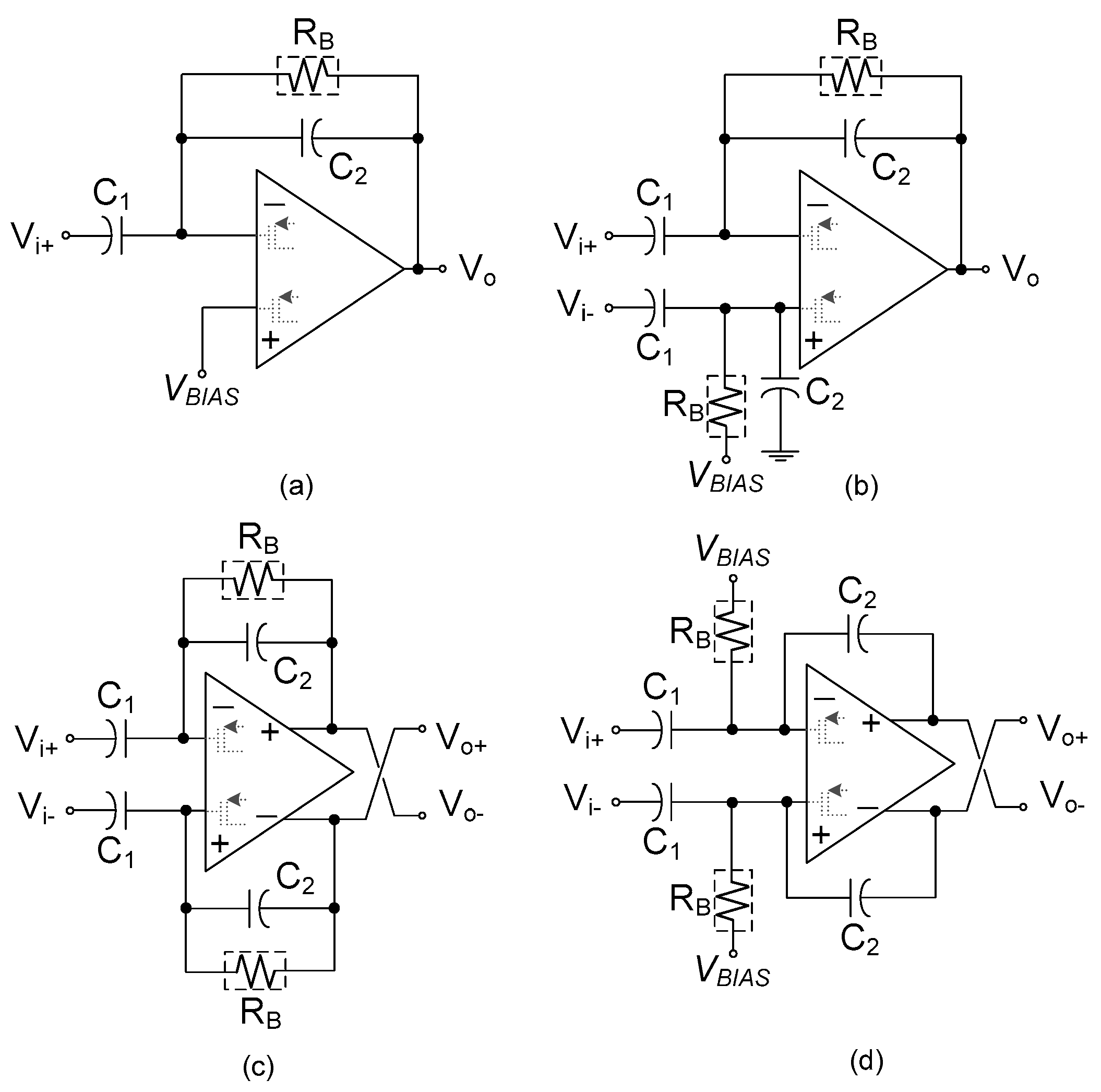

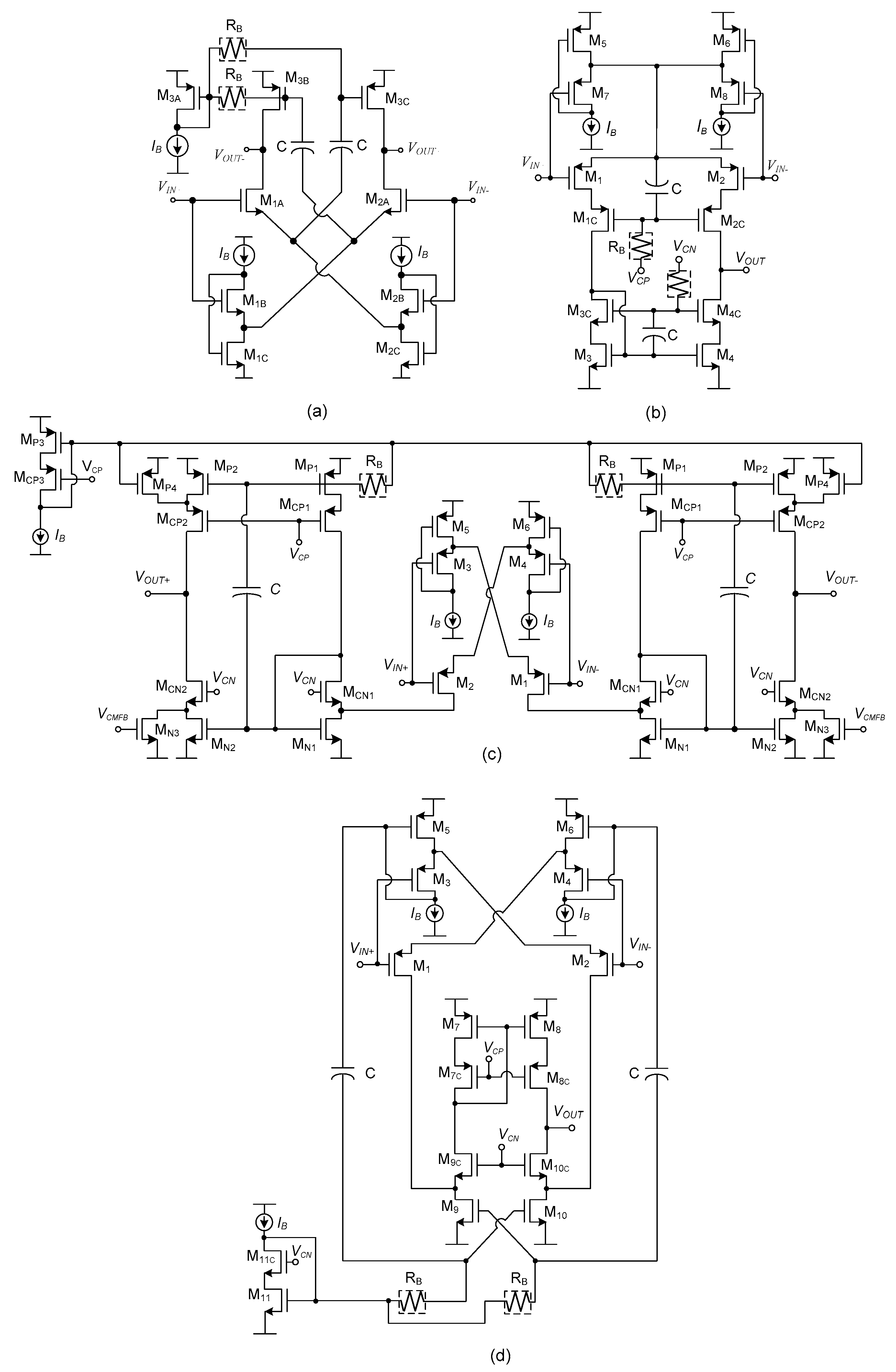

3.1. AC-Coupled Amplifiers

3.2. Single-Stage Class AB Amplifiers

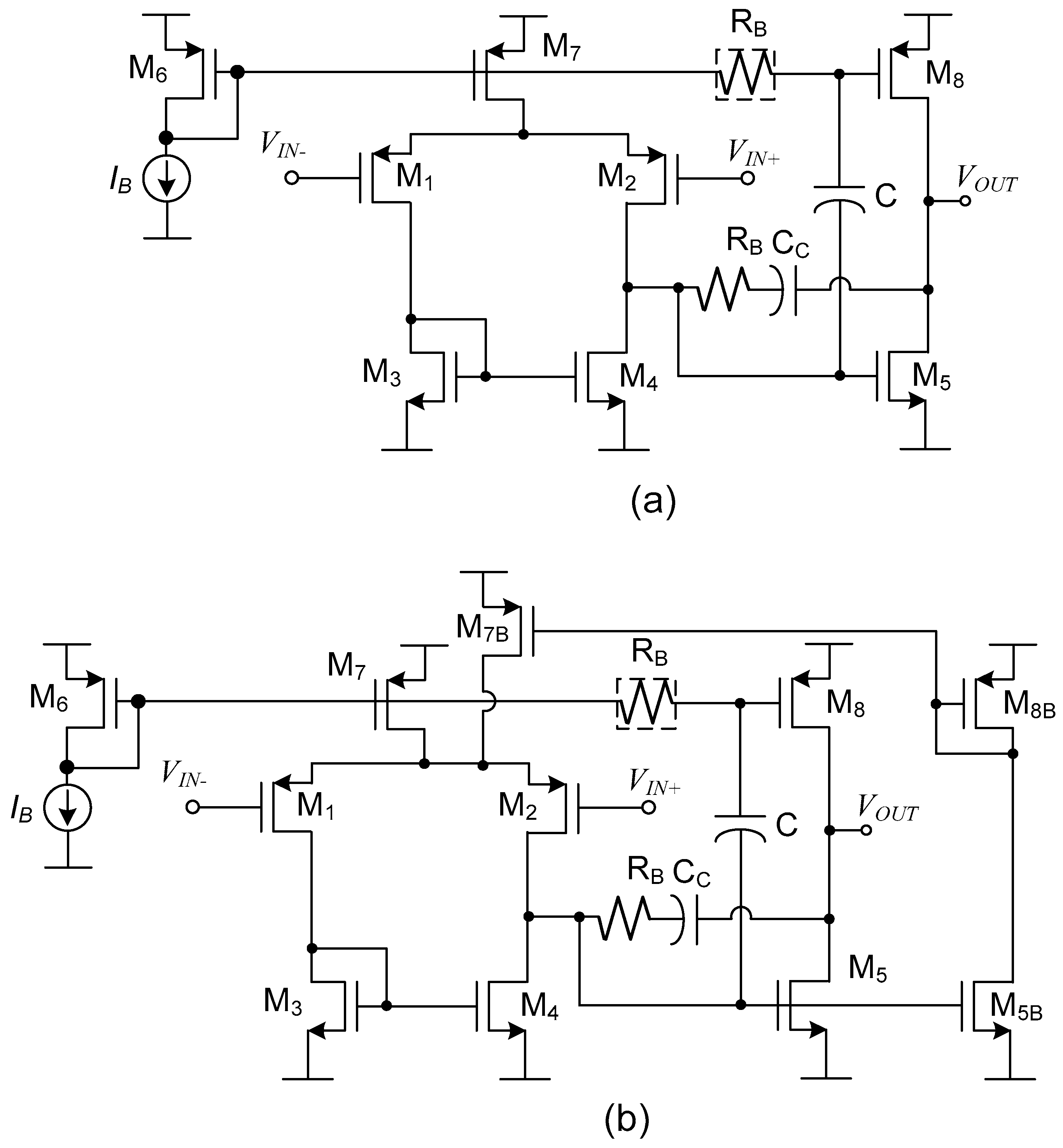

3.3. Multistage Class A/AB Amplifiers

3.4. Multistage Class AB/AB Amplifiers

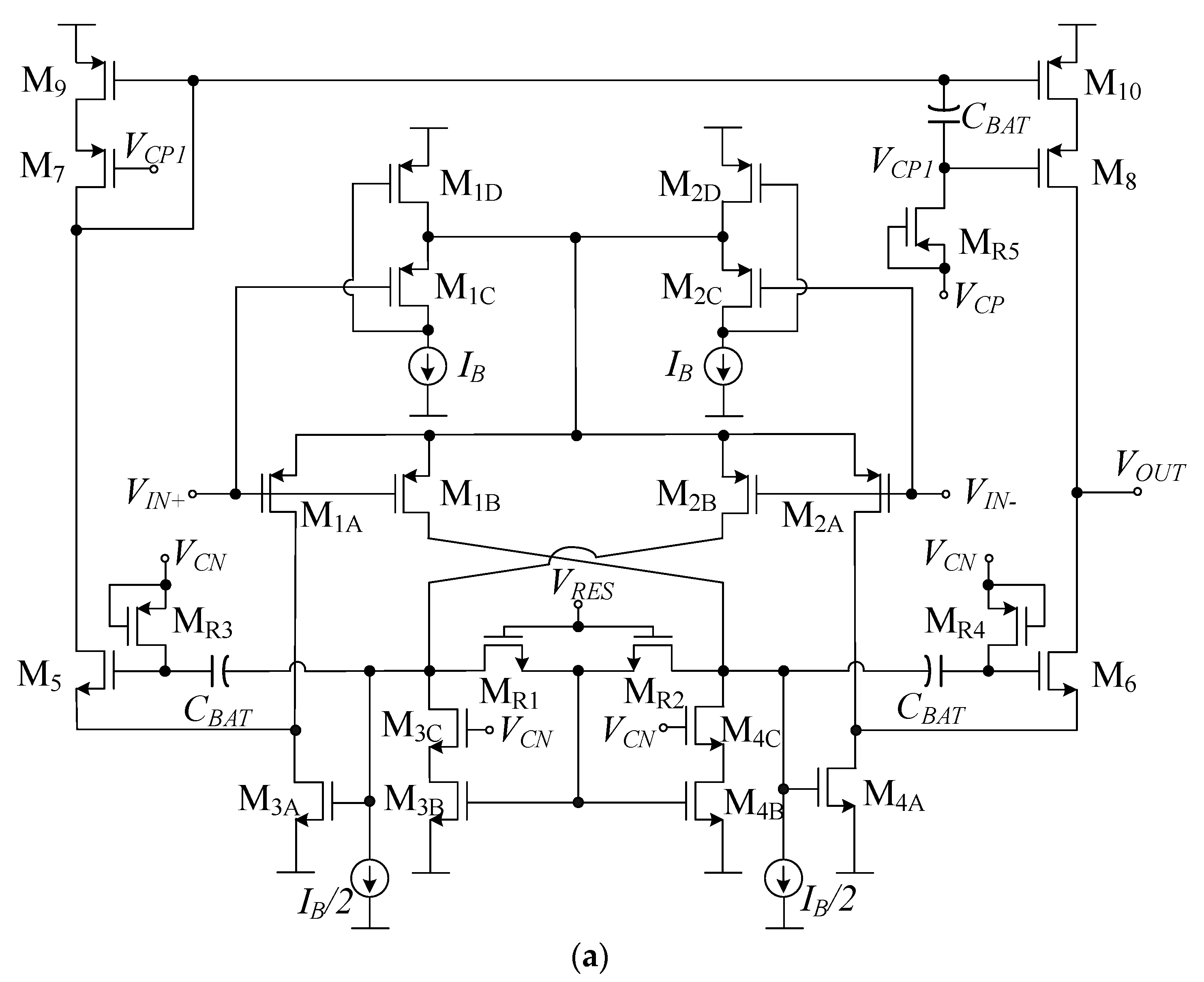

4. Design Example: Super Class AB QFG Amplifier in a 130 nm CMOS Process

4.1. Requirements and Figures of Merit for Energy Efficiency

4.2. Proposed Super Class AB Amplifier

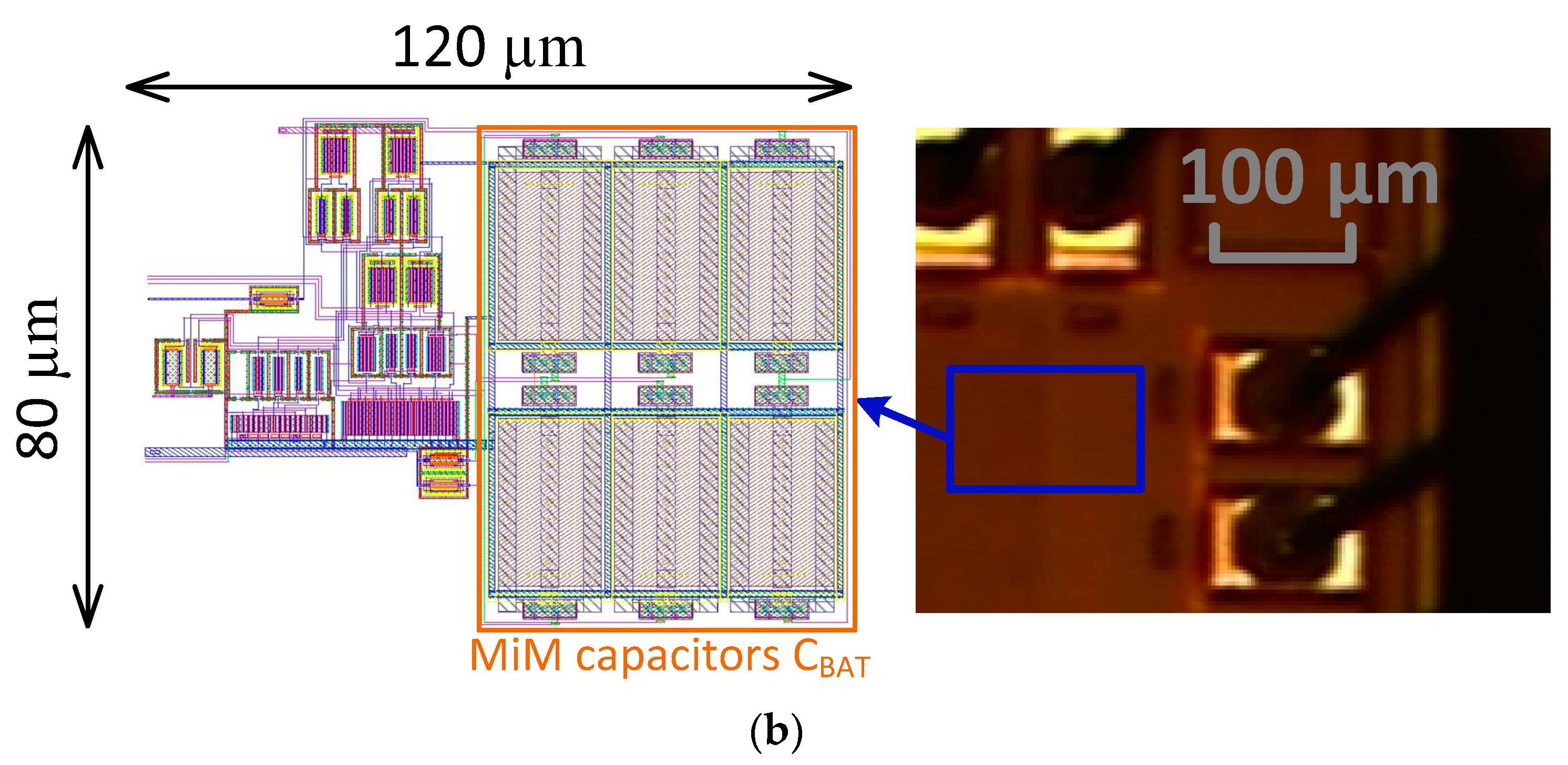

4.3. Circuit Analysis

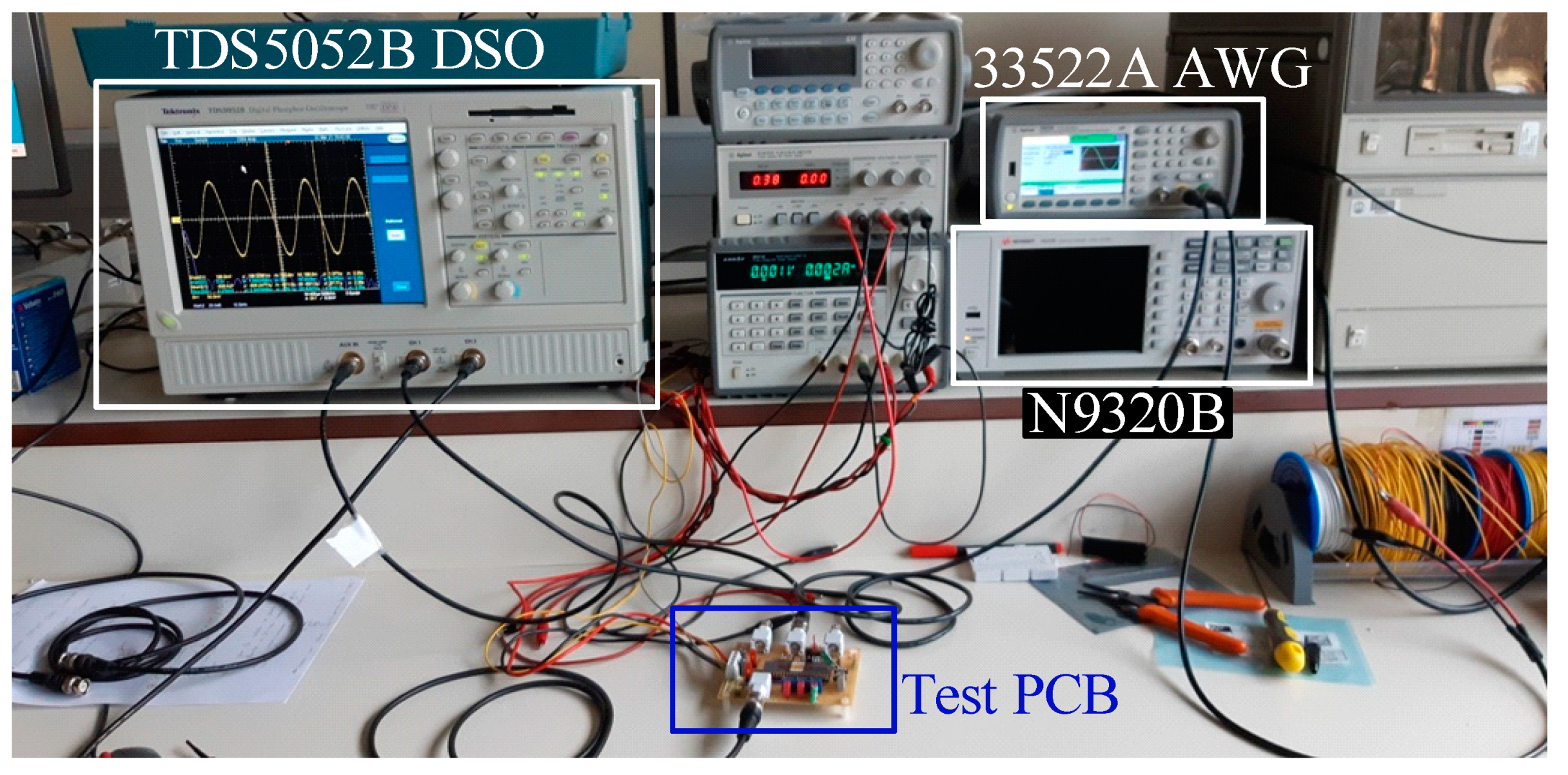

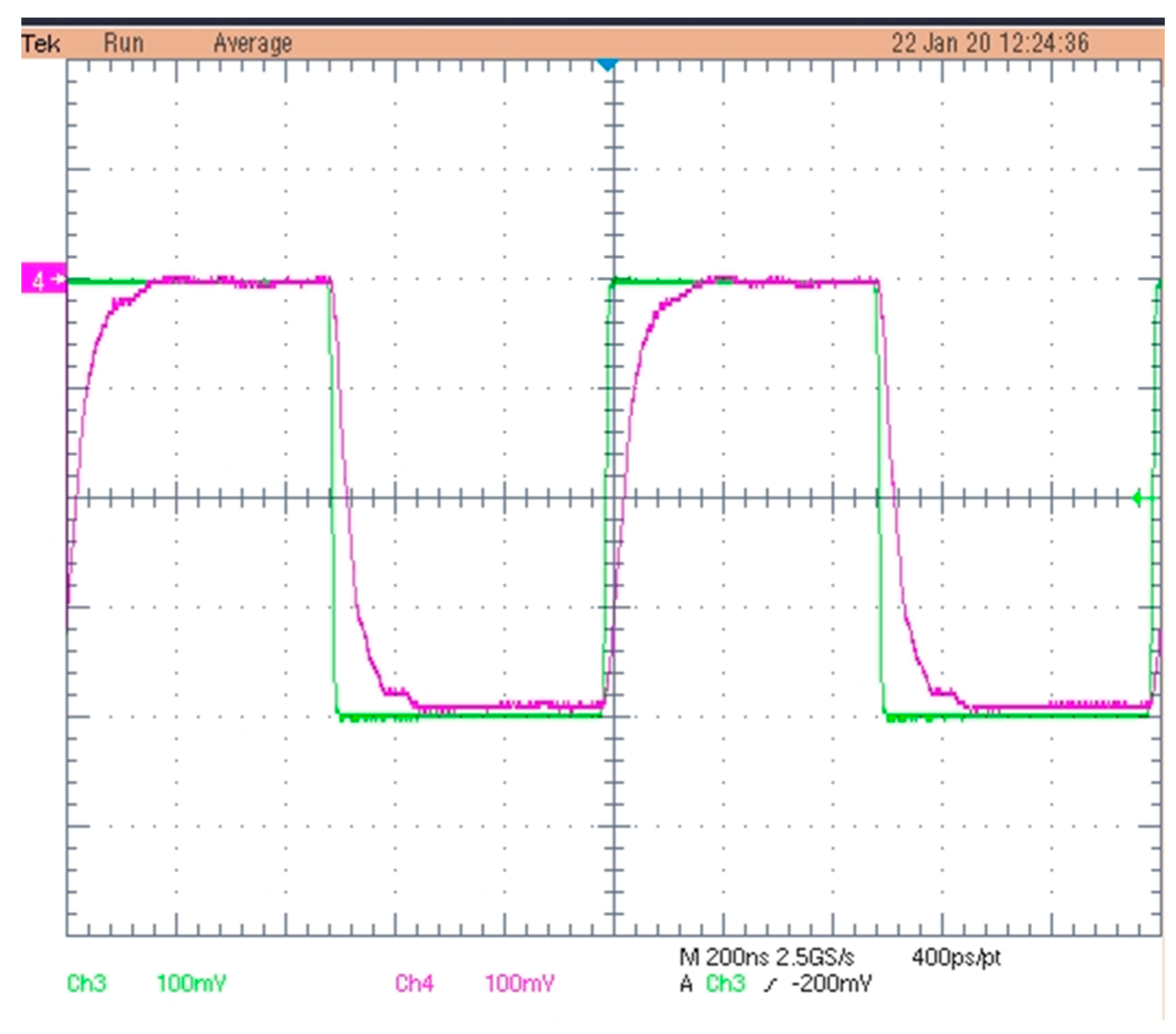

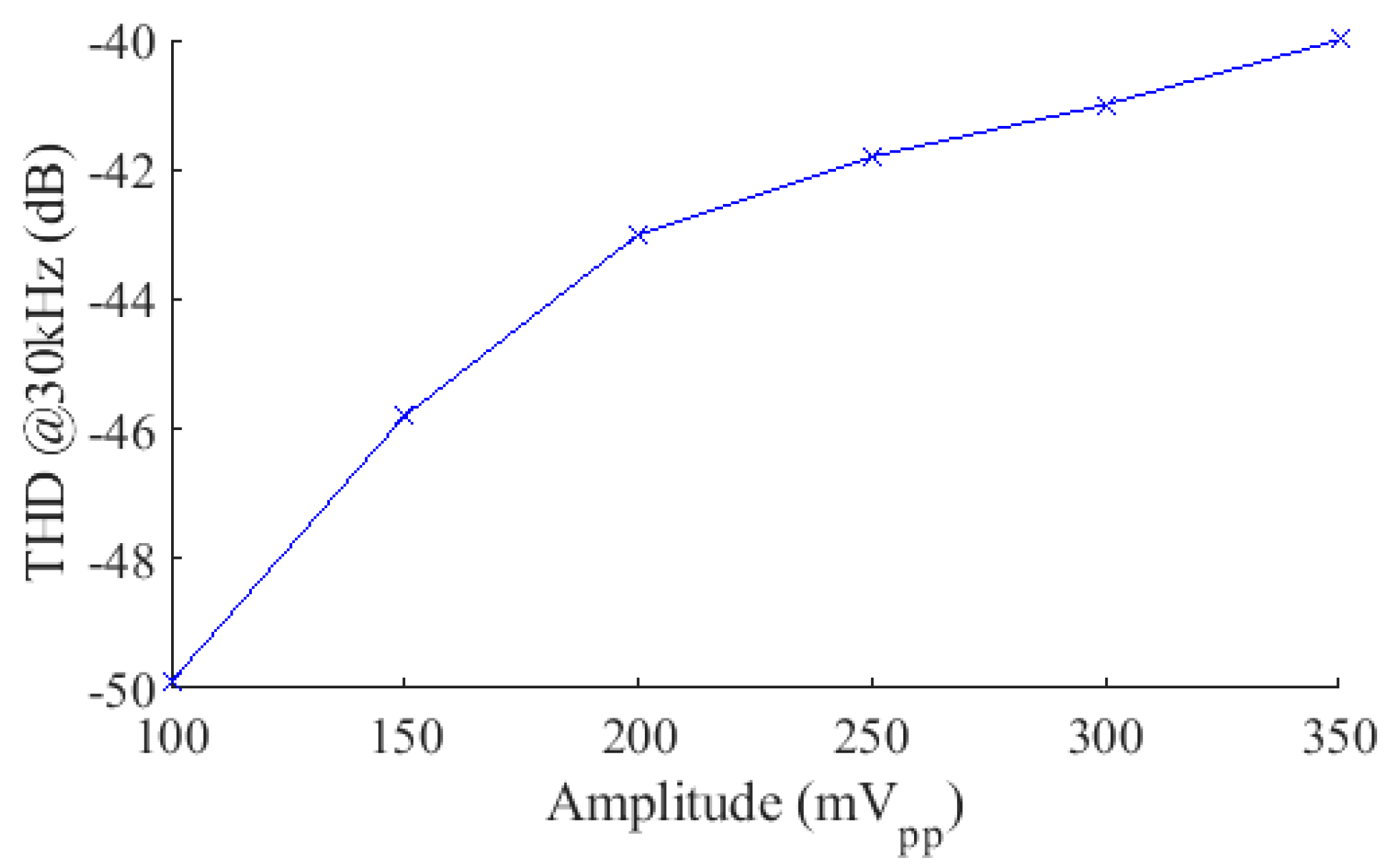

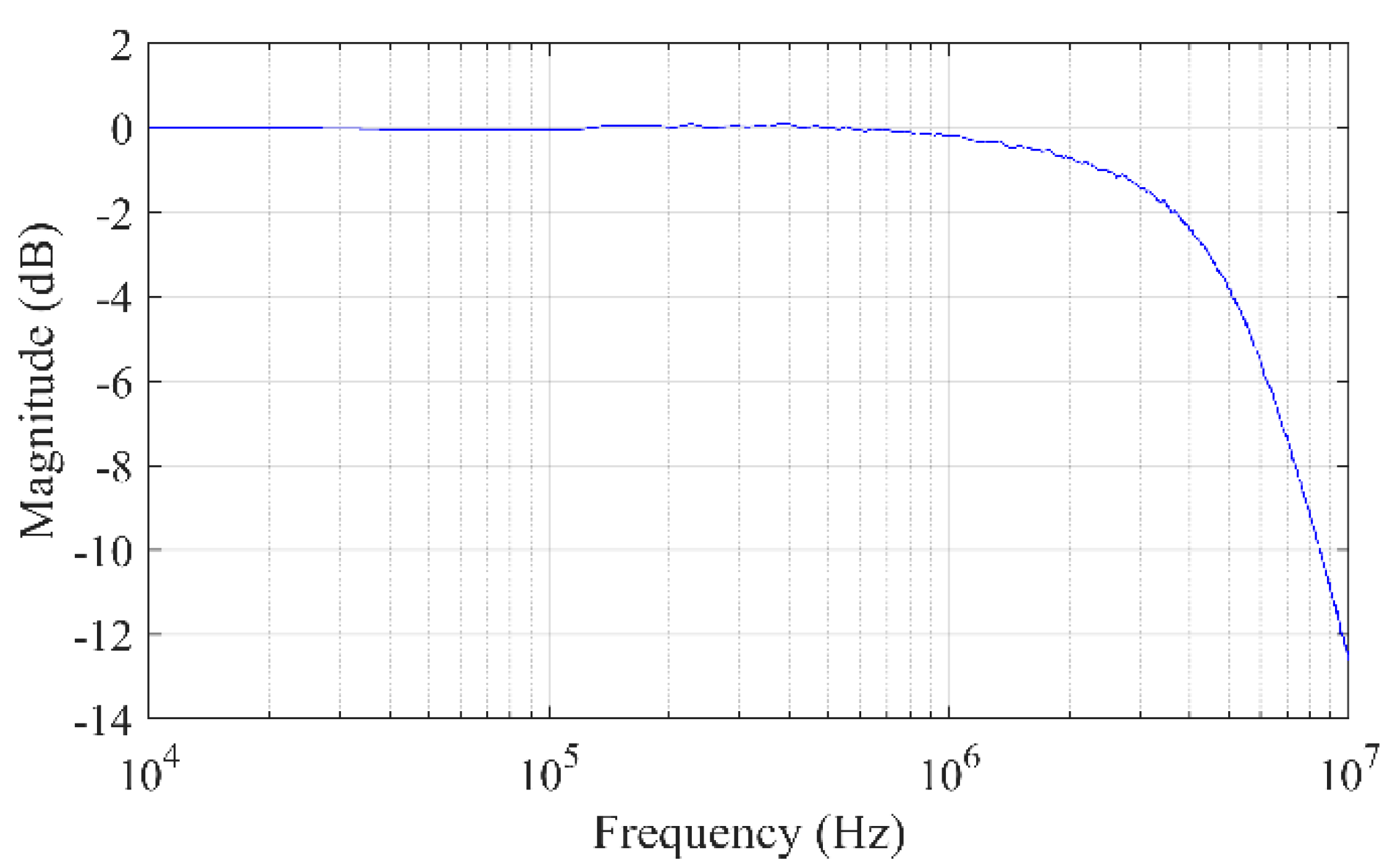

4.4. Measurement Results

5. Discussion

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Li, P.; Long, Z.; Yang, Z. RF Energy Harvesting for Battery-Less and Maintenance-Free Condition Monitoring of Railway Tracks. IEEE Internet Things J. 2020, 8, 3512–3523. [Google Scholar] [CrossRef]

- Bohr, M.T.; Young, I.A. CMOS Scaling Trends and Beyond. IEEE Micro 2017, 37, 20–29. [Google Scholar] [CrossRef]

- Svensson, C.; Wikner, J.J. Power consumption of analog circuits: A tutorial. Analog Integr. Circuits Signal Process. 2010, 65, 171–184. [Google Scholar] [CrossRef]

- Kim, J.; Song, S.; Roh, J. A High Slew-Rate Enhancement Class-AB Operational Transconductance Amplifier (OTA) for Switched-Capacitor (SC) Applications. IEEE Access 2020, 8, 226167–226175. [Google Scholar] [CrossRef]

- Ramirez-Angulo, J.; Lopez-Martin, A.J.; Carvajal, R.G.; Chavero, F.M. Very low-voltage analog signal processing based on quasi-floating gate transistors. IEEE J. Solid State Circuits 2004, 39, 434–442. [Google Scholar] [CrossRef]

- Harrison, R.R.; Charles, C. A low-power low-noise CMOS amplifier for neural recording applications. IEEE J. Solid State Circuits 2003, 38, 958–965. [Google Scholar] [CrossRef]

- Zou, X.; Xu, X.; Yao, L.; Lian, Y. A 1-V 450-nW Fully Integrated Programmable Biomedical Sensor Interface Chip. IEEE J. Solid-State Circuits 2009, 44, 1067–1077. [Google Scholar] [CrossRef]

- Guglielmi, E.; Toso, F.; Zanetto, F.; Sciortino, G.; Mesri, A.; Sampietro, M.; Ferrari, G. High-Value Tunable Pseudo-Resistors Design. IEEE J. Solid State Circuits 2020, 55, 2094–2105. [Google Scholar] [CrossRef]

- Pourashraf, S.; Ramirez-Angulo, J.; Lopez-Martin, A.J.; Carvajal, R.G.; Diaz-Sanchez, A. ±0.18-V supply voltage gate-driven PGA with 0.7-Hz to 2-kHz constant bandwidth and 0.15-μW power dissipation. Int. J. Circuit Theory Appl. 2018, 46, 272–279. [Google Scholar] [CrossRef]

- Wang, T.; Liu, L.; Peng, S. A Power-Efficient Highly Linear Reconfigurable Biopotential Sensing Amplifier Using Gate-Balanced Pseudoresistors. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 199–203. [Google Scholar] [CrossRef]

- Deepu, C.J.; Zhang, X.; Liew, W.; Wong, D.L.T.; Lian, Y. An ECG-on-Chip with 535 nW/Channel Integrated Lossless Data Compressor for Wireless Sensors. IEEE J. Solid State Circuits 2014, 49, 2435–2448. [Google Scholar] [CrossRef]

- Rezaee-Dehsorkh, H.; Ravanshad, N.; Lotfi, R.; Mafinezhad, K.; Sodagar, A.M. Analysis and Design of Tunable Amplifiers for Implantable Neural Recording Applications. IEEE J. Emerg. Sel. Topics Circuits Syst. 2011, 1, 546–556. [Google Scholar] [CrossRef]

- Bikumandla, M.; Ramírez-Angulo, J.; Urquidi, C.; Carvajal, R.G.; Lopez-Martin, A.J. Biasing CMOS amplifiers using MOS transistors in subthreshold region. IEICE Electron. Express 2004, 1, 339–345. [Google Scholar] [CrossRef]

- Ramirez-Angulo, J.; Sawant, M.; Lopez-Martin, A.; Carvajal, R.G. A Power Efficient and Simple Scheme for Dynamically Biasing Cascode Amplifiers and Telescopic Op-amps. Integr. Vlsi J. 2008, 41, 539–543. [Google Scholar] [CrossRef]

- Algueta-Miguel, J.M.; De la Cruz Blas, C.A.; Lopez-Martin, A.J.; Ramirez-Angulo, J. Design of CMOS amplifiers with offset rejection using positive-feedback QFG transistors. Analog. Integr. Circuits Signal Process. 2015, 85, 217–221. [Google Scholar] [CrossRef]

- Pourashraf, S.; Ramirez-Angulo, J.; Roman-Loera, A.; Lopez-Martin, A.J.; Diaz-Sanchez, A.; Carvajal, R.G. High current efficiency class-AB OTA with high open loop gain and enhanced bandwidth. IEICE Electron. Express 2017, 14, 20170719. [Google Scholar] [CrossRef]

- Saso, J.M.; Lopez-Martin, A.J.; Garde, M.P.; Ramirez-Angulo, J. Power-efficient class AB fully differential amplifier. Electron. Lett. 2017, 53, 1298–1300. [Google Scholar] [CrossRef]

- Pourashraf, S.; Ramirez-Angulo, J.; Lopez-Martin, A.J.; Carvajal, R.G. Super class AB OTA without open-loop gain degradation based on dynamic cascode biasing. Int. J. Cir. Theory Appl. 2017, 45, 2111–2118. [Google Scholar] [CrossRef]

- Lopez-Martin, A.J.; Garde, M.P.; Algueta, J.M.; de la Cruz Blas, C.A.; Carvajal, R.G.; Ramirez-Angulo, J. Enhanced Single-Stage Folded Cascode OTA Suitable for Large Capacitive Loads. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 441–445. [Google Scholar] [CrossRef]

- Garde, M.P.; Lopez-Martin, A.J.; Ramirez-Angulo, J. Power-efficient class-AB telescopic cascode opamp. Electron. Lett. 2018, 54, 620–622. [Google Scholar] [CrossRef]

- Algueta-Miguel, J.M.; Lopez-Martin, A.; Garde, M.P.; De La Cruz, C.A.; Ramirez-Angulo, J. ±0.5 V 15 uW Recycling Folded Cascode Amplifier With 34767 MHz·pF/mA FOM. IEEE Solid State Circuits Lett. 2018, 1, 170–173. [Google Scholar] [CrossRef]

- Garde, M.P.; Lopez-Martin, A.; Algueta, J.M.; Carvajal, R.G.; Ramirez-Angulo, J. Class AB Amplifier with Enhanced Slew Rate and GBW. Int. J. Circuit Theory Appl. 2019, 47, 1199–1210. [Google Scholar] [CrossRef]

- Galán, J.; López-Ahumada, R.; Sánchez-Rodríguez, T.; Torralba, A.; Carvajal, R.G.; Martel, I. Low Voltage Power Efficient Tunable Shaper Circuit With Rail-To-Rail Output Range for the HYDE Detector at FAIR. IEEE Trans. Nucl. Sci. 2014, 61, 844–851. [Google Scholar] [CrossRef]

- Safari, L.; Azhari, S.J. An ultra low power, low voltage tailless QFG based differential amplifier with High CMRR, rail to rail operation and enhanced slew rate. Analog. Integr. Circuits Signal Process. 2011, 67, 241–252. [Google Scholar] [CrossRef]

- Ramirez-Angulo, J.; Carvajal, R.G.; Galan, J.A.; Lopez-Martin, A.J. A free but efficient low-voltage class-AB two-stage operational amplifier. IEEE Trans. Circuits Syst. II Express Briefs 2006, 53, 568–571. [Google Scholar] [CrossRef]

- Zhang, X.; Chi, B.; Wang, Z. A 0.1–1.5 GHz Harmonic Rejection Receiver Front-End with Phase Ambiguity Correction, Vector Gain Calibration and Blocker-Resilient TIA. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 1005–1014. [Google Scholar] [CrossRef]

- Rico-Aniles, H.D.; Ramirez-Angulo, J.; Rocha-Perez, J.M.; Lopez-Martin, A.J.; Carvajal, R.G. Low-Voltage 0.81mW, 1–32 CMOS VGA with 5% Bandwidth Variations and −38dB DC Rejection. IEEE Access 2020, 8, 106310–106321. [Google Scholar] [CrossRef]

- Roman-Loera, A.; Ramirez-Angulo, J.; Lopez-Martin, A.J.; Carvajal, R.G. Free class AB–AB Miller opamp with high current enhancement. Electron. Lett. 2015, 51, 215–217. [Google Scholar] [CrossRef]

- Paul, A.; Ramírez-Angulo, J.; López-Martín, A.J.; Carvajal, R.G.; Rocha-Pérez, J.M. Pseudo-Three-Stage Miller Op-Amp with Enhanced Small-Signal and Large-Signal Performance. IEEE Trans. VLSI Syst. 2019, 27, 2246–2259. [Google Scholar] [CrossRef]

- Garcia-Alberdi, C.; Aguado-Ruiz, J.; Lopez-Martin, A.J.; Ramirez-Angulo, J. Micropower Class-AB VGA with Gain-Independent Bandwidth. IEEE Trans. Circuits Syst. II Express Briefs 2013, 60, 397–401. [Google Scholar] [CrossRef]

- Lopez-Martin, A.J.; Ramirez-Angulo, J.; Carvajal, R.G.; Algueta, J.M. Compact class AB CMOS current mirror. Electron. Lett. 2008, 44, 1335–1336. [Google Scholar] [CrossRef]

- Esparza-Alfaro, F.; Lopez-Martin, A.J.; Ramirez-Angulo, J.; Carvajal, R.G. High-performance micropower class AB current mirror. Electron. Lett. 2012, 48, 823–824. [Google Scholar] [CrossRef]

- Esparza-Alfaro, F.; Lopez-Martin, A.J.; Ramirez-Angulo, J.; Carvajal, R.G. Low-voltage highly-linear class AB current mirror with dynamic cascode biasing. Electron. Lett. 2012, 48, 1336–1338. [Google Scholar] [CrossRef]

- Esparza-Alfaro, F.; Lopez-Martin, A.J.; Carvajal, R.G.; Ramirez-Angulo, J. Highly linear micropower class AB current mirrors using Quasi-Floating Gate transistors. Microelectron. J. 2014, 61, 1261–1267. [Google Scholar] [CrossRef]

- Pourashraf, S.; Ramírez-Angulo, J.; Hinojo Montero, J.M.; González-Carvajal, R.; Lopez-Martin, A.J. ±0.25-V Class-AB CMOS Capacitance Multiplier and Precision Rectifiers. IEEE Trans. VLSI Syst. 2019, 27, 830–842. [Google Scholar] [CrossRef]

- Ramirez-Angulo, J.; Urquidi, C.A.; Gonzalez-Carvajal, R.; Torralba, A.; Lopez-Martin, A. A new family of very low-voltage analog circuits based on quasi-floating-gate transistors. IEEE Trans. Circuits Syst. I Analog Digit. Signal Process. 2003, 50, 214–220. [Google Scholar] [CrossRef]

- Ramírez-Angulo, J.; Urquidi, C.; Carvajal, R.G.; Torralba, A.; Lopez-Martin, A.J. Low-Voltage Analog Circuits Based on Wideband Capacitive Coupling. Analog Integr. Circuits Signal Process. 2003, 37, 253–257. [Google Scholar] [CrossRef]

- Ramirez-Angulo, J.; Sawant, M.; Carvajal, R.G.; Lopez-Martin, A.J. Linearisation of MOS resistors using capacitive gate voltage averaging. Electron. Lett. 2005, 41, 511–512. [Google Scholar] [CrossRef]

- Torralba, A.; Lujan-Martinez, C.; Carvajal, R.G.; Galan, J.; Pennisi, M.; Ramirez-Angulo, J.; Lopez-Martin, A. Tunable Linear MOS Resistors Using Quasi-Floating-Gate Techniques. IEEE Trans. Circuits Syst. II Express Briefs 2009, 56, 41–45. [Google Scholar] [CrossRef]

- Sanchez-Rodriguez, T.; Galan, J.; Carvajal, R.G.; Lopez-Martin, A.J.; Ramirez-Angulo, J. DC offset control with application in a zero-IF 0.18 μm CMOS Bluetooth receiver chain. Analog Integr. Circuits Signal Process. 2010, 65, 15–20. [Google Scholar] [CrossRef]

- Nunez, J.; Tlelo, E.; Ramirez, C.; Jimenez, J. CCII+ Based on QFGMOS for Implementing Chua s Chaotic Oscillator. IEEE Lat. Am. Trans. 2015, 13, 2865–2870. [Google Scholar] [CrossRef]

- Kumngern, M.; Khateb, F. 0.5 V fully differential current conveyor using bulk-driven quasi-floating-gate technique. IET Circuit Dev. Syst. 2016, 10, 78–86. [Google Scholar] [CrossRef]

- Moradzadeh, H.; Azhari, S.J. Low-voltage low-power rail-to-rail low-Rx wideband second generation current conveyor and a single resistance-controlled oscillator based on it. IET Circuit Dev. Syst. 2011, 5, 66–72. [Google Scholar] [CrossRef]

- Esparza-Alfaro, F.; Pennisi, S.; Palumbo, G.; Lopez-Martin, A.J. Low-Power Class-AB CMOS Voltage Feedback Current Operational Amplifier With Tunable Gain and Bandwidth. IEEE Trans. Circuits Syst. II Express Briefs 2014, 61, 574–578. [Google Scholar] [CrossRef]

- Lopez-Martin, A.J.; Ramirez-Angulo, J.; Carvajal, R.G.; Acosta, L. Micropower high current-drive class AB CMOS current-feedback operational amplifier. Int. J. Circuit Theory Appl. 2011, 39, 839–903. [Google Scholar] [CrossRef]

- Ramirez-Angulo, J.; Lopez-Martin, A.J.; Carvajal, R.G.; Torralba, A.; Jimenez, M. Simple Class AB voltage follower with slew rate and bandwidth enhancement and no extra static power or supply requirements. Electron. Lett. 2006, 42, 784–785. [Google Scholar] [CrossRef]

- Ramirez-Angulo, J.; Lopez-Martin, A.J.; Carvajal, R.G.; Calvo, B. Class-AB Fully Differential Voltage Followers. IEEE Trans. Circuits Syst. II Express Briefs 2008, 55, 131–135. [Google Scholar] [CrossRef]

- Lopez-Martin, A.J.; Ramirez-Angulo, J.; Carvajal, R.G.; Acosta, L. Power-efficient class AB CMOS buffer. Electron. LET Ters. 2009, 45, 89–90. [Google Scholar] [CrossRef]

- Lopez-Martin, A.J.; Algueta, J.M.; Acosta, L. Ramirez-Angulo, J.; Carvajal, R.G. Design of Two-Stage Class AB CMOS Buffers: A Systematic Approach. ETRI J. 2011, 33, 393–400. [Google Scholar] [CrossRef]

- Lopez-Martin, A.J.; Acosta, L.; Garcia-Alberdi, C.; Carvajal, R.G.; Ramirez-Angulo, J. Power-efficient analog design based on the class AB super source follower. Int. J. Circuit Theory Appl. 2012, 40, 1143–1163. [Google Scholar] [CrossRef]

- Haga, Y.; Kale, I. CMOS buffer using complementary pair of bulk-driven super source followers. Electron. Lett. 2009, 45, 917–918. [Google Scholar] [CrossRef]

- Khateb, F.; Vlassis, S.; Kumngern, M.; Psychalinos, C.; Kulej, T.; Vrba, R.; Fujcik, L. 1 V Rectifier Based on Bulk-Driven Quasi-Floating-Gate Differential Difference Amplifiers. Circuits Syst. Signal Process. 2015, 34, 2077–2089. [Google Scholar] [CrossRef]

- Algueta, J.M.; De La Cruz Blas, C.A. Lopez-Martin, A.J. CMOS triode transconductor based on quasi-floating-gate transistors. Electronics Lett. 2010, 46, 1190–1191. [Google Scholar] [CrossRef]

- Algueta, J.M.; Lopez-Martin, A.J.; Acosta, L.; Ramirez-Angulo, J. Using Floating Gate and Quasi-Floating Gate Techniques for Rail-to-Rail Tunable CMOS Transconductor Design. IEEE Trans. Circuits Syst. I Regul. Pap. 2011, 58, 1604–1614. [Google Scholar] [CrossRef]

- Lopez-Martin, A.J.; Algueta, J.M.; Garcia-Alberdi, C.; Acosta, L.; Carvajal, R.G.; Ramirez-Angulo, J. Design of micropower class AB transconductors: A systematic approach. Microelectron. J. 2013, 44, 920–929. [Google Scholar] [CrossRef]

- Crovetti, P.S. A Digital-Based Analog Differential CircuiT. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 3107–3116. [Google Scholar] [CrossRef]

- Gatti, A.; Spiazzi, G.; Gerosa, A.; Neviani, A.; Bevilacqua, A. A 130-nm CMOS Dual Input-Polarity DC–DC Converter for Low-Power Applications. IEEE Solid State Circuits Lett. 2019, 2, 211–214. [Google Scholar] [CrossRef]

- Dhanasekaran, V.; Gambhir, M.; Silva-Martinez, J.; Sanchez-Sinencio, E. A 1.1 GHz Fifth Order Active-LC Butterworth Type Equalizing Filter. IEEE J. Solid State Circuits 2007, 42, 2411–2420. [Google Scholar] [CrossRef]

- Garcia-Alberdi, C.; Lopez-Martin, A.J.; Acosta, L.; Carvajal, R.G.; Ramirez-Angulo, J. Tunable Class AB CMOS Gm-C Filter Based on Quasi-Floating Gate Techniques. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 1300–1309. [Google Scholar] [CrossRef]

- Garcia-Alberdi, C.; Lopez-Martin, A.J.; Galan, J.A.; Carvajal, R.G.; Ramirez-Angulo, J. Low-Power Analog Channel Selection Filtering Techniques. Circuits Syst Signal Process. 2017, 36, 895–915. [Google Scholar] [CrossRef]

- Paul, A.; Ramírez-Angulo, J.; Lopez-Martin, A.J.; Carvajal, R.G. CMOS First-Order All-Pass Filter With 2-Hz Pole Frequency. IEEE Trans. VLSI Syst. 2019, 27, 294–303. [Google Scholar] [CrossRef]

- Lopez-Morillo, E.; Carvajal, R.G.; Muñoz, F.; El Gmili, H.; Lopez-Martin, A.; Ramirez-Angulo, J.; Rodriguez-Villegas, E. A 1.2-V 140-nW 10-bit Sigma–Delta Modulator for Electroencephalogram Applications. IEEE Trans. Biomed. Circuits Syst. 2008, 2, 223–230. [Google Scholar] [CrossRef] [PubMed]

- Peng, S.-Y.; Qureshi, M.S.; Hasler, P.E.; Basu, A.; Degertekin, F.L. A Charge-Based Low-Power High-SNR Capacitive Sensing Interface Circuit. IEEE Trans. Circuits Syst. I Regul. Pap. 2008, 55, 1863–1872. [Google Scholar] [CrossRef] [PubMed]

- Castillo-Cabrera, G.; García-Lamont, J.; Reyes-Barranca, M.A.; Matsumoto-Kuwabara, Y.; Moreno-Cadenas, J.A.; Flores-Nava, L.M. CMOS prototype for retinal prosthesis applications with analog processing. Int. J. Electron. 2014, 101, 1621–1646. [Google Scholar] [CrossRef]

- Yao, L.; Steyaert, M.S.J.; Sansen, W. A 1-V 140-/spl mu/W 88-dB audio sigma-delta modulator in 90-nm CMOS. IEEE J. Solid-State Circuits 2004, 39, 1809–1818. [Google Scholar] [CrossRef]

- Carvajal, R.G.; Ramírez-Angulo, J.; López-Martín, A.J.; Torralba, A.; Galán, J.A.G.; Carlosena, A.; Chavero, F.M. The flipped voltage follower: A useful cell for low-voltage low-power circuit design. IEEE Trans. Circuits Syst. I Regul. Pap. 2005, 52, 1276–1291. [Google Scholar] [CrossRef]

- Baswa, S.; Martín, A.J.L.; Ramirez-Angulo, J.; Carvajal, R.G. Winner-Take-All Class AB Input Stage. Analog Integr. Circuit Sig Process. 2006, 46, 149–152. [Google Scholar] [CrossRef]

- Peng, X.; Sansen, W. AC boosting compensation scheme for low-power multistage amplifiers. IEEE J. Solid State Circuit 2004, 39, 2074–2077. [Google Scholar] [CrossRef]

- Lopez-Martin, A.J.; Baswa, S.; Ramirez-Angulo, J.; Carvajal, R.G. Low-voltage Super Class AB CMOS OTA cells with very high slew rate and power efficiency. IEEE J. Solid State Circuits 2005, 40, 1068–1077. [Google Scholar] [CrossRef]

- Garde, M.P.; Lopez-Martin, A.; Carvajal, R.G.; Ramírez-Angulo, J. Super Class-AB Recycling Folded Cascode OTA. IEEE J. Solid State Circuits 2018, 53, 2614–2623. [Google Scholar] [CrossRef]

- Yao, L.; Steyaert, M.; Sansen, W. A 0.8-V, 8-µW CMOS OTA with 50-dB gain and 1.2-MHz GBW in 18-pF load. In Proceedings of the 29th European Solid-State Circuits Conference, Estoril, Portugal, 16–18 September 2003; pp. 297–300. [Google Scholar] [CrossRef]

- Naderi, M.H.; Prakash, S.; Silva-Martinez, J. Operational Transconductance Amplifier with Class-B Slew-Rate Boosting for Fast High-Performance Switched-Capacitor Circuits. IEEE Trans. Circuits Syst. I 2018, 65, 3769–3779. [Google Scholar] [CrossRef]

- Valero Bernal, M.R.; Celma, S.; Medrano, N.; Calvo, B. An ultralow-power low-voltage class-AB fully differential OpAmp for long-life autonomous portable equipment. IEEE Trans. Circuits Syst. II 2012, 59, 643–647. [Google Scholar] [CrossRef]

- Cabrera-Bernal, E.; Pennisi, S.; Grasso, A.D.; Torralba, A.; Carvajal, R.G. 0.7-V three-stage class-AB CMOS Operational Transconductance Amplifier. IEEE Trans. Circuits Syst. I 2016, 63, 1807–1815. [Google Scholar] [CrossRef]

- Sutula, S.; Dei, M.; Teres, L.; Serra-Graells, F. Variable-mirror amplifier: A new family of process-independent class-AB single-stage OTAs for low-power SC circuits. IEEE Trans. Circuits Syst. I 2016, 63, 1101–1110. [Google Scholar] [CrossRef]

- Sundararajan, A.D.; Hasan, S.M.R. Quadruply split cross-driven doubly recycled gm-doubling recycled folded cascode for microsensor instrumentation amplifiers. IEEE Trans. Circuits Syst. II 2016, 63, 543–547. [Google Scholar] [CrossRef]

| Parameter (units) | Figure 8 | [18] | [19] | [69] | [70] | [72] | [73] | [74] | [75] | [76] |

|---|---|---|---|---|---|---|---|---|---|---|

| CMOS process (nm) | 130 | 180 | 500 | 500 | 500 | 40 | 180 | 180 | 180 | 130 |

| Supply voltage (V) | ±0.5 | ±0.9 | ±1 | ±1 | ±1 | 1.1 | 0.8 | 0.7 | 1.8 | 1.2 |

| Capacitive load (pF) | 140/120 | 23 | 70 | 80 | 70 | 0.5 | 8 | 20 | 200 | 5.2 |

| SR+ (V/μs) | 5.7 | 24.11 | 9.8 | 100 | 13.2 | 1250 | 0.14 | 1.8 | 74.1 | 98.7 |

| SR- (V/μs) | −7.1 | −23.33 | −7.6 | −78 | −25.3 | -- | -- | −3.8 | -- | -- |

| DC gain (dB) | 63.88 a | 67 | 81.7 | 43 | 76.8 | 49 | 51 | 57.5 | 72 | 75.4 |

| PM (°) | 61 a | 84 | 60 | 89.5 | 75.1 | 65 | 60 | 60 | 50 | 82.5 |

| GBW (MHz) | 4.48 | 0.57 | 4.75 | 0.725 | 3.4 | 3600 | 57 | 3 | 86.5 | 166.1 |

| CMRR @DC (dB) | 56.7 a | 73.2 | 78 | 68 | 112 | -- | -- | 19 | -- | -- |

| PSRR+ @DC (dB) | 61.5 a | 44.1 | 72 | 55 | 92 | -- | -- | 52.1 | -- | -- |

| PSRR- @DC (dB) | 71.9 a | 41.8 | 74 | 58 | 113 | -- | -- | 66.4 | -- | -- |

| Eq. input noise @1MHz (nV/√Hz) | 27.5 | -- | 35 | 230 | 23 | -- | -- | 100 | -- | -- |

| Power (μW) | 30 | 14.5 | 120 | 120 | 100 | 3300 | 1.2 | 25.4 | 11900 | 236.4 |

| Area (mm2) | 0.009 | 0.030 | 0.024 | 0.024 | 0.030 | 0.050 | 0.057 | 0.020 | 0.070 | -- |

| FoML (μA/μA) | 29.90 | 67.72 | 10.15 | 118.67 | 26.95 | 0.21 | 0.75 | 1.54 | 2.24 | 2.61 |

| FoMS (MHz·pF/mA) | 17920 | 1627.4 | 5541.7 | 966.7 | 4760 | 600 | 304 | 1653.5 | 2616.8 | 4384.4 |

| 732 | 332 | 237.1 | 338.7 | 358.1 | 11.18 | 15.1 | 50.5 | 76.6 | 106.9 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lopez-Martin, A.; Garde, M.P.; Algueta-Miguel, J.M.; Beloso-Legarra, J.; Carvajal, R.G.; Ramirez-Angulo, J. Energy-Efficient Amplifiers Based on Quasi-Floating Gate Techniques. Appl. Sci. 2021, 11, 3271. https://doi.org/10.3390/app11073271

Lopez-Martin A, Garde MP, Algueta-Miguel JM, Beloso-Legarra J, Carvajal RG, Ramirez-Angulo J. Energy-Efficient Amplifiers Based on Quasi-Floating Gate Techniques. Applied Sciences. 2021; 11(7):3271. https://doi.org/10.3390/app11073271

Chicago/Turabian StyleLopez-Martin, Antonio, Maria Pilar Garde, Jose M. Algueta-Miguel, Javier Beloso-Legarra, Ramon G. Carvajal, and Jaime Ramirez-Angulo. 2021. "Energy-Efficient Amplifiers Based on Quasi-Floating Gate Techniques" Applied Sciences 11, no. 7: 3271. https://doi.org/10.3390/app11073271

APA StyleLopez-Martin, A., Garde, M. P., Algueta-Miguel, J. M., Beloso-Legarra, J., Carvajal, R. G., & Ramirez-Angulo, J. (2021). Energy-Efficient Amplifiers Based on Quasi-Floating Gate Techniques. Applied Sciences, 11(7), 3271. https://doi.org/10.3390/app11073271