Design of W-Band GaN-on-Silicon Power Amplifier Using Low Impedance Lines

Abstract

:1. Introduction

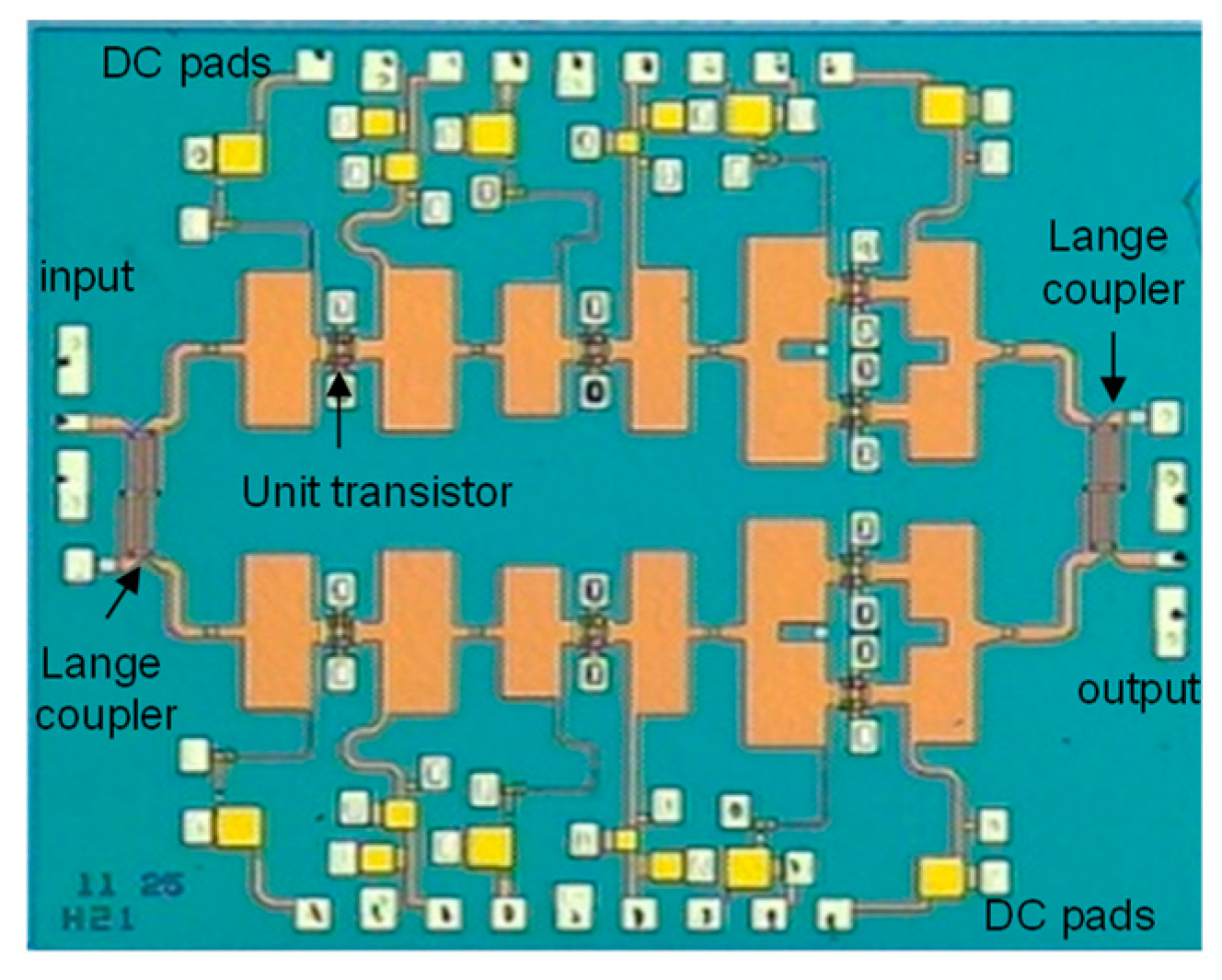

2. Design of W-Band Power Amplifier in GaN on Si HEMTs

2.1. GaN on Silicon HEMTs

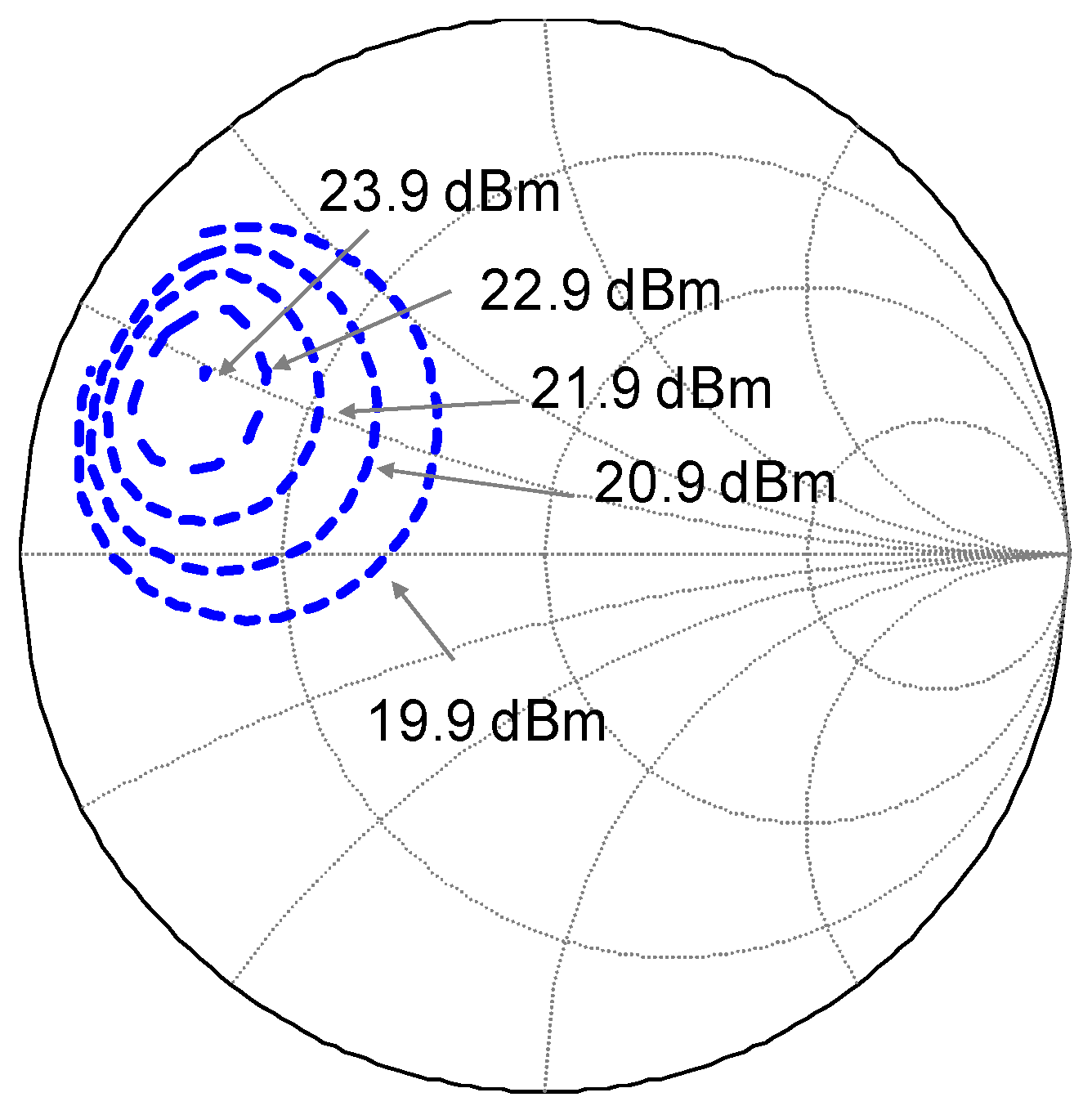

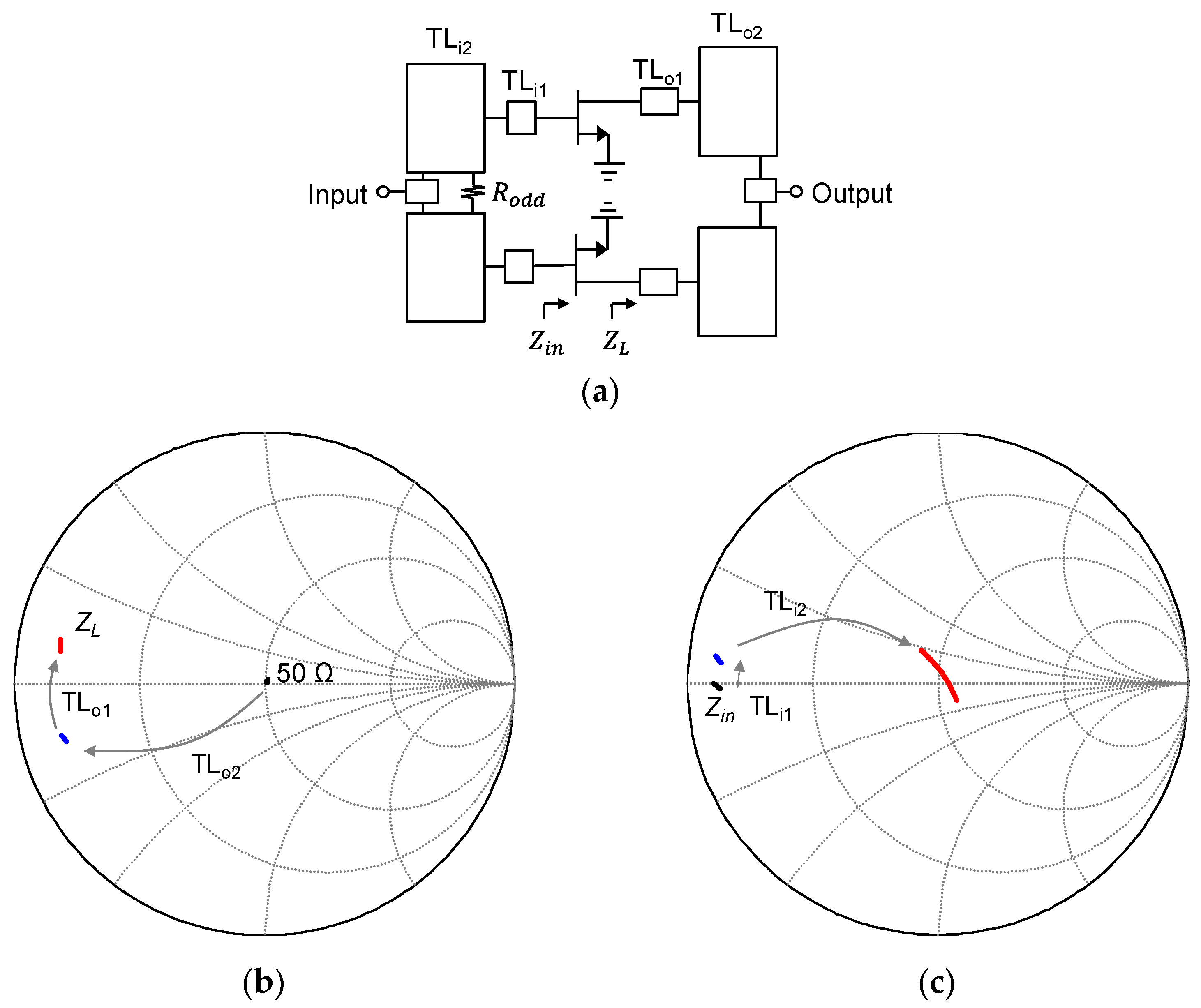

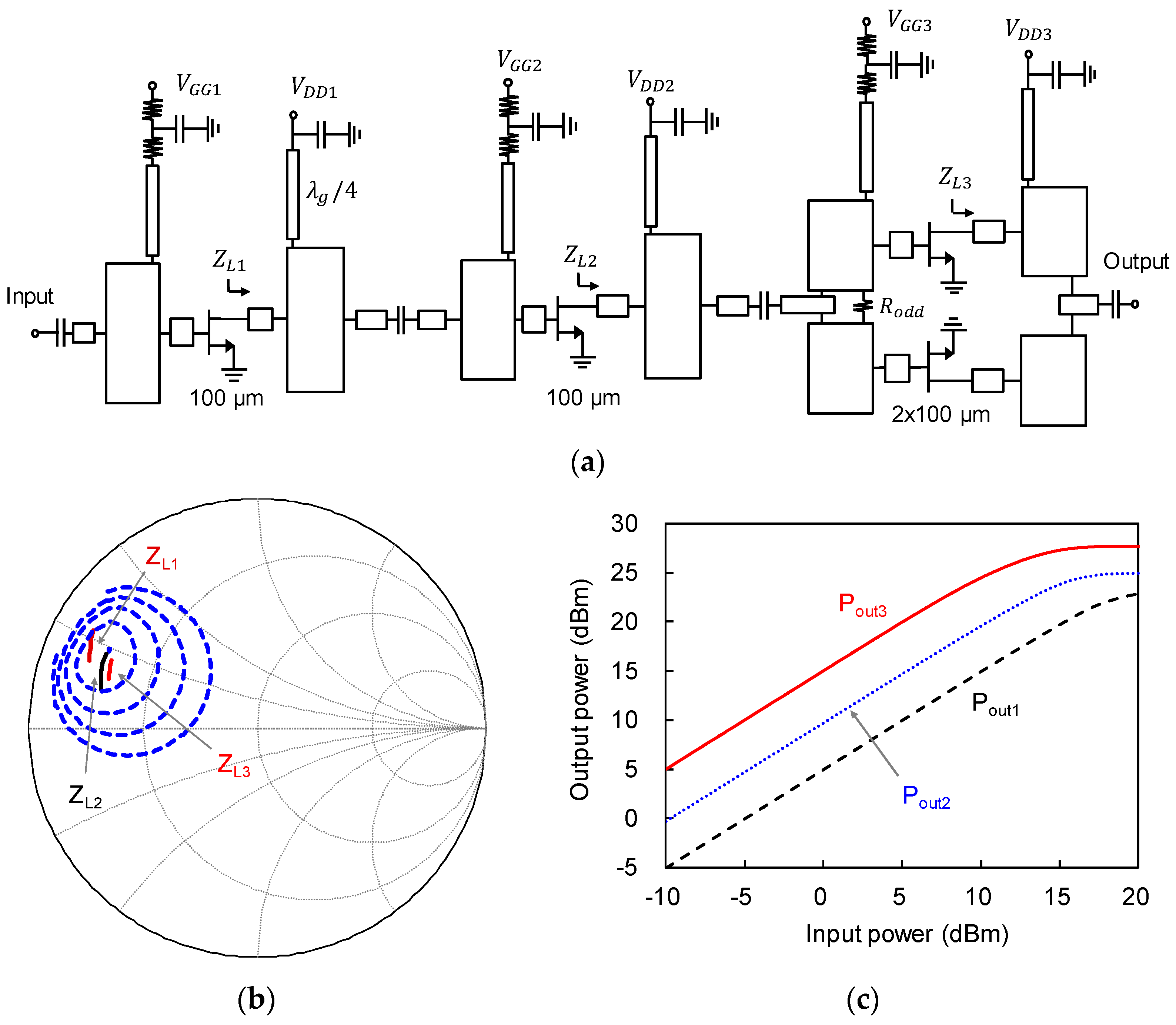

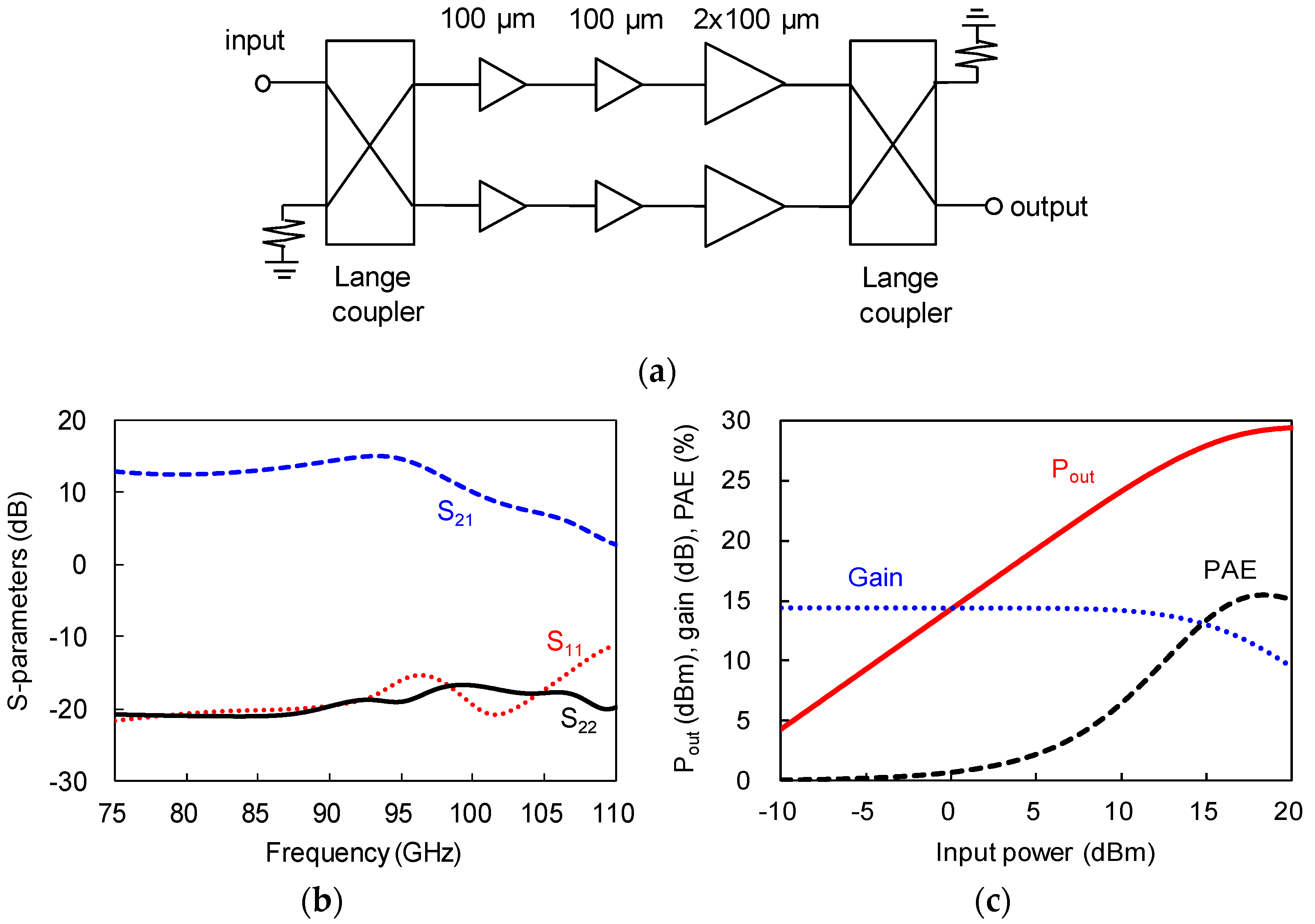

2.2. Design of W-Band Three-Stage Power Amplifier

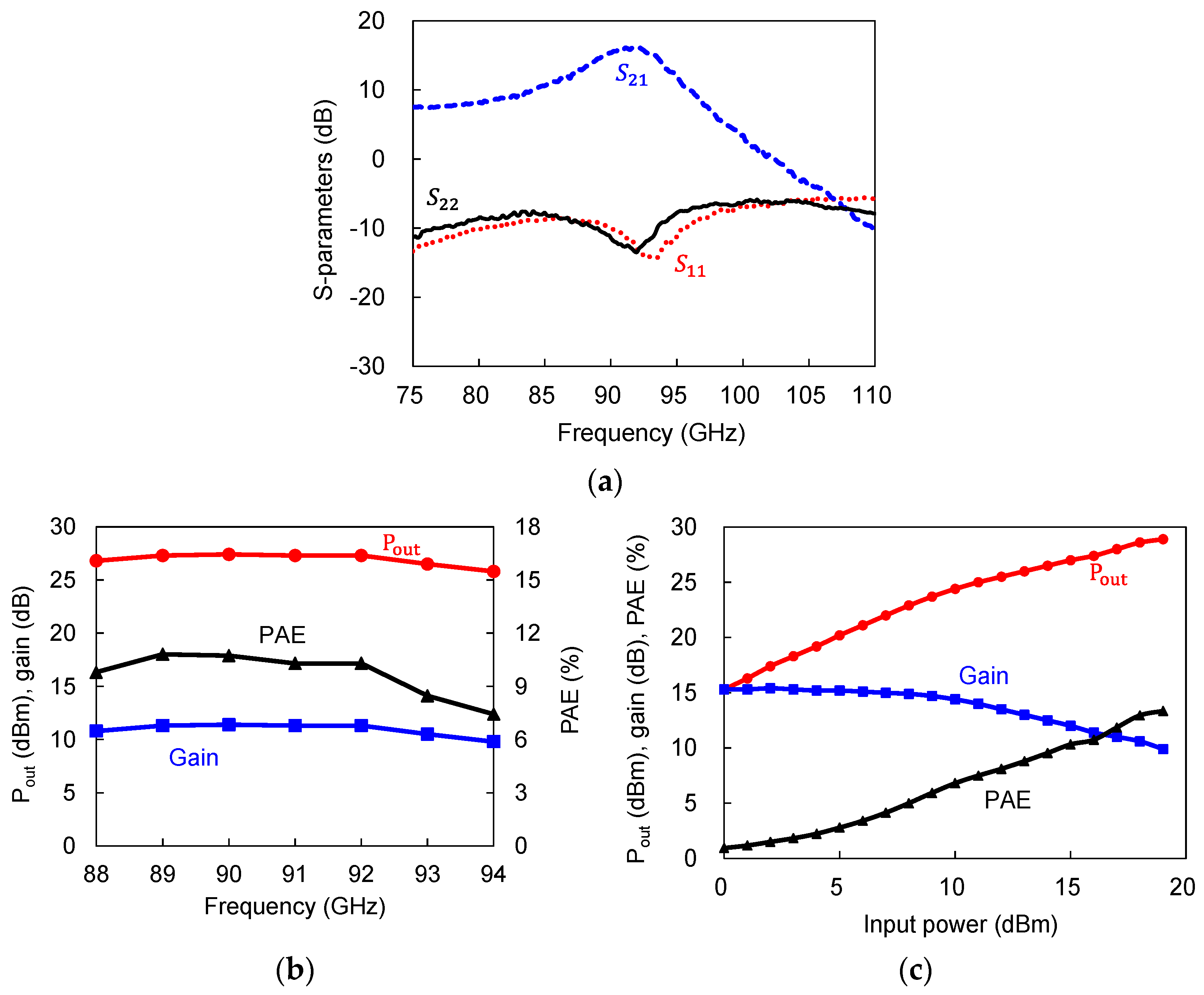

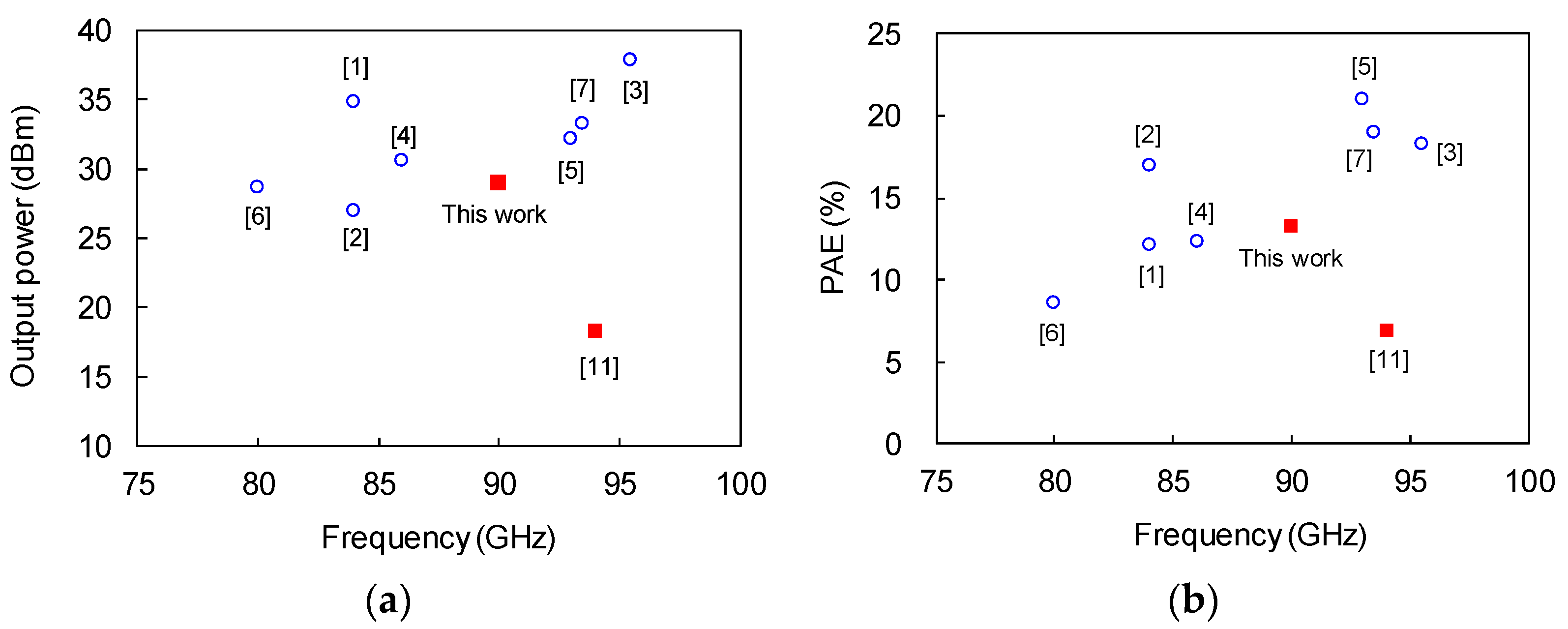

3. Measurement Results

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Schellenberg, J.M. A 2-W W-Band GaN traveling-wave amplifier with 25-GHz bandwidth. IEEE Trans. Microw. Theory Tech. 2015, 63, 2833–2840. [Google Scholar] [CrossRef]

- Micovic, M.; Kurdoghlian, A.; Moyer, H.P.; Hashimoto, P.; Hu, M.; Antcliffe, M.; Willadsen, P.J.; Wong, W.S.; Bowen, R.; Milosavljevic, I.; et al. GaN MMIC PAs for E-Band (71 GHz–95 GHz) Radio. In Proceedings of the 2008 IEEE Compound Semiconductor Integrated Circuits Symposium, Monterey, CA, USA, 12–15 October 2008; pp. 1–4. [Google Scholar] [CrossRef]

- Wang, W.; Guo, F.; Chen, T.; Wang, K. 24.8 A W-band power amplifier with distributed common-source GaN HEMT and 4-Way Wilkinson-Lange combiner achieving 6W output power and 18% PAE at 95GHz. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 376–378. [Google Scholar] [CrossRef]

- Niida, Y.; Kamada, Y.; Ohki, T.; Ozaki, S.; Makiyama, K.; Minoura, Y.; Okamoto, N.; Sato, M.; Joshin, K.; Watanabe, K. 3.6 W/mm high power density W-band InAlGaN/GaN HEMT MMIC power amplifier. In Proceedings of the 2016 IEEE Topical Conference on Power Amplifiers for Wireless and Radio Applications (PAWR), Austin, TX, USA, 24–27 February 2016; pp. 24–26. [Google Scholar] [CrossRef]

- Shaobing, W.; JianFeng, G.; Weibo, W.; Junyun, Z. W-Band MMIC PA with ultrahigh power density in 100-nm AlGaN/GaN Technology. IEEE Trans. Electron. Devices 2016, 63, 3882–3886. [Google Scholar] [CrossRef]

- Cwiklinski, M.; Friesicke, C.; Bruckner, P.; Schwantuschke, D.; Wagner, S.; Lozar, R.; Mabler, H.; Quay, R.; Ambacher, O. Full W-Band GaN Power Amplifier MMICs using a novel type of broadband radial stub. IEEE Trans. Microw. Theory Tech. 2018, 66, 5664–5675. [Google Scholar] [CrossRef]

- Micovic, M.; Kurdoghlian, A.; Margomenos, A.; Brown, D.F.; Shinohara, K.; Burnham, S.; Milosavljevic, I.; Bowen, R.; Williams, A.; Hashimoto, P.; et al. 9296 GHz GaN power amplifiers. In Proceedings of the 2012 IEEE/MTT-S International Microwave Symposium Digest, Montreal, QC, Canada, 17–22 June 2012; pp. 1–3. [Google Scholar] [CrossRef]

- Quay, R.; Schwantuschke, D.; Ture, E.; Van Raay, F.; Friesicke, C.; Krause, S.; Müller, S.; Breuer, S.; Godejohann, B.; Brückner, P. High-Power Microwave GaN/AlGaN HEMTs and MMICs on SiC and silicon substrates for modern radio communication. Phys. Status Solidi 2018, 215, 1–7. [Google Scholar] [CrossRef]

- Gasmi, A.; El Kaamouchi, M.; Poulain, J.; Wroblewski, B.; Lecourt, F.; Dagher, G.; Frijlink, P.; Leblanc, R. 10 W power amplifier and 3W transmit/receive module with 3 dB NF in Ka band using a 100nm GaN/Si process. In Proceedings of the 2017 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), Miami, FL, USA, 22–25 October 2017; pp. 1–4. [Google Scholar] [CrossRef]

- Moron, J.; Leblanc, R.; Lecourt, F.; Frijlink, P. 12W, 30% PAE, 40 GHz power amplifier MMIC using a commercially available GaN/Si process. In Proceedings of the 2018 IEEE/MTT-S International Microwave Symposium-IMS, Philadelphia, PA, USA, 10–15 June 2020; pp. 1457–1460. [Google Scholar] [CrossRef]

- Marti, D.; Lugani, L.; Carlin, J.-F.; Malinverni, M.; Grandjean, N.; Bolognesi, R. W-Band MMIC Amplifiers Based on AlInN/GaN HEMTs Grown on Silicon. IEEE Electron. Device Lett. 2016, 37, 1025–1028. [Google Scholar] [CrossRef]

- Colangeli, S.; Ciccognani, W.; Longhi, P.E.; Pace, L.; Poulain, J.; Leblanc, R.; Limiti, E. Linear Characterization and Modeling of GaN-on-Si HEMT Technologies with 100 nm and 60 nm Gate Lengths. Electron 2021, 10, 134. [Google Scholar] [CrossRef]

- Cripps, S. RF Power Amplifiers for Wireless Communications, 2nd ed.; Artech House: Norwood, MA, USA, 2006; pp. 92–100. ISBN 9781596930193. [Google Scholar]

- Li, J. Wideband PCB-to-Connectors Impedance Adapters for Liquid Crystal-based Low-loss Phase Shifters. In Proceedings of the 2020 50th European Microwave Conference (EuMC), Utrecht, The Netherlands, 12–14 January 2021; pp. 546–549. [Google Scholar]

- Timothy, B. GaN-on-Silicon-Present capabilities and future directions. In Proceedings of the AIP Conference, Mayan Riviera, Mexico, 28 August–2 September 2016; Volume 1934, pp. 1–10. [Google Scholar] [CrossRef]

- Pozar, D. Microwave Engineering, 4th ed.; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2011; pp. 343–362. ISBN 0470631554. [Google Scholar]

- Choe, W.; Kim, S.; Kim, W.; Jeong, J. W-band mixer with high image rejection by mismatch compensation using buffer amplifier. IEEE Access 2020, 8, 5824–5833. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jeong, J.; Jang, Y.; Kim, J.; Kim, S.; Kim, W. Design of W-Band GaN-on-Silicon Power Amplifier Using Low Impedance Lines. Appl. Sci. 2021, 11, 9017. https://doi.org/10.3390/app11199017

Jeong J, Jang Y, Kim J, Kim S, Kim W. Design of W-Band GaN-on-Silicon Power Amplifier Using Low Impedance Lines. Applied Sciences. 2021; 11(19):9017. https://doi.org/10.3390/app11199017

Chicago/Turabian StyleJeong, Jinho, Yeongmin Jang, Jongyoun Kim, Sosu Kim, and Wansik Kim. 2021. "Design of W-Band GaN-on-Silicon Power Amplifier Using Low Impedance Lines" Applied Sciences 11, no. 19: 9017. https://doi.org/10.3390/app11199017

APA StyleJeong, J., Jang, Y., Kim, J., Kim, S., & Kim, W. (2021). Design of W-Band GaN-on-Silicon Power Amplifier Using Low Impedance Lines. Applied Sciences, 11(19), 9017. https://doi.org/10.3390/app11199017