Ka-Band Stacked Power Amplifier Supporting 3GPP New Radio FR2 Band n258 Implemented Using 45 nm CMOS SOI

Abstract

:1. Introduction

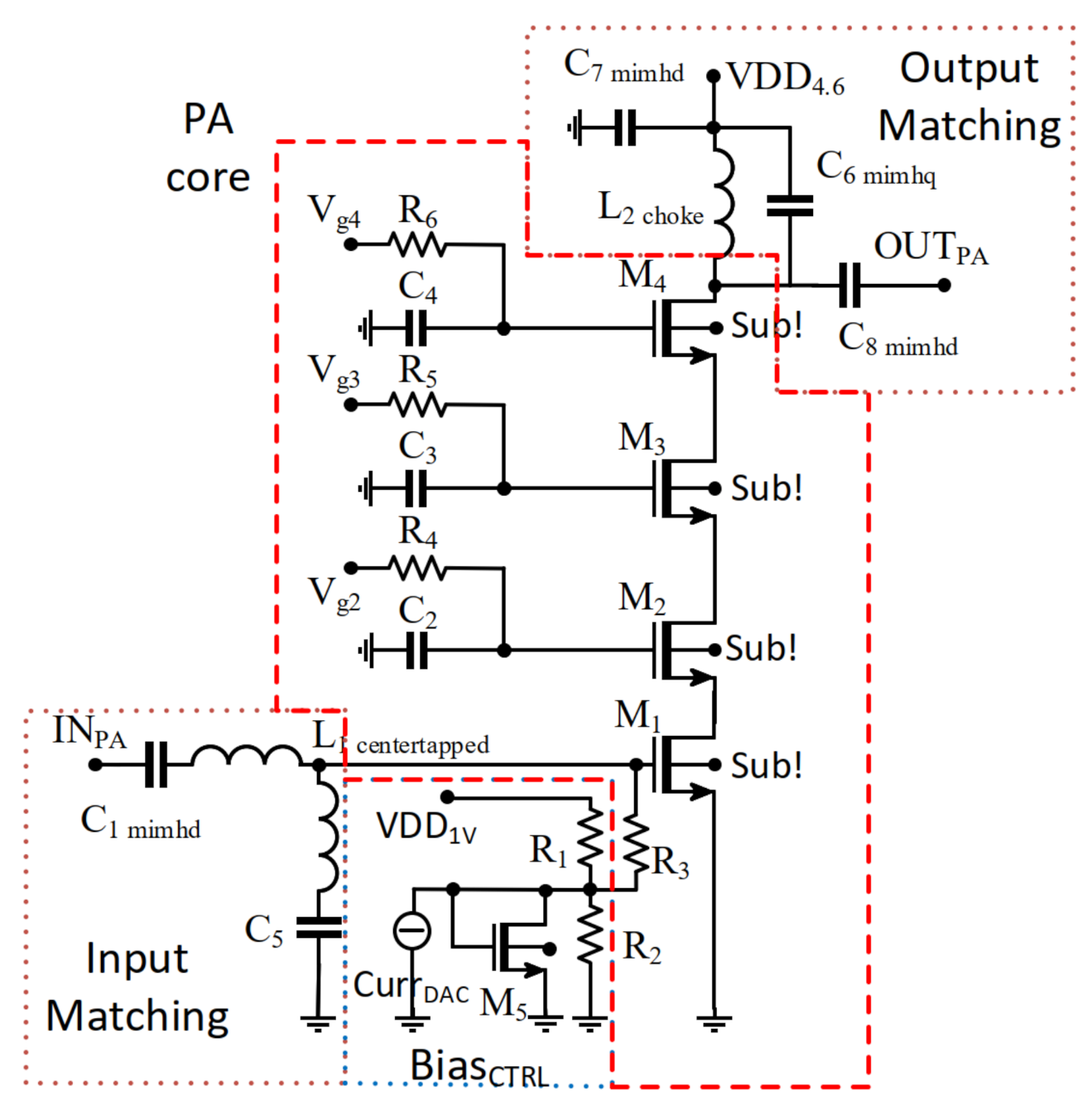

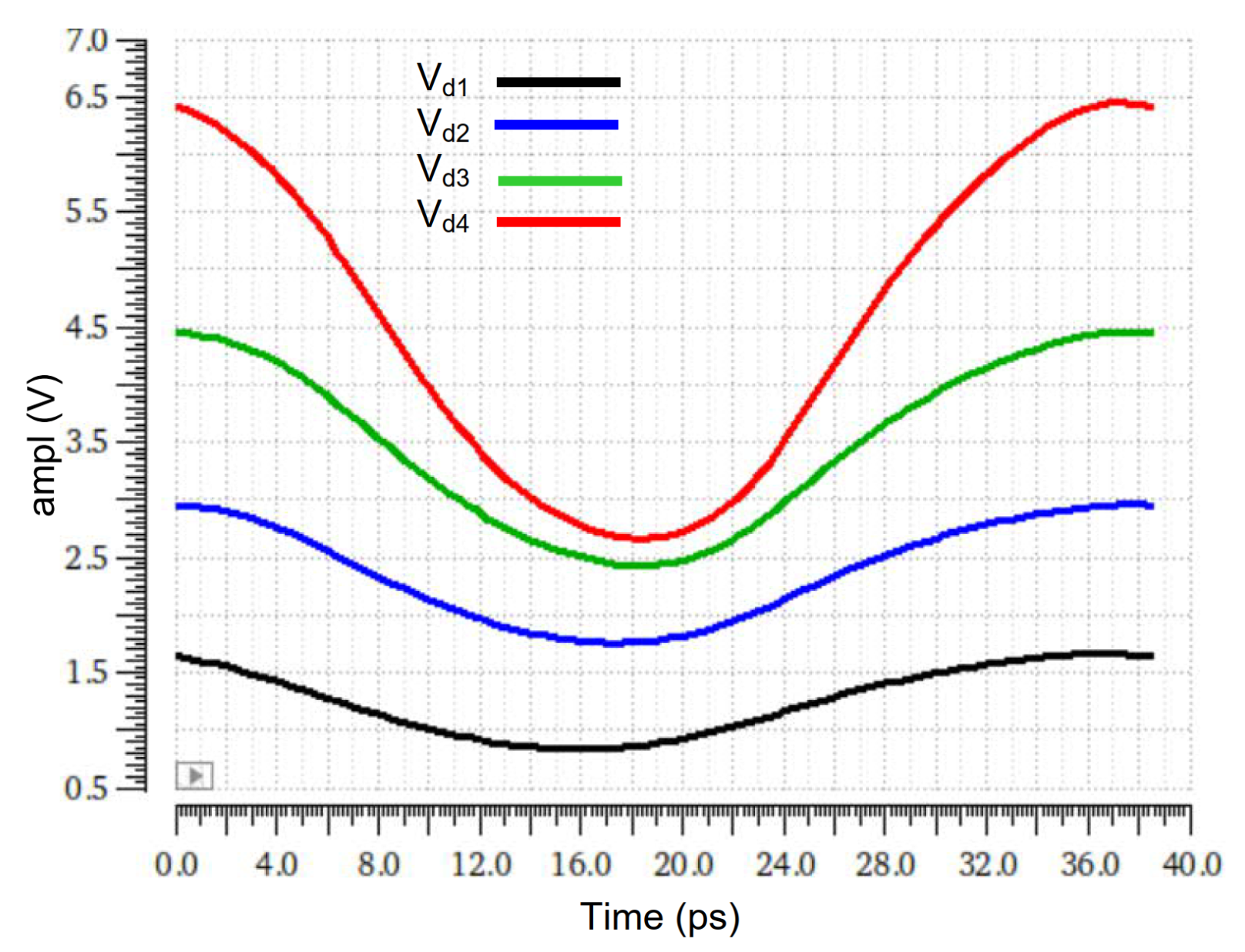

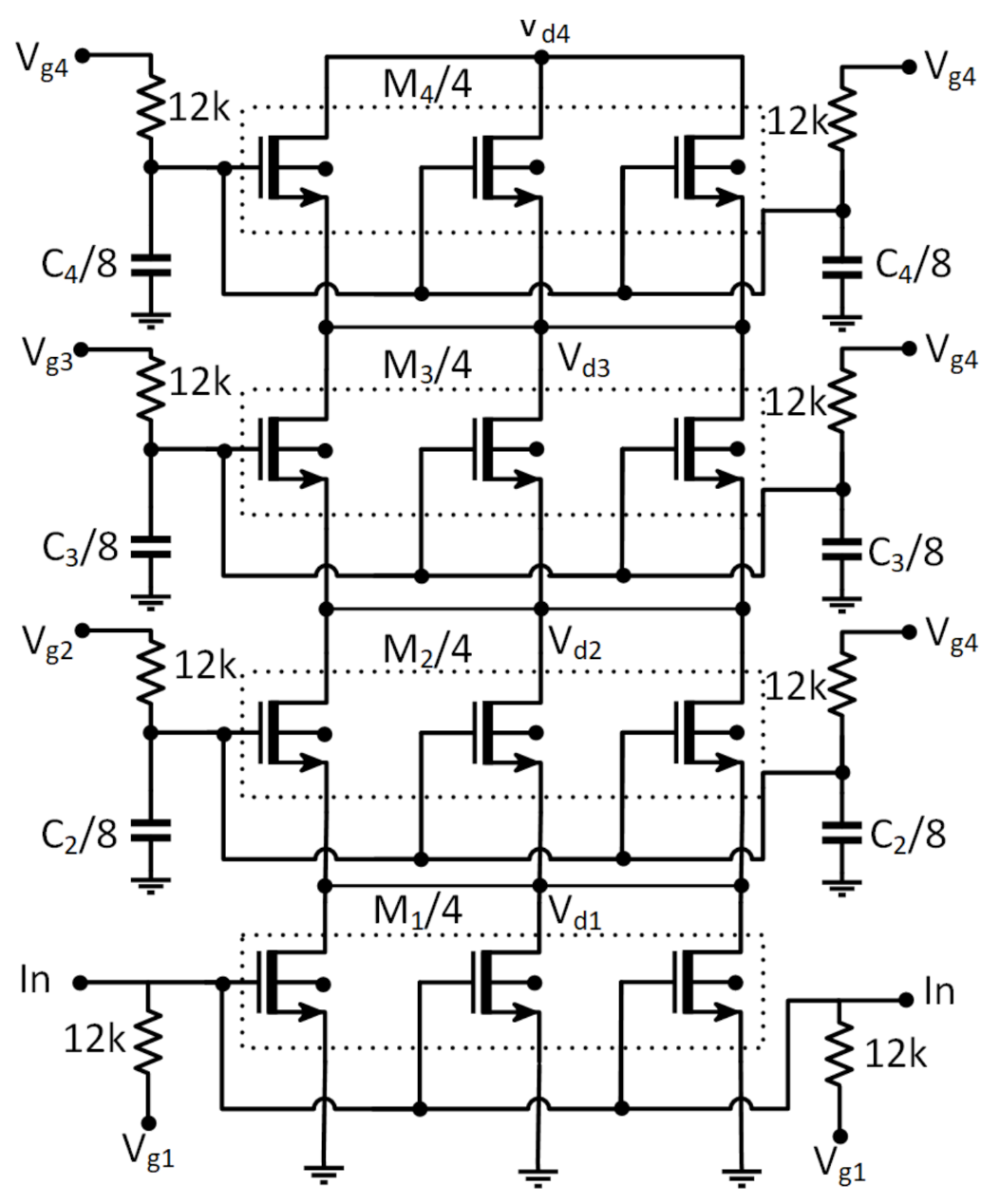

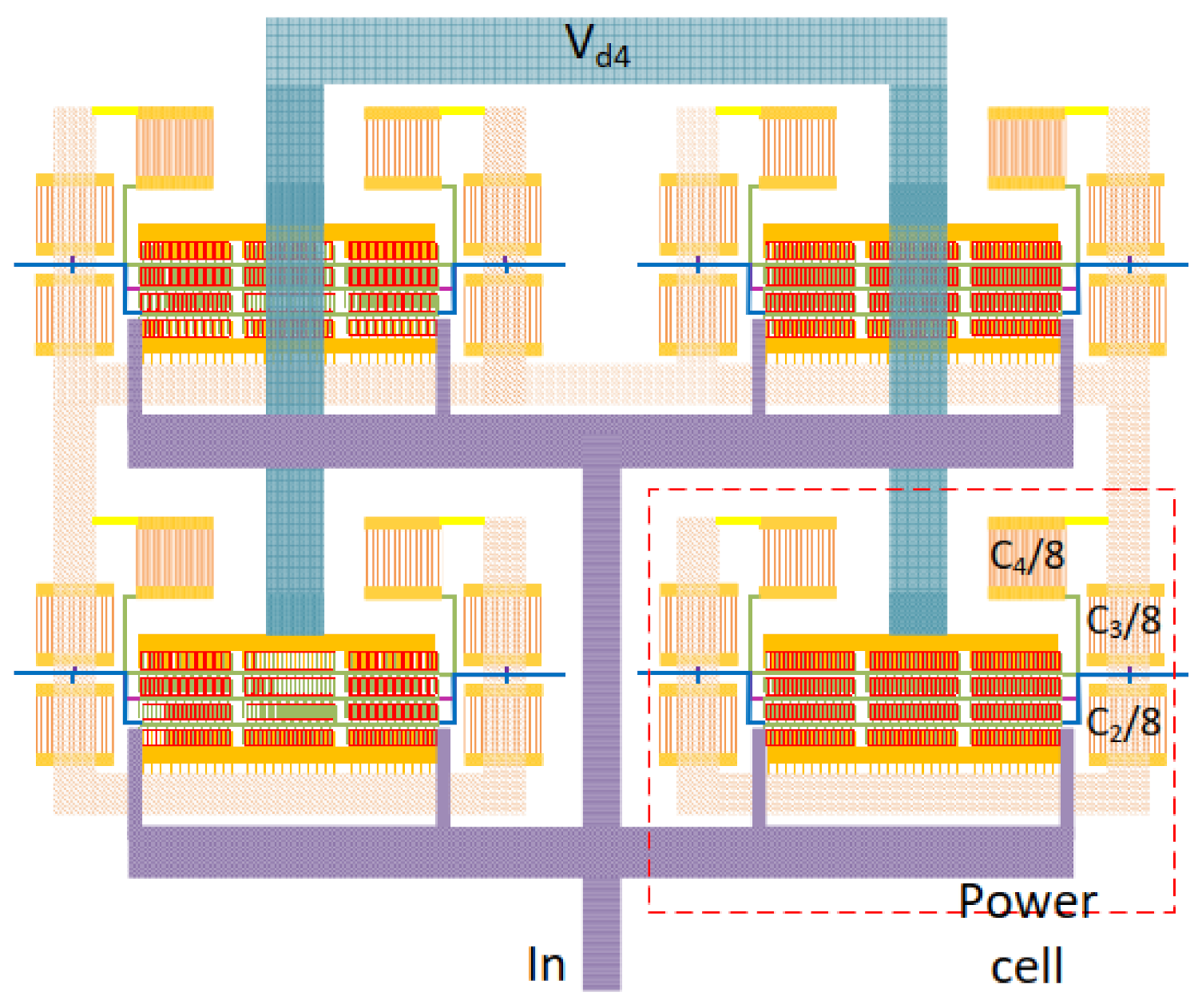

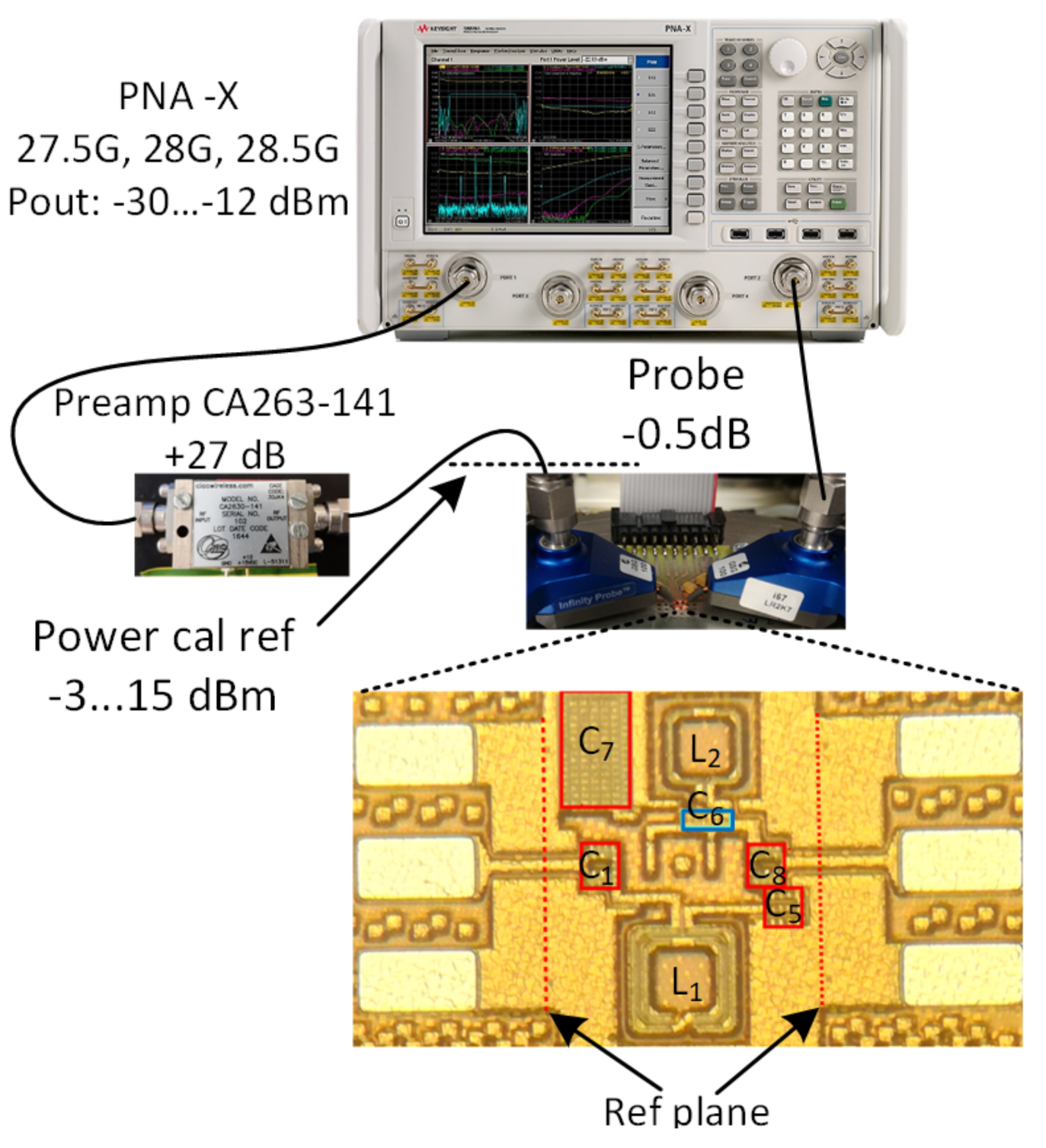

2. Stacked Power Amplifiers

3. Measurement Setup

4. Experimental Results

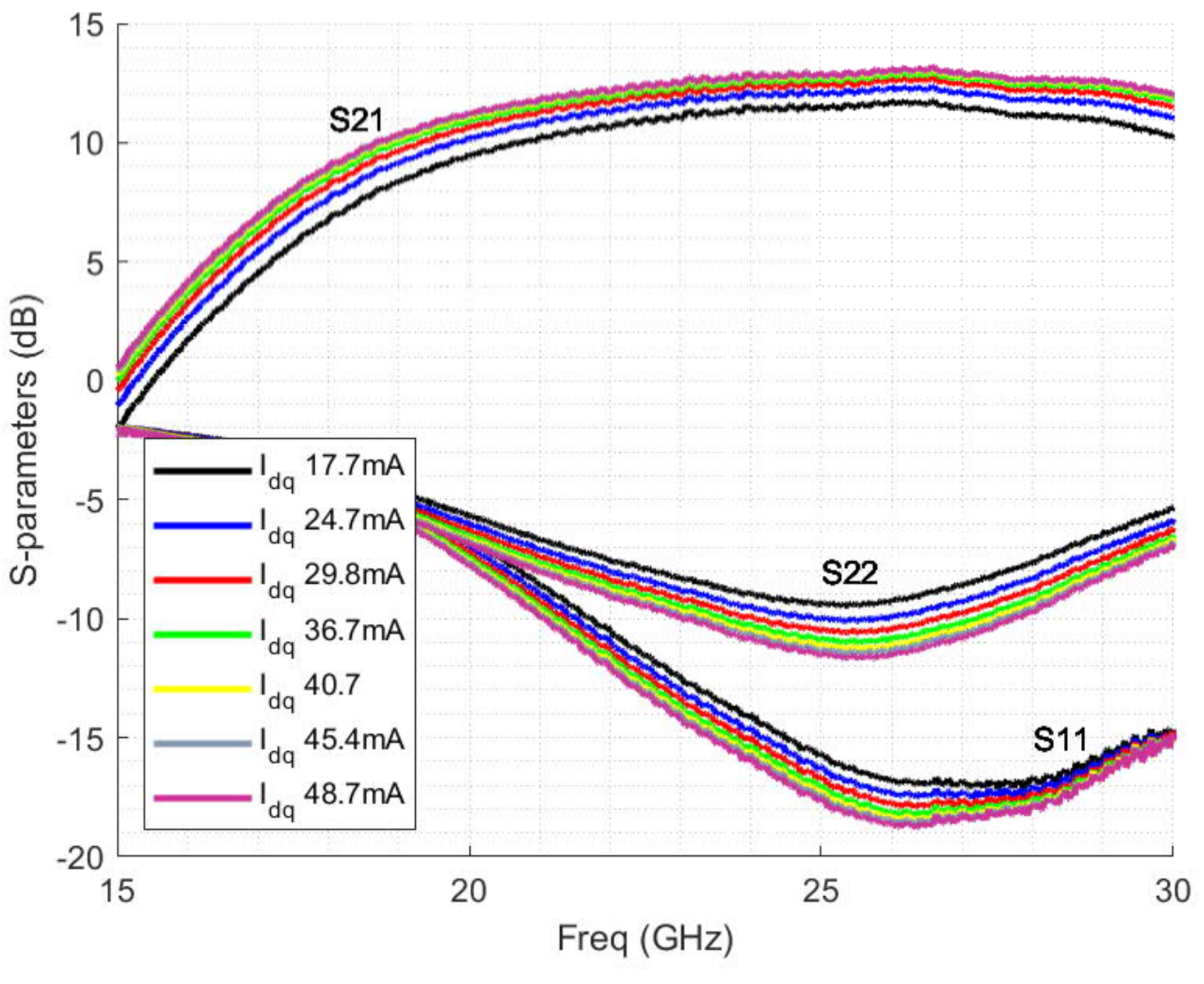

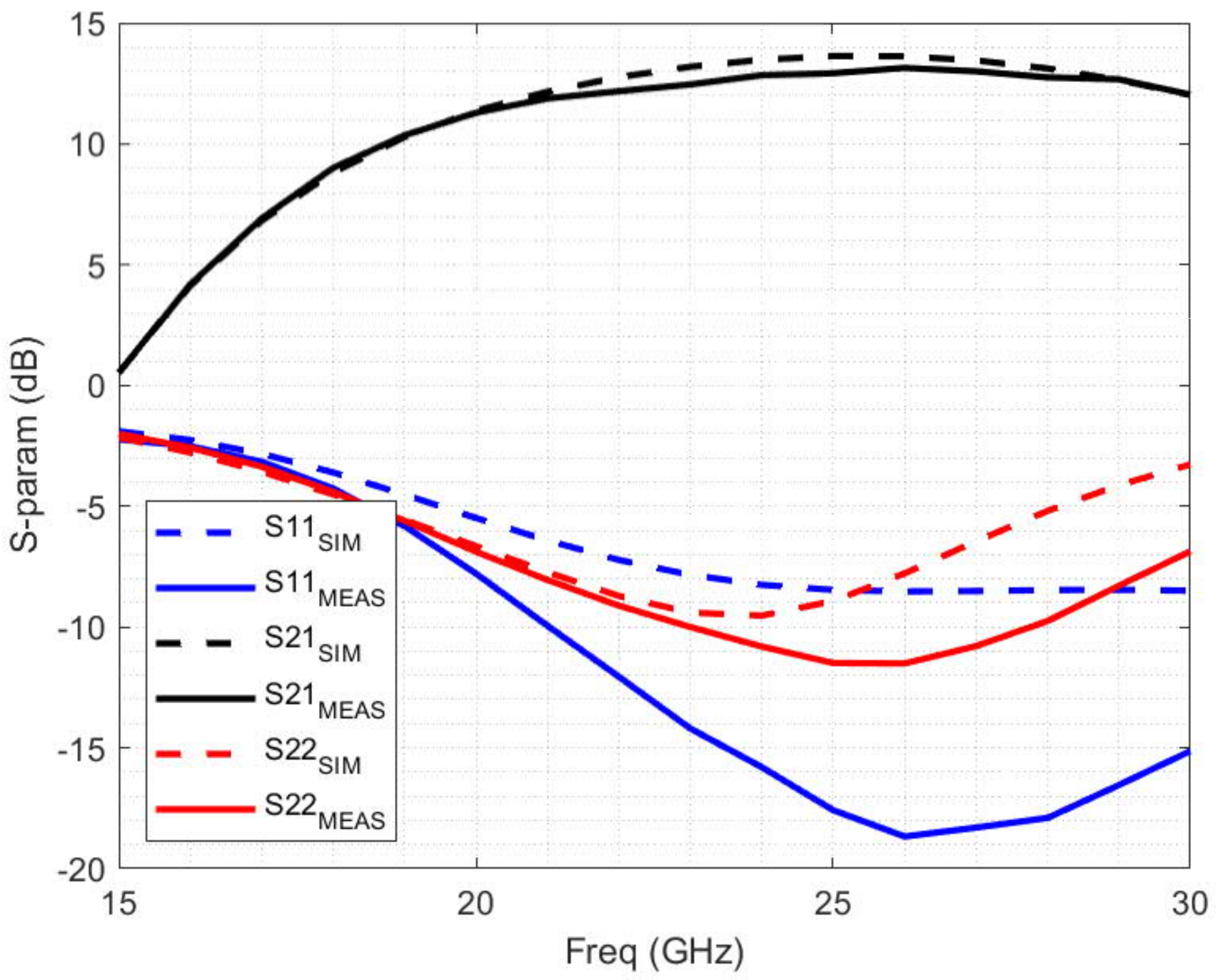

4.1. S-Parameter Measurements

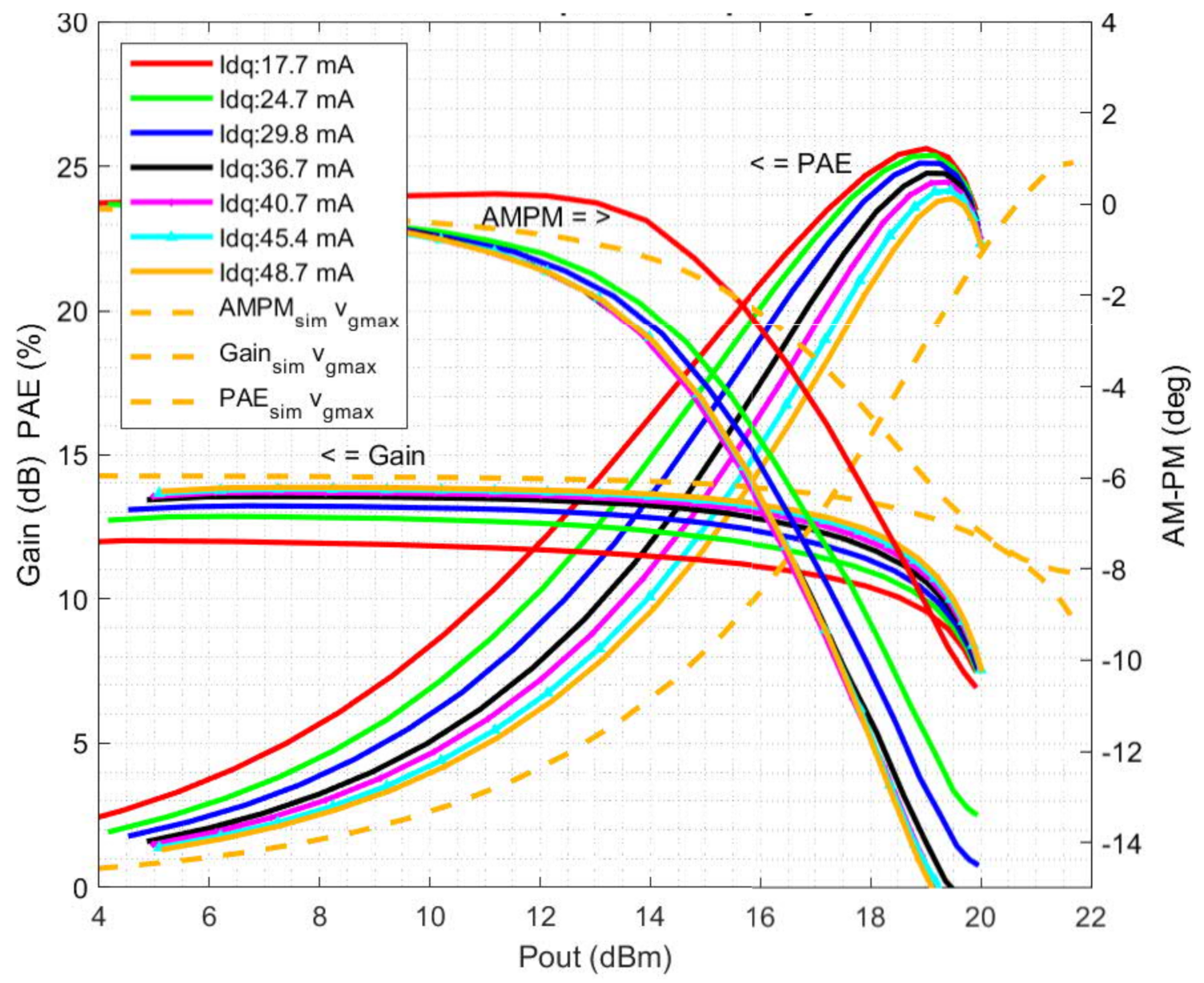

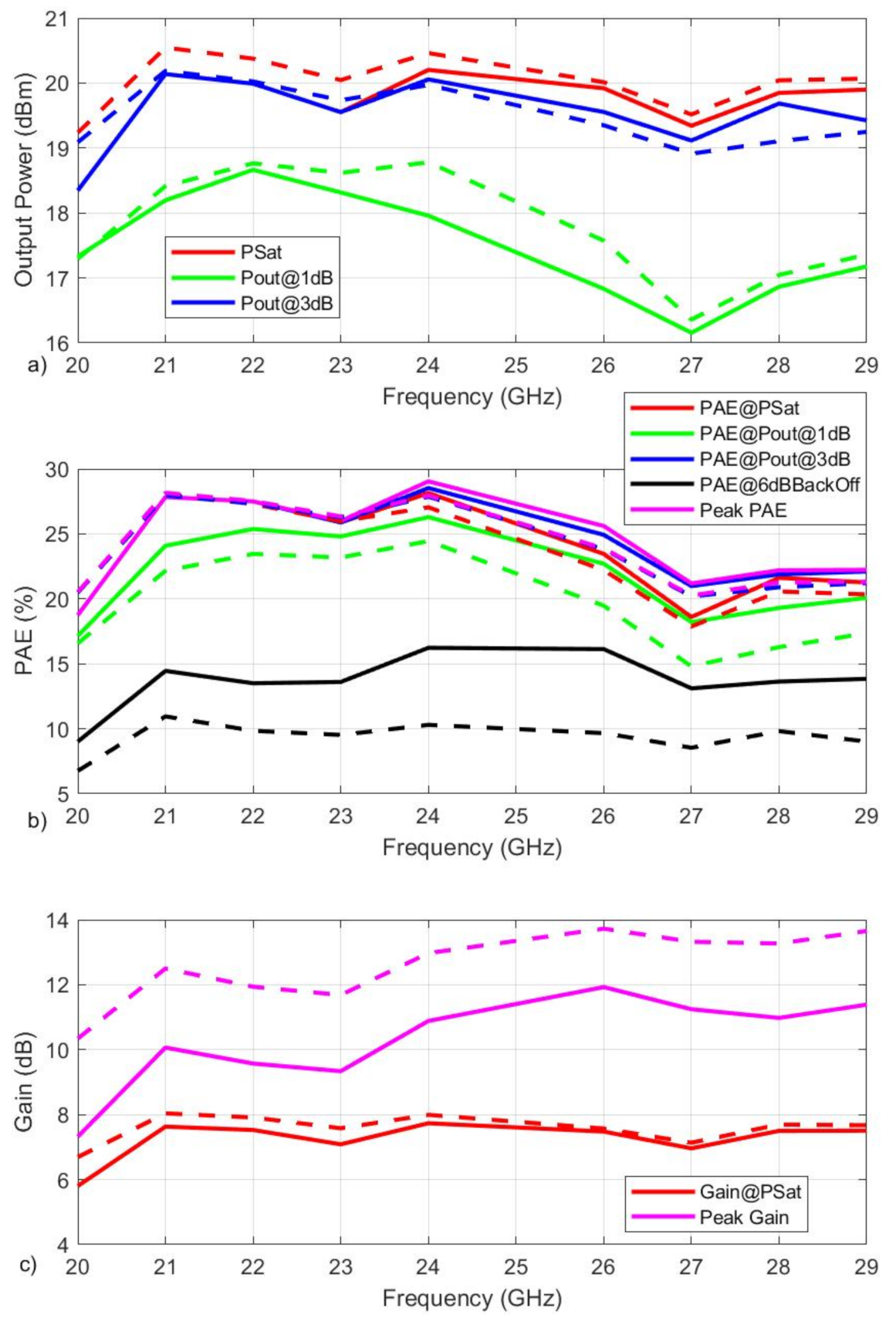

4.2. Single-Tone Measurements

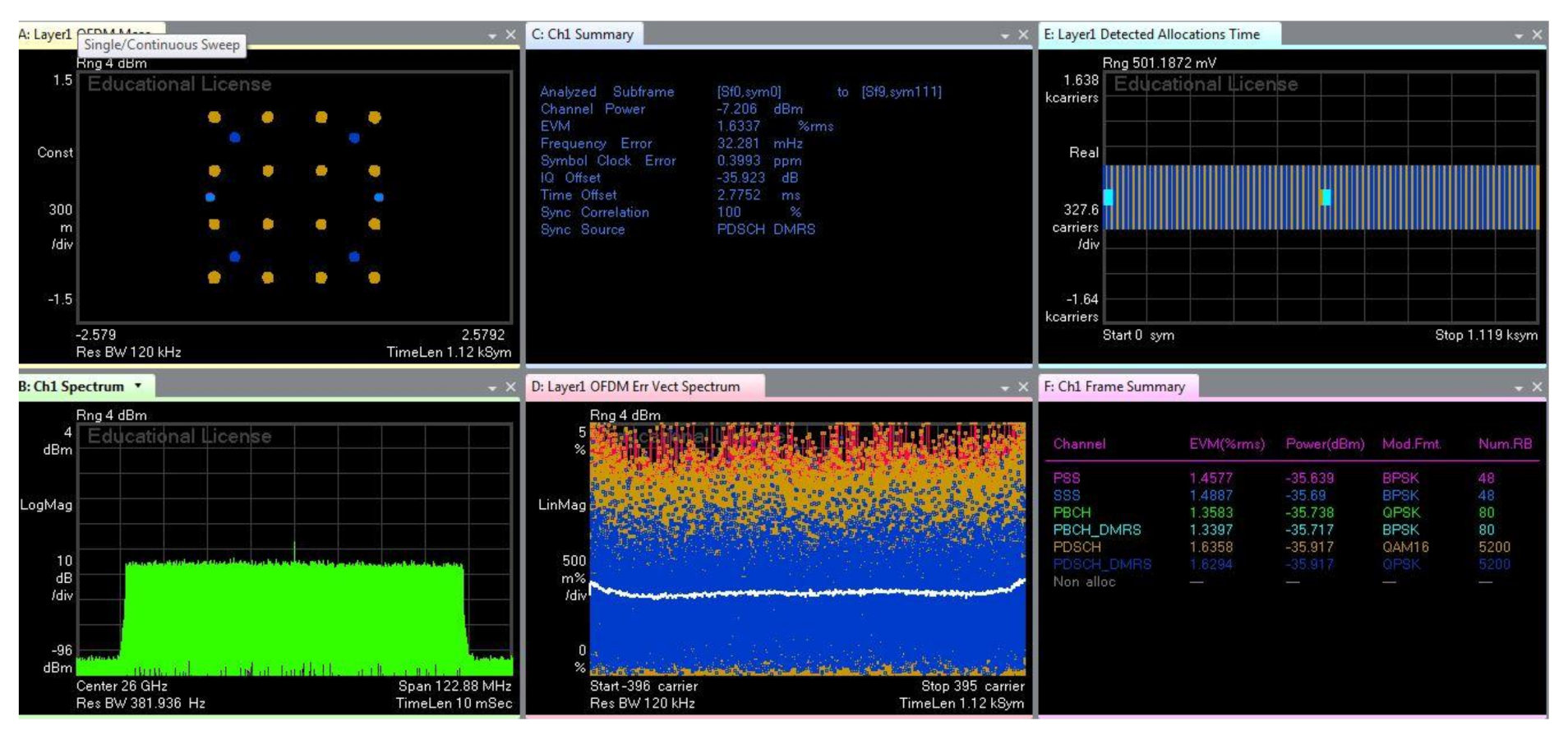

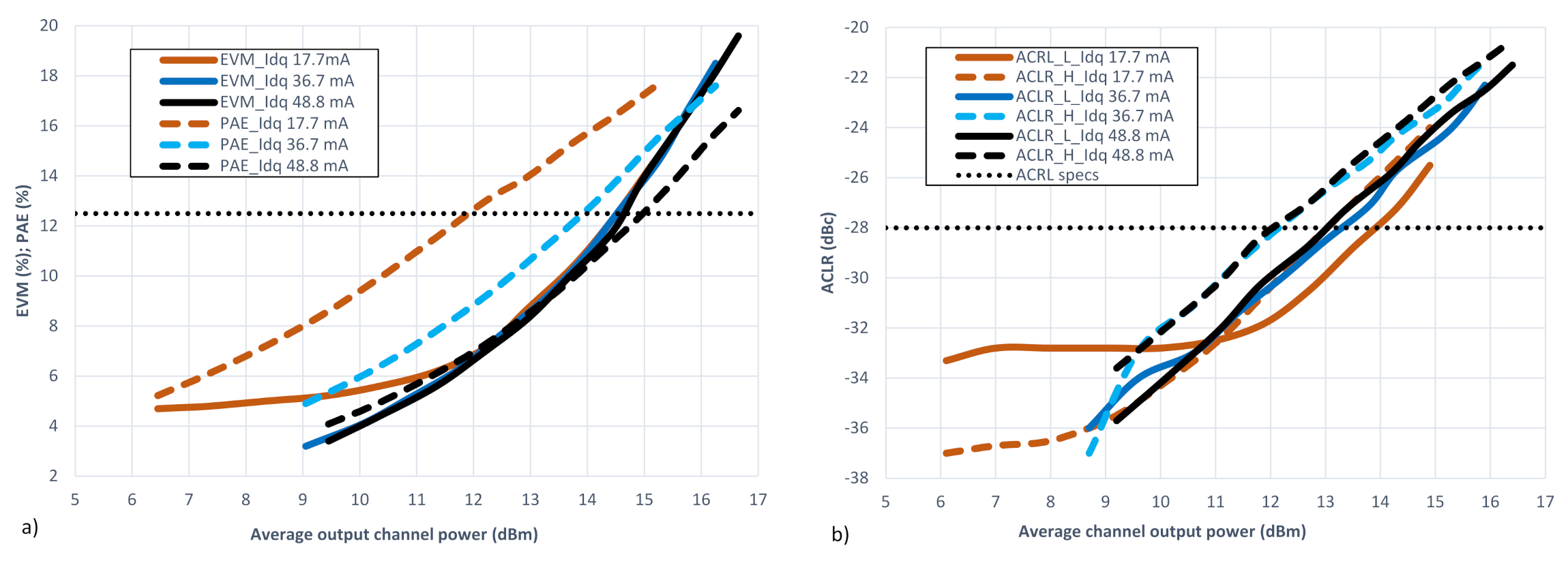

4.3. Measurements with Modulated Signal

4.4. Comparison of the Measured Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Andrews, J.G.; Buzzi, S.; Choi, W.; Hanly, S.V.; Lozano, A.; Soong, A.C.K.; Zhang, J.C. What Will 5G Be? IEEE J. Sel. Areas Commun. 2014, 32, 1065–1082. [Google Scholar] [CrossRef]

- 3GPP. NR; User Equipment (UE) Radio Transmission and Reception Part 2: Range 2 Standalone (Release 15). Technical Specification (TS) 38.101, 3rd Generation Partnership Project (3GPP). Version 15.2.0. 2018. Available online: https://www.3gpp.org/specifications (accessed on 13 July 2021).

- Rappaport, T.S.; Xing, Y.; Kanhere, O.; Ju, S.; Madanayake, A.; Alkhateeb, A.; Trichopoulos, G.C. Wireless Communications and Applications Above 100 GHz: Opportunities and Challenges for 6G and Beyond. IEEE Access 2019, 7, 78729–78757. [Google Scholar] [CrossRef]

- Pärssinen, A.; Alouini, M.; Berg, M.; Kuerner, T.; Kyosti, P.; Leinonen, M.E.; Matinmikko-Blue, M.; McCune, E.; Pfeiffer, U.; Wambacq, P. White Paper on RF Enabling 6G–Opportunities and Challenges from Technology to Spectrum; Technical Report; 6G Research Visions, No. 13; University of Oulu: Oulu, Finland, 2021. [Google Scholar]

- Han, S.; I, C.; Xu, Z.; Rowell, C. Large-scale antenna systems with hybrid analog and digital beamforming for millimeter wave 5G. IEEE Commun. Mag. 2015, 53, 186–194. [Google Scholar] [CrossRef]

- Roh, W.; Seol, J.; Park, J.; Lee, B.; Lee, J.; Kim, Y.; Cho, J.; Cheun, K.; Aryanfar, F. Millimeter-wave beamforming as an enabling technology for 5G cellular communications: Theoretical feasibility and prototype results. IEEE Commun. Mag. 2014, 52, 106–113. [Google Scholar] [CrossRef]

- Heath, R.W.; González-Prelcic, N.; Rangan, S.; Roh, W.; Sayeed, A.M. An Overview of Signal Processing Techniques for Millimeter Wave MIMO Systems. IEEE J. Sel. Top. Signal Process. 2016, 10, 436–453. [Google Scholar] [CrossRef]

- Tuovinen, T.; Tervo, N.; Pärssinen, A. Analyzing 5G RF System Performance and Relation to Link Budget for Directive MIMO. IEEE Trans. Antennas Propag. 2017, 65, 6636–6645. [Google Scholar] [CrossRef]

- Shakib, S.; Park, H.; Dunworth, J.; Aparin, V.; Entesari, K. 20.6 A 28 GHz efficient linear power amplifier for 5G phased arrays in 28nm bulk CMOS. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 352–353. [Google Scholar] [CrossRef]

- Li, C.; Wang, M.; Chi, T.; Kumar, A.; Boenke, M.; Cahoon, N.; Bandyopadhyay, A.; Joseph, A.; Wang, H. A high-efficiency 5G K/Ka-band stacked power amplifier in 45 nm CMOS SOI process supporting 9 Gb/s 64-QAM modulation with 22.4% average PAE. In Proceedings of the 2017 Texas Symposium on Wireless and Microwave Circuits and Systems (WMCS), Waco, TX, USA, 30–31 March 2017; pp. 1–4. [Google Scholar] [CrossRef]

- Zhang, Y.; Reynaert, P. A high-efficiency linear power amplifier for 28 GHz mobile communications in 40nm CMOS. In Proceedings of the 2017 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Honolulu, HI, USA, 4–6 June 2017; pp. 33–36. [Google Scholar] [CrossRef]

- Vigilante, M.; Reynaert, P. A Wideband Class-AB Power Amplifier With 29–57-GHz AM–PM Compensation in 0.9-V 28-nm Bulk CMOS. IEEE J. Solid-State Circuits 2018, 53, 1288–1301. [Google Scholar] [CrossRef]

- Ong, S.N.; Lehmann, S.; Chow, W.; Zhang, C.; Schippel, C.; Chan, L.H.K.; Andee, Y.; Hauschildt, M.; Tan, K.; Watts, J.; et al. A 22nm FDSOI Technology Optimized for RF/mmWave Applications. In Proceedings of the 2018 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Philadelphia, PA, USA, 10–12 June 2018; pp. 72–75. [Google Scholar] [CrossRef]

- Aikio, J.; Hietanen, M.; Tervo, N.; Rahkonen, T.; Pärssinen, A. Ka-Band 3-Stack Power Amplifier with 18.8 dBm Psat and 23.4% PAE Using 22nm CMOS FDSOI Technology. In Proceedings of the 2019 IEEE Topical Conference on RF/Microwave Power Amplifiers for Radio and Wireless Applications (PAWR), Orlando, FL, USA, 20–23 January 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Manente, D.; Padovan, F.; Seebacher, D.; Bassi, M.; Bevilacqua, A. A 28-GHz Stacked Power Amplifier with 20.7-dBm Output P1dB in 28-nm Bulk CMOS. IEEE Solid-State Circuits Lett. 2020, 3, 170–173. [Google Scholar] [CrossRef]

- Asbeck, P.M.; Rostomyan, N.; Özen, M.; Rabet, B.; Jayamon, J.A. Power Amplifiers for mm-Wave 5G Applications: Technology Comparisons and CMOS-SOI Demonstration Circuits. IEEE Trans. Microw. Theory Tech. 2019, 67, 3099–3109. [Google Scholar] [CrossRef]

- 3GPP. Base Station (BS) Radio Transmission and Reception. Technical Specification (TS) 38.104, 3rd Generation Partnership Project (3GPP). 2021. Available online: https://www.3gpp.org/ftp/Specs/archive/38_series/38.104/38104-h20.zip (accessed on 13 July 2021).

- Tervo, N.; Khan, B.; Kursu, O.; Aikio, J.P.; Jokinen, M.; Leinonen, M.E.; Juntti, M.; Rahkonen, T.; Pärssinen, A. Digital Predistortion of Phased-Array Transmitter With Shared Feedback and Far-Field Calibration. IEEE Trans. Microw. Theory Tech. 2021, 69, 1000–1015. [Google Scholar] [CrossRef]

- Aikio, J.P.; Sethi, A.; Hietanen, M.; Rahkonen, T.; Pärssinen, A. Ka-Band 4-Stack 45 nm CMOS SOI Power Amplifier Supporting 3GPP New Radio FR2 band n258. In Proceedings of the 2019 SBMO/IEEE MTT-S International Microwave and Optoelectronics Conference (IMOC), Aveiro, Portugal, 10–14 November 2019; pp. 1–4. [Google Scholar]

- Dabag, H.; Hanafi, B.; Golcuk, F.; Agah, A.; Buckwalter, J.F.; Asbeck, P.M. Analysis and Design of Stacked-FET Millimeter-Wave Power Amplifiers. IEEE Trans. Microw. Theory Tech. 2013, 61, 1543–1556. [Google Scholar] [CrossRef]

- Montaseri, M.H.; Aikio, J.; Rahkonen, T.; Pärssinen, A. Optimum Number of Transistors in Stacked CMOS Millimeter-Wave Power Amplifiers. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–4. [Google Scholar] [CrossRef] [Green Version]

- Jayamon, J.A.; Buckwalter, J.F.; Asbeck, P.M. Multigate-Cell Stacked FET Design for Millimeter-Wave CMOS Power Amplifiers. IEEE J. Solid-State Circuits 2016, 51, 2027–2039. [Google Scholar] [CrossRef]

- Chen, T.; Zhang, C.; Arfaoui, W.; Bellaouar, A.; Embabi, S.; Bossu, G.; Siddabathula, M.; Chew, K.W.J.; Ong, S.N.; Mantravadi, M.; et al. Excellent 22FDX Hot-Carrier Reliability for PA Applications. In Proceedings of the 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2–4 June 2019; pp. 27–30. [Google Scholar] [CrossRef]

- Park, B.; Jin, S.; Jeong, D.; Kim, J.; Cho, Y.; Moon, K.; Kim, B. Highly Linear mm-Wave CMOS Power Amplifier. IEEE Trans. Microw. Theory Tech. 2016, 64, 4535–4544. [Google Scholar] [CrossRef]

- Kim, B.; Moon, K.; Jeong, D.; Kim, S.; Shin, J. Linear PA at mm-Wave band for 5G application. In Proceedings of the 2017 10th Global Symposium on Millimeter-Waves, Hong Kong, China, 24–26 May 2017; pp. 80–82. [Google Scholar] [CrossRef]

- Thomas, D.; Rostomyan, N.; Asbeck, P. A 45% PAE pMOS Power Amplifier for 28 GHz Applications in 45 nm SOI. In Proceedings of the 2018 IEEE 61st International Midwest Symposium on Circuits and Systems (MWSCAS), Windsor, ON, Canada, 5–8 August 2018; pp. 680–683. [Google Scholar] [CrossRef]

- Xia, J.; Fang, X.; Ayed, A.B.; Boumaiza, S. Millimeter Wave SOI-CMOS Power Amplifier With Enhanced AM-PM Characteristic. IEEE Access 2020, 8, 8861–8875. [Google Scholar] [CrossRef]

| Modulation Scheme | Required EVM (%) |

|---|---|

| QPSK | 17.5 |

| 16QAM | 12.5 |

| 64QAM | 8 |

| 256QAM | 3.5 |

| Carrier BW (MHz) | FR2 Frequency Range | ACPR Limit |

|---|---|---|

| 50, 100, 200, 400 | 24.25–33.4 GHz | 28 dB |

| 50, 100, 200, 400 | 37–52.6 GHz | 26 dB |

| This Work | [24,25] | |||||||

|---|---|---|---|---|---|---|---|---|

| Freq. (GHz) | 24 | 29 | 24 | 28 | 28 | 28 | 30 | 27 |

| Design | 4-stk | 4-stk | 3-stk | Diff 3-stk | Diff 2-stk | Diff 2-stk | 2-stak pMOS | Diff CS |

| Tech. | 45 nm SOI | 45 nm SOI | 45 nm SOI | 22 nm SOI | 22 nm SOI | 28 nm CMOS | 45 nm SOI | 45 nm SOI |

| VDD (V) | 4.6 | 5 | 2.9 | - | 1.4 | 2.2 | 2.4 | 1.2 |

| Psat (dBm) | 20.5 | 24.8 | 16.2 | 21 | - | 19.8 | 19.5 | 16.6 |

| P1dB (dBm) | 18.8 | - | 14.2 | - | 15.9 | 18.6 | - | 13.9 |

| Gain (dB) | 13.2 | 13 | 13.1 | 12 | 12.4 | 13.6 | 10 | 20 |

| Peak PAE (%) | 29 | 29 | 41.5 | 30 4 | 41 | 43.3 | 46.7 | 34.2 |

| Area mm2 | 0.225 | 0.3 | 0.4125 | - | - | 0.28 | 0.18 | 0.1 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Aikio, J.P.; Sethi, A.; Hietanen, M.; Rusanen, J.; Rahkonen, T.; Pärssinen, A. Ka-Band Stacked Power Amplifier Supporting 3GPP New Radio FR2 Band n258 Implemented Using 45 nm CMOS SOI. Appl. Sci. 2021, 11, 6708. https://doi.org/10.3390/app11156708

Aikio JP, Sethi A, Hietanen M, Rusanen J, Rahkonen T, Pärssinen A. Ka-Band Stacked Power Amplifier Supporting 3GPP New Radio FR2 Band n258 Implemented Using 45 nm CMOS SOI. Applied Sciences. 2021; 11(15):6708. https://doi.org/10.3390/app11156708

Chicago/Turabian StyleAikio, Janne P., Alok Sethi, Mikko Hietanen, Jere Rusanen, Timo Rahkonen, and Aarno Pärssinen. 2021. "Ka-Band Stacked Power Amplifier Supporting 3GPP New Radio FR2 Band n258 Implemented Using 45 nm CMOS SOI" Applied Sciences 11, no. 15: 6708. https://doi.org/10.3390/app11156708

APA StyleAikio, J. P., Sethi, A., Hietanen, M., Rusanen, J., Rahkonen, T., & Pärssinen, A. (2021). Ka-Band Stacked Power Amplifier Supporting 3GPP New Radio FR2 Band n258 Implemented Using 45 nm CMOS SOI. Applied Sciences, 11(15), 6708. https://doi.org/10.3390/app11156708