XOR Multiplexing Technique for Nanocomputers

Abstract

1. Introduction

2. Error Distributions in the XOR Multiplexing System

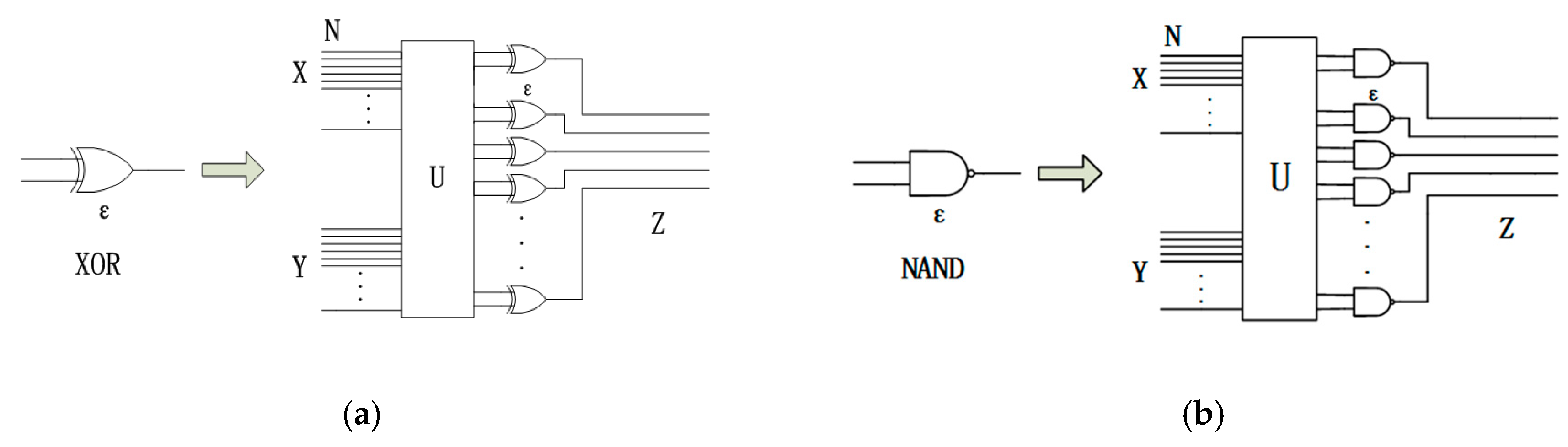

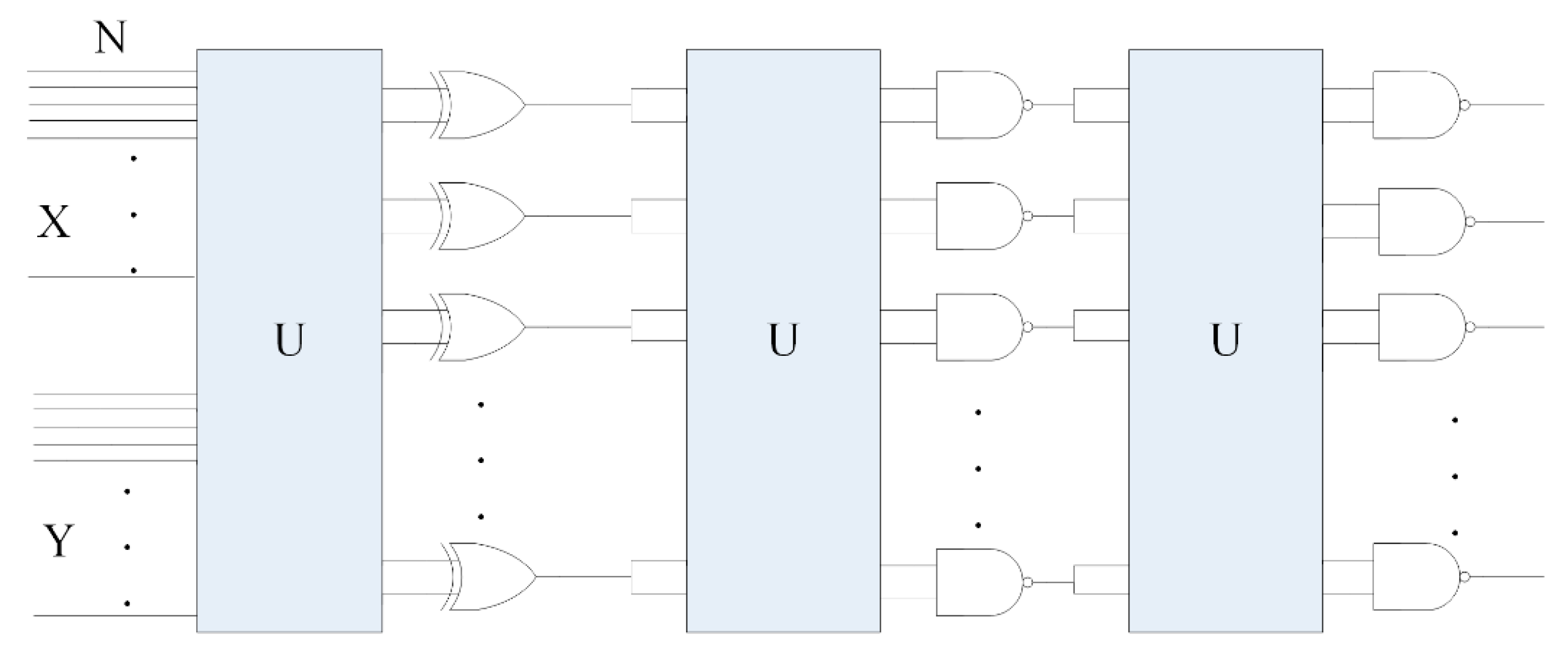

2.1. An XOR Multiplexing Unit

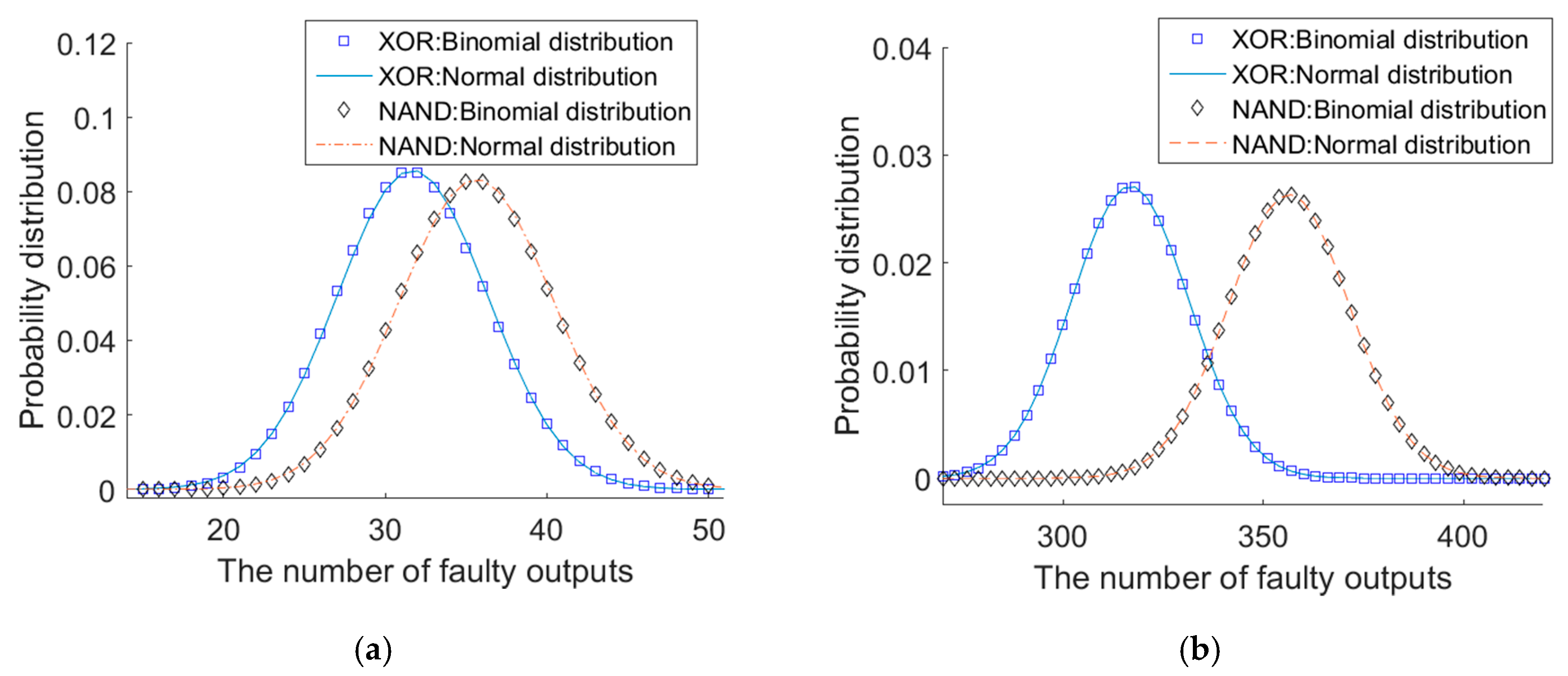

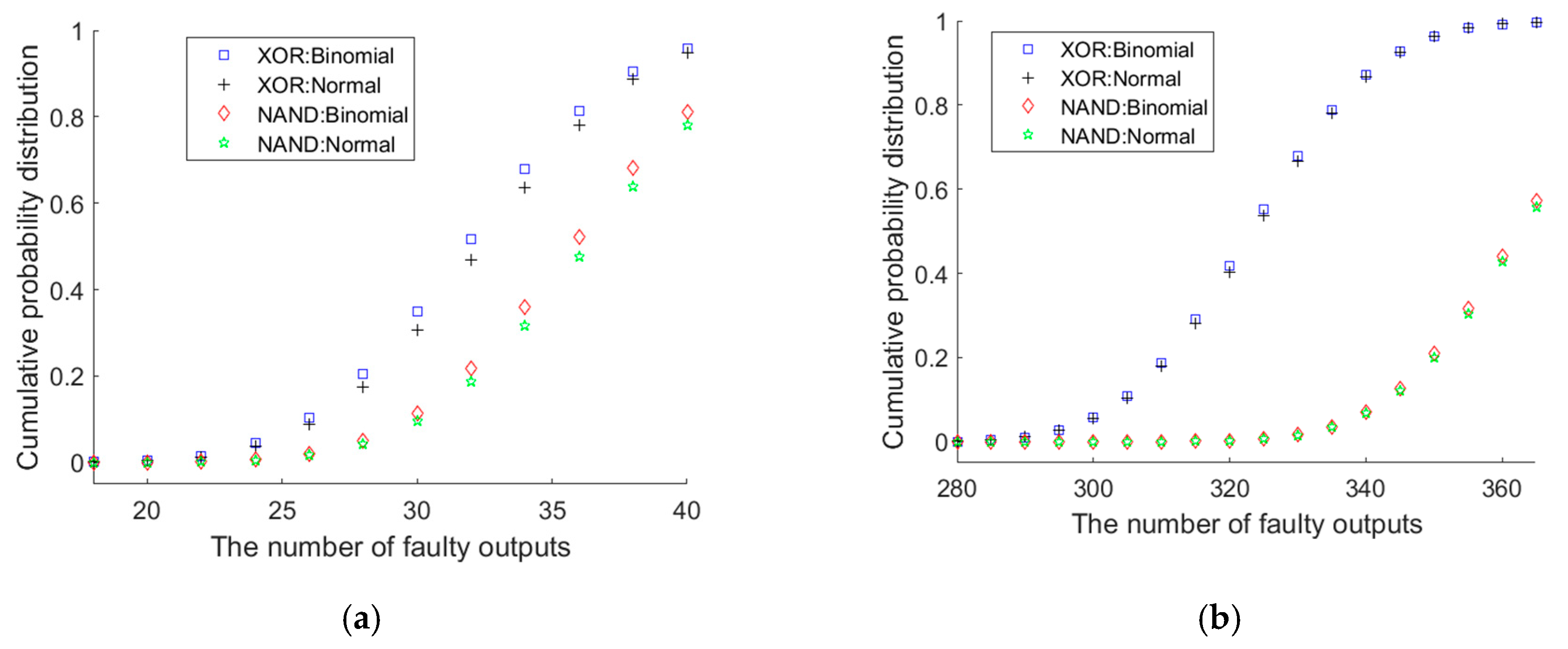

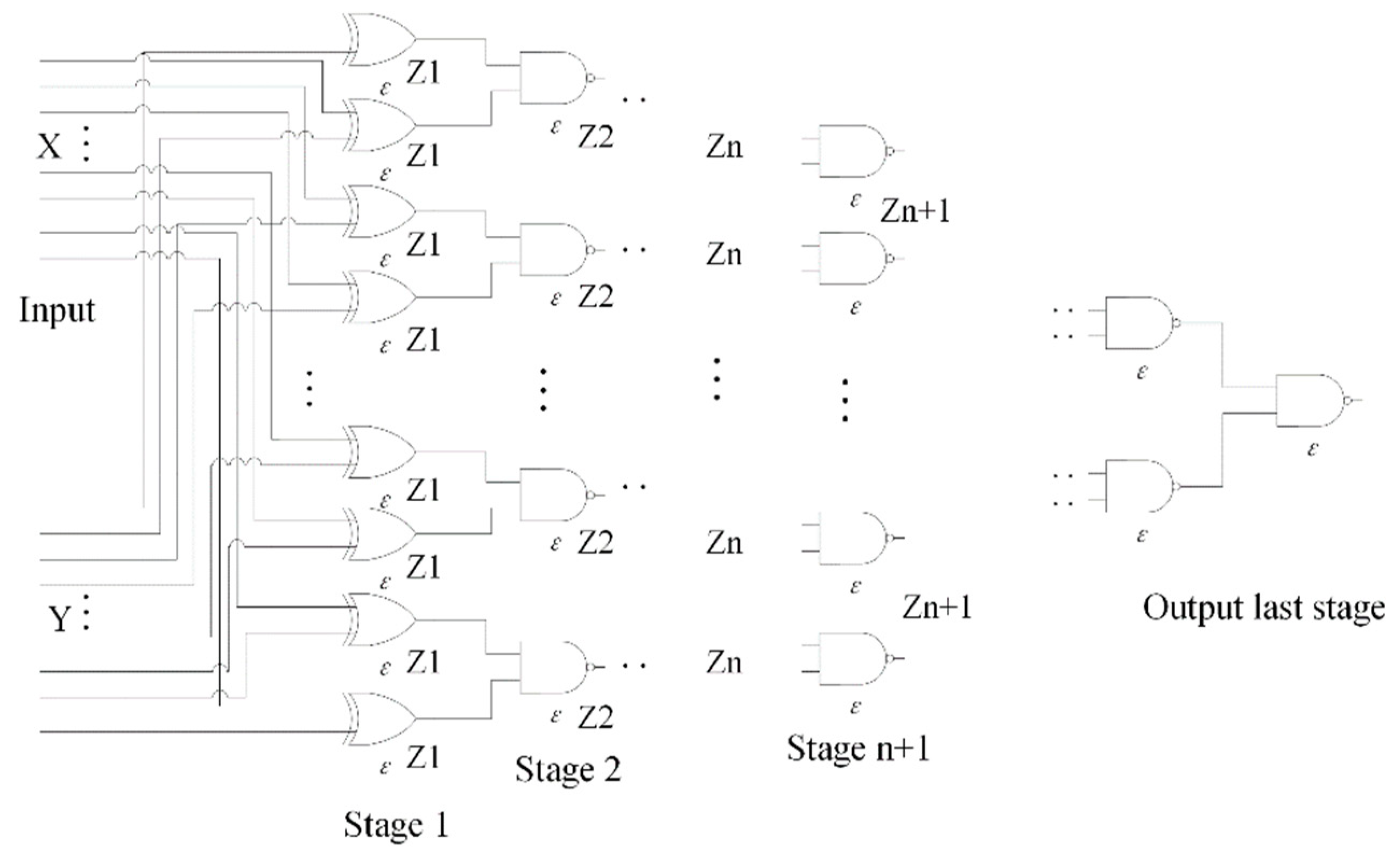

2.2. Error Distributions in the XOR Multiplexing Unit and the NAND Multiplexing Unit

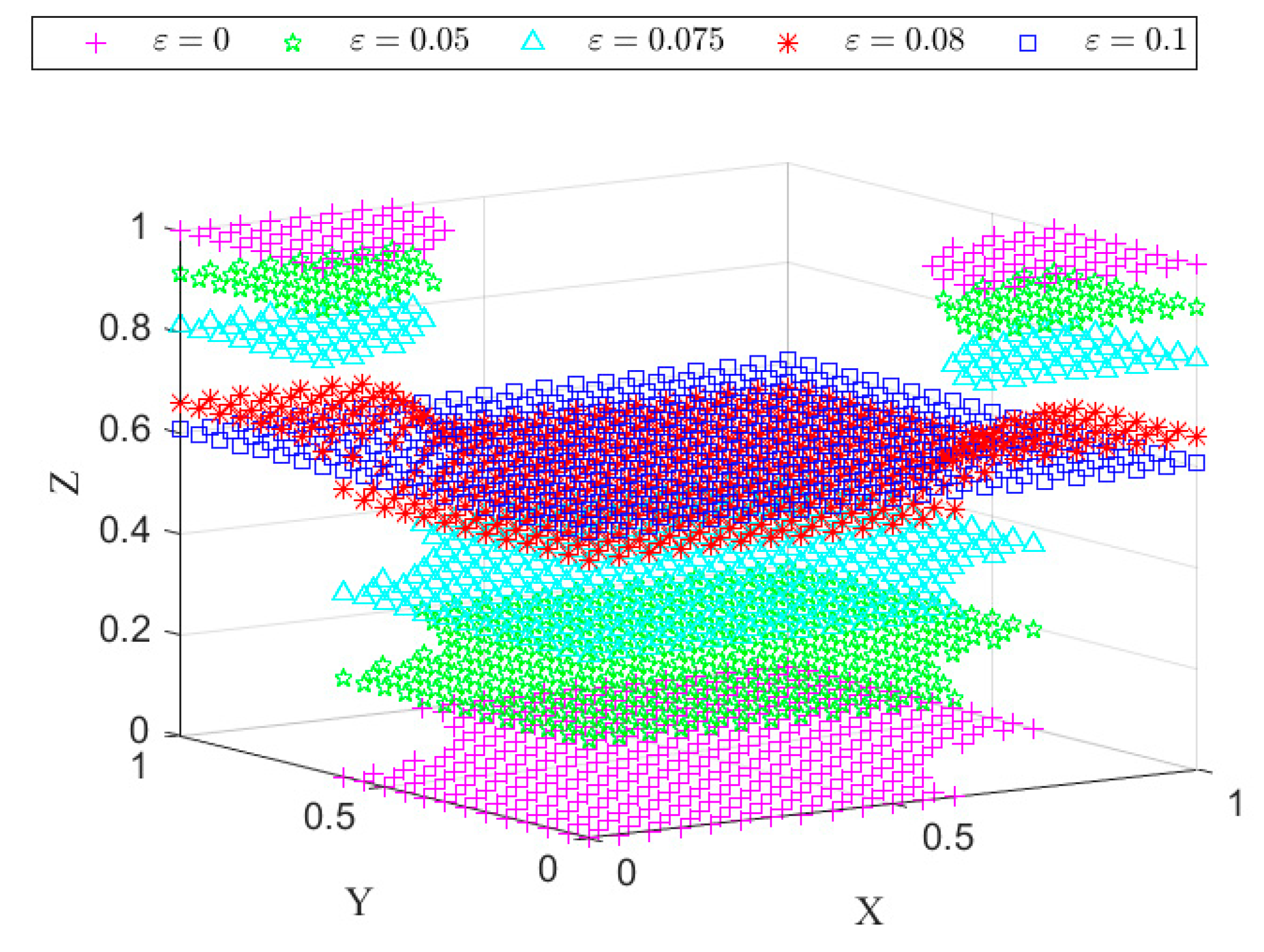

2.3. Error Distributions in the XOR Multiplexing System and the NAND Multiplexing System

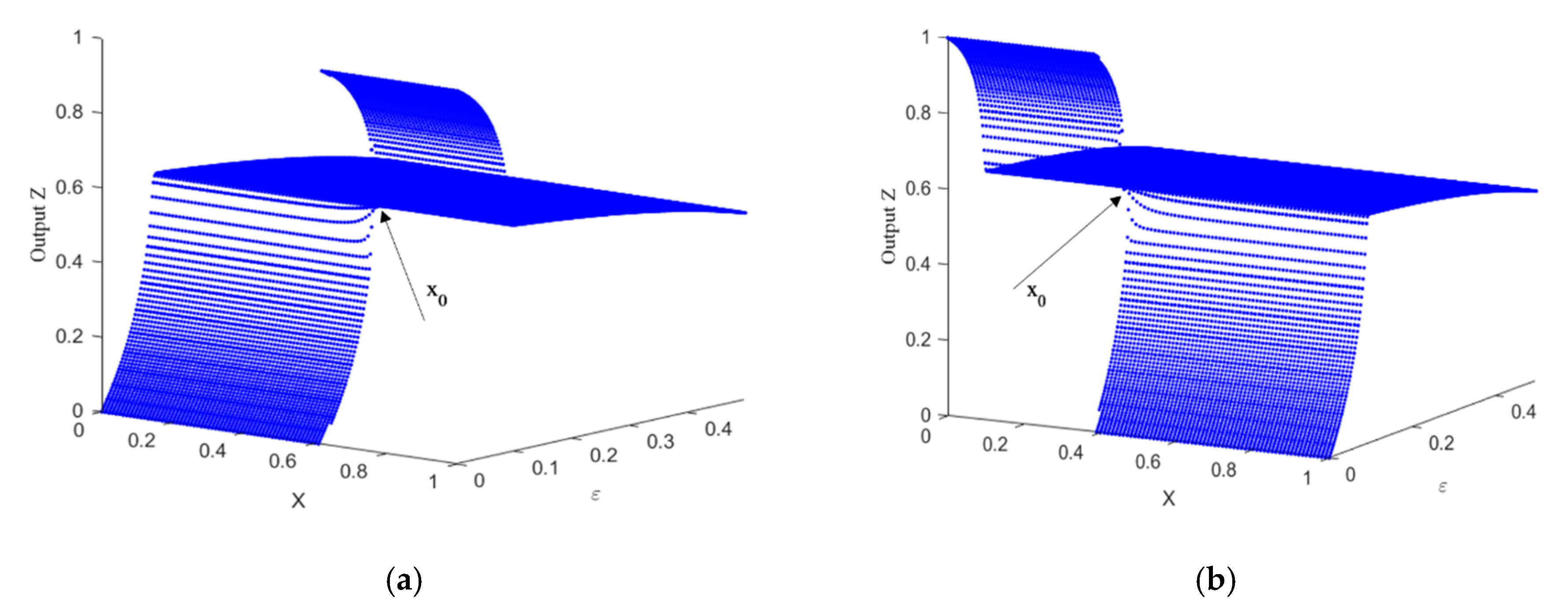

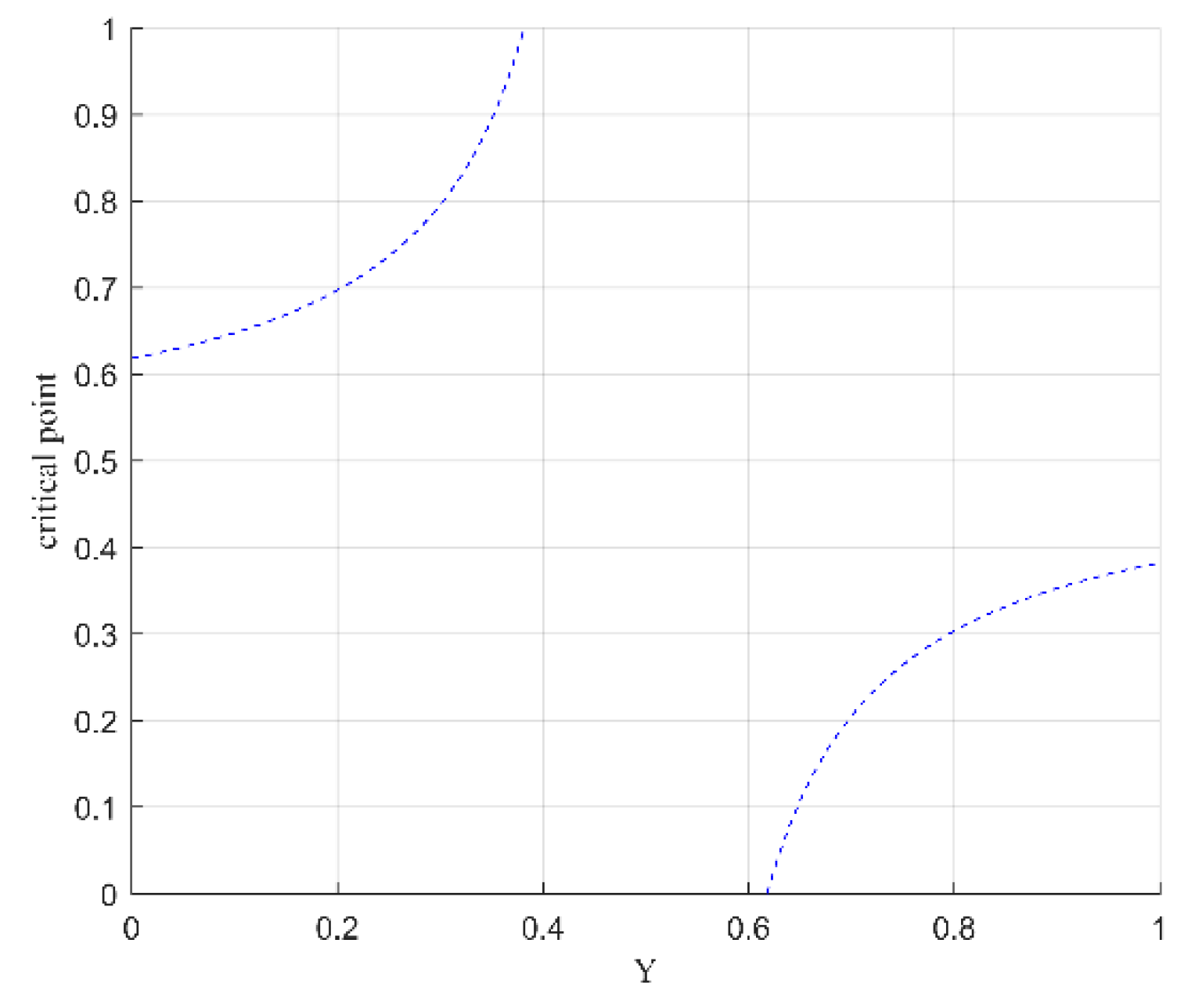

3. Bifurcation Analysis of the XOR Multiplexing System

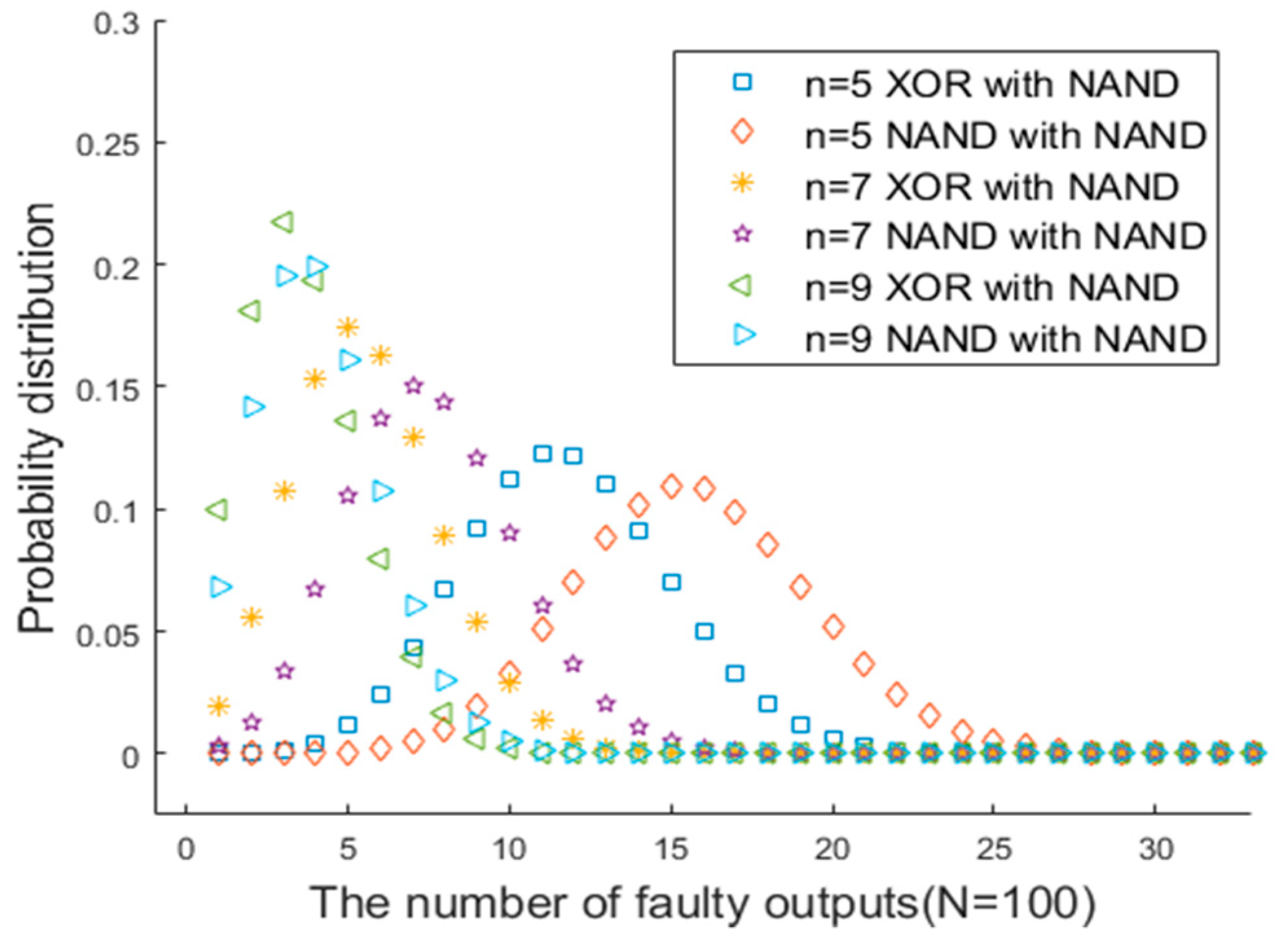

4. Fault-Tolerant Ability Analysis

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Tseng, L.; Wu, Y.; Pan, H.; Aloqaily, M.; Boukerche, A. Reliable Broadcast in Networks with Trusted Nodes. In Proceedings of the 2019 IEEE Global Communications Conference (GLOBECOM), Waikoloa, HI, USA, 9–13 December 2019; pp. 1–6. [Google Scholar]

- Ridhawi, I.A.; Otoum, S.; Aloqaily, M.; Jararweh, Y.; Baker, T. Providing secure and reliable communication for next generation networks in smart cities. Sustain. Cities Soc. 2020, 56, 102080. [Google Scholar] [CrossRef]

- Acosta Calderon, C.A.; Mohan, R.E.; Hu, L.Y.; Zhou, C.J.; Hu, H.S. Generating human-like soccer primitives from human data. Robot. Auton. Syst. 2009, 57, 860–869. [Google Scholar] [CrossRef]

- Zheng, G.; Zhang, H.T.; Zhou, K.M.; Hu, H.S. Using Machine Learning Techniques to Optimize Fall Detection Algorithms in Smart Wristband. In Proceedings of the 2019 25th International Conference on Automation and Computing (ICAC), Lancaster, UK, 5–7 September 2019; pp. 1–6. [Google Scholar] [CrossRef]

- Sakhnini, J.; Karimipour, H.; Dehghantanha, A.; Parizi, R.M.; Srivastava, G. Security aspects of Internet of Things aided smart grids: A bibliometric survey. Internet Things 2019, 100111. [Google Scholar] [CrossRef]

- Sharma, B.; Srivastava, G.; Lin Jerry, C.-W. A bidirectional congestion control transport protocol for the internet of drones. Comput. Commun. 2020, 153, 102–116. [Google Scholar] [CrossRef]

- Ali, Z.; Hossain, M.S.; Muhammad, G.; Sangaiah, A.K. An intelligent healthcare system for detection and classification to discriminate vocal fold disorders. Future Gener. Comput. Syst. 2018, 85, 19–28. [Google Scholar] [CrossRef]

- Liu, C.F.; Zhao, Z.; Qu, W.Y.; Tie, Q.; Sangaiah, A.K. A distributed node deployment algorithm for underwater wireless sensor networks based on virtual forces. J. Syst. Archit. 2019, 97, 9–19. [Google Scholar] [CrossRef]

- Anjankar, S.C.; Kolte, M.T.; Pond, A.; Kolte, P.; Kumar, A.; Mankar, P.; Ambhore, K. FPGA based multiple fault tolerant and recoverable technique using triple modular redundancy (FRTMR). Procedia Comput. Sci. 2016, 79, 827–834. [Google Scholar] [CrossRef]

- Yao, R.; Chen, Q.; Li, Z.; Sun, Y. Multi-objective evolutionary design of selective triple modular redundancy systems against SEUs. Chin. J. Aeronaut. 2015, 28, 804–813. [Google Scholar] [CrossRef]

- Siozios, K.; Savidis, I.; Soudris, D. A framework for exploring alternative fault-tolerant schemes targeting 3-D reconfigurable architectures. In Proceedings of the 2016 International Conference on Embedded Computer Systems: Architectures, Modeling and Simulation, Agios Konstantinos, Greece, 18–21 July 2016; pp. 336–341. [Google Scholar] [CrossRef]

- Mukherjee, A.; Dhar, A.S. Choice of granularity for reliable circuit design using dynamic reconfiguration. Microelectron. Reliab. 2016, 63, 291–303. [Google Scholar] [CrossRef]

- Banerjee, S.; Rao, W. A local reconfiguration based scalable fault tolerant many-processor array. In Proceedings of the 22nd Asia and South Pacific Design Automation Conference (ASP-DAC), Chiba/Tokyo, Japan, 16–19 January 2017; pp. 432–437. [Google Scholar] [CrossRef]

- Qi, Y.; Gao, J.B.; Fortes, A.B. Markov chains and probabilistic computation-A general framework for multiplexed nanoelectronic systems. IEEE Trans. Nanotechnol. 2005, 4, 194–205. [Google Scholar] [CrossRef]

- Von Neumann, J. Probabilistic logics and the synthesis of reliable organisms from unreliable components. Autom. Stud. 1956, 34, 43–98. [Google Scholar]

- Voicu, G.R.; Cotofana, S.D. Towards heterogenous 3D-stacked reliable computing with von Neumann multiplexing. In Proceedings of the 2013 IEEE/ACM International Symposium on Nanoscale Architectures, Brooklyn, New York, NY, USA, 15–17 July 2013; pp. 122–127. [Google Scholar] [CrossRef]

- Gucwa, K. On simulation of multiplexed architecture for fault-tolerant nanoelectronic systems. In Proceedings of the 12th IEEE Conference on Nanotechnology, Birmingham, UK, 20–23 August 2012; Volume 7, pp. 1–4. [Google Scholar] [CrossRef]

- Beiu, V.; Ibrahim, W. Devices and input vectors are shaping von Neumann multiplexing. IEEE Trans. Nanotechnol. 2011, 10, 606–616. [Google Scholar] [CrossRef]

- Roy, S.; Beiu, V. Majority multiplexing-economical redundant fault-tolerant designs for nanoarchitectures. IEEE Trans. Nanotechnol. 2005, 4, 441–451. [Google Scholar] [CrossRef]

- Bhaduri, D.; Shukla, S.K. Reliability evaluation of von Neumann multiplexing based defect-tolerant majority circuits. In Proceedings of the 4th IEEE Conference on Nanotechnology, Munich, Germany, 16–19 August 2004; pp. 599–601. [Google Scholar] [CrossRef]

- Bhaduri, D.; Shukla, S.K.; Graham, P.; Gokhale, M. Comparing reliability-redundancy tradeoffs for two von Neumann multiplexing architectures. IEEE Trans. Nanotechnol. 2007, 6, 265–279. [Google Scholar] [CrossRef]

- Han, J.; Jonker, P. A system architecture solution for unreliable nanoelectronic devices. IEEE Trans. Nanotechnol. 2002, 1, 201–208. [Google Scholar] [CrossRef]

- Qi, Y.; Gao, J.B. Bifurcations and fundamental error bounds for fault tolerant computations. IEEE Trans. Nanotechnol. 2005, 4, 395–402. [Google Scholar] [CrossRef]

- Han, J.; Jonker, P. A defect- and fault-tolerant architecture for nanocomputers. Nanotechnology 2003, 14, 224–230. [Google Scholar] [CrossRef]

- Han, J. Fault-Tolerant Architectures for Nanoelectronic and Quantum Devices; Tsinghua University: Beijing, China, 2004. [Google Scholar]

- Ibrahim, W.; Beiu, V.; Beg, A. On NOR-2 von Neumann multiplexing. In Proceedings of the 2010 5th International Design and Test Workshop, Abu Dhabi, UAE, 14–15 December 2010; pp. 67–72. [Google Scholar] [CrossRef]

| Fixed Y | Critical Points |

|---|---|

| Y = 0 | 0.60760 |

| Y = 0.1 | 0.63450 |

| Y = 0.2 | 0.67933 |

| Y = 0.3 | 0.76900 |

| Y = 0.7 | 0.23100 |

| Y = 0.8 | 0.32067 |

| Y = 0.9 | 0.36550 |

| Y = 1 | 0.39240 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yu, L.; Diao, M.; Chen, X.; Cheng, X. XOR Multiplexing Technique for Nanocomputers. Appl. Sci. 2020, 10, 2825. https://doi.org/10.3390/app10082825

Yu L, Diao M, Chen X, Cheng X. XOR Multiplexing Technique for Nanocomputers. Applied Sciences. 2020; 10(8):2825. https://doi.org/10.3390/app10082825

Chicago/Turabian StyleYu, Lianhua, Ming Diao, Xiaobo Chen, and Xiaochun Cheng. 2020. "XOR Multiplexing Technique for Nanocomputers" Applied Sciences 10, no. 8: 2825. https://doi.org/10.3390/app10082825

APA StyleYu, L., Diao, M., Chen, X., & Cheng, X. (2020). XOR Multiplexing Technique for Nanocomputers. Applied Sciences, 10(8), 2825. https://doi.org/10.3390/app10082825