The Effect of Deep N+ Well on Single-Event Transient in 65 nm Triple-Well NMOSFET

Abstract

:1. Introduction

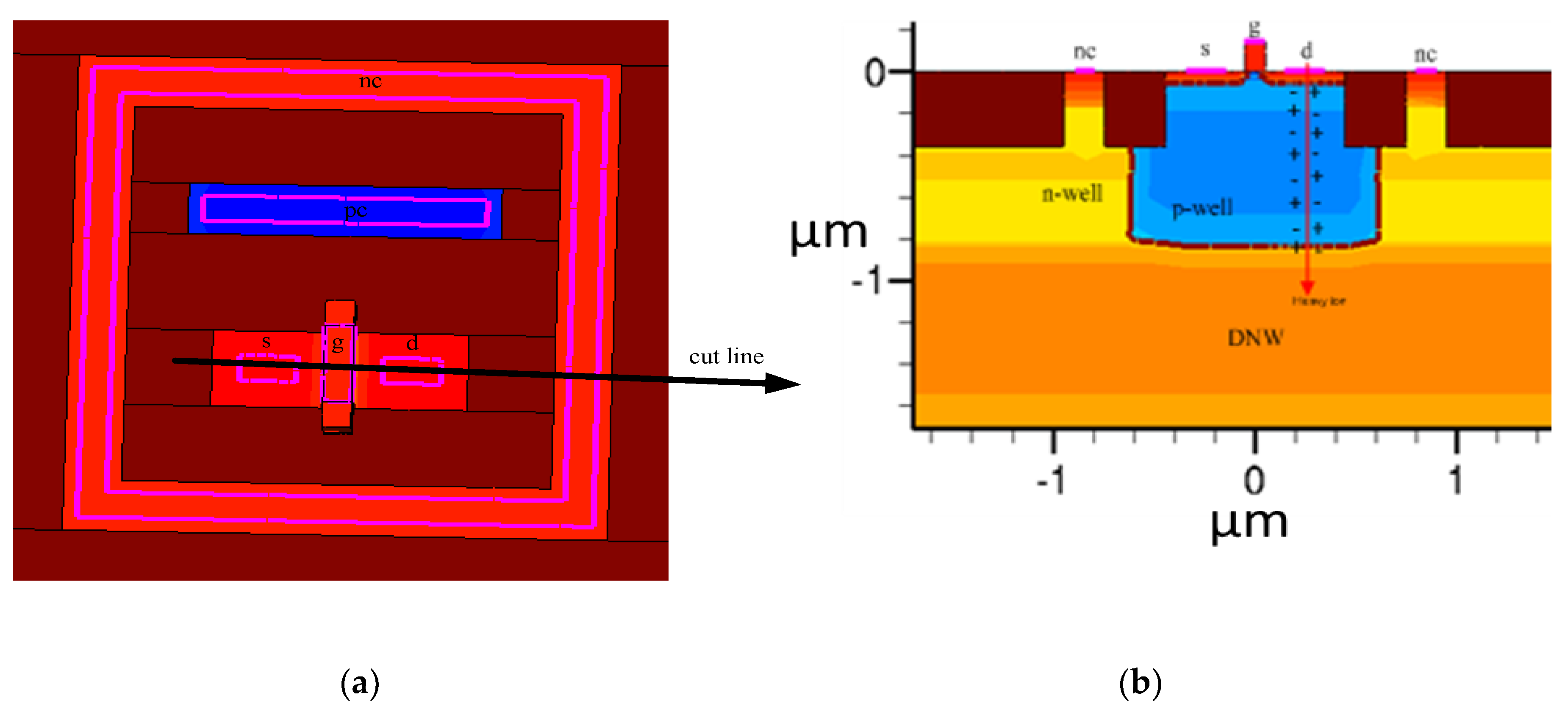

2. Device and Simulation Details

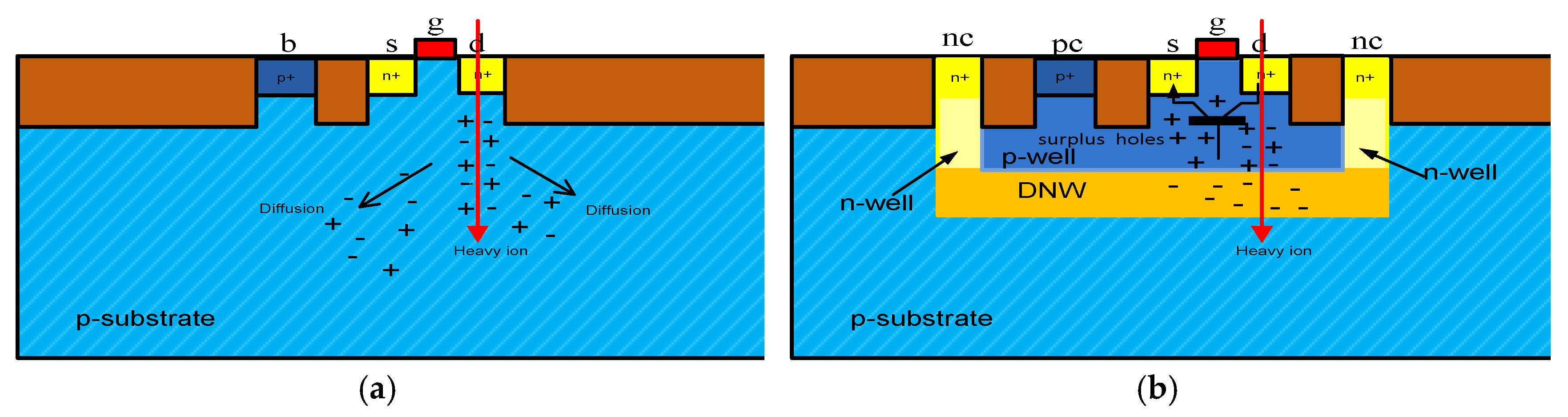

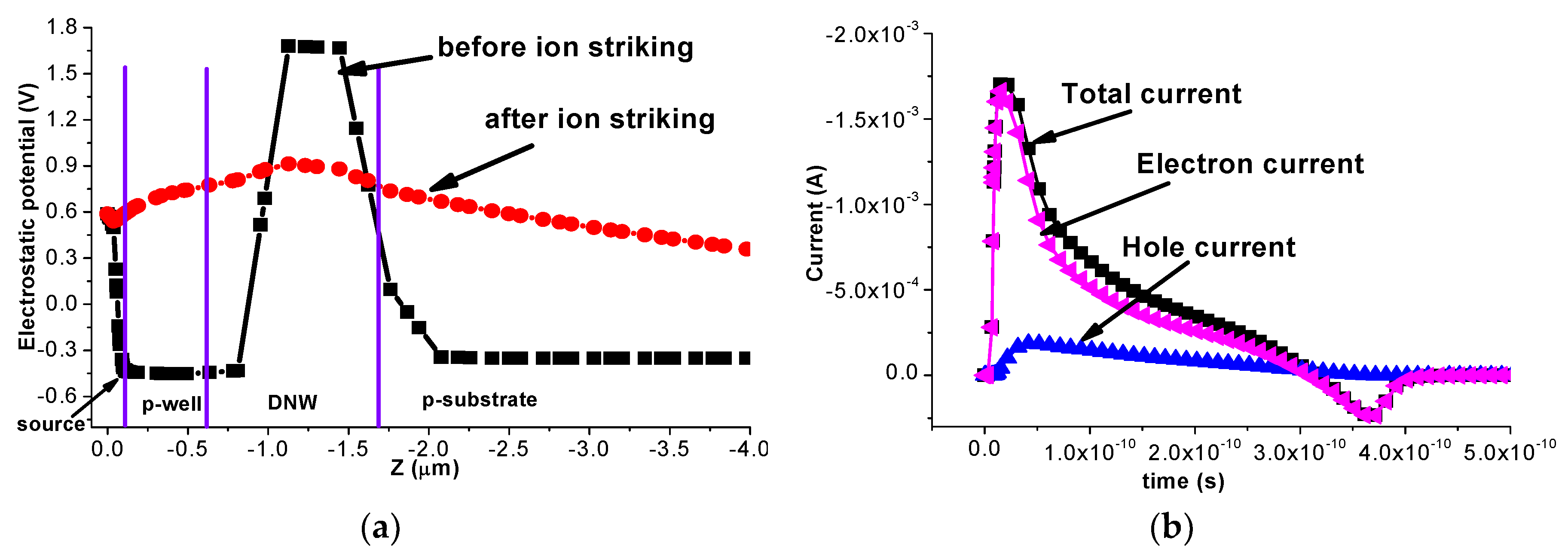

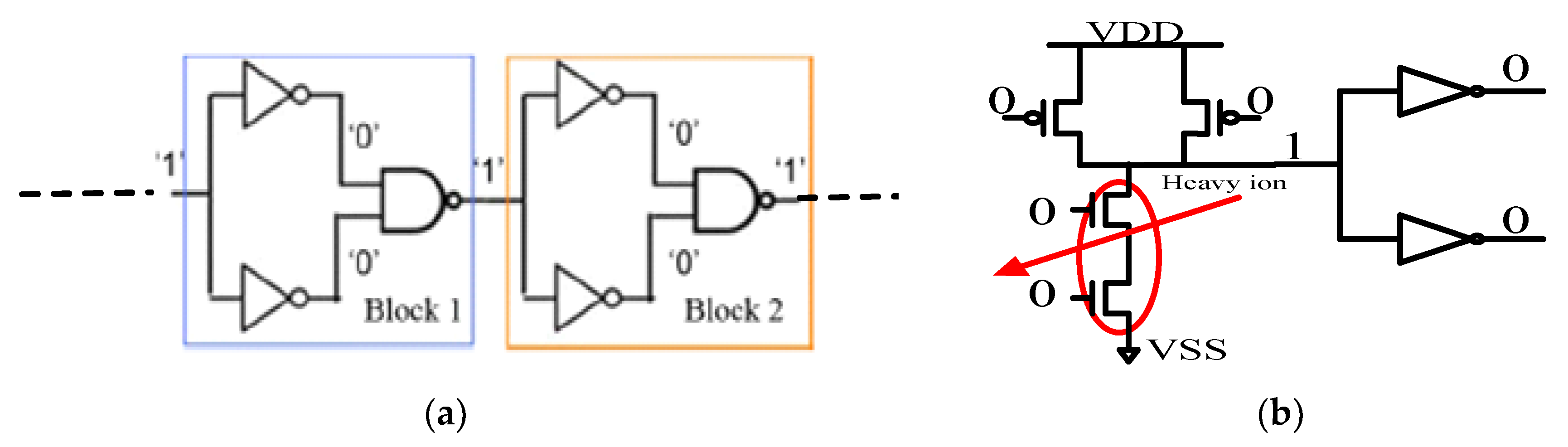

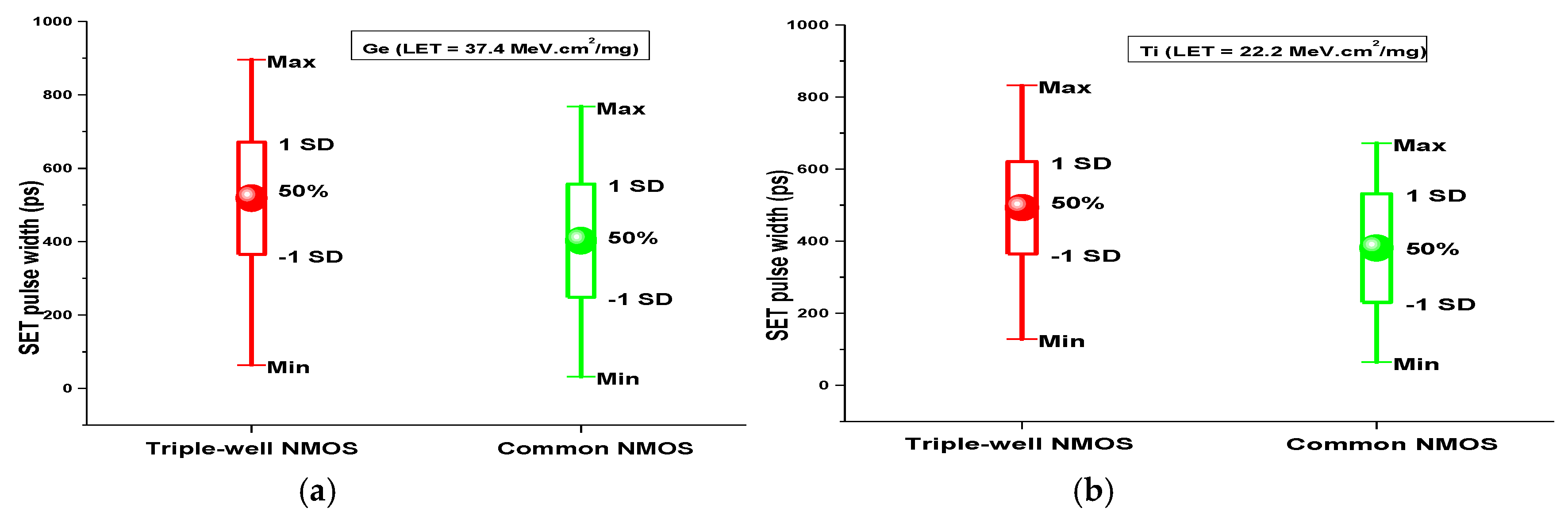

3. Simulation Results and Discussion

4. Quantitative Characterization

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Cavrois, V.F.; Massengill, L.W.; Gouker, P. Single event transients in digital CMOS A review. IEEE Trans. Nucl. Sci. 2013, 60, 1767–1790. [Google Scholar] [CrossRef]

- Huang, P.; Chen, S.; Chen, J.; Liu, B. Novel N-hit single event transient mitigation technique via open guard transistor in 65 nm bulk CMOS process. Sci. China Tech. Sci. 2013, 56, 271–279. [Google Scholar] [CrossRef]

- Chen, J.; Chen, S.; Liang, B.; Liu, F. Single event transient pulse attenuation effect in three-transistor inverter chain. Sci. China Tech. Sci. 2012, 55, 867–871. [Google Scholar] [CrossRef]

- Amusan, O.A.; Witulski, A.F.; Massengill, L.W.; Bhuva, B.L.; Fleming, P.R.; Alles, M.L.; Sternberg, A.L.; Black, J.D.; Schrimpf, R.D. Charge collection and charge sharing in a 130 nm C-MOS technology. IEEE Trans. Nucl. Sci. 2006, 53, 3253–3258. [Google Scholar] [CrossRef]

- Jagannathan, S.; Gadlage, M.J.; Bhuva, B.L.; Schrimpf, R.D.; Narasimham, B.; Chetia, J.; Ahlbin, J.R.; Massengill, L.W. Independent measurement of SET pulse widths from N-hits and P-hits in 65-nm CMOS. IEEE Trans. Nucl. Sci. 2010, 57, 3386–3391. [Google Scholar] [CrossRef]

- Gadlage, M.J.; Ahlbin, J.R.; Narasimham, B.; Bhuva, B.L.; Massengill, L.W.; Schrimpf, R.D. Single-event transient measurements in nMOS and pMOS transistors in a 65-nm bulk CM-OS technology at elevated temperatures. IEEE Trans. Device Mater. Rel. 2011, 1, 179–186. [Google Scholar] [CrossRef]

- Amusan, O.A.; Masengill, L.W.; Bhuva, B.L.; DasGupta, S.; Witulski, A.F.; Ahlbin, J.R. Design techniques to reduce SET pulse widths in deep-submicron combinational logic. IEEE Trans. Nucl. Sci. 2007, 54, 2060–2064. [Google Scholar] [CrossRef]

- Roy, T.; Witulski, A.F.; Schrimpf, R.D.; Alles, M.L.; Massengile, L.W. single Event Mechanisms in 90 nm Triple-Well CMOS Devices. IEEE Trans. Nucl. Sci. 2008, 55, 2948–2956. [Google Scholar] [CrossRef]

- He, Y.B.; Chen, S.M. Simulation study of the selectively implanted deep-N-well for PMOS SET mitigation. IEEE Trans. Device Mater. Rel. 2014, 14, 99–103. [Google Scholar]

- Chen, J.J.; Chen, S.M.; He, Y.B.; Chi, Y.Q.; Qin, J.R.; Liang, B.; Liu, B.W. Novel layout technique for N-hit single-event transient mitigation via source-extension. IEEE Trans. Nucl. Sci. 2012, 59, 2859–2866. [Google Scholar] [CrossRef]

- Chen, J.; Chen, S.; Liang, B.; Liu, B.; Liu, F. Radiation hardened by design techniques to reduce single event transient pulse width based on the physical mechanism. Microelectron. Reliab. 2012, 52, 1227–1232. [Google Scholar] [CrossRef]

- Chen, J.J.; Chen, S.M.; He, Y.B.; Qin, J.R.; Liang, B.; Liu, B.W.; Huang, P.C. Novel layout technique for single-event transient mitigation using dummy transistor. IEEE Trans. Device Mater. Rel. 2012, 13, 177–184. [Google Scholar] [CrossRef]

- Chen, J.J.; Chen, S.M.; Liang, B.; Liu, B.W. Simulation study of the layout technique for P-hit single-event transient mitigation via the source-isolation. IEEE Trans. Device Mater. Rel. 2012, 12, 501–509. [Google Scholar] [CrossRef]

- Chen, J.J.; Chen, S.M.; Chi, Y.Q.; Liang, B. Characterization of single-event transient pulse quenching among dummy gate isolated logic nodes in 65nm twin-well and triple-well CMOS technologies. IEEE Trans. Nucl. Sci. 2015, 62, 2302–2309. [Google Scholar]

- Bevilacqua, A.; Niknejad, A.M. An ultra-wideband CMOS low noise amplifier for 3.1–10.6-GHz wireless receivers. IEEE J. Solid-St Circ. 2004, 39, 2259–2268. [Google Scholar] [CrossRef]

- Chen, H.Y.; Chen, J.J.; Yao, L. Characterizations of the effect of vertical well isolation on single-event multiple cell upsets in SRAM in a 65nm triple-well CMOS technology. Sci. China Tech. Sci. 2015, 58, 1726–1730. [Google Scholar] [CrossRef]

- Narasimham, B.; Ramachandran, V.; Bhuva, B.L.; Schrimpf, R.D.; Witulski, A.F.; Holman, W.T.; Massengill, L.W.; Black, J.D.; Robinson, W.H.; McMorrow, D. On-chip Characterization of single-Event Transient Pulsewiths. IEEE Trans. Device Mater. Rel. 2006, 6, 542–549. [Google Scholar] [CrossRef]

- Xu, J.Y.; Chen, S.M.; Song, R.Q.; Wu, Z.Y.; Chen, J.J. Analysis of Single-Event Transient Sensitivity in Fully-Depleted Silicon-on-Insulator MOSFETs. Nucl. Sci. Tech. 2018, 29, 49–54. [Google Scholar] [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, J.; Chen, J.; Huang, P.; Li, S.; Fang, L. The Effect of Deep N+ Well on Single-Event Transient in 65 nm Triple-Well NMOSFET. Symmetry 2019, 11, 154. https://doi.org/10.3390/sym11020154

Zhang J, Chen J, Huang P, Li S, Fang L. The Effect of Deep N+ Well on Single-Event Transient in 65 nm Triple-Well NMOSFET. Symmetry. 2019; 11(2):154. https://doi.org/10.3390/sym11020154

Chicago/Turabian StyleZhang, Jizuo, Jianjun Chen, Pengcheng Huang, Shouping Li, and Liang Fang. 2019. "The Effect of Deep N+ Well on Single-Event Transient in 65 nm Triple-Well NMOSFET" Symmetry 11, no. 2: 154. https://doi.org/10.3390/sym11020154

APA StyleZhang, J., Chen, J., Huang, P., Li, S., & Fang, L. (2019). The Effect of Deep N+ Well on Single-Event Transient in 65 nm Triple-Well NMOSFET. Symmetry, 11(2), 154. https://doi.org/10.3390/sym11020154