3D Numerical Simulation of a Z Gate Layout MOSFET for Radiation Tolerance

Abstract

1. Introduction

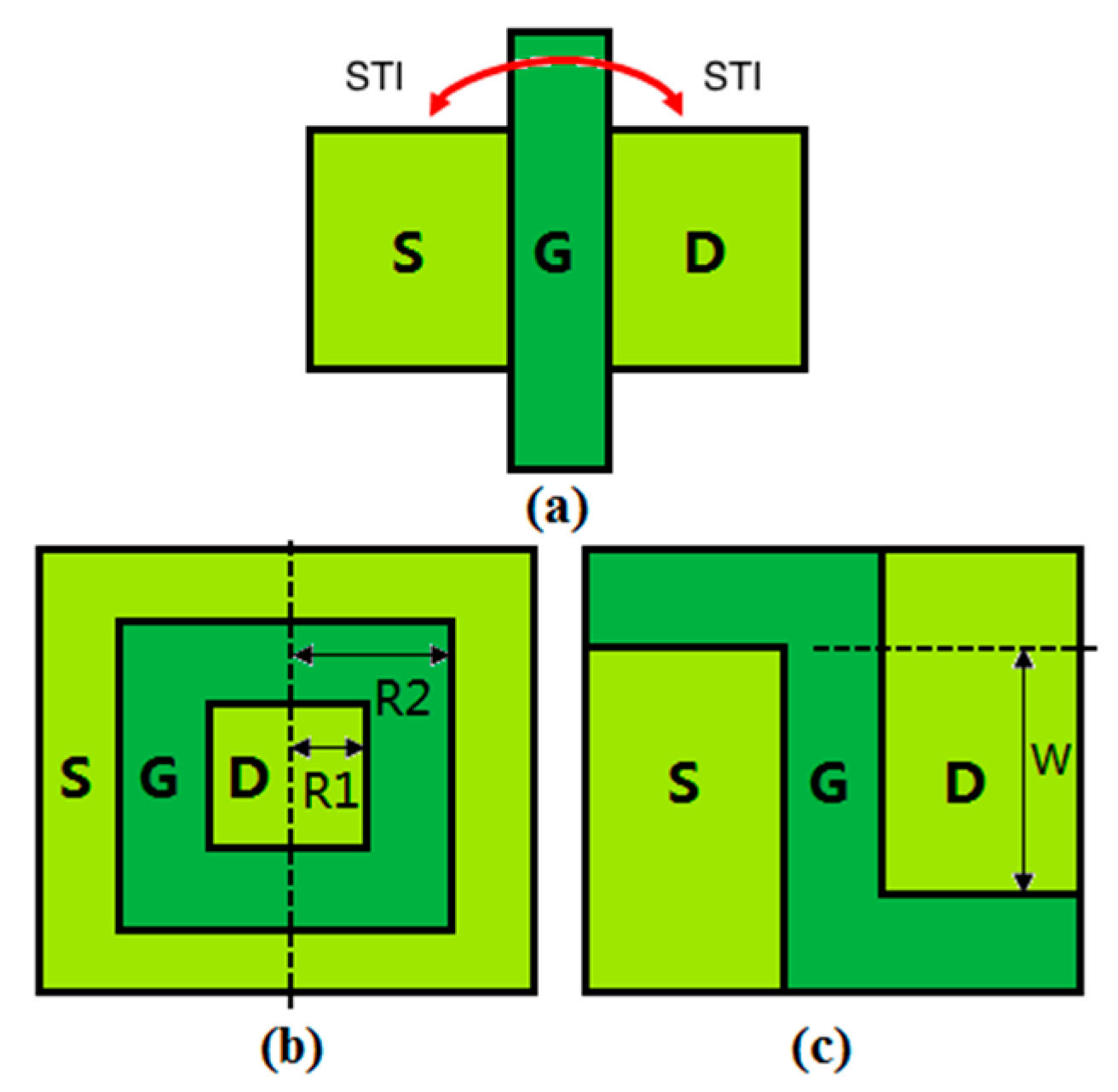

2. Device Structure and Simulation

3. Results and Discussion

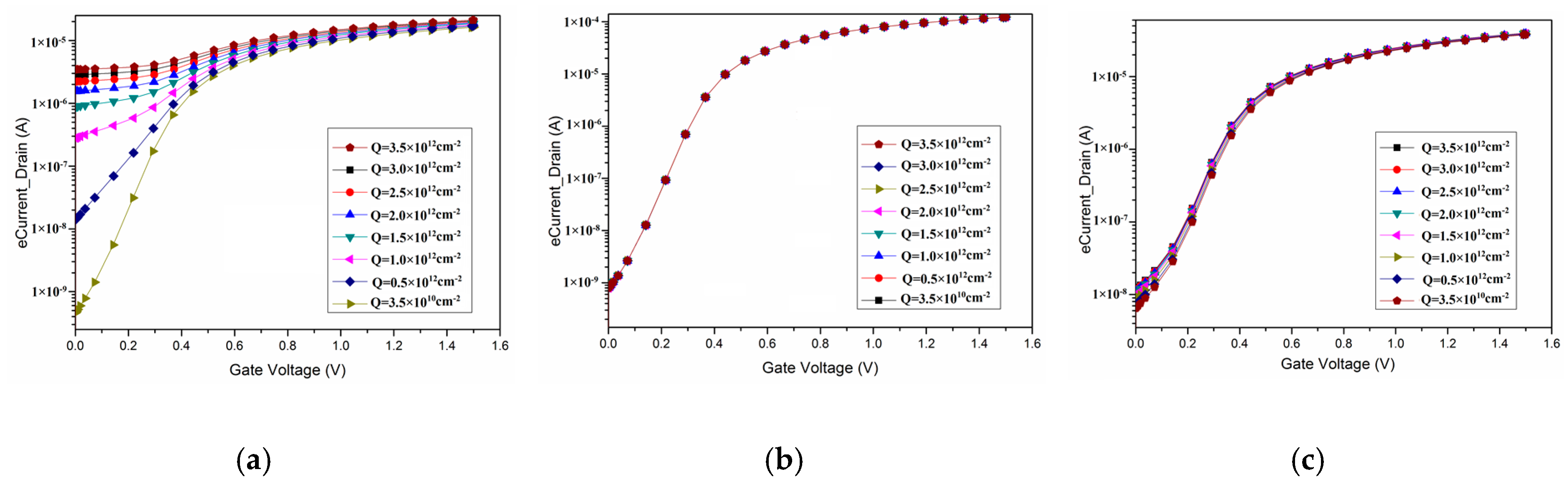

3.1. The Id-Vg Simulation Results

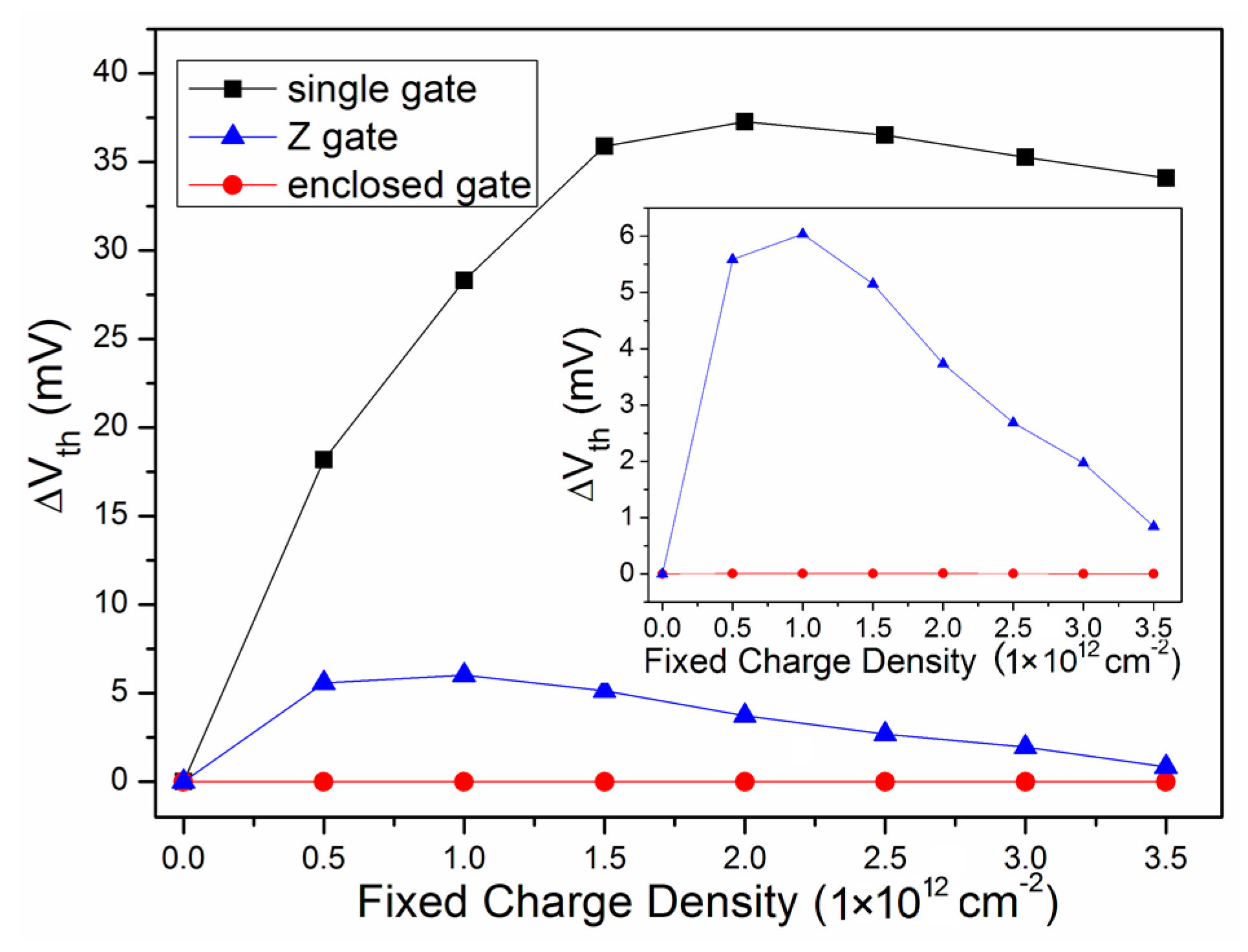

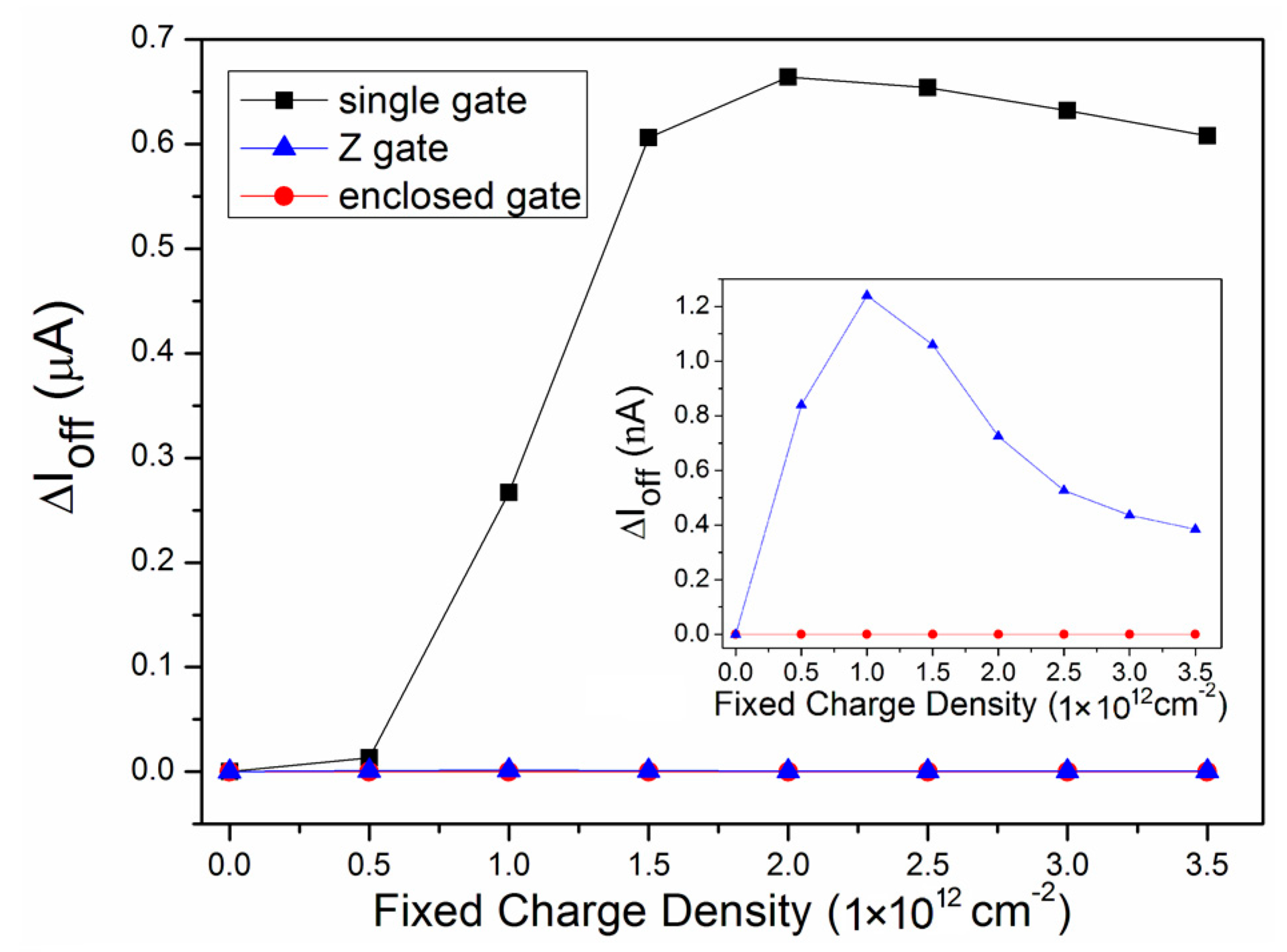

3.2. Comparison of Key Transistor Performance Parameters

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Schwank, J.R.; Shaneyfelt, M.R.; Fleetwood, D.M.; Felix, J.A.; Dodd, P.E.; Paillet, P.; Ferlet-Cavrois, V. Radiation Effects in MOS Oxides. IEEE Trans. Nucl. Sci. 2008, 55, 1833–1853. [Google Scholar] [CrossRef]

- Borghello, G.; Faccio, F.; Lerario, E.; Michelis, S.; Kulis, S.; Fleetwood, D.M.; Bonaldo, S. Dose rate sensitivity of 65 nm MOSFETs exposed to ultra-high doses. IEEE Trans. Nucl. Sci. 2018, 65, 1482–1487. [Google Scholar] [CrossRef]

- Saremi, M.; Privat, A.; Barnaby, H.J.; Clark, L.T. Physically Based Predictive Model for Single Event Transients in CMOS Gates. IEEE Trans. Electron Devices 2016, 63, 2248–2254. [Google Scholar] [CrossRef]

- Narasimham, B.; Bhuva, B.L.; Schrimpf, R.D.; Massengill, L.W.; Gadlage, M.J.; Amusan, O.A.; Benedetto, J.M. Characterization of digital single event transient pulse-widths in 130-nm and 90-nm CMOS technologies. IEEE Trans. Nucl. Sci. 2007, 54, 2506–2511. [Google Scholar] [CrossRef]

- Barnaby, H.J. Total-ionizing-dose effects in modern CMOS technologies. IEEE Trans. Nucl. Sci. 2006, 53, 3103–3121. [Google Scholar] [CrossRef]

- Faccio, F.; Cervelli, G. Radiation-induced edge effects in deep submicron CMOS transistors. IEEE Trans. Nucl. Sci. 2005, 52, 2413–2420. [Google Scholar] [CrossRef]

- Zhang, C.M.; Jazaeri, F.; Borghello, G.; Faccio, F.; Mattiazzo, S.; Baschirotto, A.; Enz, C. Characterization and Modeling of Gigarad-TID-induced Drain Leakage Current of 28-nm Bulk MOSFETs. IEEE Trans. Nucl. Sci. 2018. [Google Scholar] [CrossRef]

- Sajid, M.; Chechenin, N.G.; Torres, F.S.; Hanif, M.N.; Gulzari, U.A.; Arslan, S.; Khan, E.U. Analysis of Total Ionizing Dose effects for highly scaled CMOS devices in Low Earth Orbit. Nucl. Instrum. Methods Phys. Res. Sect. B Beam Interact. Mater. Atoms 2018, 428, 30–37. [Google Scholar] [CrossRef]

- Fleetwood, D.M. Evolution of Total Ionizing Dose Effects in MOS Devices with Moore’s Law Scaling. IEEE Trans. Nucl. Sci. 2018, 65, 1465–1481. [Google Scholar] [CrossRef]

- Dodd, P.E.; Shaneyfelt, M.R.; Schwank, J.R.; Felix, J.A. Current and future challenges in radiation effects on CMOS electronics. IEEE Trans. Nucl. Sci. 2010, 57, 1747–1763. [Google Scholar] [CrossRef]

- Faccio, F.; Borghello, G.; Lerario, E.; Fleetwood, D.M.; Schrimpf, R.D.; Gong, H.; Zhang, E.X.; Wang, P.; Michelis, S.; Gerardin, S.; et al. Influence of LDD spacers and H+ transport on the total-ionizing-dose response of 65 nm MOSFETs irradiated to ultra-high doses. IEEE Trans. Nucl. Sci. 2018, 65, 164–174. [Google Scholar] [CrossRef]

- Snoeys, W.J.; Faccio, F.; Burns, M.; Campbell, M.; Cantatore, E.; Carrer, N. Layout techniques to enhance the radiation tolerance of standard CMOS technologies demonstrated on a pixel detector readout chip. Nucl. Instrum. Methods Phys. Res. A 2000, 439, 349–360. [Google Scholar] [CrossRef]

- Snoeys, W.J.; Gutierrez, T.A.; Anelli, G. A new NMOS layout structure for radiation tolerance. IEEE Trans. Nucl. Sci. 2002, 49, 1829–1833. [Google Scholar] [CrossRef]

- Gingrich, D.M.; Böttcher, S.; Buchanan, N.J.; Liu, S.; Parsons, J.A.; Sippach, W. Radiation tolerant ASIC for controlling switched-capacitor arrays. IEEE Trans. Nucl. Sci. 2004, 51, 1324–1332. [Google Scholar] [CrossRef]

- Anelli, G.; Campbell, M.; Delmastro, M.; Faccio, F.; Florian, S.; Giraldo, A.; Hejine, E.; Jarron, P.; Kloukinas, K.; Marchioro, A.; et al. Radiation tolerant VLSI circuits in standard deep submicron CMOS technologies for the LHC experiments: Practical design aspects. IEEE Trans. Nucl. Sci. 1999, 46, 1690–1696. [Google Scholar] [CrossRef]

- Giraldo, A.; Paccagnella, A.; Minzoni, A. Aspect ratio calculation in n-channel MOSFET’s with a gate-enclosed layout. Solid-State Electron. 2000, 44, 981–989. [Google Scholar] [CrossRef]

- Gaillardin, M.; Martinez, M.; Girard, S.; Goiffon, V.; Paillet, P.; Leray, J.L.; Magnan, P.; Ouerdane, Y.; Boukenter, A.; Marcandella, C.; et al. High Total Ionizing Dose and Temperature Effects on Micro- and Nano-Electronic Devices. IEEE Trans. Nucl. Sci. 2015, 62, 1226–1232. [Google Scholar] [CrossRef]

- Imenabadi, R.M.; Saremi, M.; Vandenberghe, W.G. A Novel PNPN-Like Z-Shaped Tunnel Field-Effect Transistor with Improved Ambipolar Behavior and RF Performance. IEEE Trans. Electron Devices 2017, 64, 4752–4758. [Google Scholar] [CrossRef]

- Sachid, A.B.; Manoj, C.R.; Sharma, D.K.; Rao, V.R. Gate fringe-induced barrier lowering in underlap FinFET structures and its optimization. IEEE Electron Device Lett. 2008, 29, 128–130. [Google Scholar] [CrossRef]

- Boucart, K.; Ionescu, A.M. Double-Gate Tunnel FET with High-K Gate Dielectric. IEEE Trans. Electron Devices 2007, 54, 1725–1733. [Google Scholar] [CrossRef]

- Abadi, R.M.I.; Saremi, M.A. Resonant Tunneling Nanowire Field Effect Transistor with Physical Contractions: A Negative Differential Resistance Device for Low Power Very Large Scale Integration Applications. J. Electron. Mater. 2018, 47, 1091–1098. [Google Scholar] [CrossRef]

- Gnani, E.; Gnudi, A.; Reggiani, S.; Baccarani, G. Theory of the Junctionless Nanowire FET. IEEE Trans. Electron Devices 2011, 58, 2903–2910. [Google Scholar] [CrossRef]

- Esqueda, I.S.; Barnaby, H.J.; Holbert, K.E.; El-Mamouni, F.; Schrimpf, R.D. Modeling of Ionizing Radiation-Induced Degradation in Multiple Gate Field Effect Transistors. IEEE Trans. Nucl. Sci. 2011, 58, 499–505. [Google Scholar] [CrossRef]

- Lee, M.S.; Lee, H.C. Dummy Gate-Assisted n-MOSFET Layout for a Radiation-Tolerant Integrated Circuit. IEEE Trans. Nucl. Sci. 2013, 60, 3084–3091. [Google Scholar] [CrossRef]

- Fernandez-Martinex, P.; Cortes, I.; Hidalgo, S.; Flores, D.; Palomo, F.R. Simulation of total ionizing dose in MOS capacitors. In Proceedings of the 8th Spanish Conference on Electron Devices, Palma de Mallorca, Spain, 8–11 February 2011. [Google Scholar]

- Moon, J.-B.; Moon, D.-I.; Choi, Y.-K. Influence of Total Ionizing Dose on Sub-100 nm Gate-All-Around MOSFETs. IEEE Trans. Nucl. Sci. 2014, 61, 1420–1425. [Google Scholar] [CrossRef]

- Wang, J.; Wang, W.; Huang, R.; Pei, Y.; Xue, S.; Wang, X.A.; Wang, Y. Deteriorated radiation effects impact on the characteristics of MOS transistors with multi-finger configuration. Microelectron. Reliab. 2010, 50, 1094–1097. [Google Scholar] [CrossRef]

- Nam, J.; Kang, C.Y.; Kim, K.P.; Yeo, H.; Lee, B.J.; Seo, S.; Yang, J.-W. Influence of Ionizing Radiation on Short-Channel Effects in Low-Doped Multi-Gate MOSFETs. IEEE Trans. Nucl. Sci. 2012, 59, 3021–3026. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| Length of channel | 0.12 μm |

| Width of channel | 0.21 μm |

| Thickness of n-type poly gate | 100 nm |

| Thickness of gate oxide | 2 nm |

| Doping of source/drain region | 1.0 × 1019 cm−3 |

| Depth of source/drain region | 100 nm |

| Doping of p-type substrate | 4.0 × 1017 cm−3 |

| Layout | Vth-pre (mV) | Vth-post (mV) | ΔVth (mV) |

|---|---|---|---|

| single gate | 363 | 138 | 226 |

| enclosed gate | 374 | 374 | <1 |

| Z gate | 354 | 329 | 25 |

| Layout | Ioff-pre (A) | Ioff-post (A) | Increment |

|---|---|---|---|

| single gate | 4.58 × 10−10 | 3.44 × 10−6 | 3.44 μA |

| enclosed gate | 7.91 × 10−10 | 7.95 × 10−10 | 0.004 nA |

| Z gate | 6.46 × 10−9 | 1.17 × 10−8 | 5.24 nA |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, Y.; Shan, C.; Piao, W.; Li, X.-j.; Yang, J.-q.; Cao, F.; Yu, C.-h. 3D Numerical Simulation of a Z Gate Layout MOSFET for Radiation Tolerance. Micromachines 2018, 9, 659. https://doi.org/10.3390/mi9120659

Wang Y, Shan C, Piao W, Li X-j, Yang J-q, Cao F, Yu C-h. 3D Numerical Simulation of a Z Gate Layout MOSFET for Radiation Tolerance. Micromachines. 2018; 9(12):659. https://doi.org/10.3390/mi9120659

Chicago/Turabian StyleWang, Ying, Chan Shan, Wei Piao, Xing-ji Li, Jian-qun Yang, Fei Cao, and Cheng-hao Yu. 2018. "3D Numerical Simulation of a Z Gate Layout MOSFET for Radiation Tolerance" Micromachines 9, no. 12: 659. https://doi.org/10.3390/mi9120659

APA StyleWang, Y., Shan, C., Piao, W., Li, X.-j., Yang, J.-q., Cao, F., & Yu, C.-h. (2018). 3D Numerical Simulation of a Z Gate Layout MOSFET for Radiation Tolerance. Micromachines, 9(12), 659. https://doi.org/10.3390/mi9120659