Heterogeneous Integration Technology Drives the Evolution of Co-Packaged Optics

Abstract

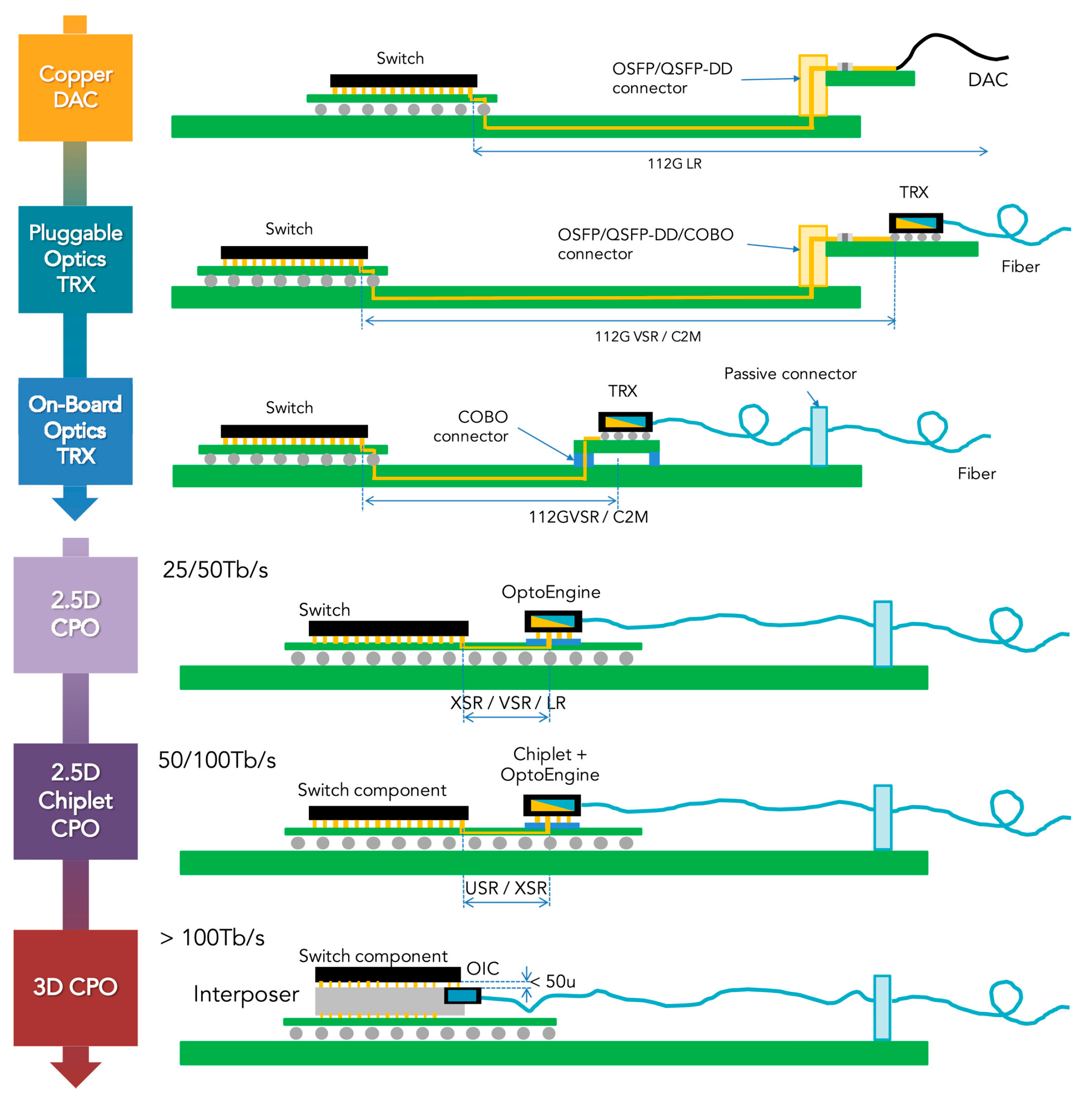

1. Introduction

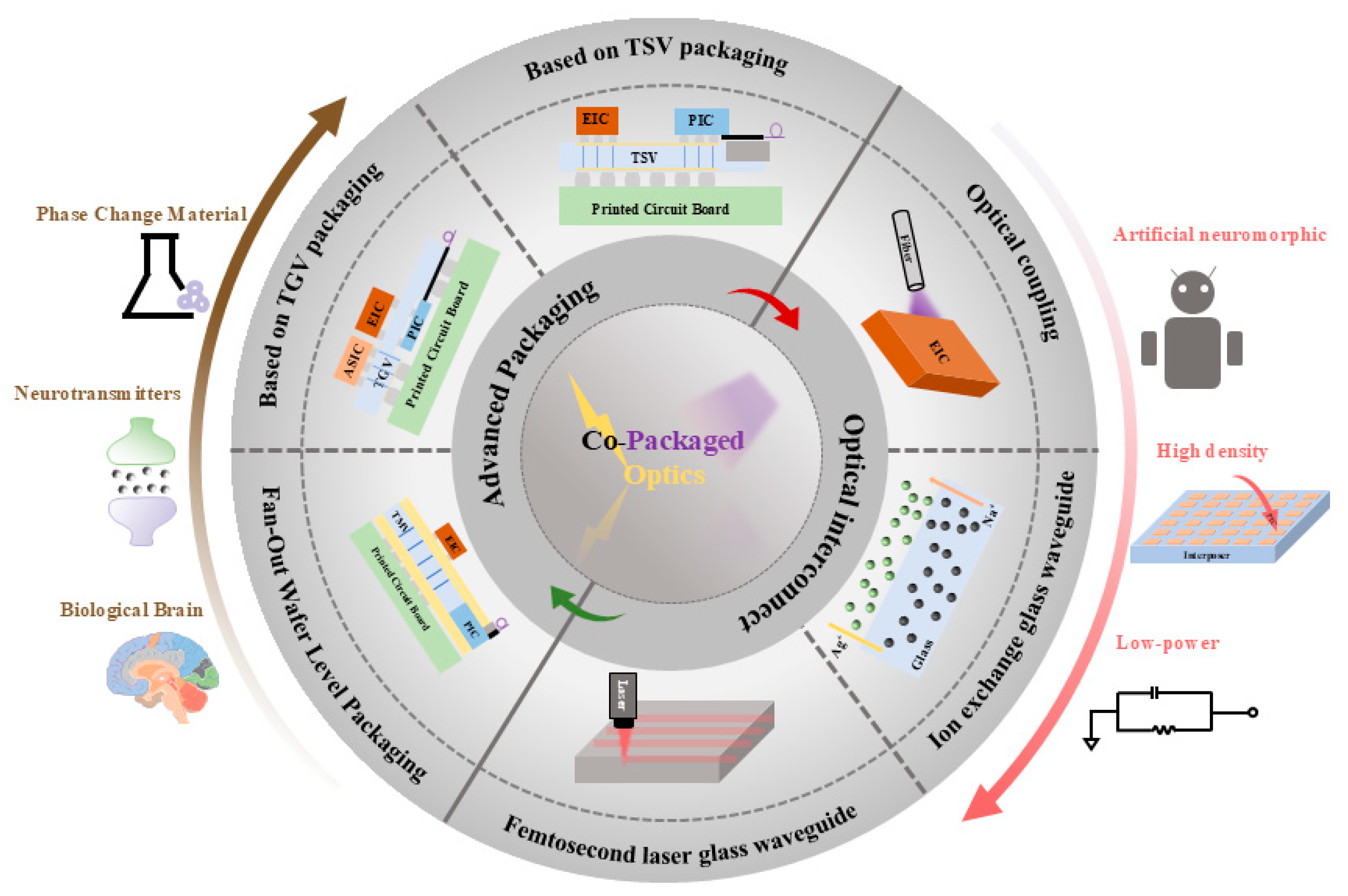

2. Advanced Packaging Technology

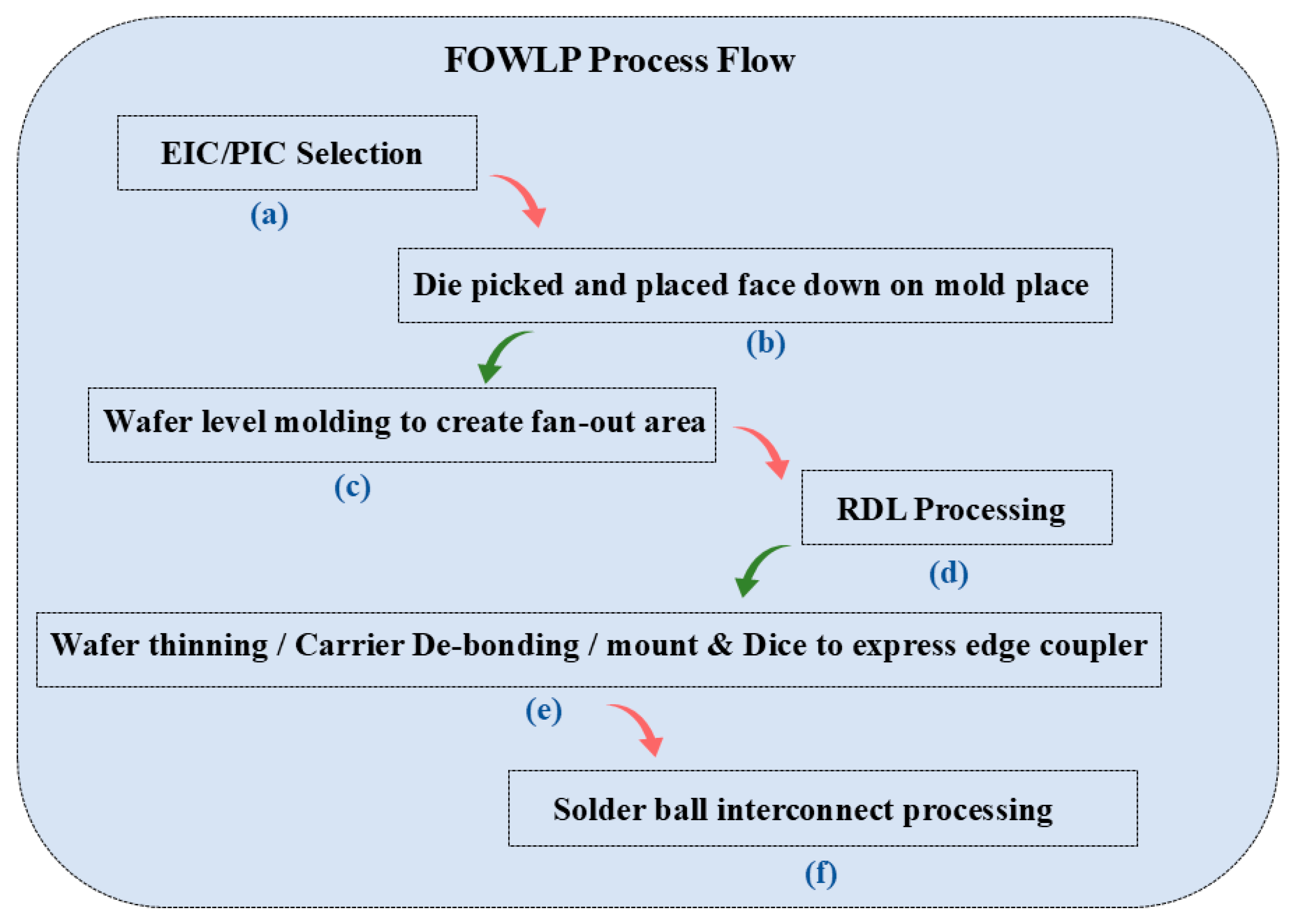

2.1. Based on FOWLP Technology

2.2. Based on TSV Packaging Technology

2.3. Based on TGV Packaging Technology

3. Optical Interconnect Technology

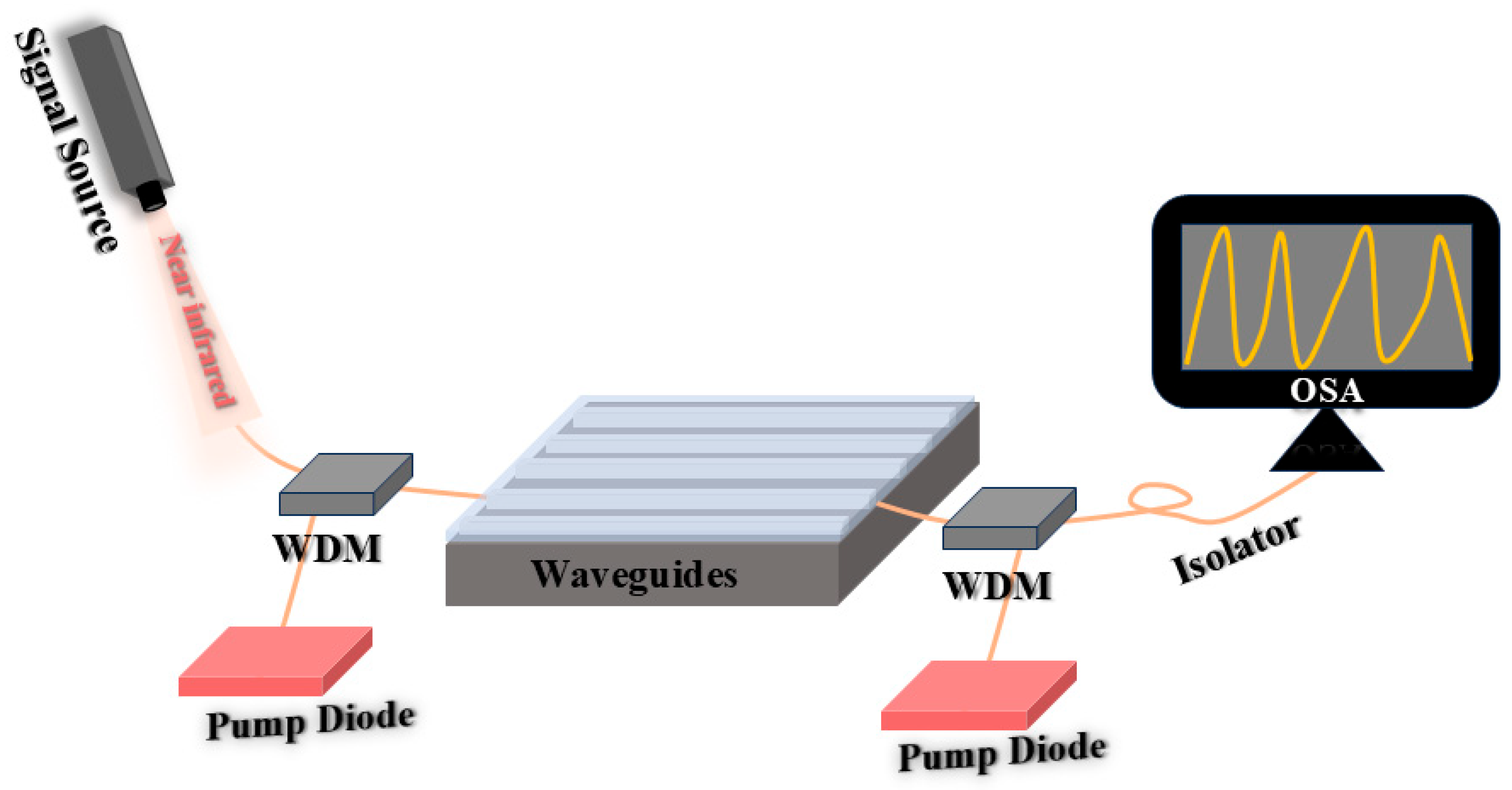

3.1. Femtosecond Laser Direct Writing Waveguide

3.2. Ion-Exchange Glass Waveguide

3.3. Fiber Coupling

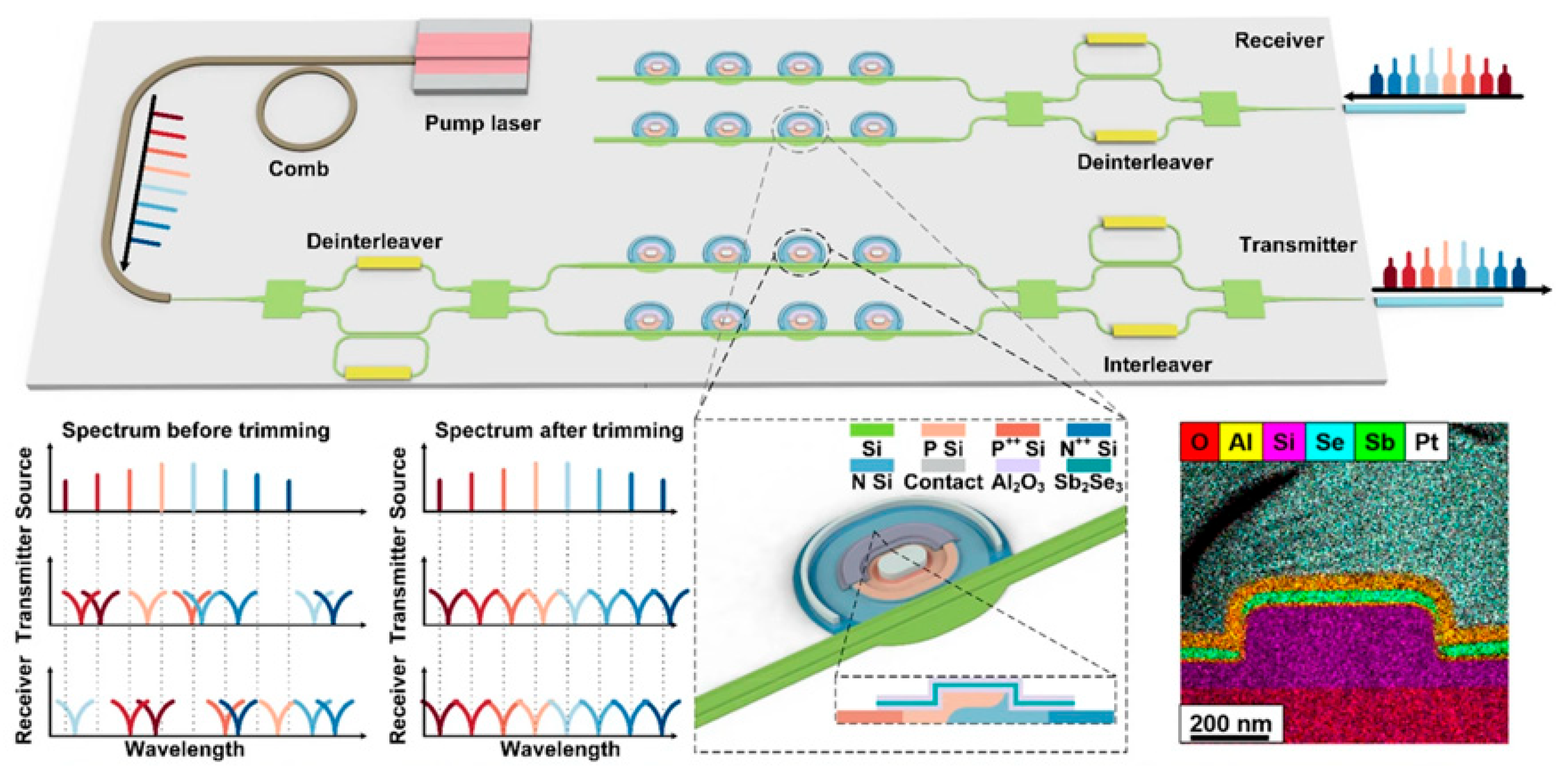

4. Artificial Neuromorphic Optical Interconnects

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Edelstein, D.; Heidenreich, J.; Goldblatt, R.; Cote, W.; Uzoh, C.; Lustig, N.; Roper, P.; McDevittt, T.; Motsifft, W.; Simon, A.; et al. Full Copper Wiring in a Sub-0.25 Pm CMOS ULSI Technology. In Proceedings of the International Electron Devices Meeting. IEDM Technical Digest, Washington, DC, USA, 6–10 December 1997; pp. 773–776. [Google Scholar]

- Kumar, S.; Sharma, R. Chip-to-Chip Copper Interconnects With Rough Surfaces: Analytical Models for Parameter Extraction and Performance Evaluation. IEEE Trans. Compon. Packag. Manuf. Technol. 2018, 8, 286–299. [Google Scholar] [CrossRef]

- Kayla Schaevitz, R.; Muth, K.; Luo, Y.; Raghuraman, V.; Margalit, N. Solving the Escape Density Problem: Making Connections Count with SCIP. In Proceedings of the 2023 Optical Fiber Communications Conference and Exhibition (OFC), San Diego, CA, USA, 5–9 March 2023; IEEE: Piscataway, NJ, USA, 2023; pp. 1–3. [Google Scholar]

- Mahajan, R.; Li, X.; Fryman, J.; Zhang, Z.; Nekkanty, S.; Tadayon, P.; Jaussi, J.; Shumarayev, S.; Agrawal, A.; Jadhav, S.; et al. Co-Packaged Photonics For High Performance Computing: Status, Challenges And Opportunities. J. Light. Technol. 2022, 40, 379–392. [Google Scholar] [CrossRef]

- Rakowski, M.; Meagher, C.; Nummy, K.; Aboketaf, A.; Ayala, J.; Harris, B.; Mclean, K.; McStay, K.; Sahin, A.; Medina, L.; et al. 45nm CMOS—Silicon Photonics Monolithic Technology (45CLO) for next-Generation, Low Power and High Speed Optical Interconnects. In Proceedings of the 2020 Optical Fiber Communications Conference and Exhibition (OFC), San Diego, CA, USA, 8–12 March 2020; pp. 1–3. [Google Scholar]

- Yu, H.; Doussiere, P.; Patel, D.; Lin, W.; Al-hemyari, K.; Park, J.; Jan, C.; Herrick, R.; Hoshino, I.; Busselle, L.; et al. 400Gbps Fully Integrated DR4 Silicon Photonics Transmitter for Data Center Applications. In Proceedings of the 2020 Optical Fiber Communications Conference and Exhibition (OFC), San Diego, CA, USA, 8–12 March 2020; pp. 1–3. [Google Scholar]

- Lau, J.H. Recent Advances and Trends in Advanced Packaging. IEEE Trans. Compon. Packag. Manuf. Technol. 2022, 12, 228–252. [Google Scholar] [CrossRef]

- Maniotis, P.; Kuchta, D.M. Exploring the Benefits of Using Co-Packaged Optics in Data Center and AI Supercomputer Networks: A Simulation-Based Analysis [Invited]. J. Opt. Commun. Netw. 2024, 16, A143–A156. [Google Scholar] [CrossRef]

- Kannan, S.; Chang, R.; Potluri, H.; Zhang, S.; Li, J.; Xu, B.; Hsu, H.-C. High Density Integration of Silicon Photonic Chiplets for 51.2T Co-Packaged Optics. In Proceedings of the 2024 IEEE 74th Electronic Components and Technology Conference (ECTC), Denver, CO, USA, 28–31 May 2024; IEEE: Piscataway, NJ, USA, 2024; pp. 81–84. [Google Scholar]

- Bogaerts, L.; El-Mekki, Z.; Van Huylenbroeck, S.; Nolmans, P.; Pantano, N.; Sun, X.; Rakowski, M.; Velenis, D.; Verheyen, P.; Balakrishnan, S.; et al. High-Speed TSV Integration in an Active Silicon Photonics Interposer Platform. In Proceedings of the 2018 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Burlingame, CA, USA, 15–18 October 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 1–3. [Google Scholar]

- Wang, S.; Wang, Q.; Liu, Y.; Jia, L.; Yu, M.; Sun, P.; Geng, F.; Cai, Y.; Tu, Z. Low-Loss through Silicon Vias (TSVs) and Transmission Lines for 3D Optoelectronic Integration. Microelectron. Eng. 2021, 238, 111509. [Google Scholar] [CrossRef]

- Kim, J.; Krishna Chekuri, V.C.; Rahman, N.M.; Dolatsara, M.A.; Torun, H.; Swaminathan, M.; Mukhopadhyay, S.; Kyu Lim, S. Silicon vs. Organic Interposer: PPA and Reliability Tradeoffs in Heterogeneous 2.5D Chiplet Integration. In Proceedings of the 2020 IEEE 38th International Conference on Computer Design (ICCD), Hartford, CT, USA, 18–21 October 2020; IEEE: Piscataway, NJ, USA, 2020; pp. 80–87. [Google Scholar]

- Brusberg, L.; Grenier, J.R.; Kocabaş, Ş.E.; Zakharian, A.R.; Yeary, L.W.; Levesque, D.W.; Paddock, B.J.; Bellman, R.A.; Force, R.M.; Terwilliger, C.C.; et al. Glass Interposer for High-Density Photonic Packaging. In Proceedings of the Optical Fiber Communication Conference (OFC) 2022, San Diego, CA, USA, 6–10 March 2022; Optica Publishing Group: Washington, DC, USA, 2022; pp. 1–3. [Google Scholar]

- Usman, A.; Shah, E.; Satishprasad, N.B.; Chen, J.; Bohlemann, S.A.; Shami, S.H.; Eftekhar, A.A.; Adibi, A. Interposer Technologies for High-Performance Applications. IEEE Trans. Compon. Packag. Manuf. Technol. 2017, 7, 819–828. [Google Scholar] [CrossRef]

- Shih, M.; Chen, K.; Lee, T.; Tarng, D.; Hung, C.P. FE Simulation Model for Warpage Evaluation of Glass Interposer Substrate Packages. IEEE Trans. Compon. Packag. Manuf. Technol. 2021, 11, 690–696. [Google Scholar] [CrossRef]

- Lau, J.H.; Li, M.; Tian, D.; Fan, N.; Kuah, E.; Kai, W.; Li, M.; Hao, J.; Cheung, Y.M.; Li, Z.; et al. Warpage and Thermal Characterization of Fan-Out Wafer-Level Packaging. IEEE Trans. Compon. Packag. Manuf. Technol. 2017, 7, 1729–1738. [Google Scholar] [CrossRef]

- Rao, V.S.; Chong, C.T.; Ho, D.; Zhi, D.M.; Choong, C.S.; Sharon, L.P.S.; Ismael, D.; Liang, Y.Y. Development of High Density Fan Out Wafer Level Package (HD FOWLP) with Multi-Layer Fine Pitch RDL for Mobile Applications. In Proceedings of the 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 31 May–3 June 2016; pp. 1522–1529. [Google Scholar]

- Bogaerts, W.; Pérez, D.; Capmany, J.; Miller, D.A.B.; Poon, J.; Englund, D.; Morichetti, F.; Melloni, A. Programmable Photonic Circuits. Nature 2020, 586, 207–216. [Google Scholar] [CrossRef]

- Snigirev, V.; Riedhauser, A.; Lihachev, G.; Churaev, M.; Riemensberger, J.; Wang, R.N.; Siddharth, A.; Huang, G.; Möhl, C.; Popoff, Y.; et al. Ultrafast Tunable Lasers Using Lithium Niobate Integrated Photonics. Nature 2023, 615, 411–417. [Google Scholar] [CrossRef]

- Xu, X.; Ren, G.; Feleppa, T.; Liu, X.; Boes, A.; Mitchell, A.; Lowery, A.J. Self-Calibrating Programmable Photonic Integrated Circuits. Nat. Photonics 2022, 16, 595–602. [Google Scholar] [CrossRef]

- Wang, Y.; Holguín-Lerma, J.A.; Vezzoli, M.; Guo, Y.; Tang, H.X. Photonic-Circuit-Integrated Titanium:Sapphire Laser. Nat. Photonics 2023, 17, 338–345. [Google Scholar] [CrossRef]

- Grivas, C.; Ismaeel, R.; Corbari, C.; Huang, C.-C.; Hewak, D.W.; Lagoudakis, P.; Brambilla, G. Generation of Multi-Gigahertz Trains of Phase-Coherent Femtosecond Laser Pulses in Ti:Sapphire Waveguides. Laser Photonics Rev. 2018, 12, 1800167. [Google Scholar] [CrossRef]

- Bae, J.E.; Calmano, T.; Kränkel, C.; Rotermund, F. Controllable Dynamic Single- and Dual-Channel Graphene Q-Switching in a Beam-Splitter-Type Channel Waveguide Laser. Laser Photonics Rev. 2022, 16, 2100501. [Google Scholar] [CrossRef]

- Lu, J.; Garcia-Caurel, E.; Ossikovski, R.; Courvoisier, F.; Zeng, X.; Poumellec, B.; Lancry, M. Femtosecond Laser Direct Writing Multilayer Chiral Waveplates with Minimal Linear Birefringence. Opt. Lett. 2023, 48, 271–274. [Google Scholar] [CrossRef]

- Sun, K.; Tan, D.; Fang, X.; Xia, X.; Lin, D.; Song, J.; Lin, Y.; Liu, Z.; Gu, M.; Yue, Y.; et al. Three-Dimensional Direct Lithography of Stable Perovskite Nanocrystals in Glass. Science 2022, 375, 307–310. [Google Scholar] [CrossRef]

- Tan, D.; Wang, Z.; Xu, B.; Qiu, J. Photonic Circuits Written by Femtosecond Laser in Glass: Improved Fabrication and Recent Progress in Photonic Devices. Adv. Photonics 2021, 3, 024002. [Google Scholar] [CrossRef]

- Zhang, B.; Wang, Z.; Tan, D.; Qiu, J. Ultrafast Laser-Induced Self-Organized Nanostructuring in Transparent Dielectrics: Fundamentals and Applications. PhotoniX 2023, 4, 24. [Google Scholar] [CrossRef]

- Ramaswamy, R.V.; Srivastava, R. Ion-Exchanged Glass Waveguides: A Review. J. Light. Technol. 1988, 6, 984–1000. [Google Scholar] [CrossRef]

- Schröder, H.; Brusberg, L. Thin Glass Based Electro-Optical Circuit Board (EOCB): Waveguide Process, PCB Technology, and Coupling Interfaces. In Proceedings of the 2015 IEEE CPMT Symposium Japan (ICSJ), Kyoto, Japan, 9–11 November 2015; pp. 109–117. [Google Scholar]

- Schwietering, J.; Herbst, C.; Kirsch, O.; Arndt-Staufenbiel, N.; Wachholz, P.; Schröder, H.; Schneider-Ramelow, M. Integrated Optical Single-Mode Waveguide Structures in Thin Glass for Flip-Chip PIC Assembly and Fiber Coupling. In Proceedings of the 2020 IEEE 70th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 3–30 June 2020; pp. 148–155. [Google Scholar]

- Vlasov, Y.A.; McNab, S.J. Losses in Single-Mode Silicon-on-Insulator Strip Waveguides and Bends. Opt. Express 2004, 12, 1622–1631. [Google Scholar] [CrossRef]

- Marchetti, R.; Lacava, C.; Carroll, L.; Gradkowski, K.; Minzioni, P. Coupling Strategies for Silicon Photonics Integrated Chips [Invited]. Photonics Res. 2019, 7, 201–239. [Google Scholar] [CrossRef]

- Chen, G.F.R.; Ong, J.R.; Ang, T.Y.L.; Lim, S.T.; Png, C.E.; Tan, D.T.H. Broadband Silicon-On-Insulator Directional Couplers Using a Combination of Straight and Curved Waveguide Sections. Sci. Rep. 2017, 7, 7246. [Google Scholar] [CrossRef]

- Wang, X.; Shi, W.; Yun, H.; Grist, S.; Jaeger, N.A.F.; Chrostowski, L. Narrow-Band Waveguide Bragg Gratings on SOI Wafers with CMOS-Compatible Fabrication Process. Opt. Express 2012, 20, 15547–15558. [Google Scholar] [CrossRef]

- Lacava, C.; Strain, M.J.; Minzioni, P.; Cristiani, I.; Sorel, M. Integrated Nonlinear Mach Zehnder for 40 Gbit/s All-Optical Switching. Opt. Express 2013, 21, 21587–21595. [Google Scholar] [CrossRef]

- Bogaerts, W.; Heyn, P.D.; Vaerenbergh, T.V.; Vos, K.D.; Selvaraja, S.K.; Claes, T.; Dumon, P.; Bienstman, P.; Thourhout, D.V.; Baets, R. Silicon Microring Resonators. Laser Photonics Rev. 2012, 6, 47–73. [Google Scholar] [CrossRef]

- Son, G.; Han, S.; Park, J.; Kwon, K.; Yu, K. High-Efficiency Broadband Light Coupling between Optical Fibers and Photonic Integrated Circuits. Nanophotonics 2018, 7, 1845–1864. [Google Scholar] [CrossRef]

- Chen, Z.; Ning, Y.; Xun, Y. Chirped and Apodized Grating Couplers on Lithium Niobate Thin Film. Opt. Mater. Express 2020, 10, 2513–2521. [Google Scholar] [CrossRef]

- Zhou, X.; Xue, Y.; Ye, F.; Feng, Z.; Li, Y.; Sun, X.; Lau, K.M.; Tsang, H.K. High Coupling Efficiency Waveguide Grating Couplers on Lithium Niobate. Opt. Lett. 2023, 48, 3267. [Google Scholar] [CrossRef] [PubMed]

- Chen, B.; Ruan, Z.; Fan, X.; Wang, Z.; Liu, J.; Li, C.; Chen, K.; Liu, L. Low-Loss Fiber Grating Coupler on Thin Film Lithium Niobate Platform. APL Photonics 2022, 7, 076103. [Google Scholar] [CrossRef]

- He, L.; Zhang, M.; Shams-Ansari, A.; Zhu, R.; Wang, C.; Marko, L. Low-Loss Fiber-to-Chip Interface for Lithium Niobate Photonic Integrated Circuits. Opt. Lett. 2019, 44, 2314–2317. [Google Scholar] [PubMed]

- Liu, X.; Gao, S.; Zhang, C.; Pan, Y.; Ma, R.; Zhang, X.; Liu, L.; Xie, Z.; Zhu, S.; Yu, S.; et al. Ultra-Broadband and Low-Loss Edge Coupler for Highly Efficient Second Harmonic Generation in Thin-Film Lithium Niobate. Adv. Photonics Nexus 2022, 1, 016001. [Google Scholar] [CrossRef]

- Jia, D.; Luo, Q.; Yang, C.; Ma, R.; Yu, X.; Gao, F.; Yang, Q.; Bo, F.; Zhang, G.; Xu, J. High-Efficiency Edge Couplers Enabled by Vertically Tapering on Lithium-Niobate Photonic Chips. Appl. Phys. Lett. 2023, 123, 263502. [Google Scholar] [CrossRef]

- Shan, X.; Zhao, C.; Wang, X.; Wang, Z.; Fu, S.; Lin, Y.; Zeng, T.; Zhao, X.; Xu, H.; Zhang, X.; et al. Plasmonic Optoelectronic Memristor Enabling Fully Light-Modulated Synaptic Plasticity for Neuromorphic Vision. Adv. Sci. 2022, 9, 2104632. [Google Scholar] [CrossRef] [PubMed]

- Liu, Z.; Tang, J.; Gao, B.; Yao, P.; Li, X.; Liu, D.; Zhou, Y.; Qian, H.; Hong, B.; Wu, H. Neural Signal Analysis with Memristor Arrays towards High-Efficiency Brain–Machine Interfaces. Nat. Commun. 2020, 11, 4234. [Google Scholar] [CrossRef] [PubMed]

- Liu, Z.; Mei, J.; Tang, J.; Xu, M.; Gao, B.; Wang, K.; Ding, S.; Liu, Q.; Qin, Q.; Chen, W.; et al. A Memristor-Based Adaptive Neuromorphic Decoder for Brain–Computer Interfaces. Nat. Electron. 2025, 8, 362–372. [Google Scholar] [CrossRef]

- Eggleton, B.J.; Luther-Davies, B.; Richardson, K. Chalcogenide Photonics. Nat. Photonics 2011, 5, 141–148. [Google Scholar] [CrossRef]

- Wuttig, M.; Bhaskaran, H.; Taubner, T. Phase-Change Materials for Non-Volatile Photonic Applications. Nat. Photonics 2017, 11, 465–476. [Google Scholar] [CrossRef]

- Miller, K.J.; Haglund, R.F.; Weiss, S.M. Optical Phase Change Materials in Integrated Silicon Photonic Devices: Review. Opt. Mater. Express 2018, 8, 2415–2429. [Google Scholar] [CrossRef]

- Ding, F.; Yang, Y.; Bozhevolnyi, S.I. Dynamic Metasurfaces Using Phase-Change Chalcogenides. Adv. Opt. Mater. 2019, 7, 1801709. [Google Scholar] [CrossRef]

- Feldmann, J.; Youngblood, N.; Wright, C.D.; Bhaskaran, H.; Pernice, W.H.P. All-Optical Spiking Neurosynaptic Networks with Self-Learning Capabilities. Nature 2019, 569, 208–214. [Google Scholar] [CrossRef]

- Cheng, Y.; Zhang, J.; Zhou, T.; Wang, Y.; Xu, Z.; Yuan, X.; Fang, L. Photonic Neuromorphic Architecture for Tens-of-Task Lifelong Learning. Light Sci. Appl. 2024, 13, 56. [Google Scholar] [CrossRef]

- Bandyopadhyay, S.; Sludds, A.; Krastanov, S.; Hamerly, R.; Harris, N.; Bunandar, D.; Streshinsky, M.; Hochberg, M.; Englund, D. Single-Chip Photonic Deep Neural Network with Forward-Only Training. Nat. Photonics 2024, 18, 1335–1343. [Google Scholar] [CrossRef]

- Shi, Y.; Ren, J.; Chen, G.; Liu, W.; Jin, C.; Guo, X.; Yu, Y.; Zhang, X. Nonlinear Germanium-Silicon Photodiode for Activation and Monitoring in Photonic Neuromorphic Networks. Nat. Commun. 2022, 13, 6048. [Google Scholar] [CrossRef] [PubMed]

- Ashtiani, F.; Geers, A.J.; Aflatouni, F. An On-Chip Photonic Deep Neural Network for Image Classification. Nature 2022, 606, 501–506. [Google Scholar] [CrossRef]

- Zheng, J.; Khanolkar, A.; Xu, P.; Colburn, S.; Deshmukh, S.; Myers, J.; Frantz, J.; Pop, E.; Hendrickson, J.; Doylend, J.; et al. GST-on-Silicon Hybrid Nanophotonic Integrated Circuits: A Non-Volatile Quasi-Continuously Reprogrammable Platform. Opt. Mater. Express 2018, 8, 1551. [Google Scholar] [CrossRef]

- Ríos, C.; Stegmaier, M.; Hosseini, P.; Wang, D.; Scherer, T.; Wright, C.D.; Bhaskaran, H.; Pernice, W.H.P. Integrated All-Photonic Non-Volatile Multi-Level Memory. Nat. Photonics 2015, 9, 725–732. [Google Scholar] [CrossRef]

- Delaney, M.; Zeimpekis, I.; Du, H.; Yan, X.; Banakar, M.; Thomson, D.J.; Hewak, D.W.; Muskens, O.L. Nonvolatile Programmable Silicon Photonics Using an Ultralow-Loss Sb2Se3 Phase Change Material. Sci. Adv. 2021, 7, 3500. [Google Scholar] [CrossRef] [PubMed]

- Minkenberg, C.; Krishnaswamy, R.; Zilkie, A.; Nelson, D. Co-packaged datacenter optics: Opportunities and challenges. IET Optoelectron. 2021, 15, 77–91. [Google Scholar] [CrossRef]

- Meade, R.; Ardalan, S.; Davenport, M.; Fini, J.; Sun, C.; Wade, M.; Wright-Gladstein, A.; Zhang, C. TeraPHY: A High-Density Electronic-Photonic Chiplet for Optical I/O from a Multi-Chip Module. In Proceedings of the Optical Fiber Communication Conference (OFC) 2019, San Diego, CA, USA, 3–7 March 2019; OSA: Washington, DC, USA, 2019; pp. 1–3. [Google Scholar]

- Brusberg, L.; Grenier, J.R.; Zakharian, A.R.; Yeary, L.W.; Seok, S.; Noh, J.; Kim, Y.; Matthies, J.; Terwilliger, C.C.; Paddock, B.J.; et al. Glass Platform for Co-Packaged Optics. IEEE J. Sel. Top. Quantum Electron. 2023, 29, 1–11. [Google Scholar] [CrossRef]

- Shi, Y.; Zhang, Y.; Wan, Y.; Yu, Y.; Zhang, Y.; Hu, X.; Xiao, X.; Xu, H.; Zhang, L.; Pan, B. Silicon Photonics for High-Capacity Data Communications. Photonics Res. 2022, 10, A106. [Google Scholar] [CrossRef]

- Razdan, S.; De Dobbelaere, P.; Xue, J.; Prasad, A.; Patel, V. Advanced 2.5D and 3D Packaging Technologies for next Generation Silicon Photonics in High Performance Networking Applications. In Proceedings of the 2022 IEEE 72nd Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 31 May 2022; IEEE: Piscataway, NJ, USA, 2022; pp. 428–435. [Google Scholar]

- Nair Gourikutty, S.B.; Wu, J.; Lim, T.G.; Sandra, S.; Jong, M.C.; Lai Yee, C.; Long, L.B.; Soon Wee Ho, D.; Choong, C.S.; Liang, D.; et al. A Compact Wafer-Level Heterogeneously Integrated Scalable Optical Transceiver for Data Centers. In Proceedings of the 2024 IEEE 74th Electronic Components and Technology Conference (ECTC), Denver, CO, USA, 28–31 May 2024; IEEE: Piscataway, NJ, USA, 2024; pp. 1398–1403. [Google Scholar]

- Yang, X.; Du, J.; Liu, J.; Wang, X.; Tang, N.; Shang, Y.; He, Z. 2.5D Optoelectronic Integration for 400G (8×56Gbps) CPO-Based Optical Interconnects. In Proceedings of the Asia Communications and Photonics Conference 2021, Shanghai, China, 24–27 October 2021; pp. 1–3. [Google Scholar]

- Fathololoumi, S.; Nguyen, K.; Mahalingam, H.; Sakib, M.; Li, Z.; Seibert, C.; Montazeri, M.; Chen, J.; Doylend, J.K.; Jayatilleka, H.; et al. 1.6Tbps Silicon Photonics Integrated Circuit for Co-Packaged Optical-IO Switch Applications. In Proceedings of the Optical Fiber Communication Conference (OFC) 2020, San Diego, CA, USA, 8–12 March 2020; Optica Publishing Group: Washington, DC, USA, 2020; pp. 1–3. [Google Scholar]

- Gourikutty, S.B.N.; Jong, M.C.; Kanna, C.V.; Ho, D.S.W.; Wu, J.; Mandal, R.; Li, N.; Lim, T.G.; Liow, J.T.-Y.; Bhattacharya, S. Towards Heterogeneous Integrated Electronic-Photonic Packages for Hyperscale Data Centers. In Proceedings of the 2021 IEEE 23rd Electronics Packaging Technology Conference (EPTC), Singapore, 7 December 2021; IEEE: Piscataway, NJ, USA, 2021; pp. 37–41. [Google Scholar]

- Hosseini, K.; Kok, E.; Shumarayev, S.Y.; Chiu, C.-P.; Sarkar, A.; Toda, A.; Ke, Y.; Chan, A.; Jeong, D.; Zhang, M.; et al. 8 Tbps Co-Packaged FPGA and Silicon Photonics Optical IO. In Proceedings of the Optical Fiber Communication Conference (OFC) 2021, San Francisco, CA, USA, 6–20 June 2021; Optica Publishing Group: Washington, DC, USA, 2021; pp. 1–3. [Google Scholar]

- Li, X.; Gourikutty, S.B.N.; Wu, J.; Lim, T.G.; Guo, P.; Davies, J.C.; Koh, E.S.C.; Lau, B.L.; Jong, M.C.; Chong, S.C.; et al. 1.6 Tbps FOWLP-Based Silicon Photonic Engine for Co-Packaged Optics. J. Light. Technol. 2025, 43, 1979–1986. [Google Scholar] [CrossRef]

- Lenihan, T.G.; Matthew, L.; Vardaman, E.J. Developments in 2.5D: The Role of Silicon Interposers. In Proceedings of the 2013 IEEE 15th Electronics Packaging Technology Conference (EPTC 2013), Singapore, 11–13 December 2013; pp. 53–55. [Google Scholar]

- Scott, G.J.; Bae, J.; Yang, K.; Ki, W.; Whitchurch, N.; Kelly, M.; Zwenger, C.; Jeon, J.; Hwang, T. Heterogeneous Integration Using Organic Interposer Technology. In Proceedings of the 2020 IEEE 70th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 3–30 June 2020; pp. 885–892. [Google Scholar]

- Jung, H.; Kim, N.; Choi, Y.; Kim, S.; Park, H.; Park, Y.; Chung, S.; Kang, J.; Kwon, J. 3D Printed Fanout Interposer Substrates with Curved Through-Holes for Rapid Prototyping of Advanced Packaging. In Proceedings of the 2025 IEEE 75th Electronic Components and Technology Conference (ECTC), Dallas, TX, USA, 27–30 May 2025; pp. 1167–1172. [Google Scholar]

- Prasad, A.; Muzio, C.; Ton, P.; Razdaan, S. Advanced 3D Packaging of 3.2Tbs Optical Engine for Co-Packaged Optics (CPO) in Hyperscale Data Center Networks. In Proceedings of the 2024 IEEE 74th Electronic Components and Technology Conference (ECTC), Denver, CO, USA, 28–31 May 2024; IEEE: Piscataway, NJ, USA, 2024; pp. 101–106. [Google Scholar]

- Margalit, N.; Xiang, C.; Bowers, S.M.; Bjorlin, A.; Blum, R.; Bowers, J.E. Perspective on the Future of Silicon Photonics and Electronics. Appl. Phys. Lett. 2021, 118, 220501. [Google Scholar] [CrossRef]

- Lu, M.-J.; Mu, S.-Y.; Cheng, C.-S.; Chen, J. Advanced Packaging Technologies for Copackaged Optics. In Proceedings of the 2022 IEEE 72nd Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 31 May–3 June 2022; IEEE: Piscataway, NJ, USA, 2022; pp. 38–42. [Google Scholar]

- Chai, T.C.; Zhang, X.; Lau, J.H.; Selvanayagam, C.S.; Damaruganath, P.; Hoe, Y.Y.G.; Ong, Y.Y.; Rao, V.S.; Wai, E.; Li, H.Y.; et al. Development of Large Die Fine-Pitch Cu/Low-k FCBGA Package with Through Silicon via (TSV) Interposer. IEEE Trans. Compon. Packag. Manufact. Technol. 2011, 1, 660–672. [Google Scholar] [CrossRef]

- Lee, J.C.; Kim, J.; Kim, K.W.; Ku, Y.J.; Kim, D.S.; Jeong, C.; Yun, T.S.; Kim, H.; Cho, H.S.; Oh, S.; et al. High Bandwidth Memory(HBM) with TSV Technique. In Proceedings of the 2016 International SoC Design Conference (ISOCC), Jeju, Republic of Korea, 23–26 October 2016; pp. 181–182. [Google Scholar]

- Khan, N.; Yoon, S.W.; Viswanath, A.G.K.; Ganesh, V.P.; Ranganathan, D.W.; Lim, S.; Vaidyanathan, K. Development of 3D Stack Package Using Silicon Interposer for High Power Application. In Proceedings of the 56th Electronic Components and Technology Conference 2006, San Diego, CA, USA, 30 May–2 June 2006; p. 5. [Google Scholar]

- Kumagai, K.; Yoneda, Y.; Izumino, H.; Shimojo, H.; Sunohara, M.; Kurihara, T.; Higashi, M.; Mabuchi, Y. A Silicon Interposer BGA Package with Cu-Filled TSV and Multi-Layer Cu-Plating Interconnect. In Proceedings of the 2008 58th Electronic Components and Technology Conference, Lake Buena Vista, FL, USA, 27–30 May 2008; pp. 571–576. [Google Scholar]

- Sunohara, M.; Tokunaga, T.; Kurihara, T.; Higashi, M. Silicon Interposer with TSVs (Through Silicon Vias) and Fine Multilayer Wiring. In Proceedings of the 2008 58th Electronic Components and Technology Conference, Lake Buena Vista, FL, USA, 27–30 May 2008; pp. 847–852. [Google Scholar]

- Abrams, N.C.; Cheng, Q.; Glick, M.; Jezzini, M.; Morrissey, P.; O’Brien, P.; Bergman, K. Silicon Photonic 2.5D Integrated Multi-Chip Module Receiver. In Proceedings of the Conference on Lasers and Electro-Optics, San Jose, CA, USA, 10–15 May 2020; Optica Publishing Group: Washington, DC, USA, 2020; pp. 1–2. [Google Scholar]

- He, H.; Xue, H.; Sun, Y.; Liu, F.; Cao, L. Design and Realization of Multi-Channel and High-Bandwidth 2.5D Transmitter Integrated With Silicon Photonic MZM. J. Light. Technol. 2022, 40, 5201–5215. [Google Scholar] [CrossRef]

- Thor, L.S.; Yu, L.H.; Chinq, J.M.; Ching, E.W.L.; Ang, T.Y.L.; Rong, O.J.; Kee, P.W.; Gandhi, A.; Eng, P.C.; Guan, L.T. Silicon Optical Interposer for EPIC 2.5D Integration. In Proceedings of the Asia Communications and Photonics Conference/International Conference on Information Photonics and Optical Communications 2020 (ACP/IPOC) (2020), Beijing, China, 24–27 October 2020; Optica Publishing Group: Washington, DC, USA, 2020; pp. 1–3. [Google Scholar]

- Muth, K.; Raghuraman, V.; Kannan, S.; Potluri, H. High Density Integration Technologies for SiPh Based Optical I/Os. In Proceedings of the 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2023; pp. 212–215. [Google Scholar]

- Thonnart, Y.; Bernabé, S.; Charbonnier, J.; Bernard, C.; Coriat, D.; Fuguet, C.; Tissier, P.; Charbonnier, B.; Malhouitre, S.; Saint-Patrice, D.; et al. POPSTAR: A Robust Modular Optical NoC Architecture for Chiplet-Based 3D Integrated Systems. In Proceedings of the 2020 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 9–13 March 2020; pp. 1456–1461. [Google Scholar]

- Tissier, P.; Charbonnier, J.; Vélard, R.; Ponthenier, F.; Farcy, A.; Boeuf, F.; Bernabé, S.; Charbonnier, B.; Broquin, J.-E. Co-Integration of TSV Mid Process and Optical Devices for Silicon Photonics Interposers. In Proceedings of the 2020 IEEE 8th Electronics System-Integration Technology Conference (ESTC), Tønsberg, Norway, 15–18 September 2020; pp. 1–5. [Google Scholar]

- Kim, D.-W.; Yu, L.H.; Chang, K.F.; Woon Leng, L.; Ser Choong, C.; Hong, C.; Bhattacharya, S. 3D System-on-Packaging Using Through Silicon Via on SOI for High-Speed Optcal Interconnections with Silicon Photonics Devices for Application of 400 Gbps and Beyond. In Proceedings of the 2018 IEEE 68th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 29 May–1 June 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 834–840. [Google Scholar]

- Zheng, Q.; Yang, P.; Xue, H.; He, H.; Cao, R.; Dai, F.; Sun, S.; Liu, F.; Wang, Q.; Cao, L.; et al. Research on 3D Optical Module Integrating Edge Coupler and TSV. J. Light. Technol. 2022, 40, 6190–6200. [Google Scholar] [CrossRef]

- Yeary, L.; Brusberg, L.; Kim, C.; Seok, S.-H.; Noh, J.; Rozenvax, A. Co-Packaged Optics on Glass Substrates for 102.4 Tb/s Data Center Switches. In Proceedings of the 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2023; pp. 224–227. [Google Scholar]

- Kang, E.K.; Jung, S.-Y.; Kwon, S.; Kang, H.C.; Kwon, W.-B.; Kim, M.; Cho, G.-S.; Moon, D.W.; Lee, J. Through-Glass-Via Interposer for High-Speed Electrical Interfacing in a 400 Gbps Optical Engine for On-Board Optics and Pluggable Optical Transceivers. J. Light. Technol. 2025, 43, 5390–5399. [Google Scholar] [CrossRef]

- Aoki, T.; Sekiguchi, S.; Simoyama, T.; Tanaka, S.; Nishizawa, M.; Hatori, N.; Sobu, Y.; Sugama, A.; Akiyama, T.; Hayakawa, A.; et al. Low-Crosstalk Simultaneous 16-Channel × 25 Gb/s Operation of High-Density Silicon Photonics Optical Transceiver. J. Light. Technol. 2018, 36, 1262–1267. [Google Scholar] [CrossRef]

- Lin, P.-Y.; Chen, C.-H.; Yan, K.; He, J. Analysis of Package-to-System Interaction on Thermal Performance of Large 2.5D Packages Using 3DFabric® Platform. In Proceedings of the 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2023; pp. 918–922. [Google Scholar]

- Yu, D.C.H.; Wang, C.-T.; Hsia, H. Foundry Perspectives on 2.5D/3D Integration and Roadmap. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021; pp. 3.7.1–3.7.4. [Google Scholar]

- Lee, C.-H.; Hu, Y.; Chen, S.; Lai, C.; Liu, M.; Chen, H.; Lin, J.; Yew, M.; Hsu, C.; Chiu, M.; et al. Next Generation Large Size High Interconnect Density CoWoS-R Package. In Proceedings of the 2024 IEEE 74th Electronic Components and Technology Conference (ECTC), Denver, CO, USA, 28–31 May 2024; pp. 259–263. [Google Scholar]

- Yan, K.; Hu, Y.-H.; Lee, C.-H.; Chen, H.-Y.; Liu, M.-S.; Chen, E.; Yew, M.C.; Hsu, C.K.; Jeng, S.-P.; He, J. Fine Pitch High Density CoWoS-R Package with 1.4/1.4um RDL Lines and 3um via CD. In Proceedings of the 2025 IEEE 75th Electronic Components and Technology Conference (ECTC), Dallas, TX, USA, 27–30 May 2025; pp. 246–250. [Google Scholar]

- Hu, Y.-H.; Lee, C.-H.; Peng, J.-S.; Chen, H.-Y.; Lee, P.-H.; Li, J.; Shieh, J.; Chen, E.; Yew, M.C.; Jeng, S.-P.; et al. Package Warpage Reduction for Large CoWoS-R Packages. In Proceedings of the 2025 IEEE 75th Electronic Components and Technology Conference (ECTC), Dallas, TX, USA, 27–30 May 2025; pp. 116–121. [Google Scholar]

- Wu, T.-Y.; Chang, K.-C.; Wang, C.-C.; Wu, B.-L.; Wang, C.; Yan, K.; Lee, C.-H.; Hsieh, C.-C.; Lu, J.-R.; Song, R.-W.; et al. Integrated Package-to-System Thermal Solution Evolution for High-Performance 2.5D CoWoS-R Advanced Packaging Technology Development. In Proceedings of the 2025 IEEE 75th Electronic Components and Technology Conference (ECTC), Dallas, TX, USA, 27–30 May 2025; pp. 481–486. [Google Scholar]

- Lien, Y.-J.; Jiang, S.-D.; Hsieh, C.-C.; Chia, H.-J.; Wu, T.; Lin, C.-C.; Shen, K.-H.; Lu, S.-W.; Yan, K.; Yee, K.-C.; et al. Direct-to-Silicon Liquid Cooling Integrated on Cowos® Platform. In Proceedings of the 2025 IEEE 75th Electronic Components and Technology Conference (ECTC), Dallas, TX, USA, 27–30 May 2025; pp. 743–747. [Google Scholar]

- Duan, G.; Zhang, Y.; Gunawan, A.; Fang, Y.; Mousavi, J.; Apte, A.A.; Ahmed, N.; Sharma, S.; Alur, S.; Chandolu, A.; et al. EMIB-T (TSV) Advanced Packaging Technology EMIB’s Next Evolution. In Proceedings of the 2025 IEEE 75th Electronic Components and Technology Conference (ECTC), Dallas, TX, USA, 27–30 May 2025; pp. 254–258. [Google Scholar]

- Li, W.; Eid, F.; Vyatskikh, A.; Vreeland, R.; Brezinski, W.; Njuki, M.; Jezewski, C.; Mongia, R.; Valavala, K.; Mei, H.; et al. Wafer-to-Wafer Bonding with Ultralow Thermal Resistance and High Bonding Energy. In Proceedings of the 2025 IEEE 75th Electronic Components and Technology Conference (ECTC), Dallas, TX, USA, 27–30 May 2025; pp. 79–82. [Google Scholar]

- Naderi, G.; Elsherbini, A.; Rawlings, B.M.; Liff, S.; Chauhan, S.; Yu, Q.; Rahimi, A.; Cooper, C.; Bejitual, T.; Shivapooja, P.; et al. Enabling Chip-To-Wafer Hybrid Bonding Scaling to 1Um Pitch With Optimal Power Delivery Using New Bond Via Architectures. In Proceedings of the 2025 IEEE 75th Electronic Components and Technology Conference (ECTC), Dallas, TX, USA, 27–30 May 2025; pp. 20–24. [Google Scholar]

- Uemura, H.; Misawa, T.; Mizuno, Y.; Itabashi, N.; Arao, H.; Nakanishi, T.; Tanaka, K.; Sano, T.; Uesaka, K.; Miyairi, M.; et al. A Surface-Mount Photonic Package with a Photonic-Wire-Bonded Glass Interposer as a Hybrid Integration Platform for Co-Packaged Optics. In Proceedings of the 2024 IEEE 74th Electronic Components and Technology Conference (ECTC), Denver, CO, USA, 28–31 May 2024; IEEE: Piscataway, NJ, USA, 2024; pp. 90–95. [Google Scholar]

- Seok, S.-H.; Kong, B.-K.; Brusberg, L.; Yeary, L.W.; Noh, J.-H.; Lee, H.-K.; Choi, K.-G.; Levesque, D.W. Advanced Glass Substrate Fabrication and Metallization Process Technology for Co-Packaged Optics. In Proceedings of the 2025 IEEE 75th Electronic Components and Technology Conference (ECTC), Dallas, TX, USA, 27–30 May 2025; pp. 337–340. [Google Scholar]

- Radhakrishnan, K.; Swaminathan, M.; Bhattacharyya, B.K. Power Delivery for High-Performance Microprocessors—Challenges, Solutions, and Future Trends. IEEE Trans. Compon. Packag. Manuf. Technol. 2021, 11, 655–671. [Google Scholar] [CrossRef]

- Khorasani, R.R.; Li, X.; Al-Juwhari, M.; Murti, W.; Cha, J.; Swaminathan, M. Embedded Silicon Chip Capacitors in Glass Package for Vertical Power Delivery. In Proceedings of the 2025 IEEE 75th Electronic Components and Technology Conference (ECTC), Dallas, TX, USA, 27–30 May 2025; pp. 416–423. [Google Scholar]

- Carroll, L.; Lee, J.-S.; Scarcella, C.; Gradkowski, K.; Duperron, M.; Lu, H.; Zhao, Y.; Eason, C.; Morrissey, P.; Rensing, M.; et al. Photonic Packaging: Transforming Silicon Photonic Integrated Circuits into Photonic Devices. Appl. Sci. 2016, 6, 426. [Google Scholar] [CrossRef]

- Lee, J.; Kim, J. Improved Through-Plane Thermal Conductivity of 3D Structured Composites via BN Alignment and AlN Surface Modification. Compos. Commun. 2021, 28, 100935. [Google Scholar] [CrossRef]

- Wang, Z.; Wang, X.; Sun, M.; Liang, L.; Yang, H.; Li, Y.; Yang, K. Enhance the Thermal Conductivity and Maintain Insulation Property of Epoxy via Constructing a Three-Dimensional Network by Doping Hexagonal Boron Nitride and Carbon Nanofiber. J. Mater. Sci. Mater. Electron. 2021, 32, 28840–28855. [Google Scholar] [CrossRef]

- Zhang, H.; Zhou, Z.; Wu, M.; Cai, Y.; Yu, M.; Lin, T. Thermal Modeling and Design of 3D Memory Stack on Processor with Thermal Bridge Structure. In Proceedings of the 2020 21st International Conference on Electronic Packaging Technology (ICEPT), Guangzhou, China, 12–15 August 2020; IEEE: Piscataway, NJ, USA, 2020; pp. 1–6. [Google Scholar]

- Deng, Y.; Liu, P.; Zhang, Z.; Jin, J.; Xu, P.; Yan, L. 3D Package Thermal Analysis and Thermal Optimization. Case Stud. Therm. Eng. 2024, 64, 105465. [Google Scholar] [CrossRef]

- Liu, Z.; Jiang, H.; Zhu, Z.; Chen, L.; Sun, Q.; Sun, Y.; Zhang, D.W. Thermal–Mechanical and Signal Reliability of a New Differentiated TSV. IEEE Trans. Electron Devices 2022, 69, 5766–5772. [Google Scholar] [CrossRef]

- Xiong, J.; Hsiang, E.-L.; He, Z.; Zhan, T.; Wu, S.-T. Augmented Reality and Virtual Reality Displays: Emerging Technologies and Future Perspectives. Light Sci. Appl. 2021, 10, 216. [Google Scholar] [CrossRef]

- Li, L.; Kong, W.; Chen, F. Femtosecond Laser-Inscribed Optical Waveguides in Dielectric Crystals: A Concise Review and Recent Advances. Adv. Photonics 2022, 4, 024002. [Google Scholar] [CrossRef]

- Davis, K.M.; Miura, K.; Sugimoto, N.; Hirao, K. Writing Waveguides in Glass with a Femtosecond Laser. Opt. Lett. 1996, 21, 1729. [Google Scholar] [CrossRef]

- Thiel, M.; Flachenecker, G.; Schade, W. Femtosecond Laser Writing of Bragg Grating Waveguide Bundles in Bulk Glass. Opt. Lett. 2015, 40, 1266. [Google Scholar] [CrossRef] [PubMed]

- Lancry, M.; Poumellec, B.; Canning, J.; Cook, K.; Poulin, J.-C.; Brisset, F. Ultrafast Nanoporous Silica Formation Driven by Femtosecond Laser Irradiation. Laser Photonics Rev. 2013, 7, 953–962. [Google Scholar] [CrossRef]

- Poumellec, B.; Lancry, M.; Chahid-Erraji, A.; Kazansky, P.G. Modification Thresholds in Femtosecond Laser Processing of Pure Silica: Review of Dependencies on Laser Parameters [Invited]. Opt. Mater. Express 2011, 1, 766. [Google Scholar] [CrossRef]

- Zhong, L.; Wang, Y.; Tan, D.; Qiu, J. Toward 3D Integration of Highly See-Through Photonic Circuits in Glass. Laser Photonics Rev. 2023, 17, 2200767. [Google Scholar] [CrossRef]

- Wang, Y.; Zhong, L.; Lau, K.Y.; Han, X.; Yang, Y.; Hu, J.; Firstov, S.; Chen, Z.; Ma, Z.; Tong, L.; et al. Precise Mode Control of Laser-Written Waveguides for Broadband, Low-Dispersion 3D Integrated Optics. Light Sci. Appl. 2024, 13, 130. [Google Scholar] [CrossRef]

- Chen, D.; Chen, Z.; Yang, Y.; Wang, Y.; Han, X.; Lau, K.Y.; Wu, Z.; Zou, C.; Zhang, Y.; Xu, B.; et al. 3D Laser Writing of Low-Loss Cross-Section-Variable Type-I Optical Waveguide Passive/Active Integrated Devices in Single Crystals. Adv. Mater. 2024, 36, 2404493. [Google Scholar] [CrossRef]

- Dupont, A.; Leonov, S.; Guérineau, T.; Messaddeq, Y.; Lapointe, J.; Vallée, R. Lasing in a Femtosecond-Laser-Written Single-Scan Waveguide Fabricated in Tm-Doped BGG Glass. Opt. Lett. 2025, 50, 666–669. [Google Scholar] [CrossRef]

- Lee, T.; Sun, Q.; Beresna, M.; Brambilla, G. Low Bend Loss Femtosecond Laser Written Waveguides Exploiting Integrated Microcrack. Sci. Rep. 2021, 11, 23770. [Google Scholar] [CrossRef]

- Sun, B.; Morozko, F.; Salter, P.S.; Moser, S.; Pong, Z.; Patel, R.B.; Walmsley, I.A.; Wang, M.; Hazan, A.; Barré, N.; et al. On-Chip Beam Rotators, Adiabatic Mode Converters, and Waveplates through Low-Loss Waveguides with Variable Cross-Sections. Light Sci. Appl. 2022, 11, 214. [Google Scholar] [CrossRef]

- Tang, G.; Zhang, D.; Zhang, F.; Zhao, W.; Qian, Q.; Yang, Z. Structure and Luminescence Properties of Tm3+ Doped Barium Gallo-Germanate Glass Tailored by Lu2O3. J. Lumin. 2023, 257, 119771. [Google Scholar] [CrossRef]

- Tan, M.; Xu, J.; Liu, S.; Feng, J.; Zhang, H.; Yao, C.; Chen, S.; Guo, H.; Han, G.; Wen, Z.; et al. Co-Packaged Optics (CPO): Status, Challenges, and Solutions. Front. Optoelectron. 2023, 16, 1. [Google Scholar] [CrossRef] [PubMed]

- Izawa, T.; Nakagome, H.; Kimura, T. Optical Waveguides Formed by Electrically Induced Migration of Ions in Glass Plates. IEEE J. Quantum Electron. 1972, 8, 545–546. [Google Scholar] [CrossRef]

- Hao, Y. Experiments and Analysis on Joule Heating Effect in Field-Assisted Ion Diffusion. Opt. Eng. 2012, 51, 014601. [Google Scholar] [CrossRef]

- Pei, C.; Yang, L.; Wang, G.; Wang, Y.; Jiang, X.; Hao, Y.; Li, Y.; Yang, J. Broadband Graphene/Glass Hybrid Waveguide Polarizer. IEEE Photonics Technol. Lett. 2015, 27, 927–930. [Google Scholar] [CrossRef]

- Hao, Y.; Liu, J.; Che, L.; Wang, S.; Meng, H.; Liu, X. Buried Optical Waveguide in Photo-Thermo-Refractive Glass by Ion Exchange Technology. IEEE Photonics Technol. Lett. 2023, 35, 793–796. [Google Scholar] [CrossRef]

- Brusberg, L.; Dejneka, M.J.; Okoro, C.A.; McEnroe, D.J.; Zakharian, A.R.; Terwilliger, C.C. Ultra Low-Loss Ion-Exchange Waveguides in Optimized Alkali Glass for Co-Packaged Optics. In Proceedings of the 2024 IEEE 74th Electronic Components and Technology Conference (ECTC), Denver, CO, USA, 28–31 May 2024; IEEE: Piscataway, NJ, USA, 2024; pp. 85–89. [Google Scholar]

- Brusberg, L.; Bigongiari, A.; Yeary, L.W.; Grenier, J.R.; Nisic, B.; Stracca, S.; Terwilliger, C.C.; Clark, J.S. Integrated Glass Waveguide Circuit for Co-Packaged Optics in Radio-Access Networks. In Proceedings of the 2025 Optical Fiber Communications Conference and Exhibition (OFC), San Francisco, CA, USA, 30 March–3 April 2025; pp. 1–3. [Google Scholar]

- Brusberg, L.; Johnson, B.J.; Herbst, C.; Grenier, J.R.; Dejneka, M.J.; Terwilliger, C.C.; Schwietering, J.; Schröder, H. Large-Scale Glass Waveguide Circuit for Board-Level Optical Interconnects Between Faceplate and Co-Packaged Optical Transceivers. In Proceedings of the 2025 IEEE 75th Electronic Components and Technology Conference (ECTC), Dallas, TX, USA, 27–30 May 2025; IEEE: Piscataway, NJ, USA, 2025; pp. 59–63. [Google Scholar]

- Al-Shami, H.; Schwietering, J.; Schröder, H. Automated Highspeed Characterization of Optical Waveguides in Large-Format Glass Substrates. In Proceedings of the 2024 IEEE 10th Electronics System-Integration Technology Conference (ESTC), Berlin, Germany, 11–13 September 2024; pp. 1–4. [Google Scholar]

- Dai, D.; Li, C.; Wang, S.; Wu, H.; Shi, Y.; Wu, Z.; Gao, S.; Dai, T.; Yu, H.; Tsang, H.-K. 10-Channel Mode (de)Multiplexer with Dual Polarizations. Laser Photonics Rev. 2018, 12, 1700109. [Google Scholar] [CrossRef]

- Shen, W.; Zeng, P.; Yang, Z.; Xia, D.; Du, J.; Zhang, B.; Xu, K.; He, Z.; Li, Z. Chalcogenide Glass Photonic Integration for Improved 2 Μm Optical Interconnection. Photonics Res. 2020, 8, 1484–1490. [Google Scholar] [CrossRef]

- Richardson, D.J.; Fini, J.M.; Nelson, L.E. Space-Division Multiplexing in Optical Fibres. Nat. Photonics 2013, 7, 354–362. [Google Scholar] [CrossRef]

- Dai, D.; Zhao, W.; Liu, D. Multimode Silicon Photonics Devices. In Proceedings of the 26th Optoelectronics and Communications Conference (2021), Hong Kong, 3–7 July 2021; Optica Publishing Group: Washington, DC, USA, 2021; pp. 1–3. [Google Scholar]

- Dai, D.; Bowers, J.E. Silicon-Based on-Chip Multiplexing Technologies and Devices for Peta-Bit Optical Interconnects. Nanophotonics 2014, 3, 283–311. [Google Scholar] [CrossRef]

- Liu, Y.; Xu, K.; Wang, S.; Shen, W.; Xie, H.; Wang, Y.; Xiao, S.; Yao, Y.; Du, J.; He, Z.; et al. Arbitrarily Routed Mode-Division Multiplexed Photonic Circuits for Dense Integration. Nat. Commun. 2019, 10, 3263. [Google Scholar] [CrossRef]

- Koonen, A.M.J.; Chen, H.; van den Boom, H.P.A.; Raz, O. Silicon Photonic Integrated Mode Multiplexer and Demultiplexer. IEEE Photonics Technol. Lett. 2012, 24, 1961–1964. [Google Scholar] [CrossRef]

- Shen, W.; Du, J.; Xiong, J.; Ma, L.; He, Z. Silicon-Integrated Dual-Mode Fiber-to-Chip Edge Coupler for 2 × 100 Gbps/Lambda MDM Optical Interconnection. Opt. Express 2020, 28, 33254–33262. [Google Scholar] [CrossRef]

- Cao, X.; Li, K.; Wan, Y.; Wang, J. Efficient Mode Coupling between a Few-Mode Fiber and Multi-Mode Photonic Chip with Low Crosstalk. Opt. Express 2022, 30, 22637–22648. [Google Scholar] [CrossRef]

- Li, K.; Cao, X.; Wang, J. Broadband and Efficient Multi-Mode Fiber-Chip Edge Coupler on a Silicon Platform Assisted with a Nano-Slot Waveguide. Opt. Express 2022, 30, 47249–47263. [Google Scholar] [CrossRef] [PubMed]

- Buscaino, B.; Kahn, J.M.; Taylor, B.D. Coherent Co-Packaged Optical Interfaces for Next-Generation Electrical Switches. In Proceedings of the 2019 IEEE Photonics Conference (IPC), San Antonio, TX, USA, 29 September–3 October 2019; pp. 1–2. [Google Scholar]

- Papatryfonos, K.; Selviah, D.R.; Maman, A.; Hasharoni, K.; Brimont, A.; Zanzi, A.; Kraft, J.; Sidorov, V.; Seifried, M.; Baumgartner, Y.; et al. Co-Package Technology Platform for Low-Power and Low-Cost Data Centers. Appl. Sci. 2021, 11, 6098. [Google Scholar] [CrossRef]

- Vermeulen, D.; Selvaraja, S.; Verheyen, P.; Lepage, G.; Bogaerts, W.; Absil, P.; Thourhout, D.V.; Roelkens, G. High-Efficiency Fiber-to-Chip Grating Couplers Realized Using an Advanced CMOS-Compatible Silicon-On-Insulator Platform. Opt. Express 2010, 18, 18278–18283. [Google Scholar] [CrossRef]

- Mu, X.; Wu, S.; Cheng, L.; Fu, H.Y. Edge Couplers in Silicon Photonic Integrated Circuits: A Review. Appl. Sci. 2020, 10, 1538. [Google Scholar] [CrossRef]

- Du, Y.; Wang, F.; Hong, Z.; Shi, Y.; Chen, X.; Zheng, X. Detachable Interface toward a Low-Loss Reflow-Compatible Fiber Coupling for Co-Packaged Optics (CPO). Opt. Express 2023, 31, 1318. [Google Scholar] [CrossRef]

- Bian, Y.; Ramachandran, K.; Wu, Z.-J.; Hedrick, B.; Dezfulian, K.K.; Houghton, T.; Nummy, K.; Fisher, D.W.; Hirokawa, T.; Donegan, K.; et al. 3D Integrated Laser Attach Technology on a 300-Mm Monolithic CMOS Silicon Photonics Platform. IEEE J. Sel. Top. Quantum Electron. 2023, 29, 8200519. [Google Scholar] [CrossRef]

- Mizuno, Y.; Kobayashi, K.; Nakamura, S.; Migita, M.; Arao, H.; Nakanishi, T.; Uemura, H.; Tanaka, K.; Uesaka, K.; Miyairi, M.; et al. Flip-Chip Photonic-Electronic Integration Platform for Co-Packaged Optics Using a Glass Substrate with Vertically-Coupled Beam Expanding Lens. In Proceedings of the 2025 IEEE 75th Electronic Components and Technology Conference (ECTC), Dallas, TX, USA, 27–30 May 2025; pp. 48–53. [Google Scholar]

- Jang, H.-S.; Heo, H.; Kim, S.; Hwang, H.; Lee, H.; Seo, M.-K.; Kwon, H.; Han, S.-W.; Jung, H. Fabrication of a 3D Mode Size Converter for Efficient Edge Coupling in Photonic Integrated Circuits. Opt. Express 2025, 33, 6909–6917. [Google Scholar] [CrossRef]

- Billah, M.R.; Blaicher, M.; Hoose, T.; Dietrich, P.-I.; Marin-Palomo, P.; Lindenmann, N.; Nesic, A.; Hofmann, A.; Troppenz, U.; Moehrle, M.; et al. Hybrid Integration of Silicon Photonics Circuits and InP Lasers by Photonic Wire Bonding. Optica 2018, 5, 876. [Google Scholar] [CrossRef]

- Blaicher, M.; Billah, M.R.; Kemal, J.; Hoose, T.; Marin-Palomo, P.; Hofmann, A.; Kutuvantavida, Y.; Kieninger, C.; Dietrich, P.-I.; Lauermann, M.; et al. Hybrid Multi-Chip Assembly of Optical Communication Engines by in Situ 3D Nano-Lithography. Light Sci. Appl. 2020, 9, 71. [Google Scholar] [CrossRef] [PubMed]

- Yu, S.; Ranno, L.; Du, Q.; Serna, S.; McDonough, C.; Fahrenkopf, N.; Gu, T.; Hu, J. Free-Form Micro-Optics Enabling Ultra-Broadband Low-Loss Off-Chip Coupling. Laser Photonics Rev. 2023, 17, 2200025. [Google Scholar] [CrossRef]

- Nambiar, S.; Ranganath, P.; Kallega, R.; Selvaraja, S.K. High Efficiency DBR Assisted Grating Chirp Generators for Silicon Nitride Fiber-Chip Coupling. Sci. Rep. 2019, 9, 18821. [Google Scholar] [CrossRef] [PubMed]

- Lomonte, E.; Stappers, M.; Krämer, L.; Pernice, W.H.P.; Lenzini, F. Scalable and Efficient Grating Couplers on Low-Index Photonic Platforms Enabled by Cryogenic Deep Silicon Etching. Sci. Rep. 2024, 14, 4256. [Google Scholar] [CrossRef] [PubMed]

- Shekhar, S.; Bogaerts, W.; Chrostowski, L.; Bowers, J.E.; Hochberg, M.; Soref, R.; Shastri, B.J. Roadmapping the next Generation of Silicon Photonics. Nat. Commun. 2024, 15, 751. [Google Scholar] [CrossRef]

- Shekhar, S. Silicon Photonics: A Brief Tutorial. IEEE Solid-State Circuits Mag. 2021, 13, 22–32. [Google Scholar] [CrossRef]

- Li, J.; Lee, H.; Vahala, K.J. Microwave Synthesizer Using an On-Chip Brillouin Oscillator. Nat. Commun. 2013, 4, 2097. [Google Scholar] [CrossRef]

- Ran, S.; Zhou, G.; Li, Y.; Lu, L.; Tang, N.; Liu, F.; Chen, J.; Zhou, L. Micro-Ring Modulators With Integrated Inductor to Mitigate Bandwidth and Extinction Ratio Trade-Off. IEEE Photonics Technol. Lett. 2024, 36, 231–234. [Google Scholar] [CrossRef]

- Yuan, Y.; Peng, Y.; Sorin, W.V.; Cheung, S.; Huang, Z.; Liang, D.; Fiorentino, M.; Beausoleil, R.G. A 5 × 200 Gbps Microring Modulator Silicon Chip Empowered by Two-Segment Z-Shape Junctions. Nat. Commun. 2024, 15, 918. [Google Scholar] [CrossRef]

- Jayatilleka, H.; Frish, H.; Kumar, R.; Heck, J.; Ma, C.; Sakib, M.N.; Huang, D.; Rong, H. Post-Fabrication Trimming of Silicon Photonic Ring Resonators at Wafer-Scale. J. Light. Technol. 2021, 39, 5083–5088. [Google Scholar] [CrossRef]

- Zhang, W.; Ebert, M.; Li, K.; Chen, B.; Yan, X.; Du, H.; Banakar, M.; Tran, D.T.; Littlejohns, C.G.; Scofield, A.; et al. Harnessing Plasma Absorption in Silicon MOS Ring Modulators. Nat. Photonics 2023, 17, 273–279. [Google Scholar] [CrossRef]

- Chan, D.W.U.; Wu, X.; Lu, C.; Lau, A.P.T.; Tsang, H.K. Efficient 330-Gb/s PAM-8 Modulation Using Silicon Microring Modulators. Opt. Lett. 2023, 48, 1036. [Google Scholar] [CrossRef]

- Zhang, Y.; Zhang, H.; Zhang, J.; Liu, J.; Wang, L.; Chen, D.; Chi, N.; Xiao, X.; Yu, S. 240 Gb/s Optical Transmission Based on an Ultrafast Silicon Microring Modulator. Photonics Res. 2022, 10, 1127. [Google Scholar] [CrossRef]

- Cheng, Q.; Rumley, S.; Bahadori, M.; Bergman, K. Photonic Switching in High Performance Datacenters [Invited]. Opt. Express 2018, 26, 16022–16043. [Google Scholar] [CrossRef]

- Shen, Y.; Harris, N.C.; Skirlo, S.; Prabhu, M.; Baehr-Jones, T.; Hochberg, M.; Sun, X.; Zhao, S.; Larochelle, H.; Englund, D.; et al. Deep Learning with Coherent Nanophotonic Circuits. Nat. Photonics 2017, 11, 441–446. [Google Scholar] [CrossRef]

- Arrazola, J.M.; Bergholm, V.; Brádler, K.; Bromley, T.R.; Collins, M.J.; Dhand, I.; Fumagalli, A.; Gerrits, T.; Goussev, A.; Helt, L.G.; et al. Quantum Circuits with Many Photons on a Programmable Nanophotonic Chip. Nature 2021, 591, 54–60. [Google Scholar] [CrossRef] [PubMed]

- Strukov, D.B.; Snider, G.S.; Stewart, D.R.; Williams, R.S. The Missing Memristor Found. Nature 2008, 453, 80–83. [Google Scholar] [CrossRef]

- Lee, J.; Lu, W.D. On-Demand Reconfiguration of Nanomaterials: When Electronics Meets Ionics. Adv. Mater. 2018, 30, 1702770. [Google Scholar] [CrossRef] [PubMed]

- Ielmini, D. Brain-Inspired Computing with Resistive Switching Memory (RRAM): Devices, Synapses and Neural Networks. Microelectron. Eng. 2018, 190, 44–53. [Google Scholar] [CrossRef]

- Gong, G.; Zhou, Y.; Xiong, Z.; Sun, T.; Li, H.; Li, Q.; Zhao, W.; Zhang, G.; Zhai, Y.; Lv, Z.; et al. An Antagonistic Photovoltaic Memristor for Bioinspired Active Contrast Adaptation. Adv. Mater. 2024, 36, 2409844. [Google Scholar] [CrossRef]

- Jarvis, S.E.; Zamponi, G.W. Interactions between Presynaptic Ca2+ Channels, Cytoplasmic Messengers and Proteins of the Synaptic Vesicle Release Complex. Trends Pharmacol. Sci. 2001, 22, 519–525. [Google Scholar] [CrossRef]

- Dolphin, A.C.; Lee, A. Presynaptic Calcium Channels: Specialized Control of Synaptic Neurotransmitter Release. Nat. Rev. Neurosci. 2020, 21, 213–229. [Google Scholar] [CrossRef]

- Amin, R.; Maiti, R.; Gui, Y.; Suer, C.; Miscuglio, M.; Heidari, E.; Chen, R.T.; Dalir, H.; Sorger, V.J. Sub-Wavelength GHz-Fast Broadband ITO Mach–Zehnder Modulator on Silicon Photonics. Optica 2020, 7, 333–335. [Google Scholar] [CrossRef]

- Li, G.; Krishnamoorthy, A.V.; Shubin, I.; Yao, J.; Luo, Y.; Thacker, H.; Zheng, X.; Raj, K.; Cunningham, J.E. Ring Resonator Modulators in Silicon for Interchip Photonic Links. IEEE J. Sel. Top. Quantum Electron. 2013, 19, 95–113. [Google Scholar] [CrossRef]

- Alexoudi, T.; Kanellos, G.T.; Pleros, N. Optical RAM and Integrated Optical Memories: A Survey. Light Sci. Appl. 2020, 9, 91. [Google Scholar] [CrossRef]

- Wu, C.; Yu, H.; Li, H.; Zhang, X.; Takeuchi, I.; Li, M. Low-Loss Integrated Photonic Switch Using Subwavelength Patterned Phase Change Material. ACS Photonics 2019, 6, 87–92. [Google Scholar] [CrossRef]

- Li, P.; Yang, X.; Maß, T.W.W.; Hanss, J.; Lewin, M.; Michel, A.-K.U.; Wuttig, M.; Taubner, T. Reversible Optical Switching of Highly Confined Phonon–Polaritons with an Ultrathin Phase-Change Material. Nat. Mater 2016, 15, 870–875. [Google Scholar] [CrossRef] [PubMed]

- Meng, J.; Gui, Y.; Nouri, B.M.; Ma, X.; Zhang, Y.; Popescu, C.-C.; Kang, M.; Miscuglio, M.; Peserico, N.; Richardson, K.; et al. Electrical Programmable Multilevel Nonvolatile Photonic Random-Access Memory. Light Sci. Appl. 2023, 12, 189. [Google Scholar] [CrossRef] [PubMed]

- Chen, R.; Fang, Z.; Perez, C.; Miller, F.; Kumari, K.; Saxena, A.; Zheng, J.; Geiger, S.J.; Goodson, K.E.; Majumdar, A. Non-Volatile Electrically Programmable Integrated Photonics with a 5-Bit Operation. Nat. Commun. 2023, 14, 3465. [Google Scholar] [CrossRef] [PubMed]

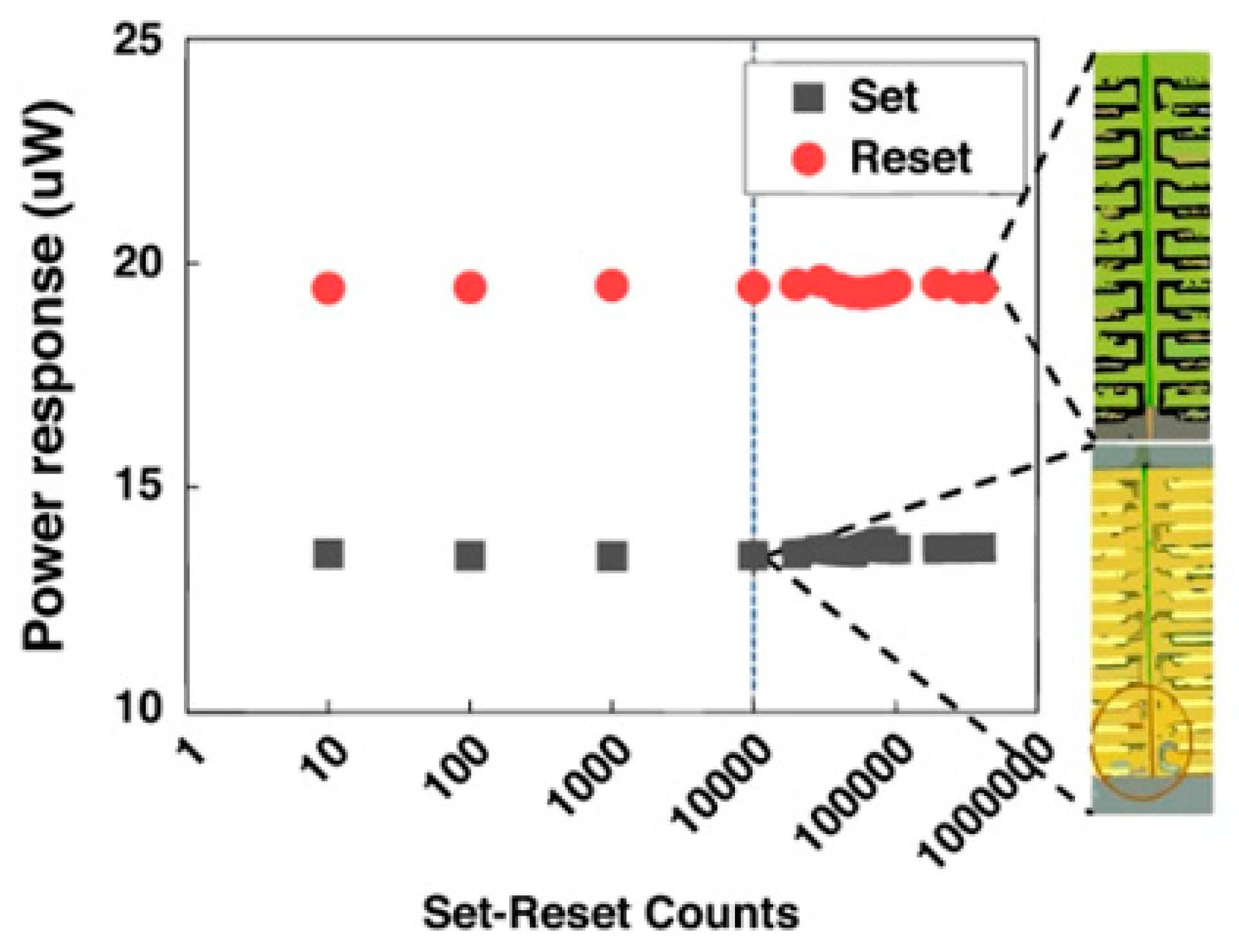

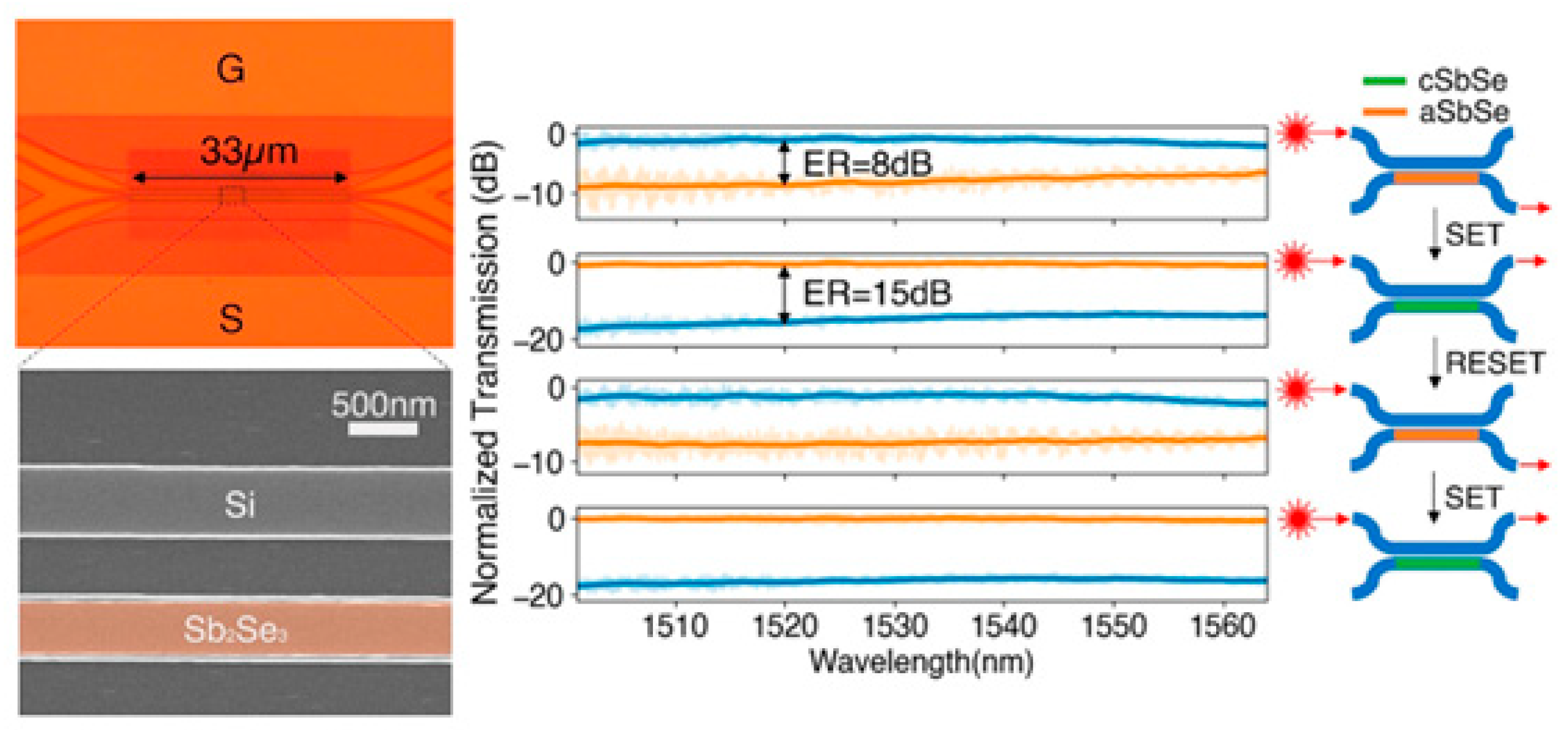

- Delaney, M.; Zeimpekis, I.; Lawson, D.; Hewak, D.W.; Muskens, O.L. A New Family of Ultralow Loss Reversible Phase-Change Materials for Photonic Integrated Circuits: Sb2S3 and Sb2Se3. Adv. Funct. Mater. 2020, 30, 2002447. [Google Scholar] [CrossRef]

- Fang, Z.; Mills, B.; Chen, R.; Zhang, J.; Xu, P.; Hu, J.; Majumdar, A. Arbitrary Programming of Racetrack Resonators Using Low-Loss Phase-Change Material Sb2Se3. Nano Lett. 2023, 24, 97–103. [Google Scholar] [CrossRef]

- Fang, Z.; Chen, R.; Zheng, J.; Khan, A.I.; Neilson, K.M.; Geiger, S.J.; Callahan, D.M.; Moebius, M.G.; Saxena, A.; Chen, M.E.; et al. Ultra-Low-Energy Programmable Non-Volatile Silicon Photonics Based on Phase-Change Materials with Graphene Heaters. Nat. Nanotechnol. 2022, 17, 842–848. [Google Scholar] [CrossRef]

- Yang, X.; Ran, S.; Li, Z.; Lu, L.; Li, Y.; Wai, N.P.; Zhang, M.; Lo, G.-Q.; Chen, J.; Zhou, L. Field Programmable Silicon Microring WDM Transceiver Leveraging Monolithically Integrated Phase-Change Materials. PhotoniX 2025, 6, 16. [Google Scholar] [CrossRef]

- Wei, M.; Xu, K.; Tang, B.; Li, J.; Yun, Y.; Zhang, P.; Wu, Y.; Bao, K.; Lei, K.; Chen, Z.; et al. Monolithic Back-End-of-Line Integration of Phase Change Materials into Foundry-Manufactured Silicon Photonics. Nat. Commun. 2024, 15, 2786. [Google Scholar] [CrossRef] [PubMed]

- Ranno, L.; Sia, J.X.B.; Dao, K.P.; Hu, J. Multi-Material Heterogeneous Integration on a 3-D Photonic-CMOS Platform. Opt. Mater. Express 2023, 13, 2711. [Google Scholar] [CrossRef]

- Geler-Kremer, J.; Eltes, F.; Stark, P.; Stark, D.; Caimi, D.; Siegwart, H.; Jan Offrein, B.; Fompeyrine, J.; Abel, S. A Ferroelectric Multilevel Non-Volatile Photonic Phase Shifter. Nat. Photonics 2022, 16, 491–497. [Google Scholar] [CrossRef]

| Ref. | Transfer Rate (Gbps) | Modulation Mode | Bandwidth | Channel | Insertion Loss (dB) | Return Loss (dB) | Package Size (mm) |

|---|---|---|---|---|---|---|---|

| [64] | 200 | PAM4 | 800 G | 4 | <0.05 @ 28 GHz | >10 @ 100 GHz | 8.3 × 13 |

| [65] | 56 | NRZ | 400 G | 8 | <0.46 @ 56 GHz | >20 @ 40 GHz | 12 × 12 |

| [66] | 106 | PAM4 | 1.6 T | 16 | - | - | - |

| [69] | 224 | PAM4 | 1.79 T | 6 | <0.5 @ 56 GHz | <−18 @ 56 GHz | 9.5 × 13 |

| [67] | - | - | - | - | <0.5 @ 60 GHz | >20 @ 60 GHz | 11 × 11 |

| [9] | 100 | - | 51.2 T | 64 | - | - | - |

| [72] | - | - | - | - | <0.5 @ 40 GHz | - | - |

| [73] | 800 | PAM4 | 3.2 T | 4 | 1.5 @ 26 GHz | - | - |

| Ref. | Transfer Rate (Gbps) | Modulation Mode | Bandwidth | Channel | Insertion Loss (dB) | Packaging | Through-Hole | Bit Error Rate | Power (Pj/Bit) |

|---|---|---|---|---|---|---|---|---|---|

| [81] | 11.3 | NRZ | - | 4 | <1.1 @ 75 GHz | 2.5D | TSV | 10−9 | - |

| [82] | 64 | PAM4 | 256 G | 4 | <−1.55 @ 75 GHz | 2.5D | TSV | - | 6 |

| [84] | 100 | PAM4 | 3.2 T | 32 | 2–3 | 2.5D | TSV | 10−8 | 5 |

| [87] | 100 | PAM4 | 400 G | 4 | 3.5 | 3D | TSV | - | - |

| [88] | 112 | PAM4 | - | - | 0.35 | 3D | TSV | - | - |

| [89] | 224 | PAM4 | 102.4 T | - | 0.72 | 2.5D | TGV | - | - |

| [90] | 100 | PAM4 | 400 G | 4 | −1.5 | 2.5D | TGV | 10−7 | - |

| [91] | 25 | NRZ | 400 G | 16 | - | 3D | TGV | 10−12 | - |

| Ref. | [115] | [118] | [119] | [120] | [121] |

| Waveguide size (um) | 1–50 | 4.9–26.5 | 8–18 | ≈10 | 13 × 16 |

| Refractive index contrast | 5.8 × 10−4 | 5 × 10−4 | 10−5 | 10−2 | 3.5 × 10−3 |

| Propagation loss (dB/cm) | <0.2 | 0.31–0.34 | 0.2 | 0.23 | 0.28 |

| Coupling loss (dB) | - | - | 0.045 | 0.084 | - |

| Wavelength | 840/1550 | 450–1550 | 980–1610 | 1310/1550 | 1890 |

| Depth (μm) | 5–500 | 150 | 20–170 | 150 | 150 |

| Thermal stability | 250 °C | Room temperature | - | - | - |

| Laser parameters | 5 kHz, 224 nJ | 1 MHz, 20–30 nJ | 1 MHz, 28–30 nJ | 1087 kHz, 123 nJ | 5 MHz, 90 nJ |

| Ref. | Waveguide Type | Material | Propagation Loss (dB/cm) | Coupling Loss (dB) | Wavelength (nm) | Panel Size (mm) | Reliability |

|---|---|---|---|---|---|---|---|

| [129] | Single mode | PTR glass | 0.08 | 0.47 | 1550 | 76.2 × 1 | - |

| [130] | Single mode | Alkali glass | 0.034 | 0.31 | 1310 | 150 × 150 | 1000 h (130 °C/85%RH) |

| [131] | Single mode | Alkali glass | 0.08 | 0.3 | 1310 | 100 × 50 | 1000 Cycle (−40~125 °C) |

| [132] | Single mode | Molten glass | <0.1 | 0.5 | 1310 | 420 × 255 | - |

| [133] | Single/multimode | D263T | ~0.15 | 0.15 | 1550 | 303 × 227 | 1000 Cycle |

| Ref. | Platform | Coupling Method | Coupling Efficiency | Insertion Loss (dB) | Crosstalk (dB) | Bandwidth (nm) |

|---|---|---|---|---|---|---|

| [141] | SOI | Edge coupling | ~62% | <2 | <−10 | 90 |

| [142] | SOI | Edge coupling | >87% | −0.6 | <−25 | @ 1550 |

| [143] | SOI | Edge coupling | >98% | >−0.6 | <−19 | C-band |

| [148] | SiP PIC | Edge coupling | >85% | <1 | - | - |

| [150] | Glass substrate | Flip-chip + VCBEL | - | 1.6 | - | O-band |

| [151] | LNOI | Edge coupling | - | 1.16 | - | @ 1550 |

| [153] | SOI | Photonic wire bond | - | 0.73 dB | - | @ 1550 nm |

| [154] | SiN | Free-form micro-optical reflector | - | 0.5 dB | - | @ 1550 nm |

| [156] | SiN | Apodized grating coupling with aluminum back reflector | 88% | - | - | C-band |

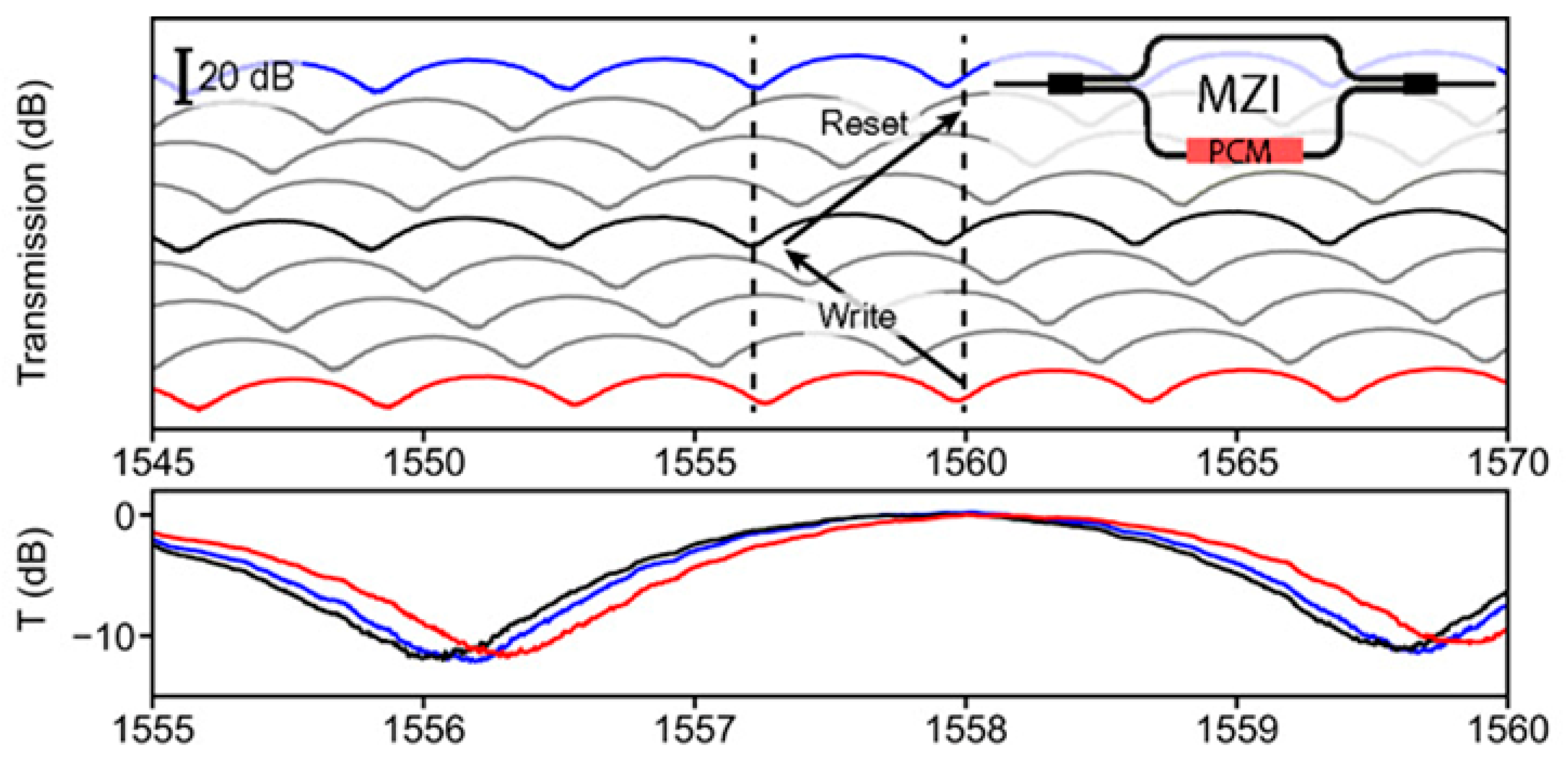

| Ref. | [180] | [181] | [182] | [183] | [184] | [58] | [185] | [188] |

| Device | P-RAM memory | Directional coupling switch | Directional coupling switch | Microring switch | Phase modulator | MZI Phaser | MRR | Ferroelectric phase shifter |

| Material structure | Si-GSSe | Si-Sb2S3 | Si-Sb2Se3 | Si-GST | Si-Sb2Se3 | Si-Sb2Se3 | Si-Sb2Se3 | Si/BaTiO3/Au |

| Insertion loss (dB) | 0.12 | <1.0 | 0.36 | 0.5 | 0.002 | <0.02 | 0.6 | 0.07 |

| Extinction ratio (dB) | 12 | 10–15 | 15/8 | 3 | - | - | 13.6 | - |

| Energy (nJ) | 1.5 | 11.6–29.2 | 0.57 | 5.55 | 9.25 | ~10 | 5.8 | 4.6 × 10−3 |

| Durable cycle | 5 × 105 | >1600 | >1000 | >1500 | >2000 | >500 | >100 | >300 |

| Response time | 0.5 ms | 200 ms | 100 µs | 100 µs | 100 µs | 50 ms | 1 ns | 100 μs |

| Phase coordination | - | - | - | - | 0.0082π | >10 | - | 0.15π |

| Wavelength coordination | - | 0.39 | - | - | 0.021 | - | 7.2 | - |

| Multi-level bit width | 4 | 5 | 5 | 7 | 14 | - | - | >3 |

| Device length (um) | 80 | 79 | 33 | 4.7 | 6 | 250 | 13 | 150 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gao, H.; Yan, W.; Zhang, D.; Yu, D. Heterogeneous Integration Technology Drives the Evolution of Co-Packaged Optics. Micromachines 2025, 16, 1037. https://doi.org/10.3390/mi16091037

Gao H, Yan W, Zhang D, Yu D. Heterogeneous Integration Technology Drives the Evolution of Co-Packaged Optics. Micromachines. 2025; 16(9):1037. https://doi.org/10.3390/mi16091037

Chicago/Turabian StyleGao, Han, Wanyi Yan, Dan Zhang, and Daquan Yu. 2025. "Heterogeneous Integration Technology Drives the Evolution of Co-Packaged Optics" Micromachines 16, no. 9: 1037. https://doi.org/10.3390/mi16091037

APA StyleGao, H., Yan, W., Zhang, D., & Yu, D. (2025). Heterogeneous Integration Technology Drives the Evolution of Co-Packaged Optics. Micromachines, 16(9), 1037. https://doi.org/10.3390/mi16091037