Design and Fabrication of Embedded Microchannel Cooling Solutions for High-Power-Density Semiconductor Devices

Abstract

1. Introduction

2. Related Work

3. Design, Simulation, and Manufacturing

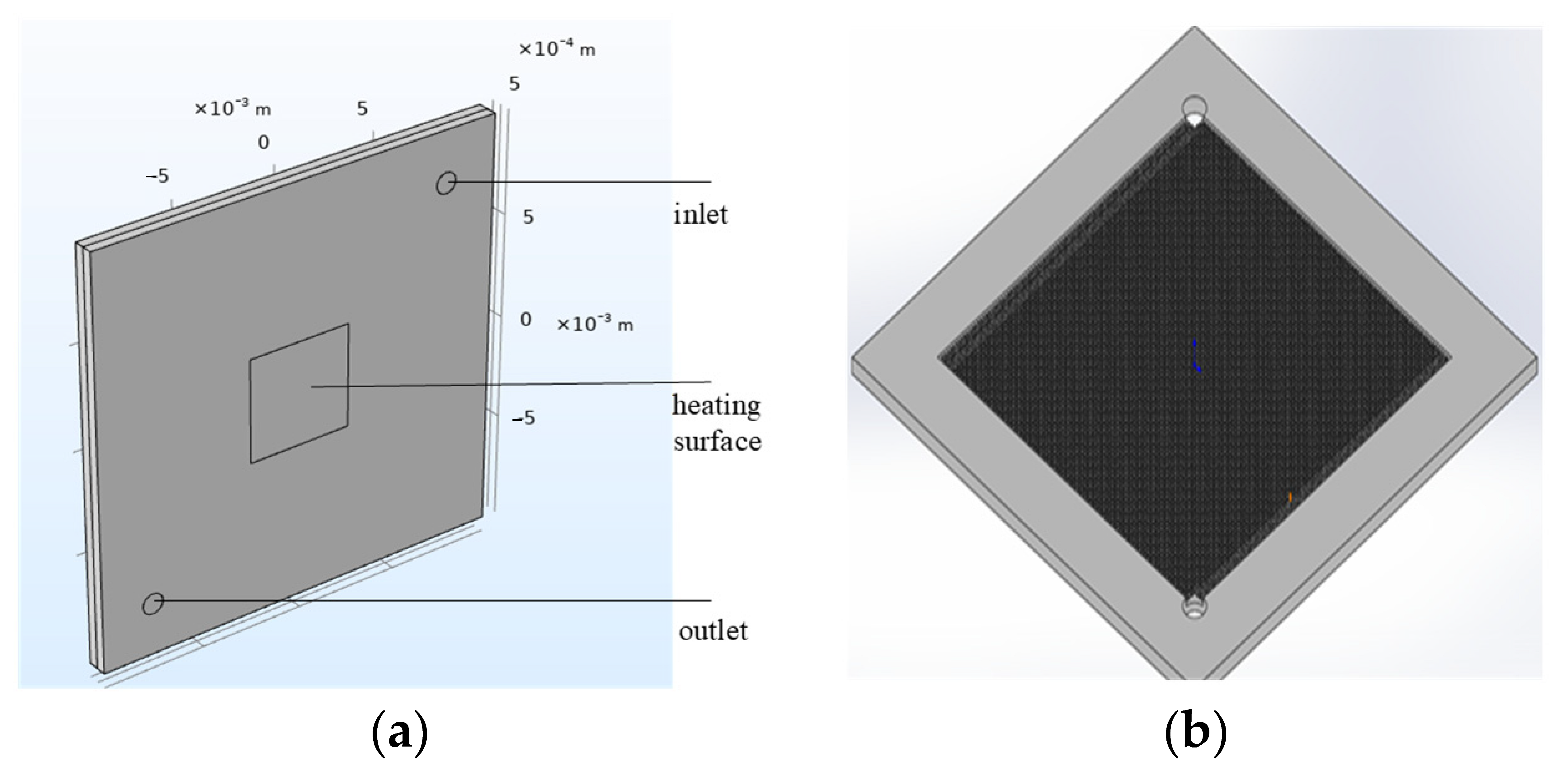

3.1. Numerical Modeling and Design

3.2. Fabrication Process

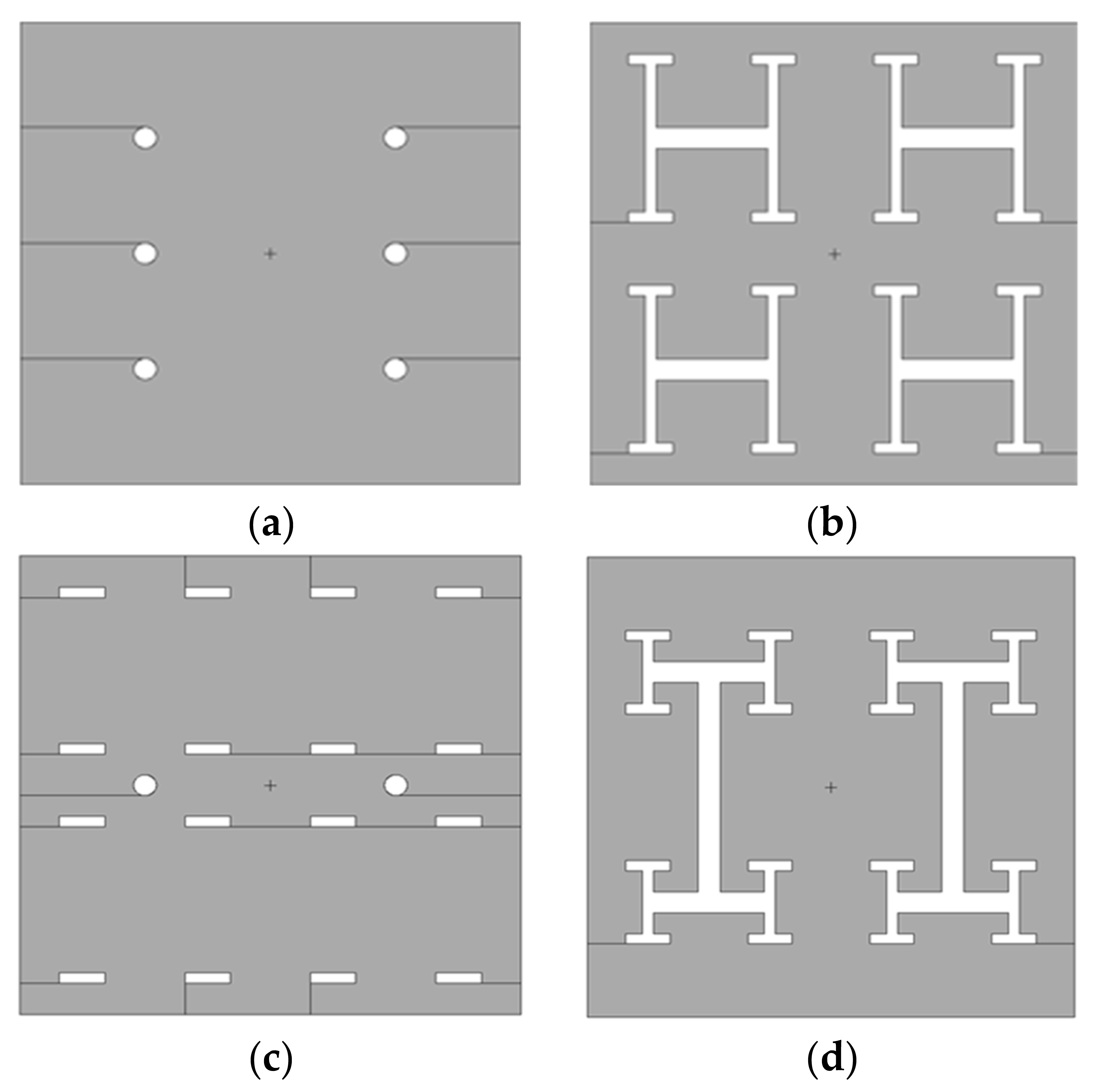

3.2.1. Development of Microchannel Cooling Structures

3.2.2. Development of the Coolant Distribution Structure

3.2.3. Development of the Surface Structure Modulation Process

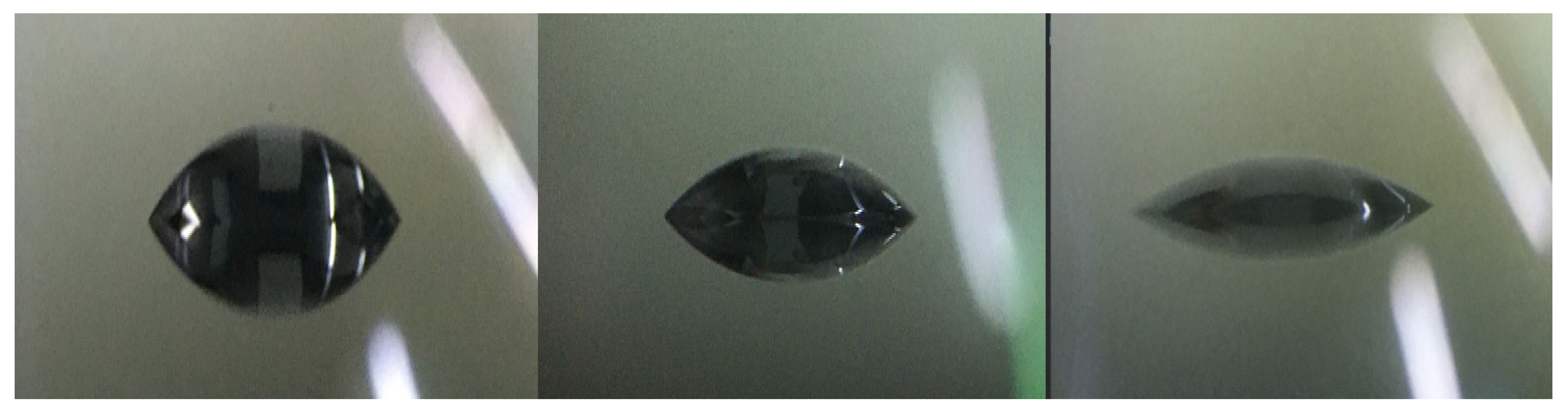

3.2.4. Sealing and Bonding

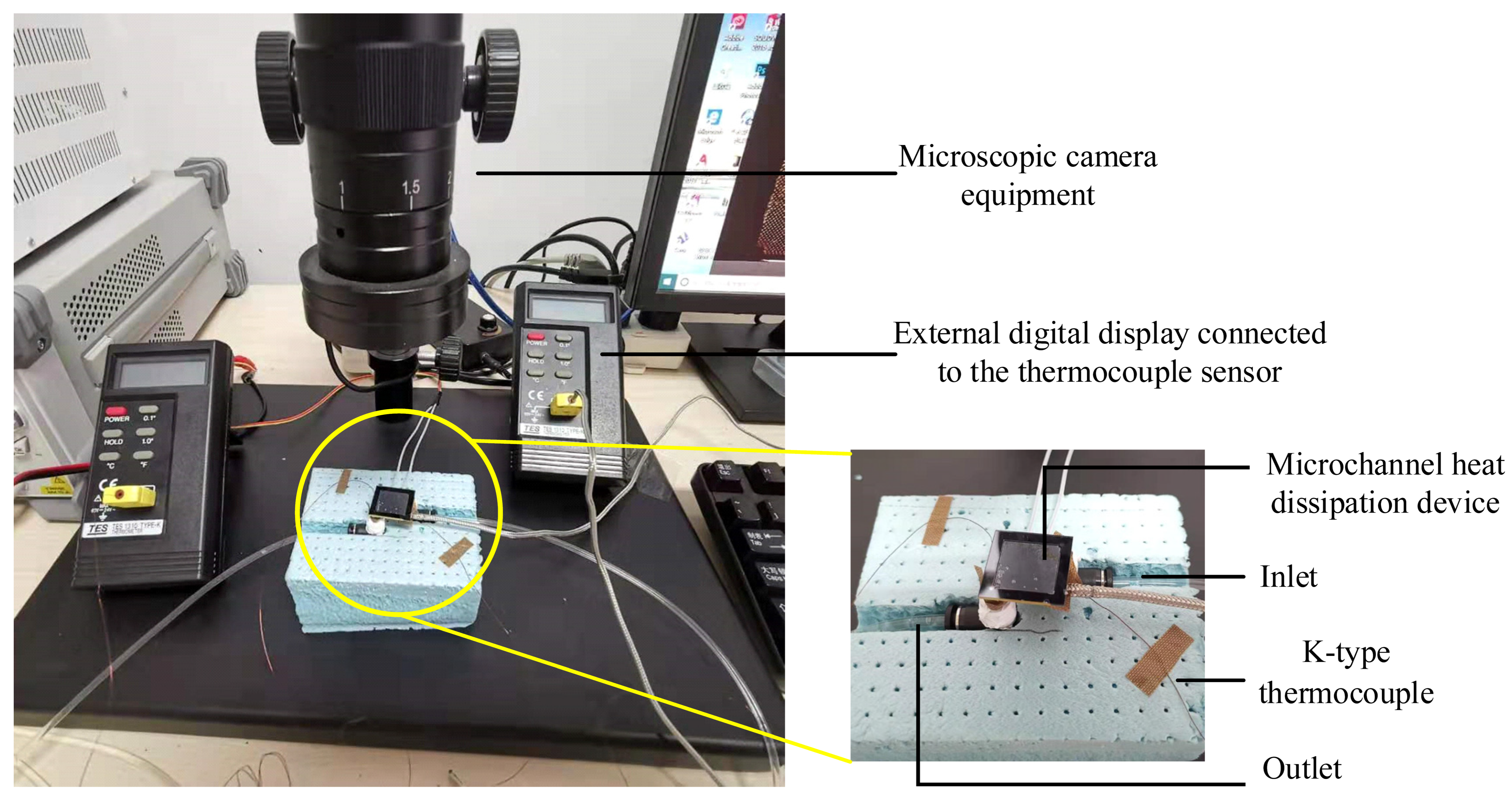

3.3. Experimental Setup and Testing Procedure

4. Results and Discussion

4.1. Analysis of Simulation Results

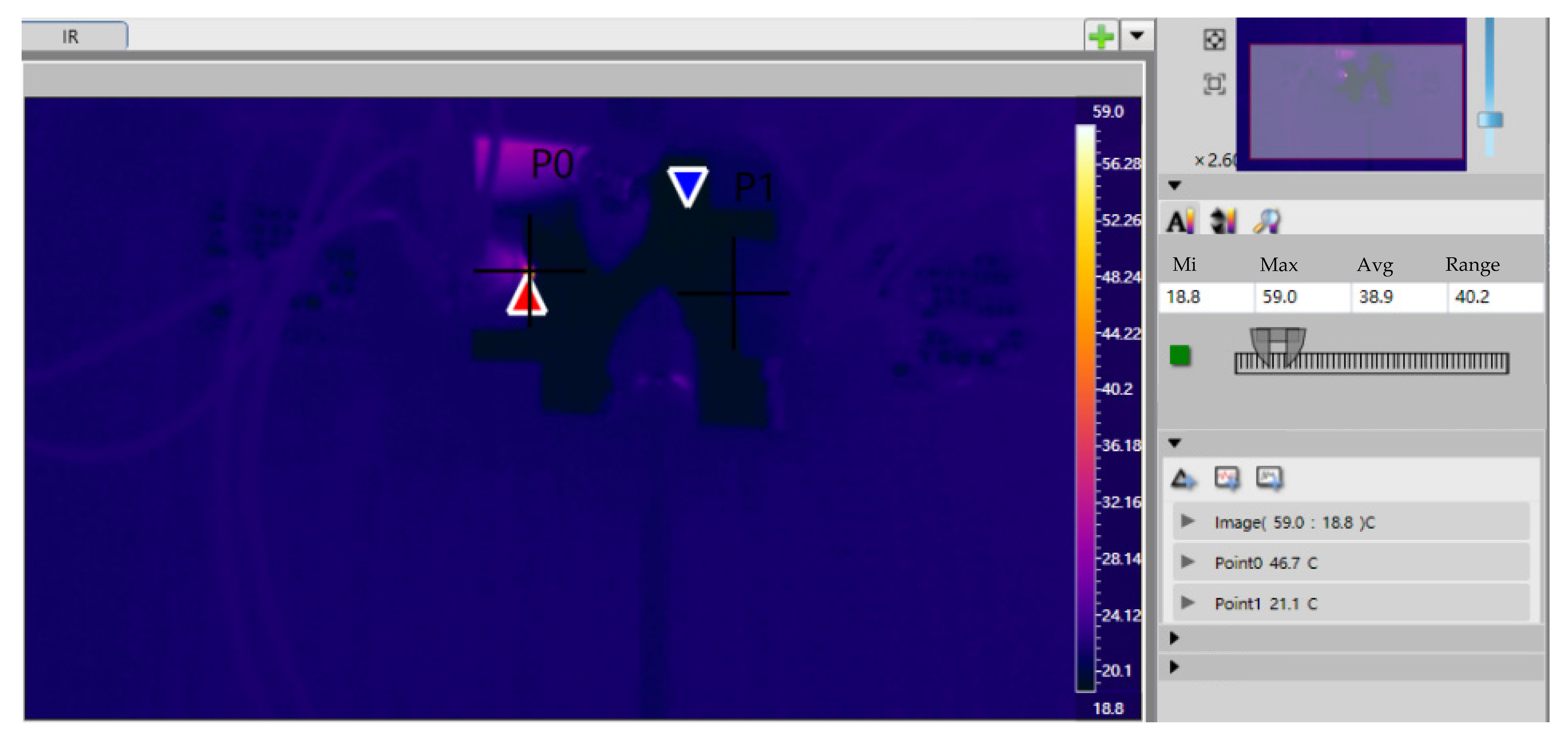

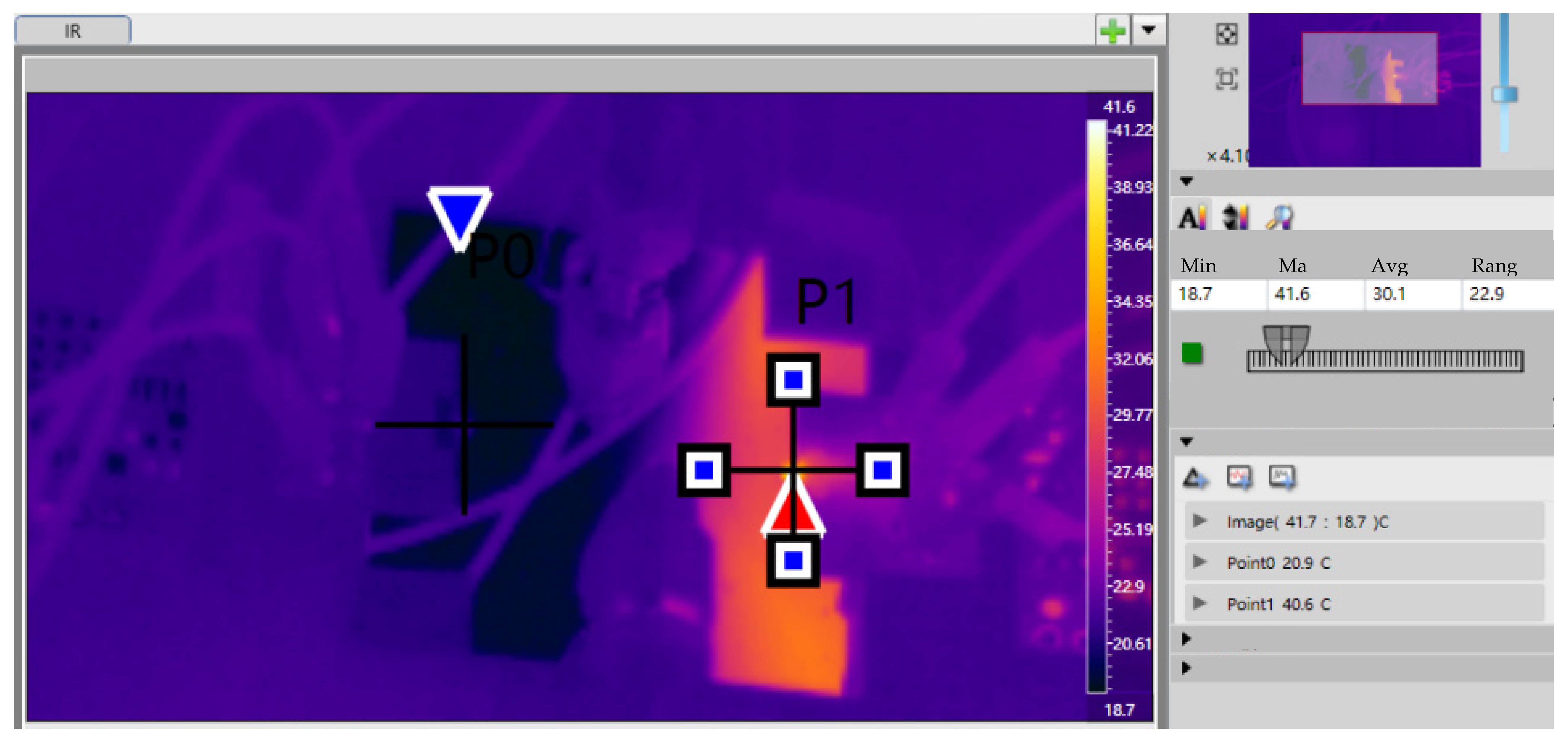

4.2. Experimental Performance Evaluation

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Li, G.; Shan, G.; Meng, B.; Zheng, Y.; Yang, Y. Intelligent Multifield Collaborative Optimization Method for TSV Array with Performance Constraints. IEEE Trans. Electron Devices 2023, 70, 4772–4778. [Google Scholar] [CrossRef]

- Jin, X.; Zhang, J.; Zhai, L.; Chen, W.; Shan, G.; Yang, Y. An Analytical Model for Calculating Transient Temperatures of 3-D Integrated System Considering Heat Capacity Variations. Microelectron. Reliab. 2025, 170, 115777. [Google Scholar] [CrossRef]

- Yang, X.; Lin, K.; Zhang, D.; Liu, S.; Han, B.; Wang, Z.; Yu, K.; Wu, W.; Ge, D.; Wang, C. A Novel Manifold Dual-Microchannel Flow Field Structure with High-Performance Heat Dissipation. Micromachines 2022, 13, 1420. [Google Scholar] [CrossRef] [PubMed]

- Pirouz, B.; Javadi Nejad, H.; Chirillo, A.S.; Naghib, S.N.; Piro, P. Enhancing the Design of Microdevices: The Role of Computational Fluid Dynamics and Experimental Investigation. Micromachines 2025, 16, 316. [Google Scholar] [CrossRef] [PubMed]

- Song, R.; Zhang, J.; Zhu, Z.; Shan, G.; Yang, Y. Fault and Self-Repair for High Reliability in Die-to-Die Interconnection of 2.5D/3D IC. Microelectron. Reliab. 2024, 158, 115429. [Google Scholar] [CrossRef]

- Hu, C.; Yang, X.; Ma, Z.; Ma, X.; Feng, Y.; Wei, J. Research on Heat Transfer and Flow Distribution of Parallel-Configured Microchannel Heat Sinks for Arrayed Chip Heat Dissipation. Appl. Therm. Eng. 2024, 255, 124003. [Google Scholar] [CrossRef]

- Tuckerman, D.B.; Pease, R.F.W. High-Performance Heat Sinking for VLSI. IEEE Electron Device Lett. 1981, 2, 126–129. [Google Scholar] [CrossRef]

- Wei, Y.; Pang, Y.; Zeng, X.; Zeng, C.; Ren, L.; Xu, J.; Sun, R.; Zeng, X. Thermally Conductive Yield-Stress Fluids with Reversible Solid–Liquid Transition Used as Thermal Interface Materials for Heat Dissipation of Chips. Adv. Funct. Mater. 2025, 35, 2412156. [Google Scholar] [CrossRef]

- Li, Z.; Luo, H.; Jiang, Y.; Liu, H.; Xu, L.; Cao, K.; Wu, H.; Gao, P.; Liu, H. Comprehensive Review and Future Prospects on Chip-Scale Thermal Management: Core of Data Center’s Thermal Management. Appl. Therm. Eng. 2024, 251, 123612. [Google Scholar] [CrossRef]

- Liu, H.; Yu, Z.; Zhao, Z.; Hao, X.; You, G.; Yue, Y. Study of Microfluidic Heat Transfer in 2D Hydrophobic Walls with Different Slip Mechanisms. Int. Commun. Heat Mass Transf. 2024, 159, 108077. [Google Scholar] [CrossRef]

- Ye, W.-Q.; Zhang, W.; Xu, Z.-R. Shape-Memory Microfluidic Chips for Fluid and Droplet Manipulation. Biomicrofluidics 2024, 18, 021301. [Google Scholar] [CrossRef]

- Bai, D.; Zhao, Z.; Avila, R.; Xia, D.; Huang, Y.; Rogers, J.A.; Xie, Z. Mechanics and Thermal Analyses of Microfluidic Nerve-Cooler System. J. Mech. Phys. Solids 2024, 190, 105741. [Google Scholar] [CrossRef]

- Aryal, P.; Henry, C.S. Advancements and Challenges in Microfluidic Paper-Based Analytical Devices: Design, Manufacturing, Sustainability, and Field Applications. Front. Lab. Chip. Technol. 2024, 3, 1467423. [Google Scholar] [CrossRef]

- Xie, M.; Zhan, Z.; Li, Y.; Zhao, J.; Zhang, C.; Wang, Z.; Wang, Z. Functional Microfluidics: Theory, Microfabrication, and Applications. Int. J. Extrem. Manuf. 2024, 6, 032005. [Google Scholar] [CrossRef]

- Sureddi, R.C.; Li, L.; Wu, H.; Giannetti, N.; Saito, K.; Rees, D. A Review of Recent Advancements in Heat Pump Systems and Developments in Microchannel Heat Exchangers. Machines 2025, 13, 333. [Google Scholar] [CrossRef]

- Zhang, L.-Y.; Zhang, Y.-F. Simulation on Heat Transfer of Microchannels and Thermal Vias for High Power Electronic Packages. In Proceedings of the 2014 15th International Conference on Electronic Packaging Technology, Chengdu, China, 12–15 August 2014; pp. 508–510. [Google Scholar]

- Zhang, L.-Y.; Zhang, Y.-F.; Chen, J.-Q.; Bai, S.-L. Fluid Flow and Heat Transfer Characteristics of Liquid Cooling Microchannels in LTCC Multilayered Packaging Substrate. Int. J. Heat Mass Transf. 2015, 84, 339–345. [Google Scholar] [CrossRef]

- Pietrikova, A.; Girasek, T.; Lukacs, P.; Welker, T.; Müller, J. Simulation of Cooling Efficiency via Miniaturised Channels in Multilayer LTCC for Power Electronics. J. Electr. Eng. 2017, 68, 132–137. [Google Scholar] [CrossRef]

- Yu, H.; Han, B.; Miao, M.; Cui, X.; Zhao, K. Design and Analysis of Microchannel for the Thermal Management of Multi-Stacked LTCC Laminates. In Proceedings of the 2018 19th International Conference on Electronic Packaging Technology (ICEPT), Shanghai, China, 8–11 August 2018; pp. 872–875. [Google Scholar]

- Drummond, K.P.; Weibel, J.A.; Garimella, S.V. Two-Phase Flow Morphology and Local Wall Temperatures in High-Aspect-Ratio Manifold Microchannels. Int. J. Heat Mass Transf. 2020, 153, 119551. [Google Scholar] [CrossRef]

- Tong, Y.; Luo, T.; Wang, Q.; Liu, J.; Peng, Y.; Chen, M. Heat Dissipation Enhancement of High-Power LEDs Through Compact Ceramic Substrate Integrated with Microchannel. IEEE Trans. Electron Devices 2023, 70, 4749–4753. [Google Scholar] [CrossRef]

- He, W.; Yin, E.; Zhou, F.; Zhao, Y.; Hu, D.; Li, J.; Li, Q. Integrated Manifold Microchannels and Near-Junction Cooling for Enhanced Thermal Management in 3D Heterogeneous Packaging Technology. Energy 2024, 305, 132263. [Google Scholar] [CrossRef]

- Tian, B.; Yang, D.; Ma, H.; Xu, J.; Liang, D. A Manufacturing Method of Integrated Ceramic Heat Spreaders Embedded with Interconnected Microchannels. Mater. Des. 2019, 180, 107969. [Google Scholar] [CrossRef]

- Mikulics, M.; Kordoš, P.; Fox, A.; Kočan, M.; Lüth, H.; Sofer, Z.; Hardtdegen, H. Efficient Heat Dissipation in AlGaN/GaN Heterostructure Grown on Silver Substrate. Appl. Mater. Today 2017, 7, 134–137. [Google Scholar] [CrossRef]

- Wu, X.; Liu, W. An Engineering Roadmap for the Thermoelectric Interface Materials. J. Mater. 2024, 10, 748–750. [Google Scholar] [CrossRef]

- Liu, N.; Jin, Y.; Miao, M.; Cui, X. Optimization of Heat Transfer of Microchannels in LTCC Substrate with via Holes and Liquid Metal. In Proceedings of the 2016 17th International Conference on Electronic Packaging Technology (ICEPT), Wuhan, China, 16–19 August 2016; pp. 1135–1139. [Google Scholar]

- Zhang, R.; Hodes, M.; Lower, N.; Wilcoxon, R. High Heat Flux, Single-Phase Microchannel Cooling. In Proceedings of the 2014 Semiconductor Thermal Measurement and Management Symposium (SEMI-THERM), San Jose, California, 9–13 March 2014; pp. 1–7. [Google Scholar]

- Wei, H.; Huang, C.; Lu, L.; Wang, J. Stress and Strain Analysis of LTCC Substrate Module Based on Microchannel. In Proceedings of the 2018 19th International Conference on Electronic Packaging Technology (ICEPT), Shanghai, China, 8–11 August 2018; pp. 210–214. [Google Scholar]

- Wei, H.; Huang, C.; Ying, L. Analysis of Thermal Stress and Strain in BGA Solder Joint Based on Microchannel Ceramic Substrate. IEEE Trans. Compon. Packag. Manuf. Technol. 2019, 9, 895–904. [Google Scholar] [CrossRef]

- Kang, T.; Ye, Y.; Jia, Y.; Kong, Y.; Jiao, B. Enhanced Thermal Management of GaN Power Amplifier Electronics with Micro-Pin Fin Heat Sinks. Electronics 2020, 9, 1778. [Google Scholar] [CrossRef]

- Yin, P.; Li, Y.; Zhang, P.; Xiao, G.; Yuan, H. On-Chip Heat Dissipation Design for High-Power SiP Modules with LTCC Substrates. In Proceedings of the 2019 20th International Conference on Electronic Packaging Technology (ICEPT), Hong Kong, China, 12–15 August 2019; pp. 1–4. [Google Scholar]

- Haertel, J.H.K.; Engelbrecht, K.; Lazarov, B.S.; Sigmund, O. Topology Optimization of a Pseudo 3D Thermofluid Heat Sink Model. Int. J. Heat Mass Transf. 2018, 121, 1073–1088. [Google Scholar] [CrossRef]

- Chen, J.; Zhang, S.; Tang, Y.; Chen, H.; Yuan, W.; Zeng, J. Effect of Operational Parameters on Flow Boiling Heat Transfer Performance for Porous Interconnected Microchannel Nets. Appl. Therm. Eng. 2017, 121, 443–453. [Google Scholar] [CrossRef]

- Fathi, M.; Heyhat, M.M.; Zabetian Targhi, M.; Bigham, S. Porous-Fin Microchannel Heat Sinks for Future Micro-Electronics Cooling. Int. J. Heat Mass Transf. 2023, 202, 123662. [Google Scholar] [CrossRef]

- Van Erp, R.; Soleimanzadeh, R.; Nela, L.; Kampitsis, G.; Matioli, E. Co-Designing Electronics with Microfluidics for More Sustainable Cooling. Nature 2020, 585, 211–216. [Google Scholar] [CrossRef]

- Hanks, D.F.; Lu, Z.; Sircar, J.; Salamon, T.R.; Antao, D.S.; Bagnall, K.R.; Barabadi, B.; Wang, E.N. Nanoporous Membrane Device for Ultra High Heat Flux Thermal Management. Microsyst. Nanoeng. 2018, 4, 1. [Google Scholar] [CrossRef]

| Step | Process | Parameters |

|---|---|---|

| 1 | Substrate preparation | 4-inch P <100>, 1–10 Ω∙cm, 525 µm thickness, double-side polished |

| 2 | Thermal oxidation | 100 ± 10 nm (hard mask) |

| 3 | Backside photolithography | Inlet/outlet patterning |

| 4 | RIE oxide etching | Over-etching |

| 5 | Deep silicon etching | 260 ± 10 µm |

| 6 | Frontside photolithography | Micropillar patterning |

| 7 | RIE oxide etching | Over-etching |

| 8 | Deep silicon etching | 260 ± 10 µm |

| 9 | Bonding | Channel sealing |

| Sample | Power (W) | Current (A) | Voltage (V) | Temperature (°C) |

|---|---|---|---|---|

| Chip 1 | 1.823 | 0.606 | 3.009 | 46.7 |

| Chip 2 | 1.823 | 0.554 | 3.303 | 40.6 |

| Works | Dissipation Method | Structure | Material | Heat Flux (W/cm2) | Temperature Rise (K) |

|---|---|---|---|---|---|

| [31] | Heat sink | SiP | PCM | 20 W/- | 77 |

| [32] | Forced air cooled | Fin | PCM | 20 W/- | 31.9 |

| [22] | Microchannel | Manifold | Copper | 700 | - |

| [33] | Microchannel | Porous interconnected | Copper | 200~500 | 16.7 |

| [34] | Microchannel | Porous-fin | Porous copper | 100 | - |

| [35] | Microchannel | Parallel and manifold | AlGaN and GaN | 1000 (single-phase water-cooling) | 60 |

| [36] | Microchannel | Nanoporous membrane | SOI and silicon | (665 ± 74) | (28.5 ± 1.8) |

| Our work | Microchannel | Square microcolumn | Silicon | 1200 | 27.9 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Fu, Y.; Shan, G.; Zhang, X.; Zhao, L.; Yang, Y. Design and Fabrication of Embedded Microchannel Cooling Solutions for High-Power-Density Semiconductor Devices. Micromachines 2025, 16, 908. https://doi.org/10.3390/mi16080908

Fu Y, Shan G, Zhang X, Zhao L, Yang Y. Design and Fabrication of Embedded Microchannel Cooling Solutions for High-Power-Density Semiconductor Devices. Micromachines. 2025; 16(8):908. https://doi.org/10.3390/mi16080908

Chicago/Turabian StyleFu, Yu, Guangbao Shan, Xiaofei Zhang, Lizheng Zhao, and Yintang Yang. 2025. "Design and Fabrication of Embedded Microchannel Cooling Solutions for High-Power-Density Semiconductor Devices" Micromachines 16, no. 8: 908. https://doi.org/10.3390/mi16080908

APA StyleFu, Y., Shan, G., Zhang, X., Zhao, L., & Yang, Y. (2025). Design and Fabrication of Embedded Microchannel Cooling Solutions for High-Power-Density Semiconductor Devices. Micromachines, 16(8), 908. https://doi.org/10.3390/mi16080908