1. Introduction

As semiconductor technology continues its push into the sub-10 nm regime, conventional bulk MOSFET architectures are increasingly limited by short-channel effects, high leakage currents, and variability induced by process scaling [

1,

2,

3]. To address these challenges, FinFETs built on silicon-on-insulator (SOI) substrates have become a widely adopted alternative due to their excellent electrostatic control, lower off-state leakage, and scalability [

4,

5]. Among these, junctionless FinFETs, where the source, drain, and channel are uniformly doped, offer added benefits of fabrication simplicity and reduced variability, making them suitable for ultra-scaled nodes [

6].

Field-Programmable Gate Arrays (FPGAs), known for their flexibility and reconfigurability, are particularly sensitive to device-level characteristics such as leakage power, switching delay, and gate capacitance [

7]. Traditional CMOS-based FPGAs face scaling bottlenecks due to increasing static power and degraded signal integrity [

8]. Several studies have explored the use of FinFETs to improve FPGA performance [

9,

10]. For instance, prior work has demonstrated that FinFET-based FPGA fabrics can achieve significant reductions in power consumption and delay compared to planar CMOS, owing to superior channel control and reduced leakage [

11]. Furthermore, FinFETs allow for multi-threshold tuning and better trade-offs between performance and power, which are key requirements in modern FPGA design [

12].

However, as FinFET gate lengths shrink below 10 nm, new challenges arise. Even SOI-based and junctionless FinFETs suffer from increased gate leakage, drain-induced barrier lowering (DIBL), and subthreshold degradation, especially due to fringing fields from the drain and the gate spacers. To improve FinFET performance and mitigate these effects, several studies have explored the impact of gate spacer engineering. Sachid et al. investigated high-κ spacers, demonstrating improved drive current and reduced short-channel effects due to enhanced electrostatic control, albeit with increased parasitic capacitance [

13]. Studies on wavy FinFET structures have compared various materials such as SiO

2, Si

3N

4, and HfO

2, finding that HfO

2 spacers deliver a significant leakage reduction and improved I

ON/I

OFF ratio [

14]. Moreover, hybrid spacer stacks combining low-κ and high-κ dielectrics have been applied in DG-TFET and planar transistors, where SiO

2/HfO

2 configurations yield optimal tunneling efficiency and retention in memory-type devices [

15]. Also, asymmetric spacer configurations, such as dual-κ or corner spacers, have been proposed to tailor source/drain fringe fields independently, resulting in enhanced capacitance characteristics and inverter responses in TFETs and negative-capacitance FinFETs [

16].

Building upon these spacer engineering strategies, this work introduces a novel FinFET architecture, termed the S3-FinFET (Stepped-Spacer Structured FinFET), which employs a three-layer spacer stack composed of HfO2/Si3N4/HfO2 arranged in a stepped vertical configuration. This design not only enhances fringe field coupling near the gate, but also screens unwanted electric field penetration near the source/drain terminals, thus improving both ON- and OFF-state behavior. Through rigorous 2D TCAD simulations using the Silvaco Atlas platform, the S3-FinFET is evaluated for key performance metrics including transfer and output characteristics, subthreshold swing, DIBL, ON/OFF current ratio, gate capacitance profiles, and cut-off frequency.

Despite the advantages mentioned above, integrating FinFET technology into FPGA fabrics remains a nontrivial task. The performance of FPGAs is heavily dependent on the behavior of their constituent devices under static conditions, particularly in routing paths and configuration logic, where leakage and capacitance directly impact power and speed. Moreover, as gate lengths scale below 10 nm, even advanced FinFET structures encounter worsening electrostatic integrity, fringing field effects, and layout-induced variability. These challenges underscore the need for novel device architectures that specifically address FPGA-centric requirements.

The study of the S3-FinFET design reported here highlights its strong potential for FPGA applications. Its excellent electrostatic gate control makes it a promising candidate for integration into next-generation FPGA fabrics, enabling energy-efficient, high-speed reconfigurable systems at deeply scaled technology nodes.

2. Device Architecture and Simulation Framework

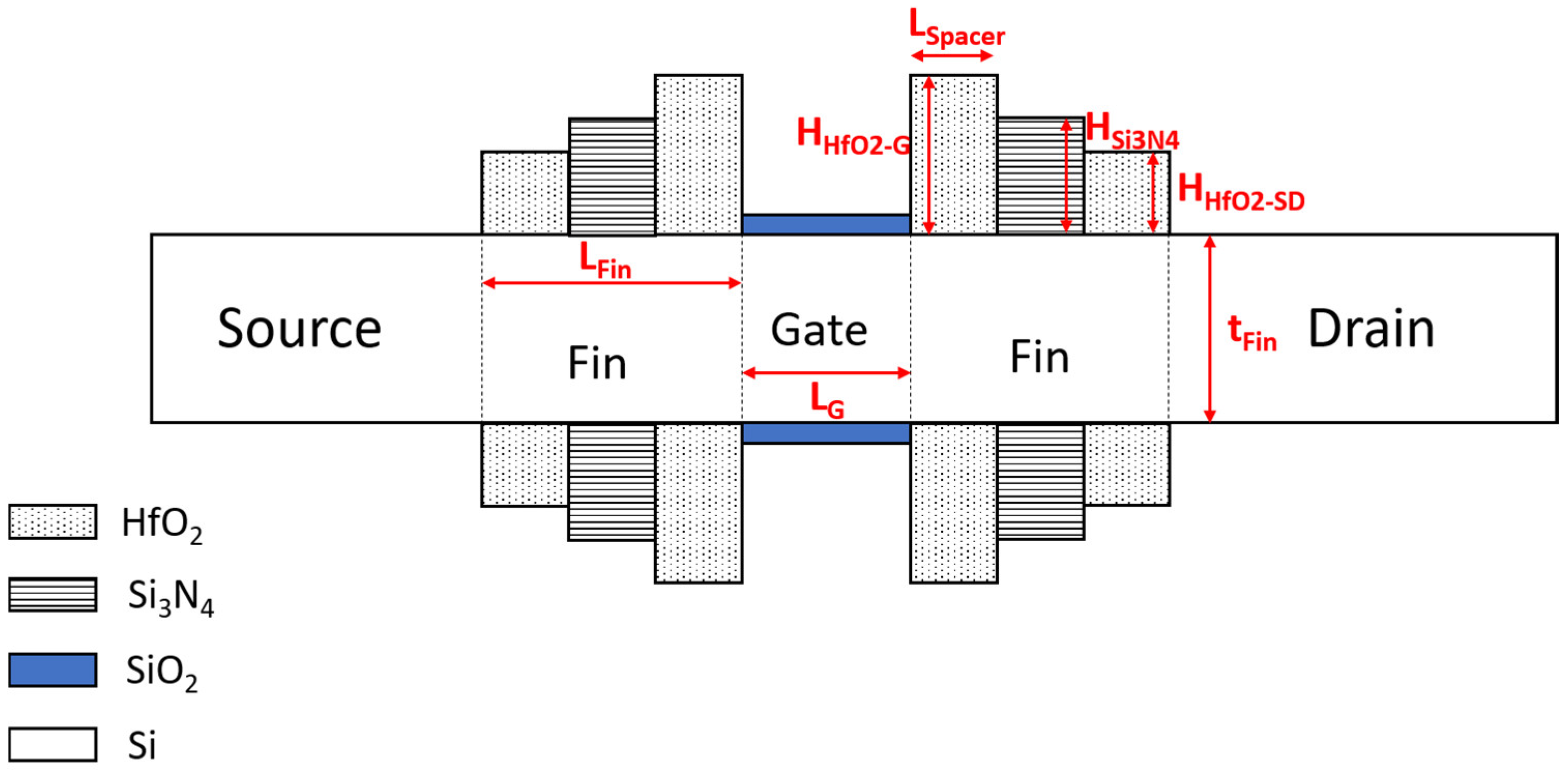

The S

3-FinFET investigated in this work is simulated using 2D Silvaco TCAD simulator [

17]. The device features a gate length of 5 nm and is designed on an SOI platform, which includes an 80 nm buried oxide layer for substrate isolation, as shown in

Figure 1. A high work-function metal gate (4.8 eV) is placed atop a SiO

2 gate dielectric, with the oxide thickness set to an equivalent oxide thickness (EOT) that meets advanced technology node requirements [

18].

Unlike in traditional designs, the source, drain, and channel regions are doped entirely and uniformly to a concentration of 1 × 10

19 cm

−3, ensuring junctionless conduction. Both source/drain and spacer lengths are fixed at 12 nm, as shown in the top view of the proposed structure in

Figure 2. The key differentiator in this structure is the use of a three-layer spacer stack. An inner HfO

2 layer adjacent to the gate enhances gate-to-channel coupling; a middle Si

3N

4 layer acts as a dielectric buffer; and a second outer HfO

2 layer near the source/drain junctions further screens fringing fields. These spacers are arranged in a stepped structure, with the HfO

2 spacer near the gate having the greatest height, which gradually decreases toward the source and drain sides.

The simulations incorporate advanced physical models to capture quantum and high-doping effects. Carrier transport is modeled using the drift–diffusion approach, enhanced with Fermi–Dirac statistics. The quantum density-gradient model accounts for confinement and tunneling, while bandgap narrowing and band-to-band tunneling models address heavy doping and leakage. Mobility degradation from interface scattering and phonon interactions is considered via the Lombardi model, and carrier recombination is modeled using the Shockley–Read–Hall (SRH) approach.

Simulation results demonstrate that the proposed S

3-FinFET exhibits improved performance due to the use of the three-layer spacer structure. For recombination, the Shockley–Read–Hall (SRH) model is used, which calculates the recombination rate based on carrier lifetimes and trap-assisted transitions. The SRH rate is formulated using the following formula [

17]:

where n and

p are the electron and hole concentrations, n

i,eff is the effective intrinsic carrier concentration, τ

n and τ

p are the carrier lifetimes, and n

1 and p

1 are the trap densities.

To simplify the fabrication process, the lengths of all three spacers are kept the same. The fabrication of the proposed S

3-FinFET begins with the formation of a silicon-on-insulator (SOI) substrate, followed by thinning of the top silicon layer and fin patterning using lithography and anisotropic etching. A gate oxide is then deposited using chemical vapor deposition (CVD), and a metal gate is formed. Subsequently, a tri-layer spacer structure is created. An inner HfO

2 spacer is deposited and etched first, followed by the deposition and patterning of a middle Si

3N

4 spacer; finally, the outer HfO

2 spacer is formed after source/drain extension implantation. Ion implantation is performed for the source/drain extensions, using a photoresist mask to protect the gate and spacer stack [

19]. Afterward, selective epitaxial growth is used to form the heavily doped source and drain regions, followed by high-temperature annealing to activate the dopants. The process concludes with metallization to establish electrical contacts, completing the device structure.

Additional device parameters are provided in

Table 1.

3. Results and Discussion

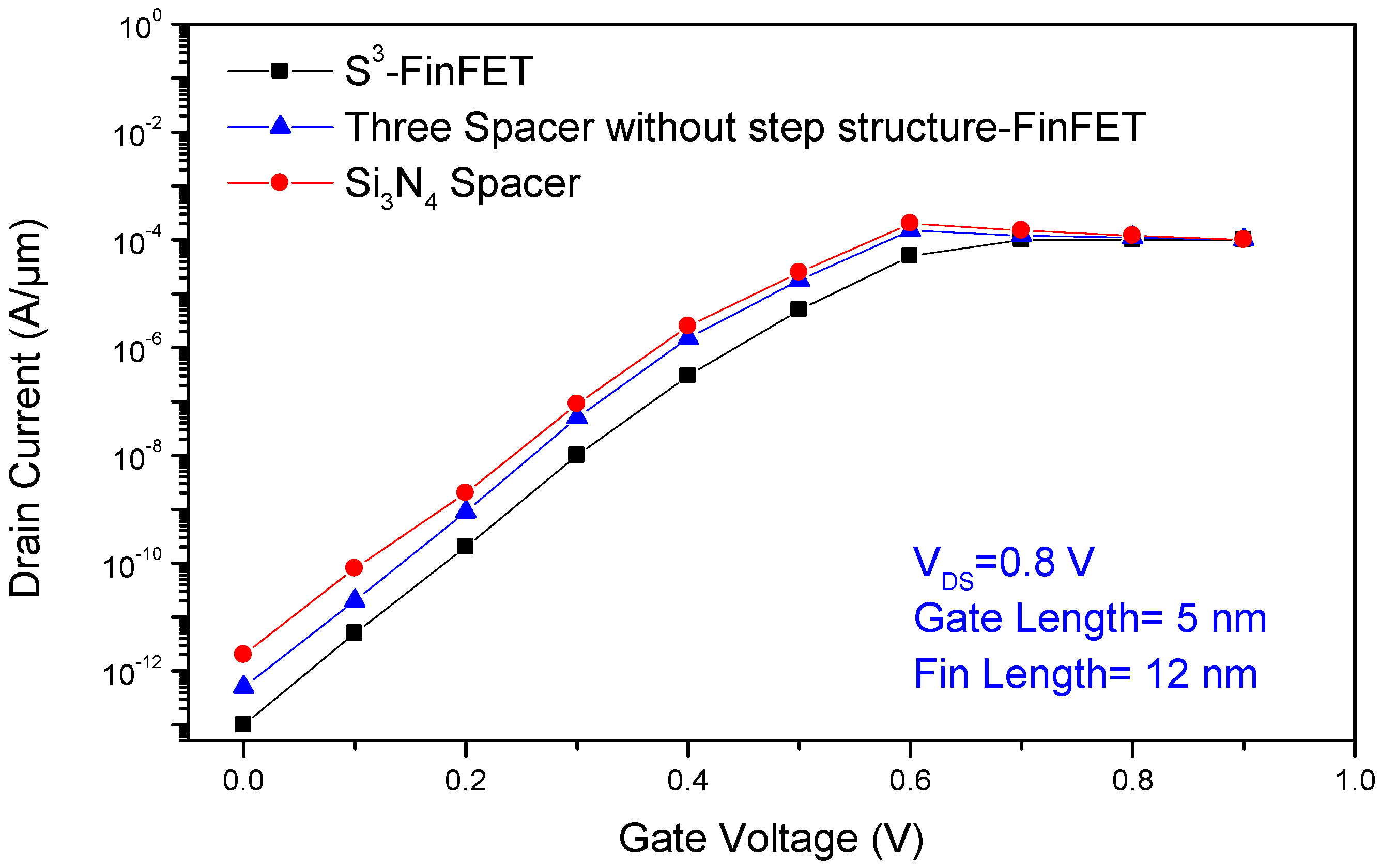

The transfer characteristics of the proposed S3-FinFET, compared to two other FinFET structures, a three-spacer FinFET without a stepped design and a conventional FinFET using only Si3N4 as a spacer, demonstrate the effectiveness of the novel stepped high-k spacer configuration. This design enhances fringe field penetration into the channel, thereby improving gate control across the entire fin body, which is especially beneficial at ultra-short gate lengths. The inclusion of an inner HfO2 layer with high permittivity extends the gate’s electrostatic reach without physically increasing gate length, improving barrier formation and reducing channel length modulation.

As shown in

Figure 3, the transfer characteristics indicate that the S

3-FinFET achieves lower sub-threshold leakage current due to a higher vertical electric field in the OFF state, while maintaining unaffected drive current in the ON state owing to a near-zero lateral electric field. Furthermore, the subthreshold swing (SS) of the S

3-FinFET is significantly improved compared to the other two structures, highlighting its superior suppression of thermionic leakage and excellent interface control.

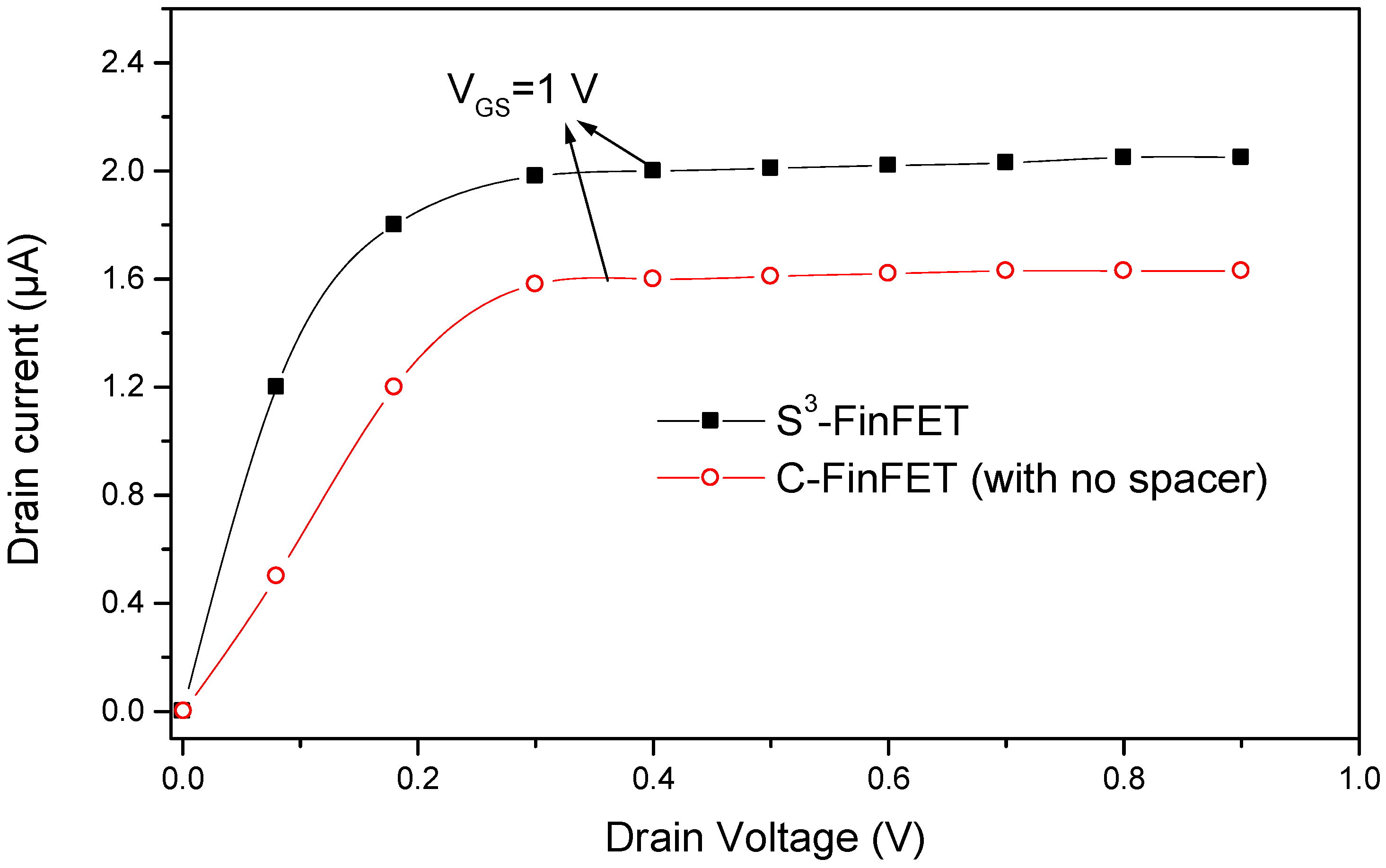

To further validate the performance enhancements introduced by the proposed HfO

2/Si

3N

4/HfO

2 stepped spacer structure, a comparative analysis was conducted between the S

3-FinFET and a conventional FinFET (C-FinFET) without any spacer.

Figure 4 presents the output characteristics of both devices, highlighting the superior current-driving capability of the S

3-FinFET across a range of gate voltages. This enhancement is attributed to the improved electrostatic control enabled by the high-k stepped spacer, which strengthens gate-to-channel coupling.

Additionally,

Figure 5 shows the transfer characteristics of both devices. It can be seen that the S

3-FinFET exhibits a significantly higher I

ON/I

OFF ratio, confirming the effectiveness of the proposed spacer in enhancing device performance. These comparisons provide clear evidence that the S

3-FinFET structure offers substantial benefits over conventional designs in terms of both current driving and short-channel control.

To evaluate the current-driving capability and short-channel behavior of the proposed S

3-FinFET under different biasing conditions, output characteristics were analyzed at two gate voltages, V

GS = 0.5 V and V

GS = 1 V, as shown in

Figure 6. In the figure, the curves exhibit a clear transition from the linear region to the saturation region, reflecting strong channel modulation and proper saturation behavior. At V

GS = 0.5 V, the drain current increases linearly with V

D in the low-voltage region, indicating good channel formation, while saturation occurs at higher V

D values, demonstrating effective gate control. At V

GS = 1 V, a significantly higher drain current is observed across all V

D values, highlighting the structure’s ability to support strong inversion and enhanced carrier injection due to improved electrostatics. The stepped high-k spacer in the S

3-FinFET enhances fringe field coupling and reinforces gate control across the fin body, minimizing channel length modulation even at scaled dimensions. The saturation region shows minimal slope, which further confirms the suppression of drain-induced barrier lowering (DIBL). The nearly ideal output behavior at both gate voltages supports the effectiveness of the proposed design in maintaining high drive current and strong saturation, making it well-suited for ultra-scaled low-power applications.

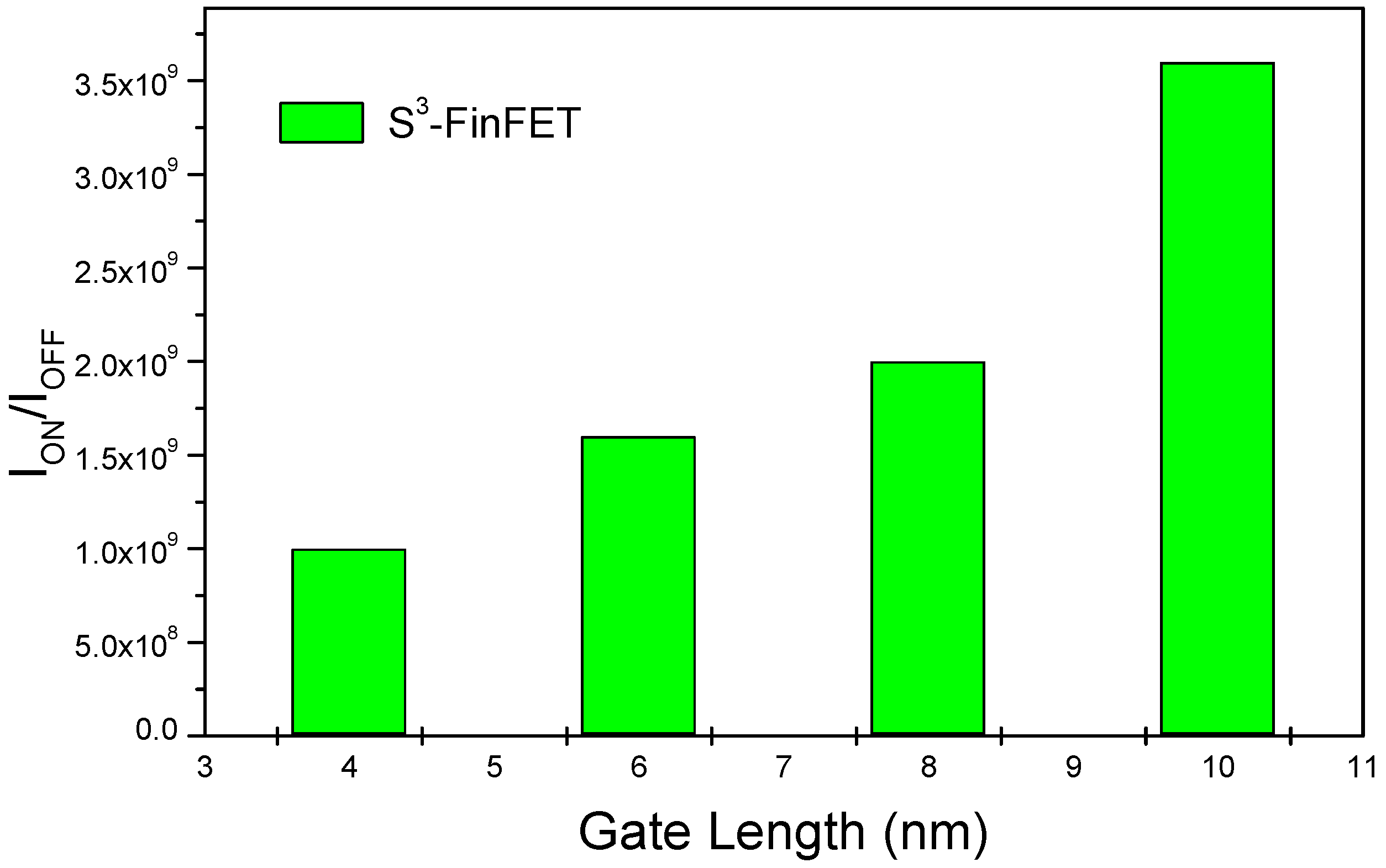

Figure 7 presents I

ON/I

OFF ratio values of the proposed S

3-FinFET. In the figure, a peak value exceeding 10

8 can be seen. This high ratio reflects the device’s excellent ability to combine low leakage with strong drive current. The OFF-state current remains impressively low, in the order of ~10

−13 A/μm, primarily due to the junctionless design and the well-engineered potential barrier within the channel. Uniform doping prevents abrupt junction transitions that typically act as leakage paths, resulting in smooth conduction band profiles and suppressed leakage in the OFF state. Moreover, the stepped spacer structure effectively reduces source-to-drain tunnelling by decoupling the drain electric field from the source/channel interface, maintaining a robust potential barrier under reverse bias. At the same time, the high ON current is enabled by efficient carrier injection from the source into the heavily doped channel, facilitated by the absence of depletion zones typical of junction-based devices. Additionally, quantum confinement within the narrow fin slightly increases the effective bandgap, further reducing OFF-state leakage and enhancing overall device switching performance.

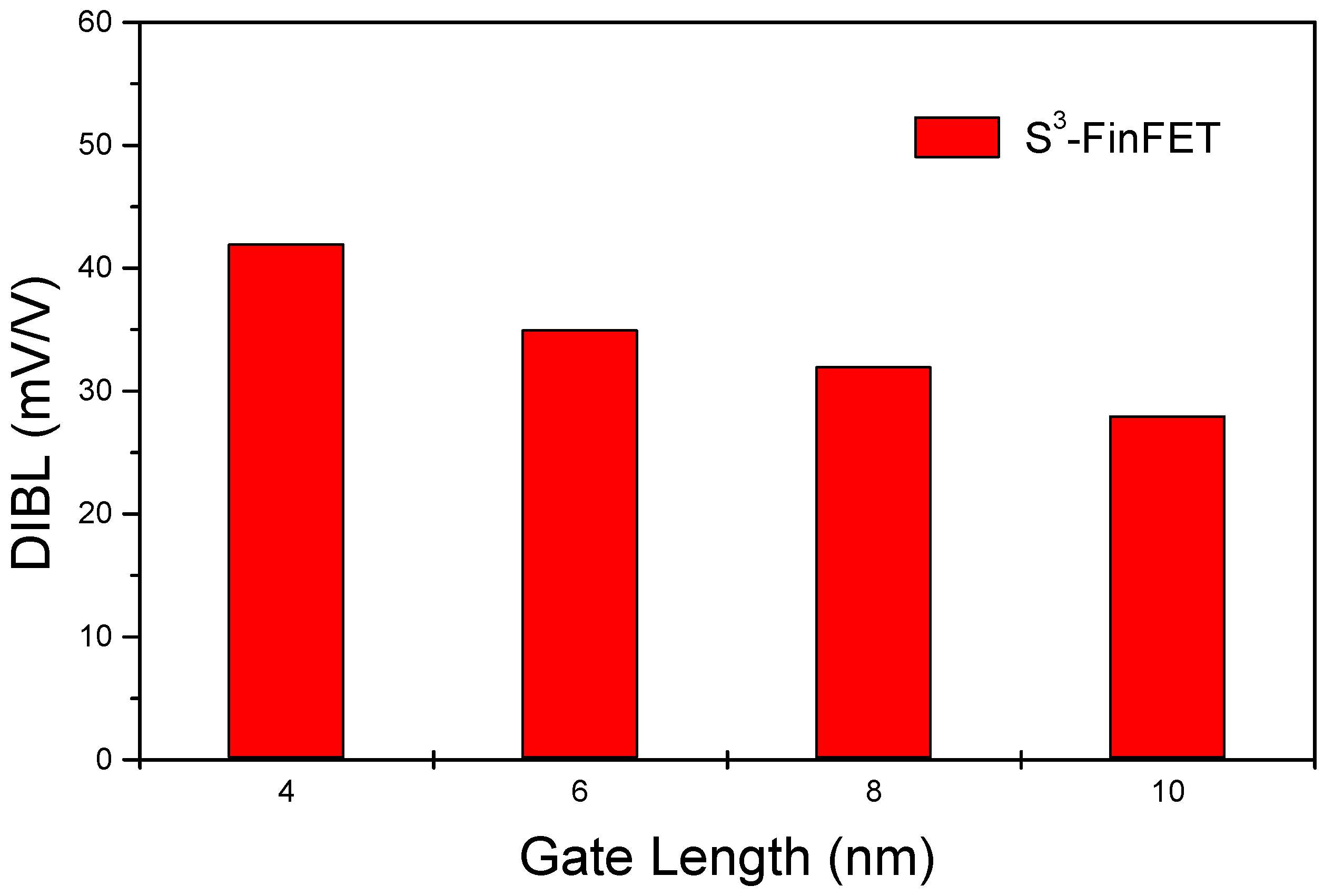

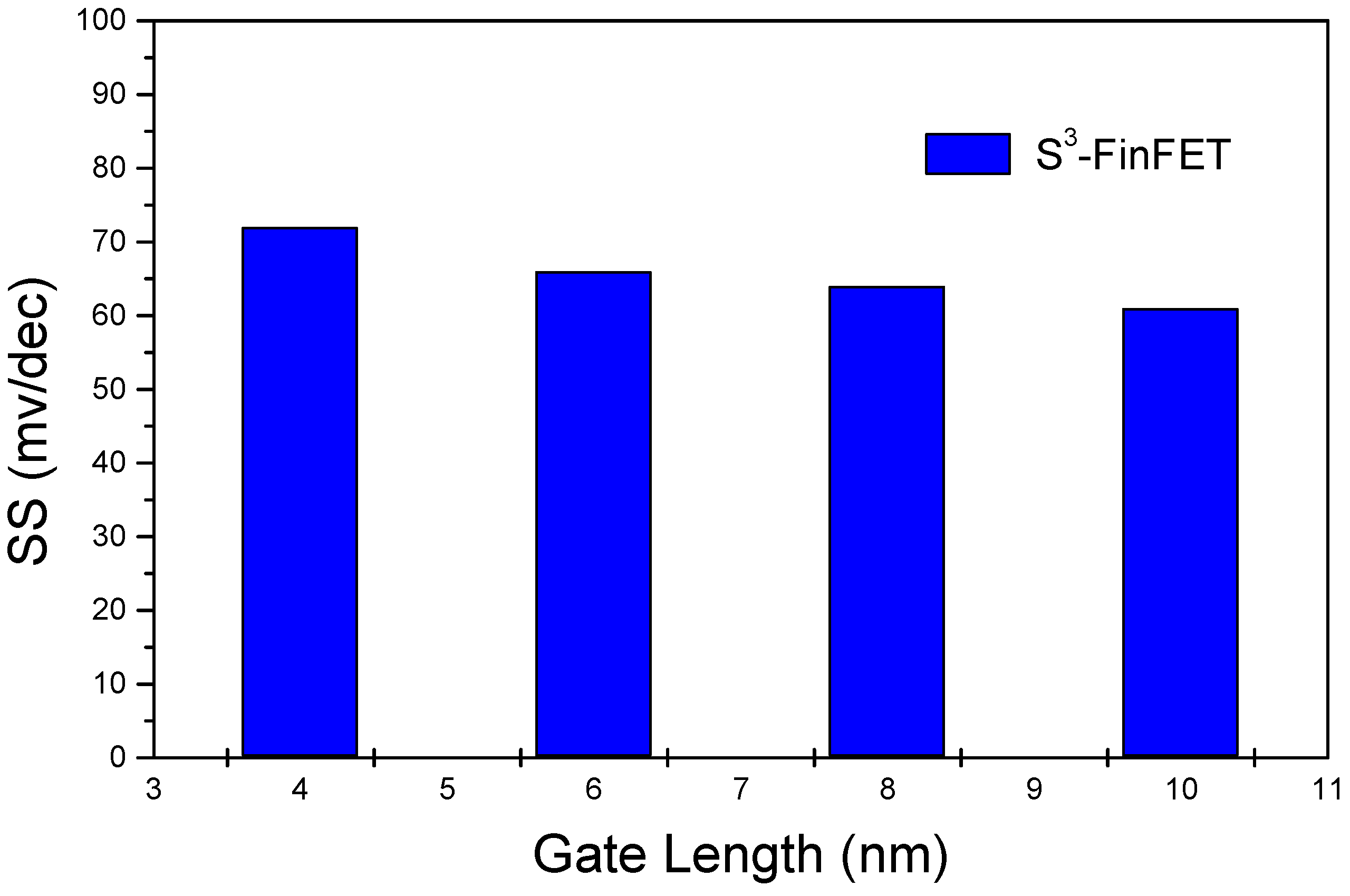

The DIBL and subthreshold swing (SS) of the proposed S

3-FinFET are plotted in

Figure 8 and

Figure 9, respectively. DIBL is calculated by measuring the change in threshold voltage (V

th) with respect to the change in drain voltage (V

D), using the following formula [

20]:

where Vth

(VD=low) and Vth

(VD=high) are the threshold voltages extracted at low and high drain biases, respectively. This parameter quantifies the extent to which the drain voltage influences the channel barrier, indicating short-channel effects.

The DIBL remains below 50 mV/V across the entire simulated gate length range, reflecting excellent suppression of drain-induced barrier lowering in the S3-FinFET. This performance is attributed to the serial capacitance effect of the three-layer spacer stack. Specifically, the low-k Si3N4 middle layer acts as a bottleneck that impedes the penetration of the drain’s electric field into the channel. As a result, a significant portion of the drain-induced voltage drops across the spacer itself, minimizing potential modulation of the channel barrier and enhancing threshold voltage stability under bias stress.

Meanwhile, the subthreshold swing exhibits minimal variation with changes in gate length and fin width, owing to the strong electrostatic insulation provided by the silicon-on-insulator (SOI) substrate and buried oxide (BOX) layer. These layers effectively block substrate-related parasitic effects, leading to consistent and improved subthreshold characteristics.

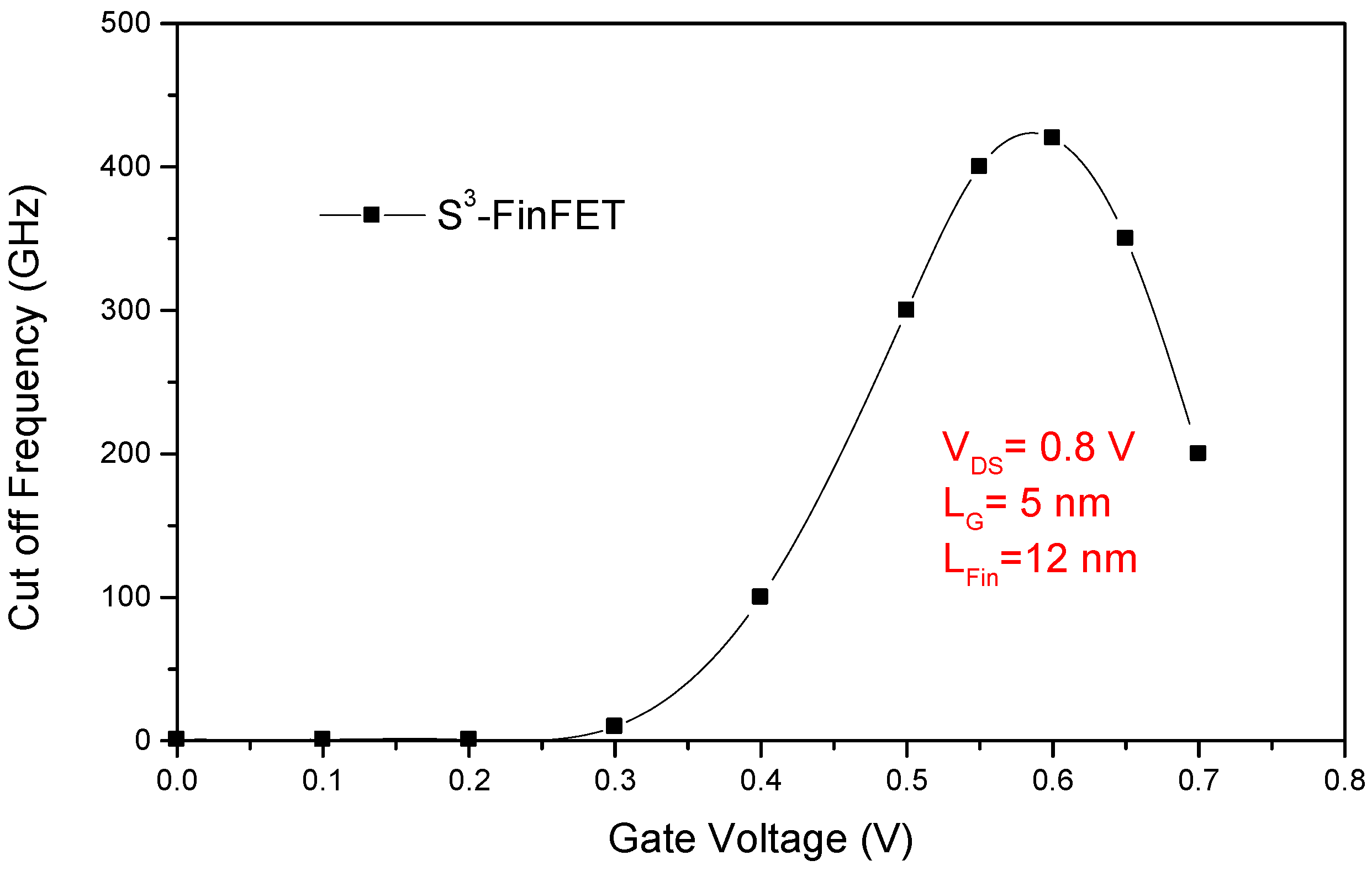

Figure 10 illustrates the gate-to-drain capacitance (C

gd) and total gate capacitance (C

gg) of the proposed S

3-FinFET as functions of the gate voltage (V

GS), while the cut-off frequency (f

T) versus V

GS is presented in

Figure 11. The relatively low C

gd, commonly known as the Miller capacitance or feedback capacitance, plays a crucial role in minimizing delay and dynamic power consumption, especially in FPGA interconnects and logic switches where fast and efficient signal transitions are essential. The S

3-FinFET exhibits good behavior in terms of gate-to-drain capacitance. Additionally, the total gate capacitance, C

gg, is the sum of C

gs and C

gd, reflecting both the intrinsic gate-channel coupling and parasitic capacitances. The near-linear variation of C

gg with V

GS suggests stable gate modulation with minimal charge trapping effects across the operating voltage range, indicating reliable device behavior under different bias conditions.

The cut-off frequency (fT), calculated using a small-signal approximation, captures the high-frequency performance of the device. This figure of merit benefits from the combination of high transconductance and relatively low total gate capacitance, both resulting from the optimized gate electrostatics and spacer engineering in the S3-FinFET. Efficient coupling between the gate and the channel reduces capacitive delays, enabling the device to sustain high-speed operation, which is critical for RF and high-frequency digital applications.

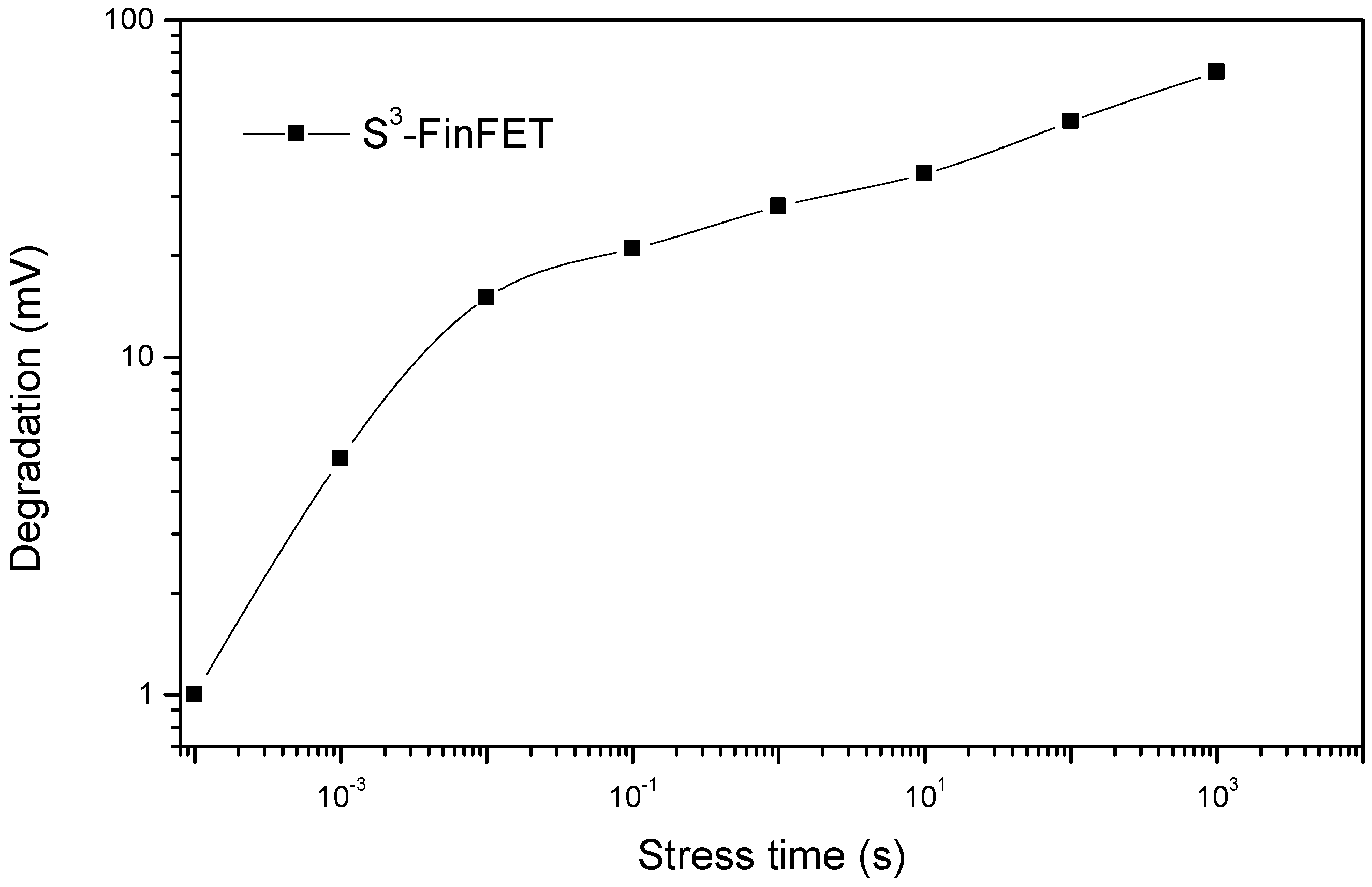

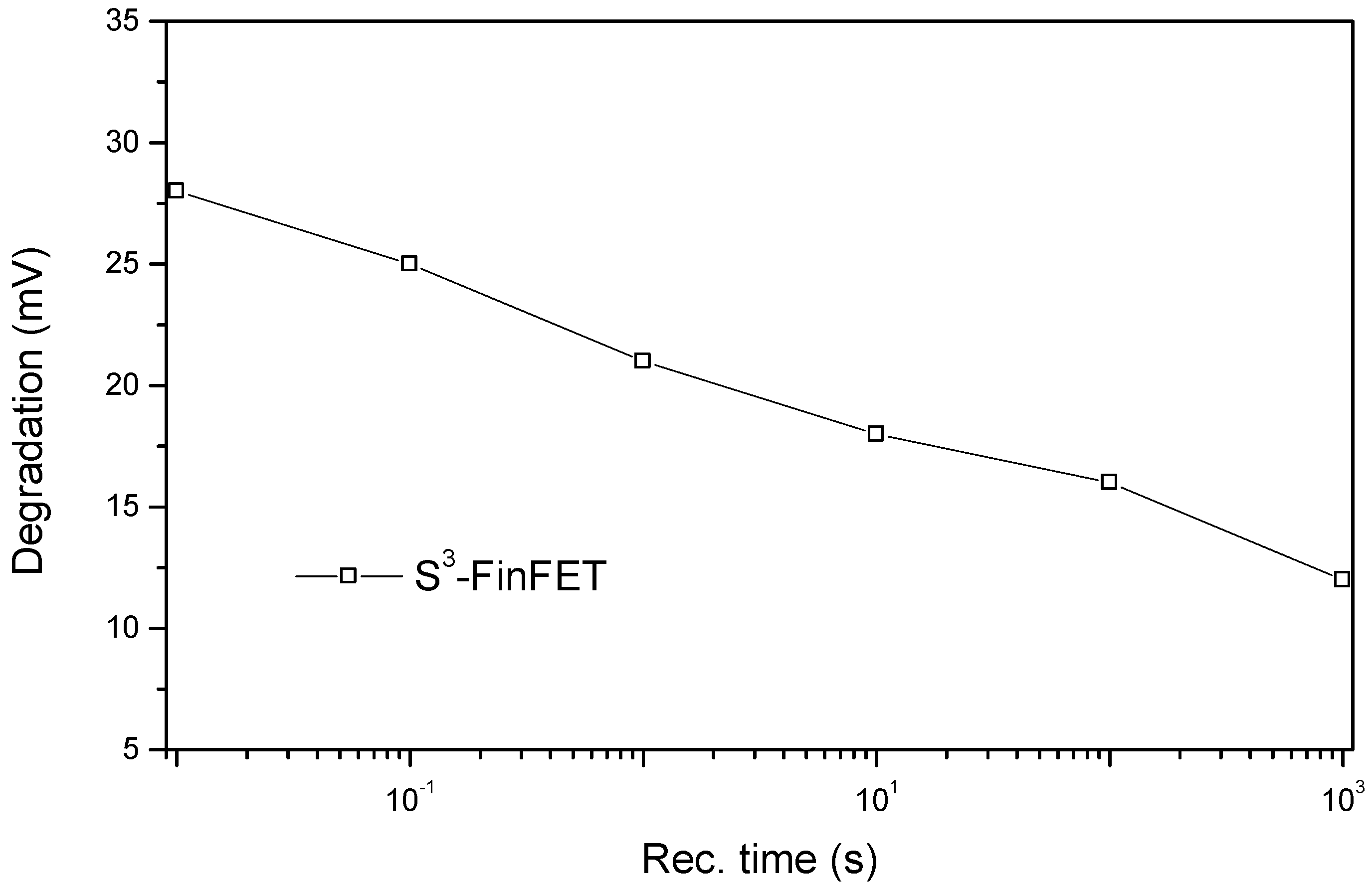

Negative Bias Temperature Instability (NBTI) is a key reliability concern in transistors [

21]. NBTI occurs when a device is subjected to negative gate bias (V

G < 0) at elevated temperatures, which is typical during circuit operation. Over time, this stress causes the generation of interface traps and positive fixed charges in the gate dielectric near the interface. These defects lead to a shift in the threshold voltage (ΔV

th), reducing drive current and degrading device performance. As device dimensions scale, quantum confinement pushes the inversion-layer charge centroid away from the interface [

21]. Therefore, understanding and mitigating NBTI in a device’s structure is critical for ensuring long-term device reliability.

In this study, NBTI stress is simulated using Silvaco by applying a negative gate bias to the channel device to replicate the stress conditions responsible for NBTI degradation. Interface trap generation and recovery behavior are approximated using defined trap parameters at the Si/SiO

2 interface within the simulation environment. Transient simulations are employed to observe the evolution of threshold voltage shift (ΔV

th) during both stress and recovery intervals. This method enables an estimation of NBTI effects on device reliability under realistic operating conditions. The results are shown in

Figure 12 and

Figure 13. During NBTI stress, the threshold voltage shift (ΔV

th) increases over time, mainly due to the continuous growth of interface traps. This causes ΔV

th to worsen as stress time progresses. When the stress is stopped and recovery begins, ΔV

th decreases gradually because of trap passivation and neutralization, but this recovery happens over a much longer time scale compared to the fast initial increase during stress.

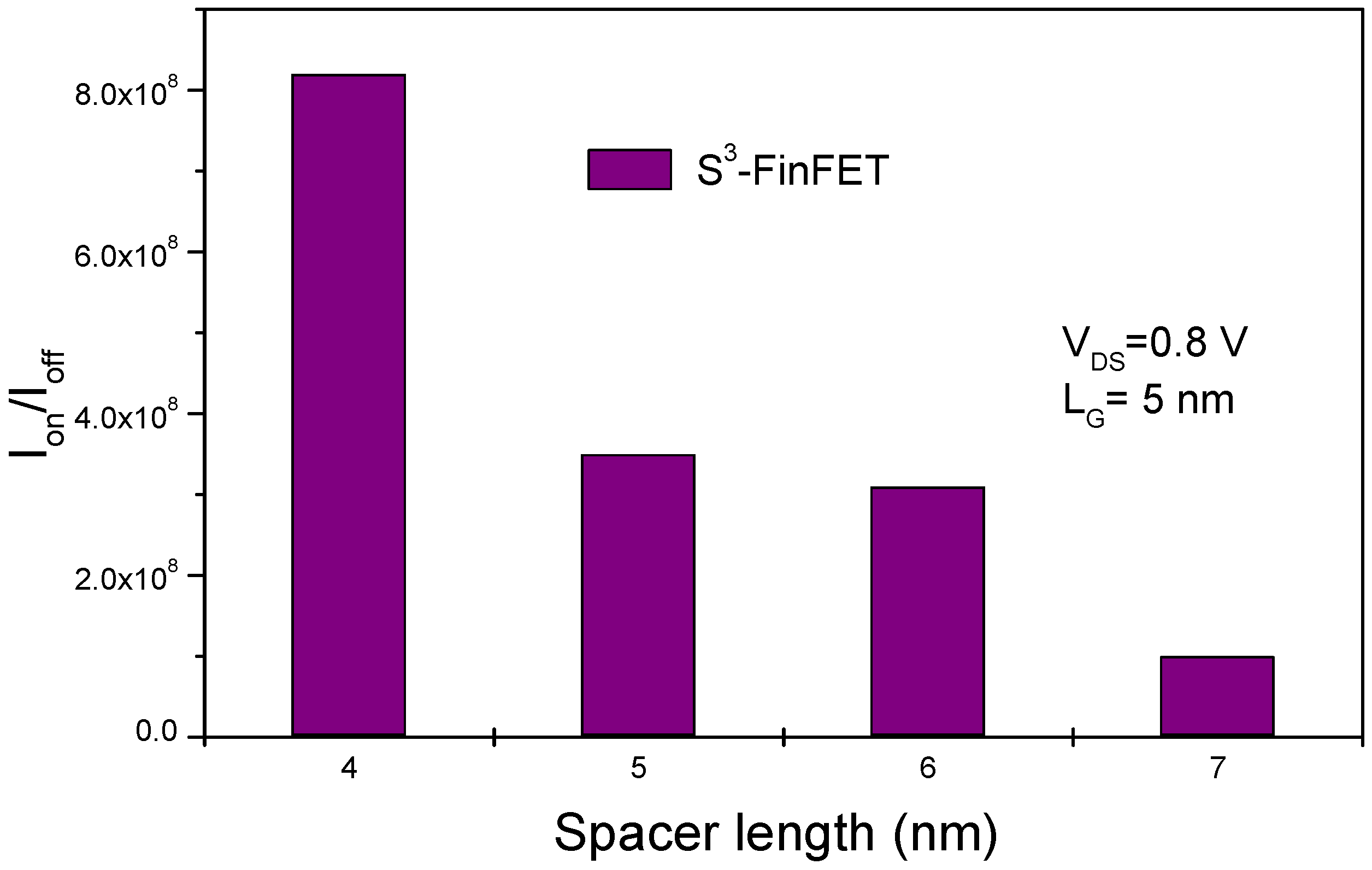

The impacts of spacer height and length scaling are critical factors influencing the electrical performance of the proposed S

3-FinFET structure.

Figure 14 and

Figure 15 show the effects of variations in spacer height and spacer length, respectively.

Increasing the spacer height in the proposed S3-FinFET, while keeping gate and spacer length fixed, reduces the gate’s ability to effectively control the channel. This weaker control allows more leakage current to flow when the transistor should be off, decreasing power efficiency. Additionally, as spacers’ heights increase, the aspect ratio of the spacer’s height to its length decreases, meaning that the spacer becomes relatively thinner compared to its height. This change in device geometry further contributes to increased leakage currents and degraded overall device performance.

Decreasing the spacer length brings the source and drain regions closer to the gate, which can improve short-channel control and enhance the ION/IOFF ratio. This happens because a narrower spacer reduces the distance between the gate and the lightly doped drain extension regions, allowing the gate to better suppress leakage and enhance drive current. However, too much reduction in spacer length can lead to parasitic capacitance increase and short-channel effects, which may eventually impair performance. Moderate spacer length scaling can therefore increase ION/IOFF.

To evaluate the advantages of the proposed S

3-FinFET structure, a performance comparison was conducted with another configuration: a FinFET using only HfO

2 as the spacer material. Key device parameters, including I

ON/I

OFF ratio, drain-induced barrier lowering (DIBL), and subthreshold swing (SS) are summarized in

Table 2.

The S3-FinFET achieves a significantly higher ION/IOFF ratio, indicating that drive current is improved while low off-state leakage is maintained. Furthermore, the S3-FinFET exhibits markedly reduced DIBL and SS values, suggesting better electrostatic control and reduced short-channel effects. These results confirm that the S3 spacer configuration offers superior device performance compared to the FinFET with HfO2-only spacer.