Design and Study of a Novel P-Type Junctionless FET for High Performance of CMOS Inverter

Abstract

1. Introduction

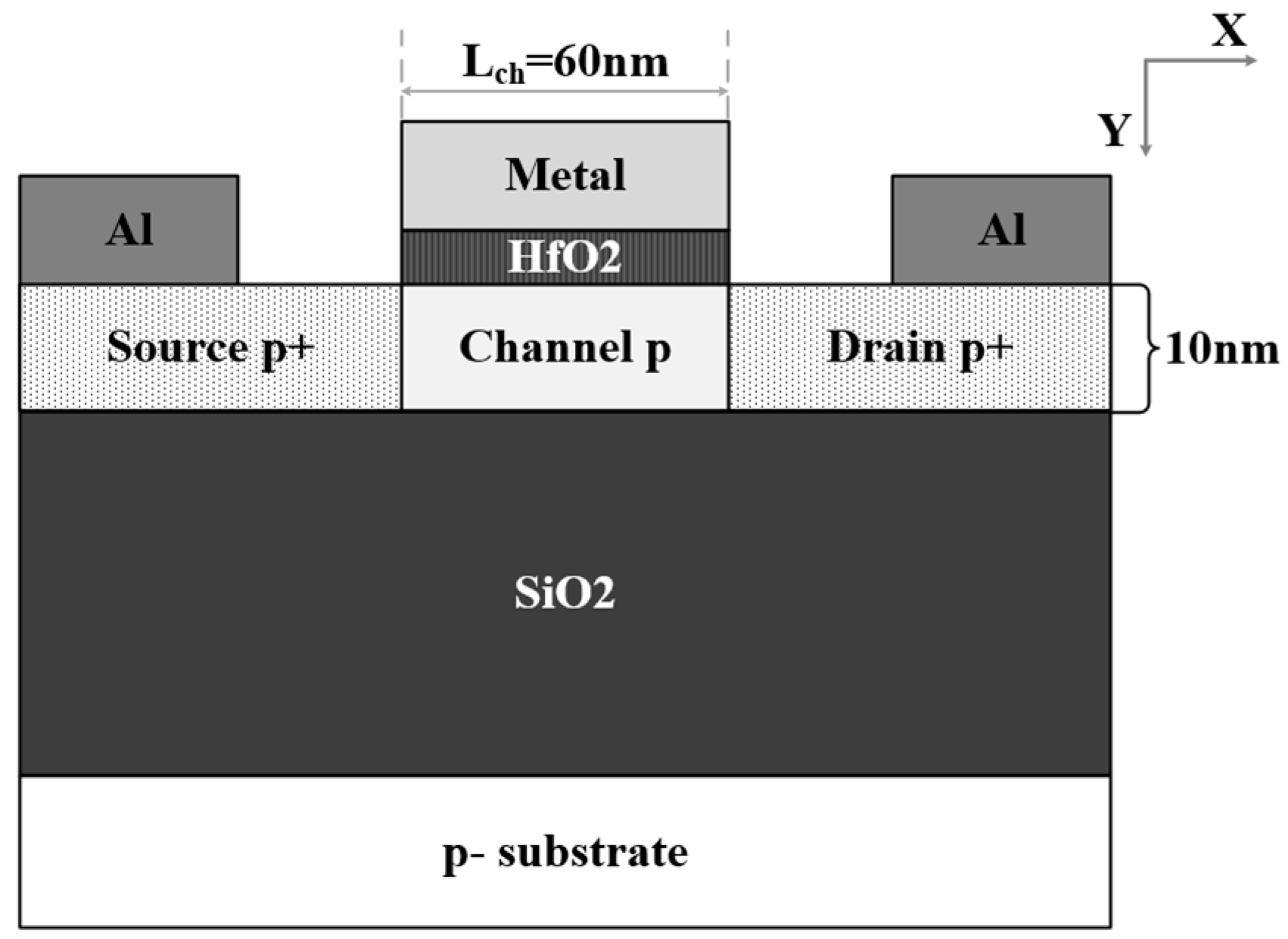

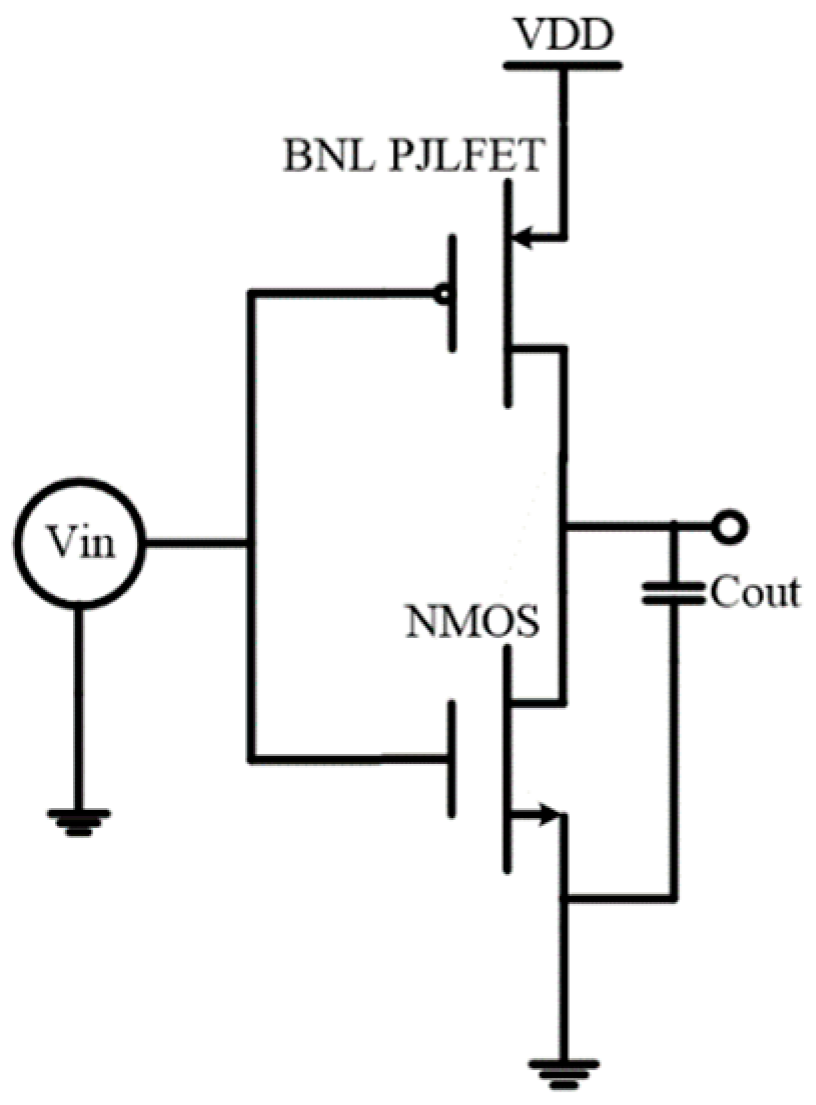

2. Device Structure and Simulation Approach

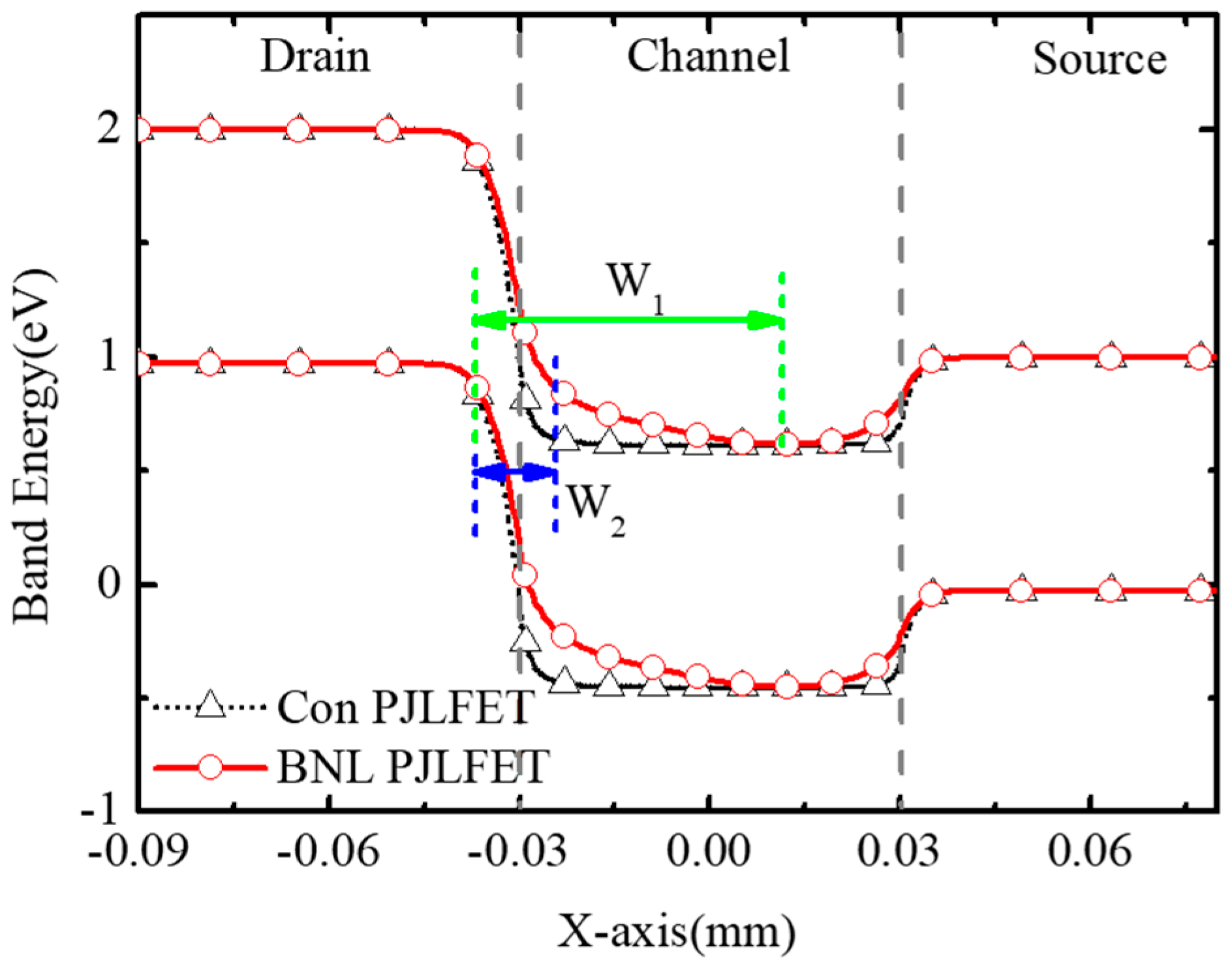

3. Operation Principle of BNL PJLFET

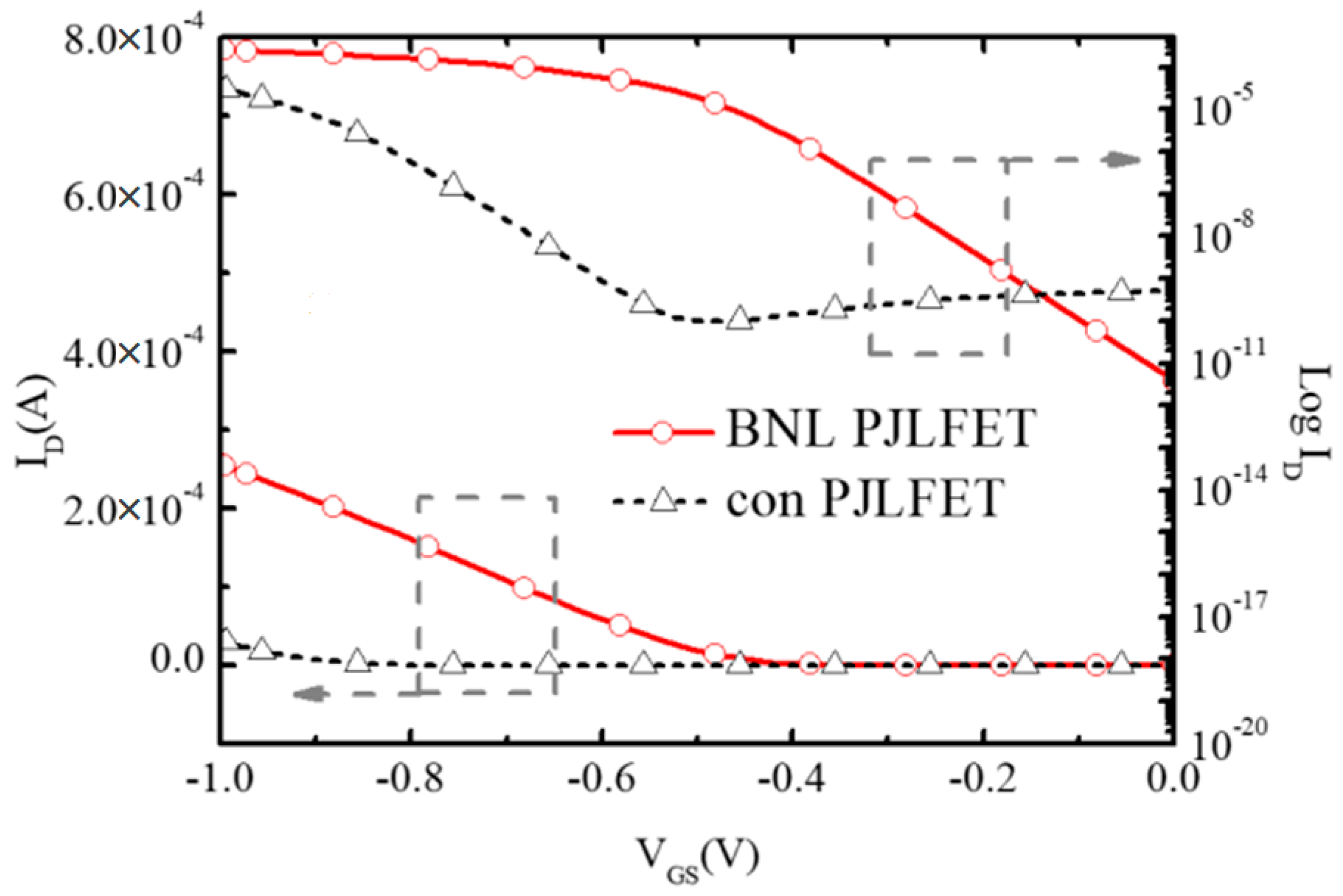

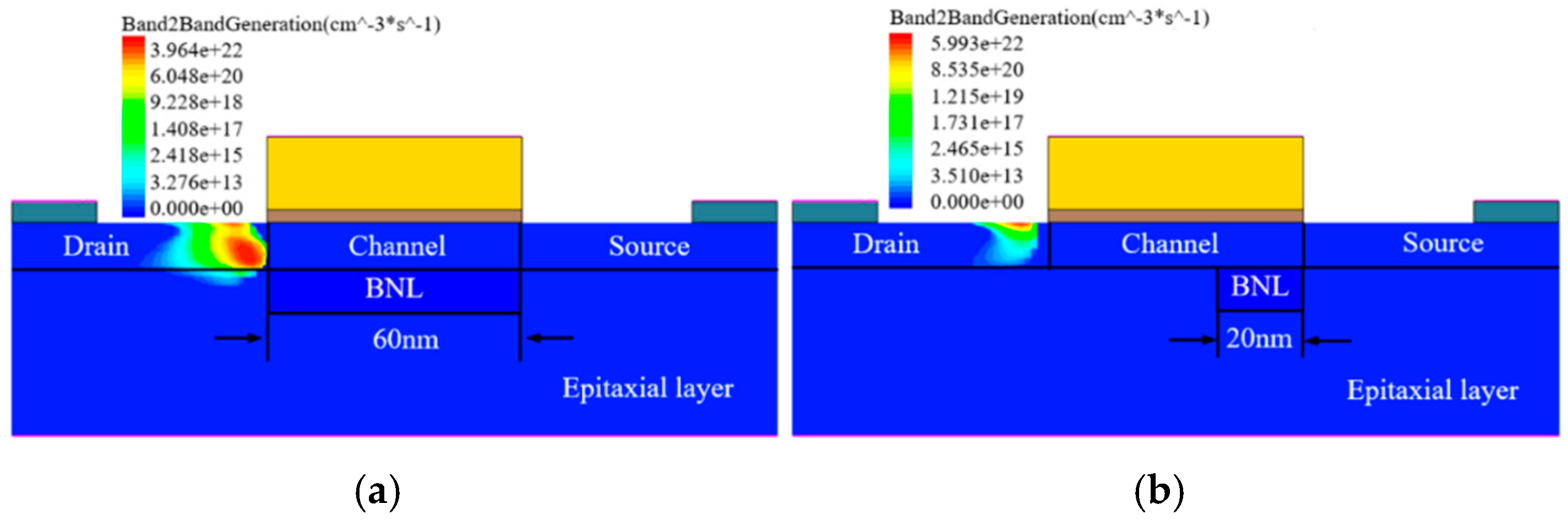

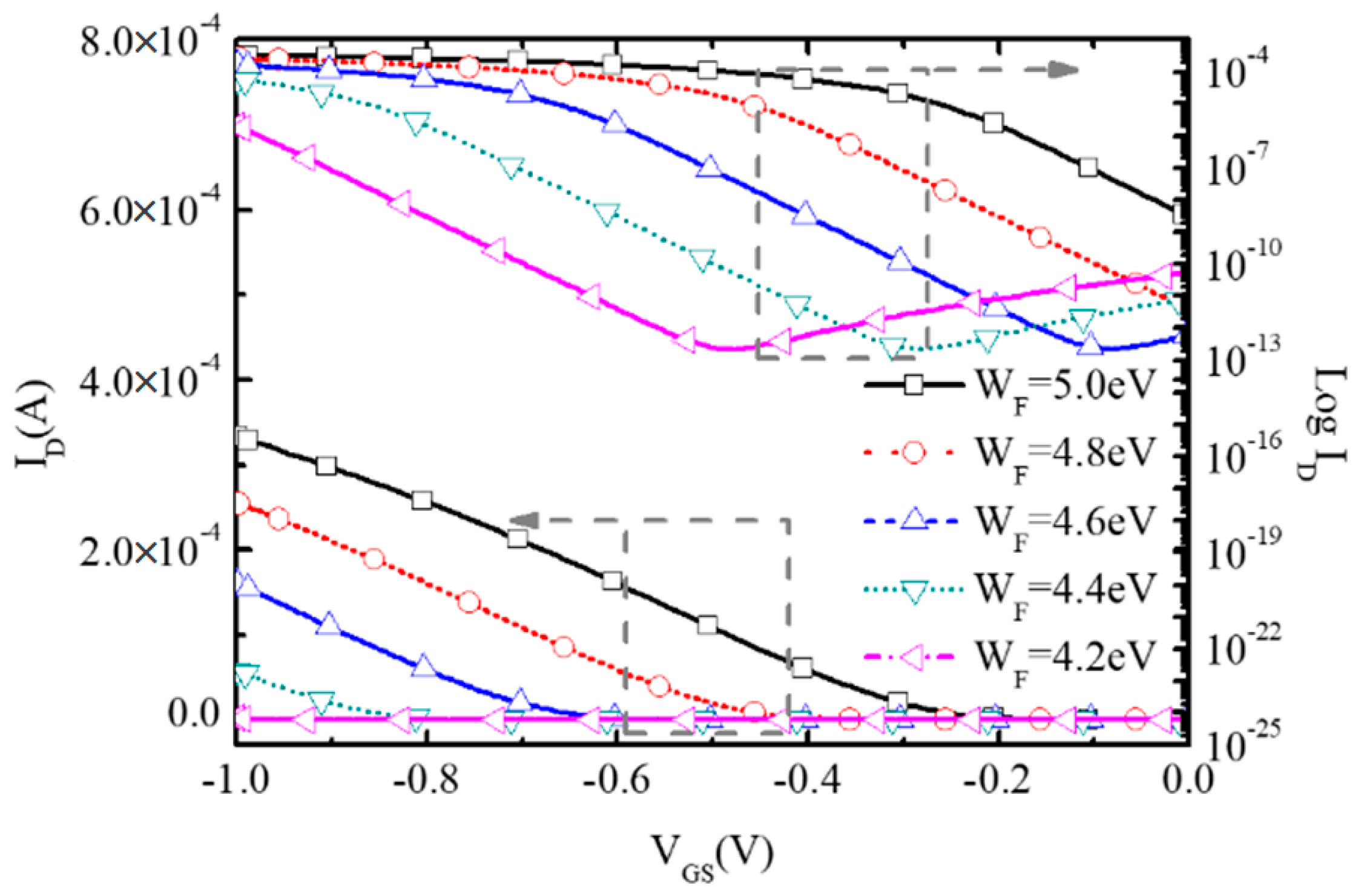

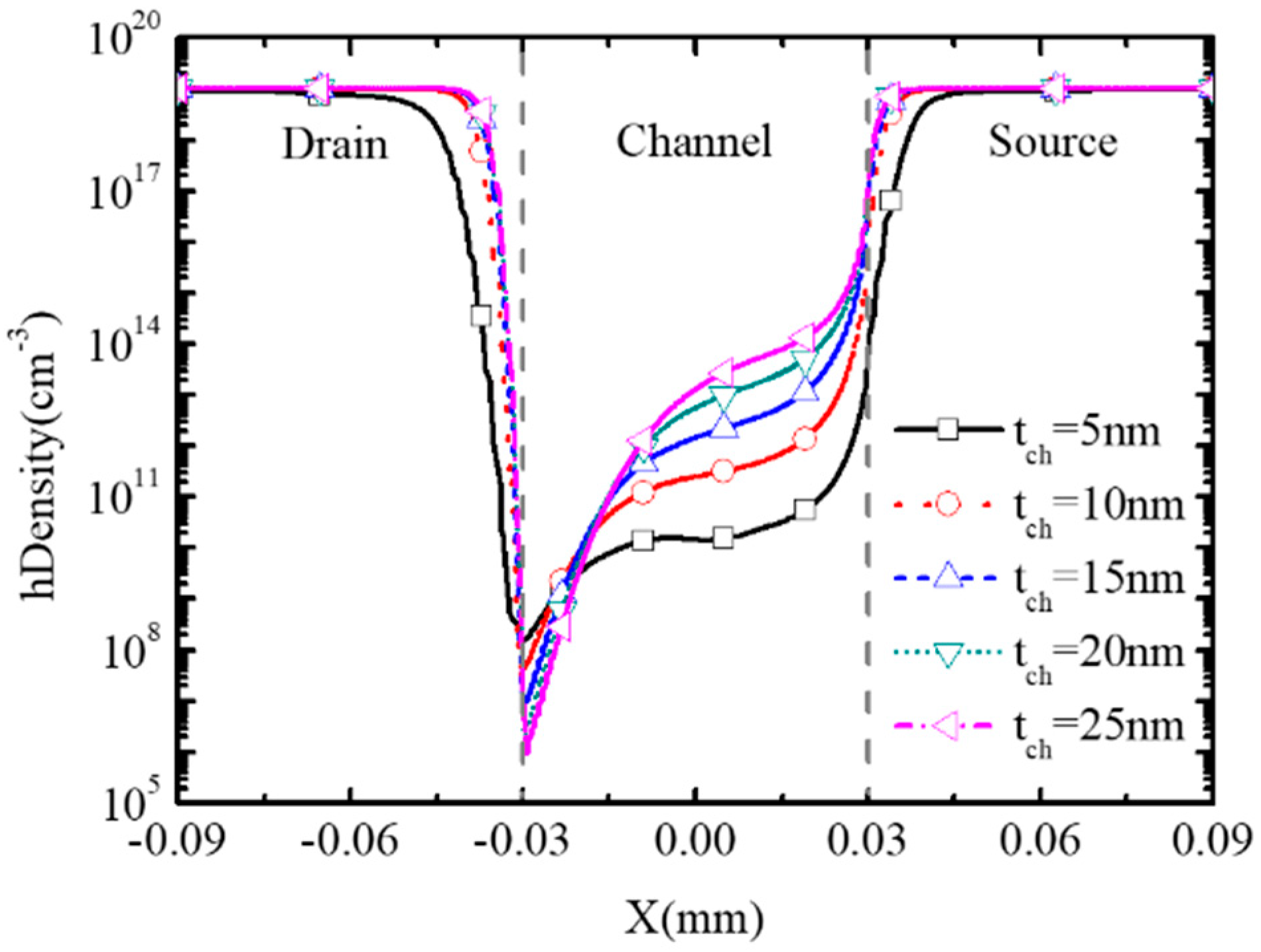

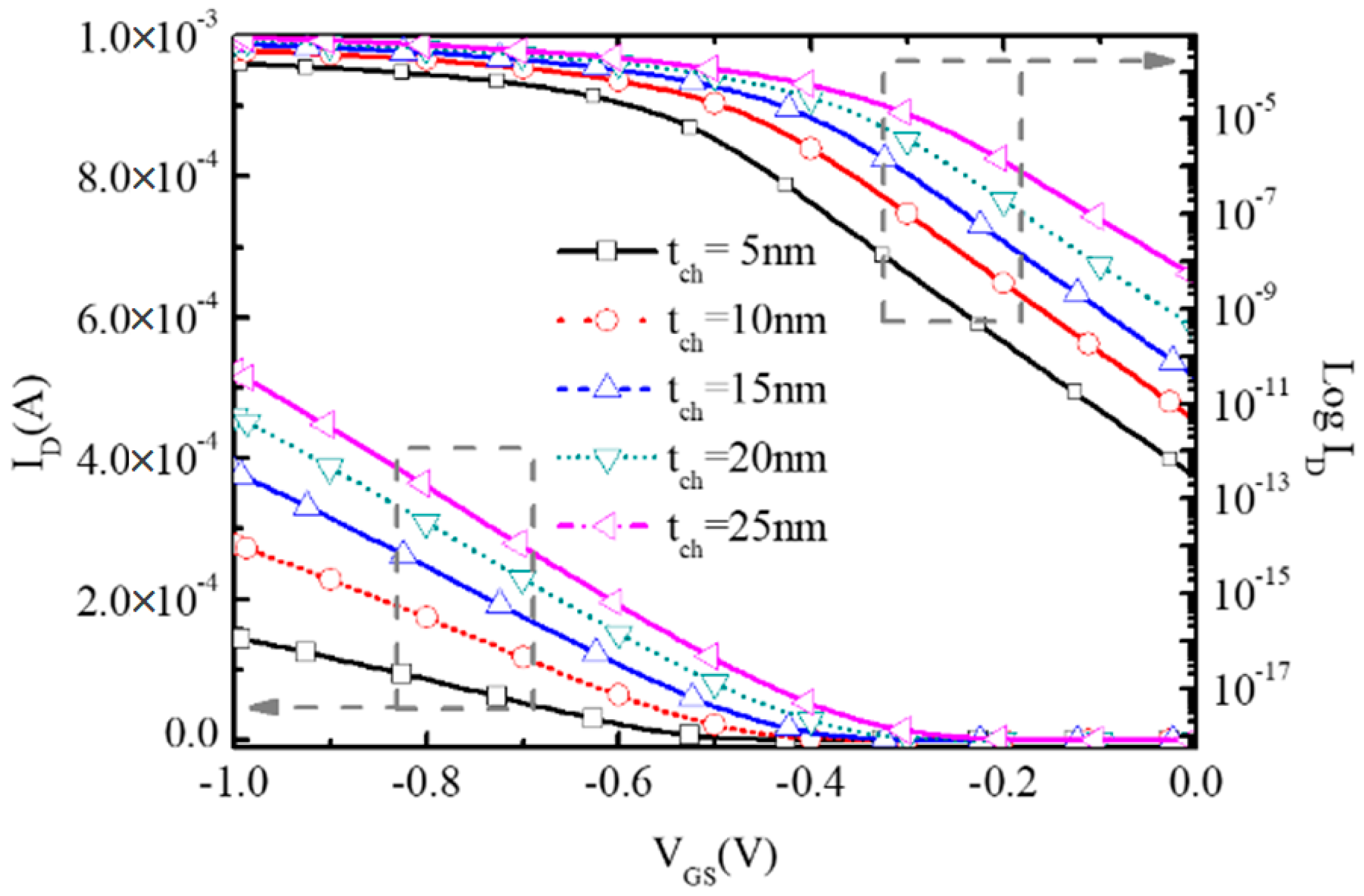

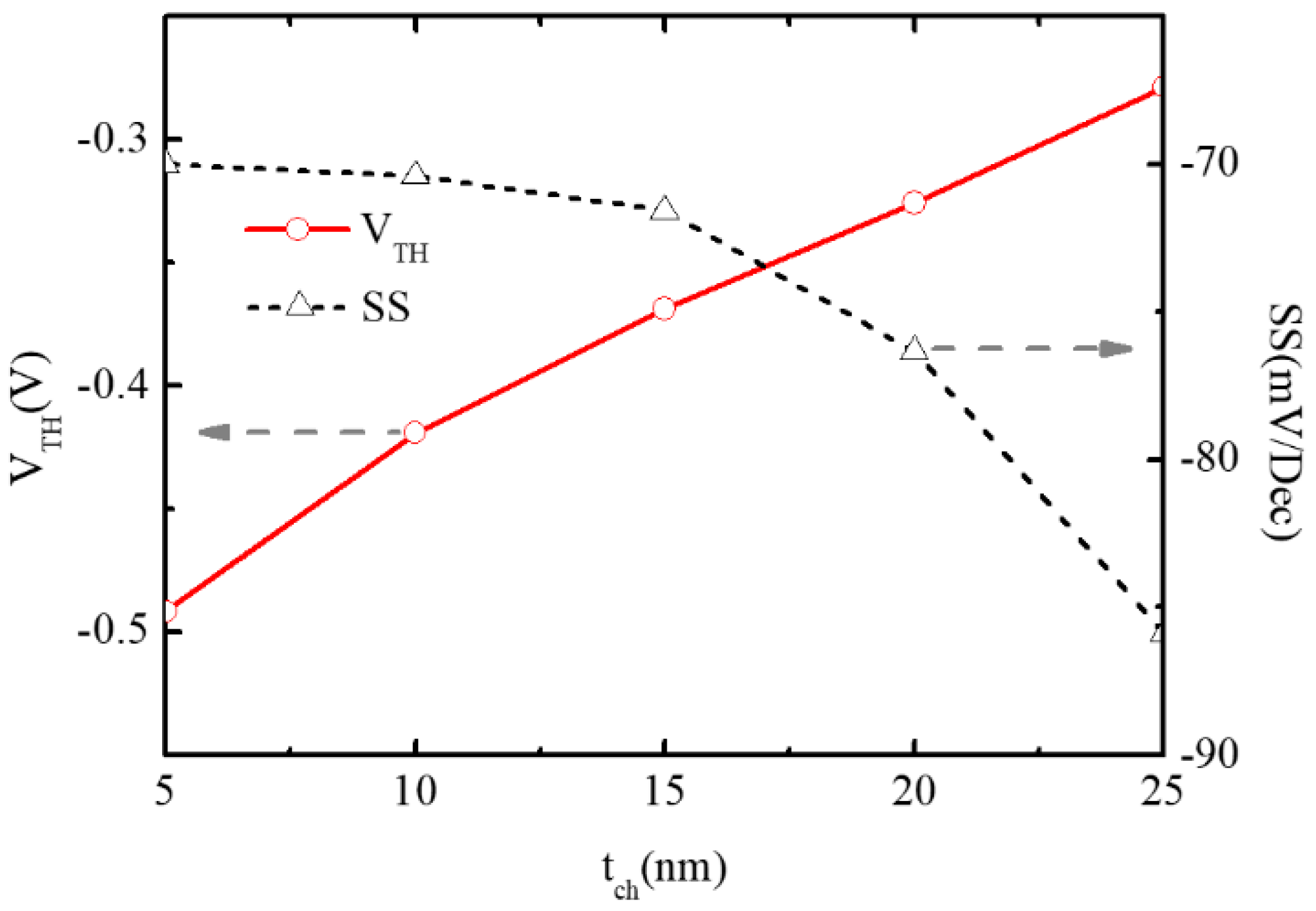

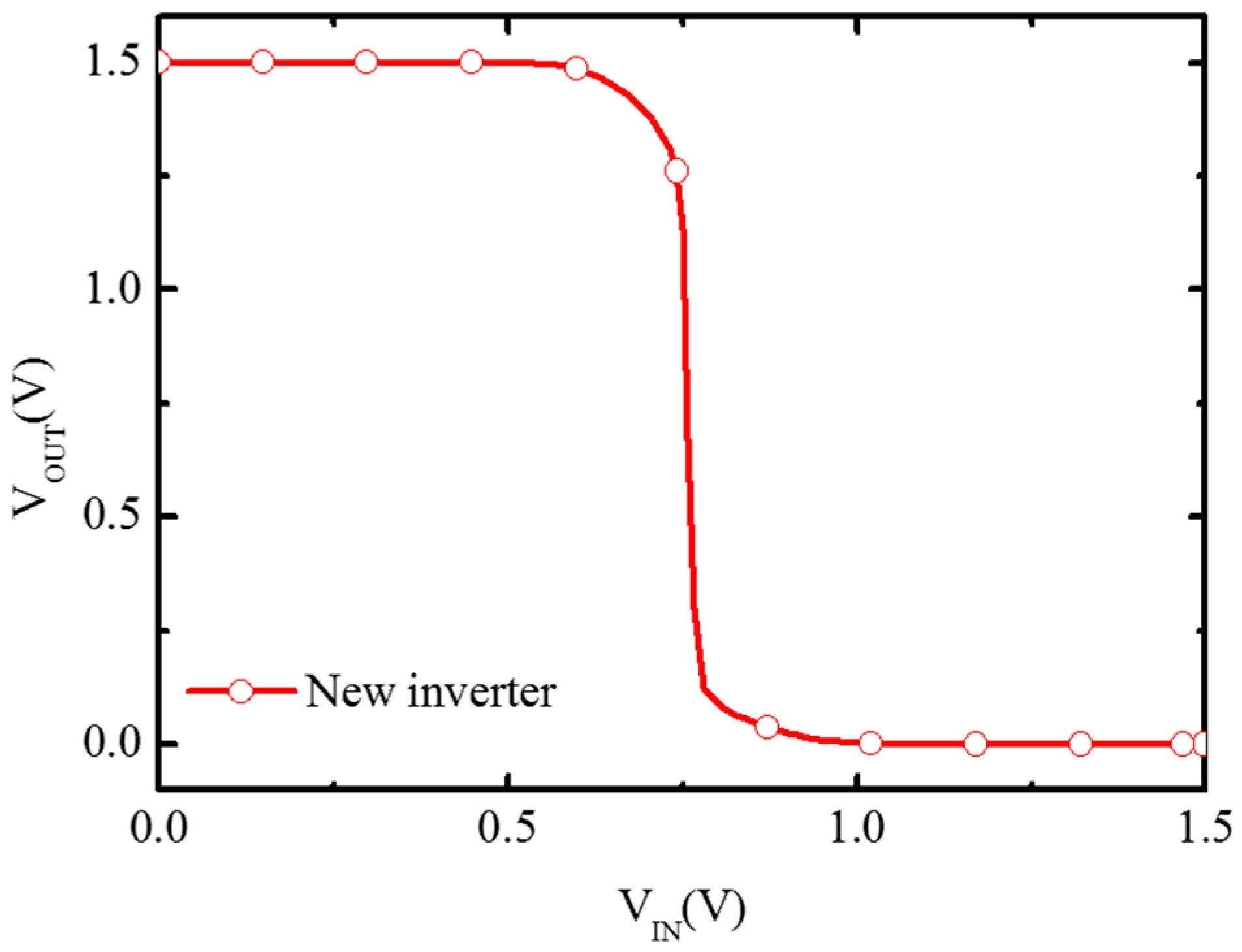

4. Results and Discussion

5. Investigation

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Ghosh, B.; Bal, P.; Mondal, P. A junctionless tunnel field effect transistor with low subthreshold slope. J. Comput. Electron. 2013, 12, 428–436. [Google Scholar] [CrossRef]

- Lee, C.W.; Ferain, I.; Kranti, A.; Akhavan, N.D.; Razavi, P.; Yan, R.; Yu, R.; O’Neill, B.; Blake, A.; White, M.; et al. Short-channel junctionless nanowire transistors. In Proceedings of the 2010 International Conference on Solid Sate Devices and Materials (SSDM2010), Tokyo, Japan, 22–24 September 2010; pp. 1044–1045. [Google Scholar]

- Boucart, K.; Ionescu, A.M. Double-gate tunnel FET with high-κ gate dielectric. IEEE Trans. Electron Devices 2007, 54, 1725–1733. [Google Scholar] [CrossRef]

- Tang, X.; Hua, T.; Liu, Y.; Han, Z. Heterogeneous CMOS Integration of InGaAs-OI nMOSFETs and Ge pMOSFETs Based on Dual-Gate Oxide Technique. Micromachines 2022, 13, 1806. [Google Scholar] [CrossRef]

- Arimura, H.; Cott, D.; Boccardi, G.; Loo, R.; Wostyn, K.; Brus, S.; Capogreco, E.; Opdebeeck, A.; Witters, L.; Conard, T.; et al. A record GmSAT/SSSAT and PBTI reliability in Si-passivated Ge nFinFETs by improved gate stack surface preparation. In Proceedings of the 2019 Symposium on VLSI Technology, Kyoto, Japan, 9–14 June 2019; pp. T92–T93. [Google Scholar]

- Capogreco, E.; Arimura, H.; Witters, L.; Vohra, A.; Porret, C.; Loo, R.; De Keersgieter, A.; Dupuy, E.; Marinov, D.; Hikavyy, A.; et al. High performance strained Germanium Gate All Around p-channel devices with excellent electrostatic control for sub-Jtlnm LG. In Proceedings of the 2019 Symposium on VLSI Technology, Kyoto, Japan, 9–14 June 2019; pp. T94–T95. [Google Scholar]

- Cai, X.; Vardi, A.; Grajal, J.; Alamo, J.A.D. Reassessing InGaAs for logic: Mobility extraction in sub-10nm fin-width FinFETs. In Proceedings of the 2019 Symposium on VLSI Technology, Kyoto, Japan, 9–14 June 2019; pp. T246–T247. [Google Scholar]

- Ahn, T.J.; Yu, Y.S. Circuit Simulation Considering Electrical Coupling in Monolithic 3D Logics with Junctionless FETs. Micromachines 2020, 11, 887. [Google Scholar] [CrossRef] [PubMed]

- Lee, G.J.; Yu, Y.S. An Investigation of the Effect of the Work-Function Variation of a Monolithic 3D Inverter Stacked with MOSFETs. Micromachines 2022, 13, 1524. [Google Scholar] [CrossRef] [PubMed]

- Li, Z.-H.; Li, R.-L.; Jiang, Y.-L.; Zhang, Y.-W.; Cao, Y.-F.; Wang, X.-J. Performance Improvement by Blanket Boron Implant in the Sigma-Shaped Trench Before the Embedded SiGe Source/Drain Formation for 28-nm PMOSFET. IEEE Electron Device Lett. 2020, 41, 796–799. [Google Scholar] [CrossRef]

- Qureshi, S.; Mehrotra, S. Potential Well Based FDSOI MOS-FET: A Novel Planar Device for 10 nm Gate Length. In Proceedings of the 2019 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), San Jose, CA, USA, 14–17 October 2019; pp. 1–3. [Google Scholar]

- Sreenivasulu, V.B.; Prasad, M.; Deepthi, E.; Kumar, A.S. Analysis of Novel Core-Shell Junctionless Nnosheet FET for CMOS Logic Applications. IEEE Access 2024, 12, 144479–144488. [Google Scholar] [CrossRef]

- Gu, J.; Zhang, Q.; Wu, Z.; Yao, J.; Zhang, Z.; Zhu, X.; Wang, G.; Li, J.; Zhang, Y.; Cai, Y.; et al. Cryogenic Transport Characteristics of P-Type Gate-All-Around Silicon Nanowire MOSFETs. Nanomaterials 2021, 11, 309. [Google Scholar] [CrossRef] [PubMed]

- Jhan, Y.-R.; Thirunavukkarasu, V.; Wang, C.-P.; Wu, Y.-C. Performance evaluation of Silicon and Germanium ultrathin body (1 nm) junctionless field-effect transistor with ultrashort gate lengh (1 nm and 3 nm). IEEE Electron Device Lett. 2015, 36, 654–656. [Google Scholar] [CrossRef]

- Chaudhary, S.; Dewan, B.; Singh, D.; Yadav, M. Impact of Temperature Sensitivity on Dead Channel Junctionless FET for Linearity and High Frequency. Semicond. Sci. Technol. 2024, 39, 125012. [Google Scholar] [CrossRef]

- Parmar, J.S.; Sahu, C. CMOS-Compatible Ex-Situ Incorporated Junctionless Enhancement-Mode Thin Polysilicon Film FET pH Sensor. IEEE Trans. Device Mater. Reliab. 2021, 21, 2–8. [Google Scholar] [CrossRef]

- Sreenivasulu, V.B.; Kumar, N.A.; Lokesh, V.; Ajayan, J.; Uma, M.; Vijayvargiya, V. Design of Resistive Load Inverter and Common Source Amplifier Circuits using Symmetric and Asymmetric Nanowire FETs. J. Electron. Meter. 2023, 52, 7268–7279. [Google Scholar] [CrossRef]

- Ye, H.Y.; Chung, C.C.; Liu, C.W. Mobility Calculation of Ge Nanowire Junctionless and Inversion-Mode Nanowire NFETs with Size and Shape Dependence. IEEE Trans. Electron Devices 2018, 65, 5259–5300. [Google Scholar] [CrossRef]

- Shubham, S.; Mamidala, J.K. Insight into Lateral Band-to-Band-Tunneling in Nanowire Junctionless FETs. IEEE Trans. Electron Devices 2016, 63, 4138–4142. [Google Scholar]

- Shubham, S.; Mamidala, J.K. Physical Insights Into the Nature of Gate-Induced Drain Leakage in Ultrashort Channel Nanowire FETs. IEEE Trans. Electron Devices 2017, 64, 2604–2610. [Google Scholar]

- Jung, S.G.; Yu, H.Y. Impact of Random Dopant Fluctuation on n-Type Ge Junctionless FinFETs with Met-al-Interlayer-Semiconductor Source/Drain Contact Structure. IEEE J. Electron Devices Soc. 2019, 7, 1119–1124. [Google Scholar] [CrossRef]

- Jung, S.-G.; Kim, S.-H.; Kim, G.-S.; Yu, H.-Y. Effects of metal-interlayer-semiconductor source/drain contact structure on n-type germanium junctionless FinFETs. IEEE Trans. Electron Devices 2018, 65, 3136–3141. [Google Scholar] [CrossRef]

- Sahay, S.; Kumar, M.J. Junctionless Field-Effect Transistors; Wiley-IEEE Press: Hoboken, NJ, USA, 2019. [Google Scholar]

- Choi, W.Y.; Park, B.; Lee, J.D.; Liu, T.K. Tunneling Field-Effect Transistors (TFETs) with Subthreshold Swing (SS) Less Than 60mV/dec. IEEE Electron Device Lett. 2007, 28, 743–745. [Google Scholar] [CrossRef]

- Mamidala, J.K.; Vishnoi, R.; Pandey, P. Simulation of TFETs. In Tunnel Field-Effect Transistors (TFET): Modelling and Simulation; Wiley: Hoboken, NJ, USA, 2017; pp. 181–193. [Google Scholar]

- Liu, X.Y.; Hu, H.Y.; Wang, B.; Wang, M.; Han, G.Q.; Cui, S.M.; Zhang, H.M. Study of novel junctionless Ge n-Tunneling Field-Effect Transistors with lightly doped drain (LDD) region. Superlattices Microstruct. 2017, 102, 7–16. [Google Scholar] [CrossRef]

| Parameter | BNL PJLFET | CON PJLFET |

|---|---|---|

| Gate length (Lch) | 60 nm | 60 nm |

| Channel doping concentration | 1 × 1018 cm−3 | 1 × 1018 cm−3 |

| HfO2 thickness (Tox) | 3 nm | 3 nm |

| Buried layer length (LBN) | 30 nm | / |

| Epitaxial layer doping (Nepi) | 1 × 1016 cm−3 | / |

| Buried performing concentration (NBN) | 1 × 1019 cm−3 | / |

| Work function of gate electrode | 4.8 eV | 4.1 eV |

| Work function of source/drain electrode | 4.1 eV | 4.1 eV |

| Source/drain doping concentration | 1 × 1020 cm−3 | 1 × 1020 cm−3 |

| Parameter | BNL PJLFET | CON NMOS |

|---|---|---|

| Gate length (Lch) | 60 nm | 60 nm |

| Channel doping concentration | 1 × 1018 cm−3 | 1 × 1018 cm−3 |

| HfO2 thickness (Tox) | 3 nm | 3 nm |

| Buried layer length (LBN) | 30 nm | / |

| Epitaxial layer doping (Nepi) | 1 × 1016 cm−3 | 1 × 1016 cm−3 |

| Buried performing concentration (NBN) | 1 × 1019 cm−3 | / |

| Work function of gate electrode | 4.7 eV | 4.7 eV |

| Work function of source/drain electrode | 4.1 eV | 4.1 eV |

| Source/drain doping concentration | 1 × 1019 cm−3 | 1 × 1019 cm−3 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, B.; Tang, Z.; Song, Y.; Liu, L.; Yang, W.; Wu, L. Design and Study of a Novel P-Type Junctionless FET for High Performance of CMOS Inverter. Micromachines 2025, 16, 106. https://doi.org/10.3390/mi16010106

Wang B, Tang Z, Song Y, Liu L, Yang W, Wu L. Design and Study of a Novel P-Type Junctionless FET for High Performance of CMOS Inverter. Micromachines. 2025; 16(1):106. https://doi.org/10.3390/mi16010106

Chicago/Turabian StyleWang, Bin, Ziyuan Tang, Yuxiang Song, Lu Liu, Weitao Yang, and Longsheng Wu. 2025. "Design and Study of a Novel P-Type Junctionless FET for High Performance of CMOS Inverter" Micromachines 16, no. 1: 106. https://doi.org/10.3390/mi16010106

APA StyleWang, B., Tang, Z., Song, Y., Liu, L., Yang, W., & Wu, L. (2025). Design and Study of a Novel P-Type Junctionless FET for High Performance of CMOS Inverter. Micromachines, 16(1), 106. https://doi.org/10.3390/mi16010106