3.1. Influence of Different Drain Voltages on Electrical Characteristics of Devices

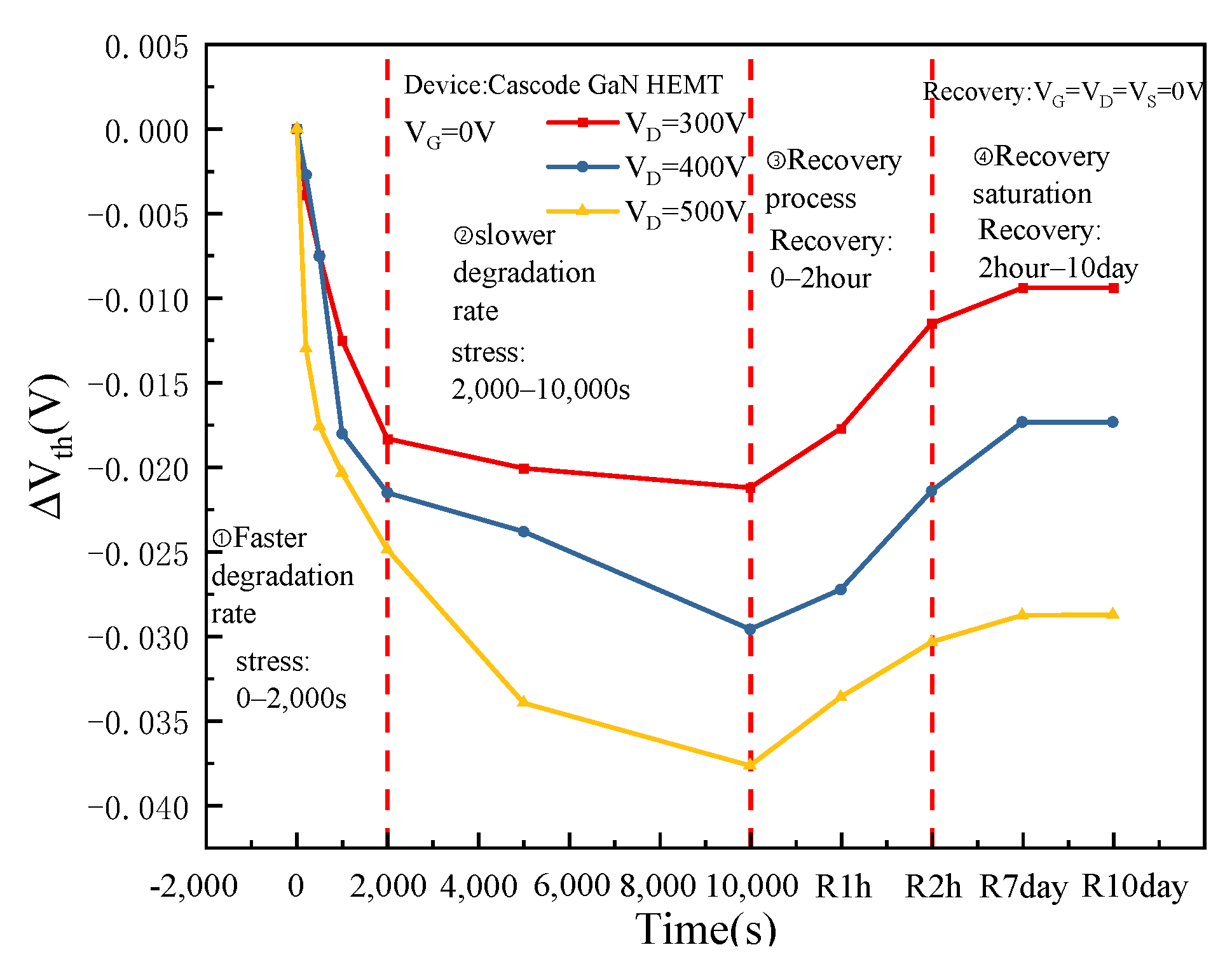

To explore the degradation of Cascode GaN HEMT power devices under off-state high-field stress, 300 V, 400 V, and 500 V high-field stress are applied at the drain electrode.

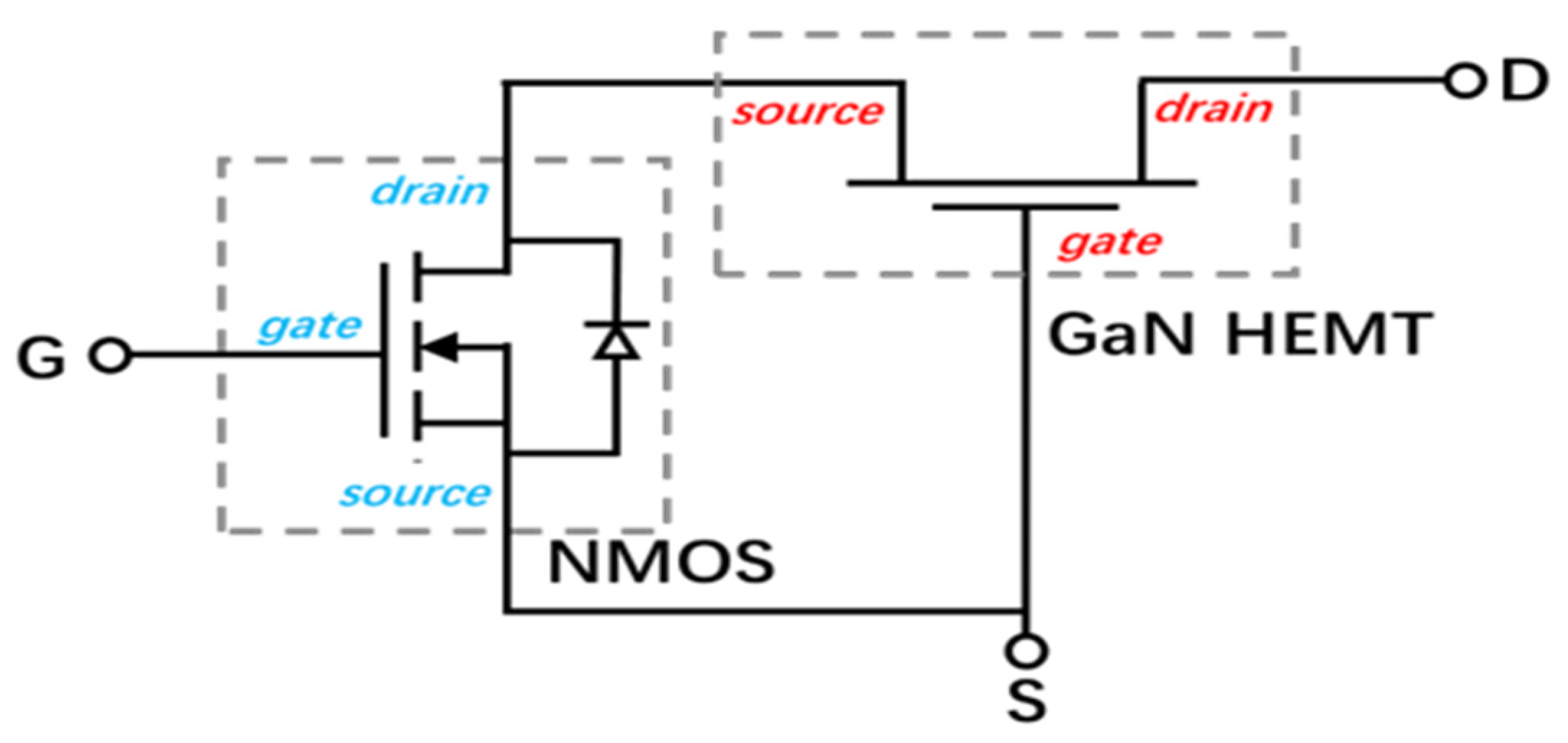

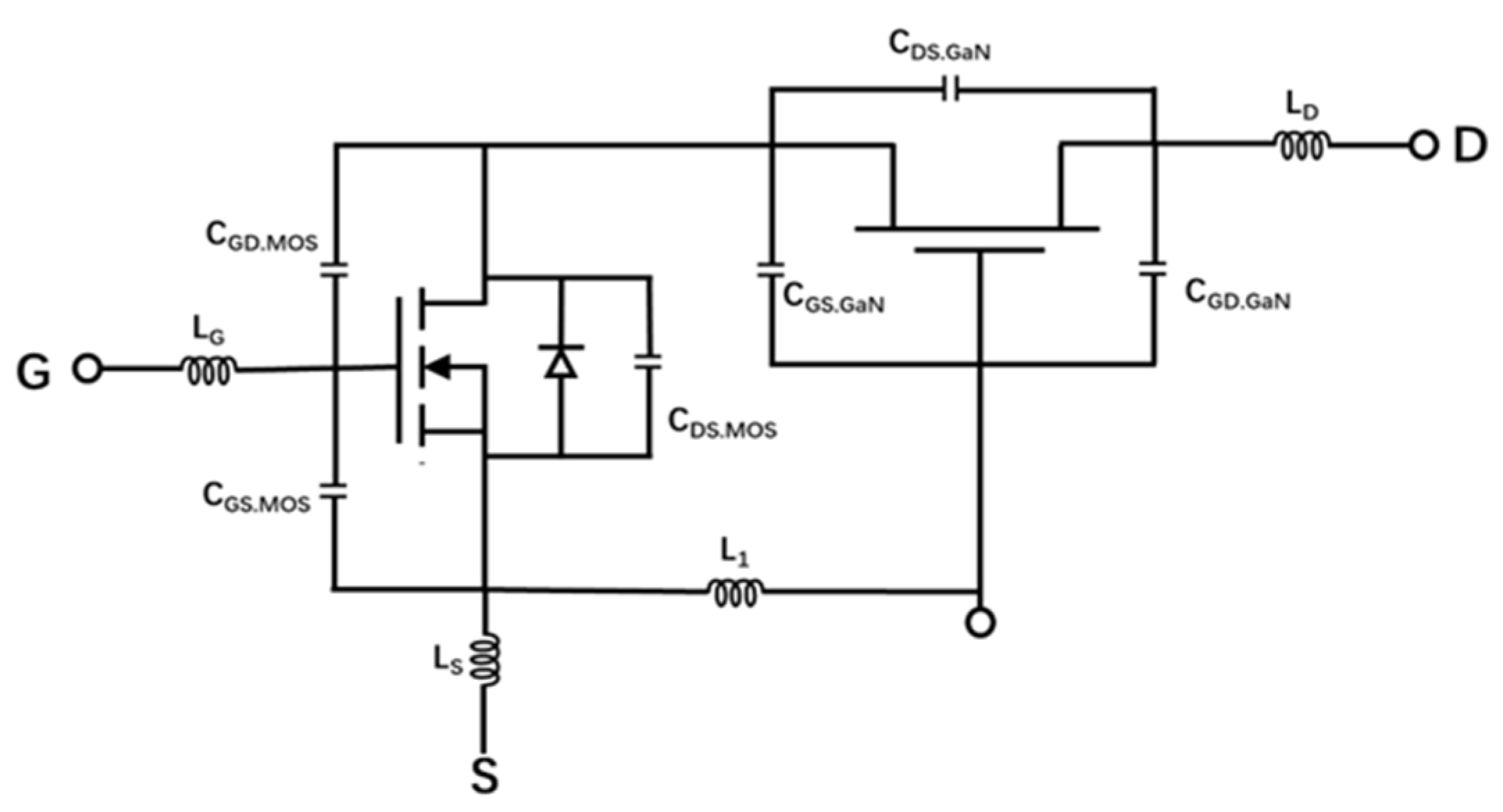

Figure 3 shows the degradation and recovery of threshold voltage over time under different off-state high-field stress. The gate of the Cascode GaN HEMT power device is the gate of the enhanced MOS device, and the cascaded GaN HEMT device is the depletion type; thus, the enhanced MOS devices play a role in controlling the switching of the entire circuit. Hence, the threshold voltage of the Cascode GaN HEMT power device is the threshold voltage of the enhanced MOS device. In the off-state stress test, the MOS device and GaN HEMT device are in the off-state, and the entire circuit can be approximately regarded as two capacitors connected in series together, and the drain voltage is shared by the MOS device and GaN HEMT device. Because the channel resistance of GaN devices is much larger than the channel resistance of MOS devices, GaN HEMT devices receive much of the voltage, and MOS devices receive the minority of the voltage. The gate voltage division of MOS devices is relatively small, so the devices will not break down [

21]. In a series capacitor circuit, with the rise of the total voltage, the voltage division of each capacitor also goes up. Therefore, as the drain voltage of the Cascode GaN power device rises, the voltage division of the MOS device grows.

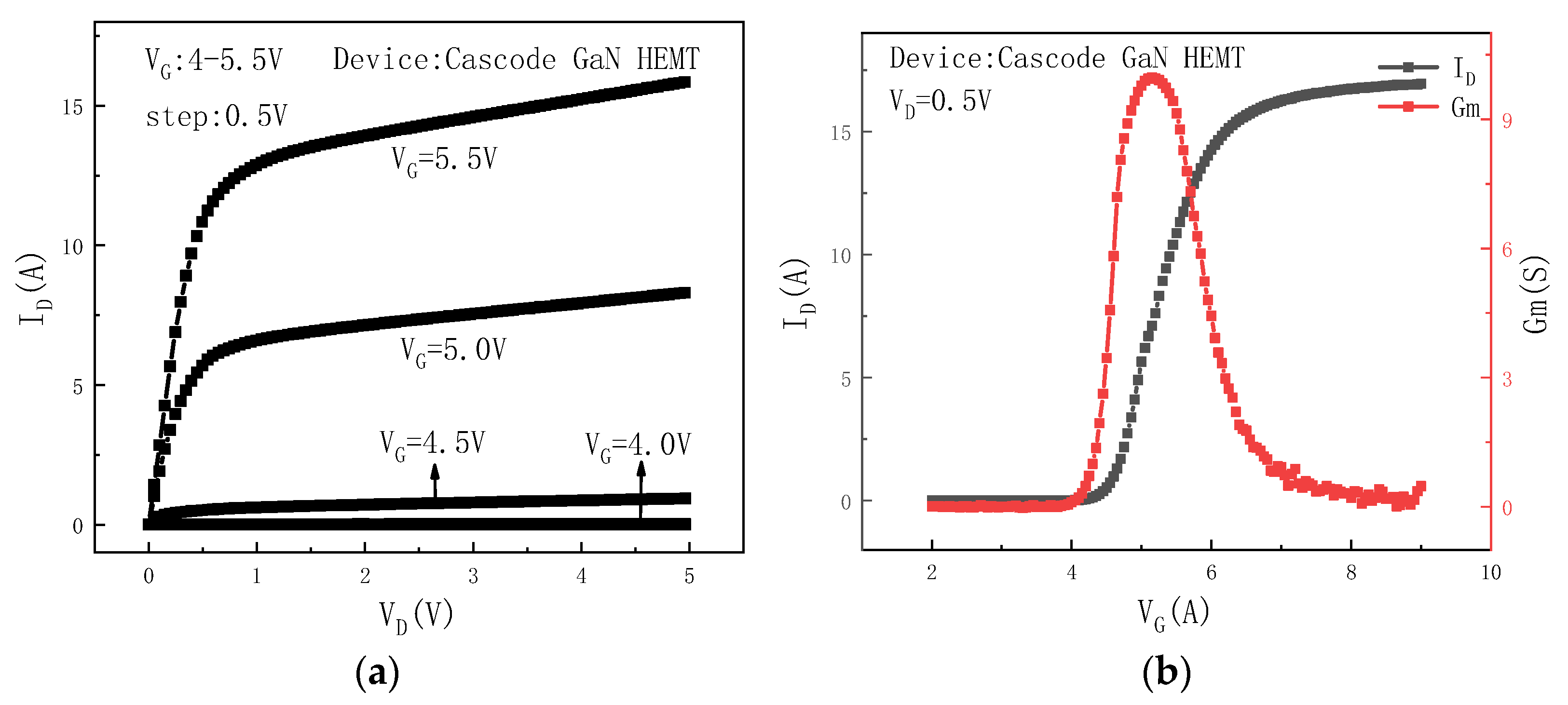

The Cascode GaN HEMT power device controls the opening of the depletion GaN HEMT device through the enhanced MOS device. Therefore, when studying the threshold voltage degradation of Cascode GaN power devices, the research mainly focuses on MOS devices in the cascaded structure. It can be seen from

Figure 4 that the threshold voltage degradation rate is fast in the initial period of stress application, and the threshold voltage degradation rate slows down after a period. The degradation of threshold voltage increases with the increase in drain voltage. At the initial stage of stress removal, the threshold voltage recovery rate is fast. After a period, the threshold voltage recovery reaches saturation and is lower than the initial level, indicating that permanent damage has occurred in the devices.

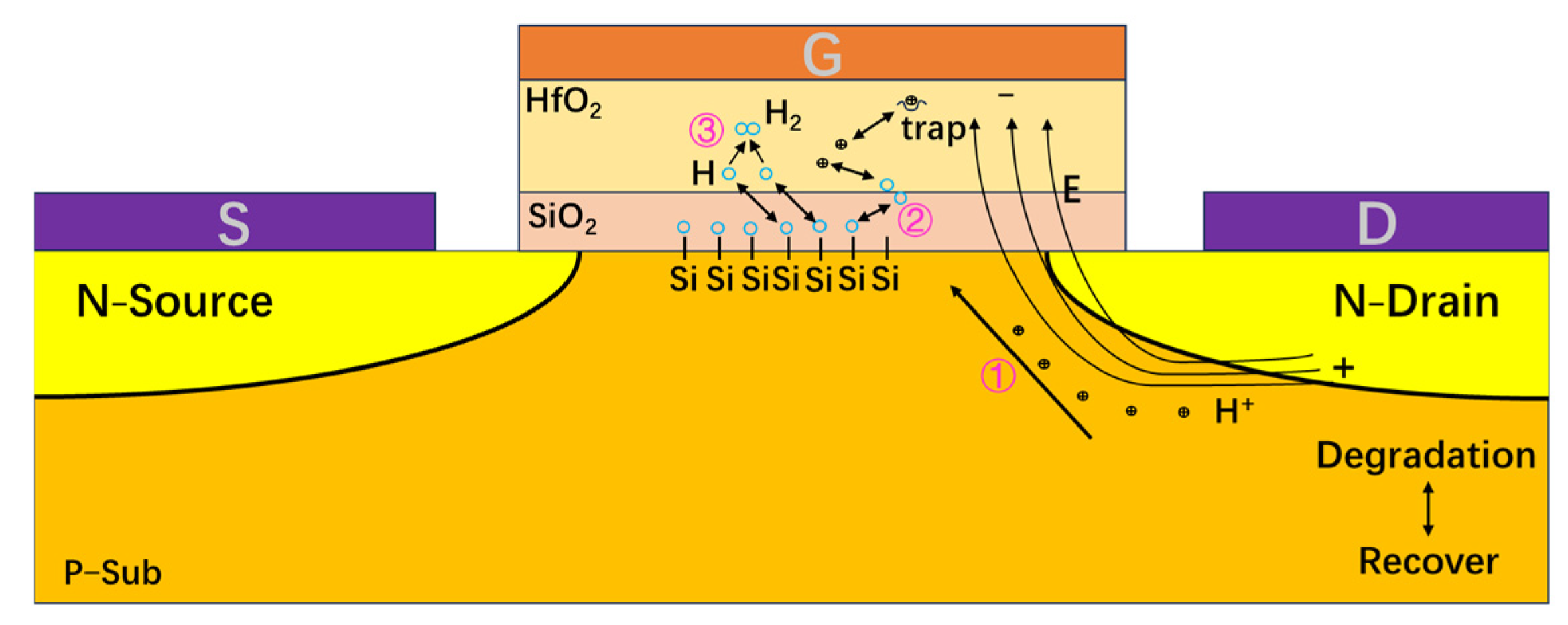

In the off-state high-field-stress experiment, the drain voltage of the MOS device is higher than the gate voltage of the MOS device, and there is a negative bias electric field under the gate of the MOS device. As shown in ① in

Figure 5, the holes in the substrate move towards the gate under the action of the electric field, which has an impact on the Si-H bonds at the interface between the oxide layer and the substrate [

22]. With the increase in time, part of the Si-H bonds is destroyed. Si- and H atoms are produced as shown in ② in

Figure 5. Si- atoms form interface traps, and H atoms will spread to the gate direction. Part of the H atoms will lose electrons to form hydrogen ions, and hydrogen ions will shift to the gate direction under the action of the negative bias electric field. When passing through the oxide layer, part of the hydrogen ions is captured by the oxide layer traps to form positive charge traps, which leads to the degradation of threshold voltage.

The positive charge traps formed in the oxide layer will prevent hydrogen ions from shifting towards the gate. At the initial stage of stress application, the positive charge traps formed in the oxide layer are fewer, and the obstacles to hydrogen ions shifting toward the gate are weak.

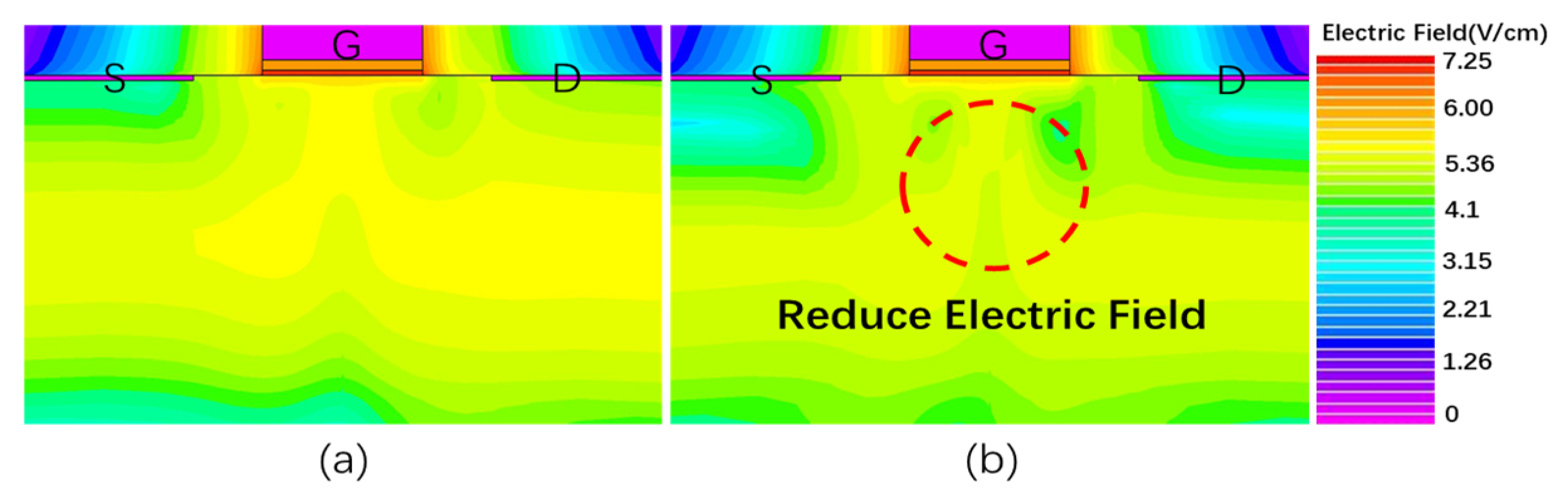

Figure 6a shows the electric field under the gate during the rapid degradation stage of the threshold voltage when stress is first applied. At this time, the electric field generated by the positive charge traps is smaller than that generated by the stress. The hydrogen ions shift toward the gate direction more easily, and the oxide trap is easy to trap hydrogen ions to form positive charge traps, and the degradation rate of the threshold voltage of the device is faster. With the increase in time, more and more positive charge traps are formed in the oxide layer, and the obstacle of hydrogen ions shifting toward the gate becomes stronger and stronger, and hydrogen ions shifting toward the gate becomes difficult.

Figure 6b shows the electric field under the gate during the saturation stage of threshold voltage degradation after stress is applied for a period. At this time, the electric field generated by the positive charge traps is equal to that generated by stress. The oxide traps are not easy to capture hydrogen ions to form positive charge traps, and the degradation rate of the threshold voltage of the device slows down.

After the stress is removed, the recovery is mainly caused by the detrapping of some hydrogen ions. Some H atoms return to the interface between the oxide layer and the substrate to form Si-H bonds with the Si suspension bonds, and the device threshold voltage begins to recover. Because a small number of H atoms will combine with each other to form H

2 during the process of diffusing towards the gate, as shown in ③ in

Figure 5. Therefore, the threshold voltage of the devices still does not reach the initial level when they recover to the saturation state. The high-field stress causes permanent damage at the gate oxide layer and the interface between the oxide layer and the substrate of the devices. When the drain voltage of the Cascode GaN HEMT power device rises, the total voltage of the circuit grows. The voltage division at the gate of the MOS device increases, and the degradation of the device’s threshold voltage becomes more pronounced.

To verify the degradation mechanism of threshold voltage of MOS devices in cascade structure under negative gate stress, the method of adding donor defects in the oxide layer of MOS devices was adopted. The donor defects were used to capture holes to form positive charge traps to simulate the trapping of hydrogen ions by the oxide layer traps under the high field stress in the off-state. Because the threshold voltage of the MOS device determines the threshold voltage of the cascode. Hence, the threshold voltage of a MOS device is a very important parameter. The threshold voltage of the MOS simulation model is 4.41 V, which is in good agreement with the actual devices’ threshold voltage of 4.43 V. In the simulation, the oxide layer width-to-length ratio of the MOS device is 1000 nm/100 nm. Relevant physical models are added in the simulation to more realistically mimic practical scenarios. Under the action of a high electric field, carriers collide with lattice atoms to cause impact ionization, generating high-density charges. Therefore, an impact self-model and a Fermi–Dirac carrier number statistics model, which more accurately calculates high-concentration carriers, are added. Since doping concentration affects mobility, a concentration-dependent mobility model is included. The high electric field saturation influences the charge drift velocity, so a parallel electric field-dependent model is added. Due to the high source-drain doping concentration in the MOSFET device, the bandgap narrowing model is needed to describe the bandgap narrowing effect under high doping concentration.

Figure 7 shows the comparison of the internal simulation electric field distribution between a conventional MOS device and a MOS device with donor defects. As can be seen from

Figure 7, adding donor defects to the oxide layer of the MOS device will reduce the electric field of the substrate below the gate of the MOS device. This is because the trapping of holes by donor defects in the oxide layer decreases the concentration of holes at the interface between the oxide layer and the substrate. This results in a decrease in the internal electric field of the substrate below the gate, which corresponds to ① in

Figure 5. The reduction in the electric field of the substrate below the gate will reduce the source-substrate voltage

VSB. Formula (1) is the calculation formula of the threshold voltage of the MOS device. From Equation (1), a decrease in

VSB reduces

in Equation (1), resulting in a decrease in

Vth and a negative shift in the device threshold voltage. It is consistent with the MOS device threshold voltage degradation mechanism presented in

Figure 5.

where

VFB is the flat band voltage;

ΦF is the Fermi potential;

q is the electron charge;

εS is the dielectric constant;

NA is the substrate doping concentration;

VSB is the source-substrate voltage; and

COX is the oxide layer capacitance.

When constant off-state high field stress is applied to the drain electrode, the device transconductance degrades.

Figure 8 shows the transconductance curve of the device varies with time. It can be seen from

Figure 8 that the transconductance degradation rate is fast in the initial period of stress application and slows down after a period. Moreover, the degree of transconductance degradation increases with the increase in drain voltage. At the beginning of stress removal, the transconductance recovery rate is fast. After a period, the transconductance recovery reaches saturation, but it is lower than the initial level, which also proves that permanent damage occurs inside the device.

The transconductance of the Cascode GaN HEMT power device is obtained by comparing the drain current of the GaN HEMT device to the gate voltage of the MOS device. The threshold voltage of MOS devices shifts negatively. When the gate voltage is the same, the device’s turn-on degree is higher and the output current is larger. However, the threshold voltage shift of MOS devices is relatively small. The change in drain current caused by the threshold voltage shift is also relatively small. Therefore, when studying the transconductance degradation of Cascode GaN HEMT power devices, the research mainly focuses on GaN HEMT devices in the cascaded structure.

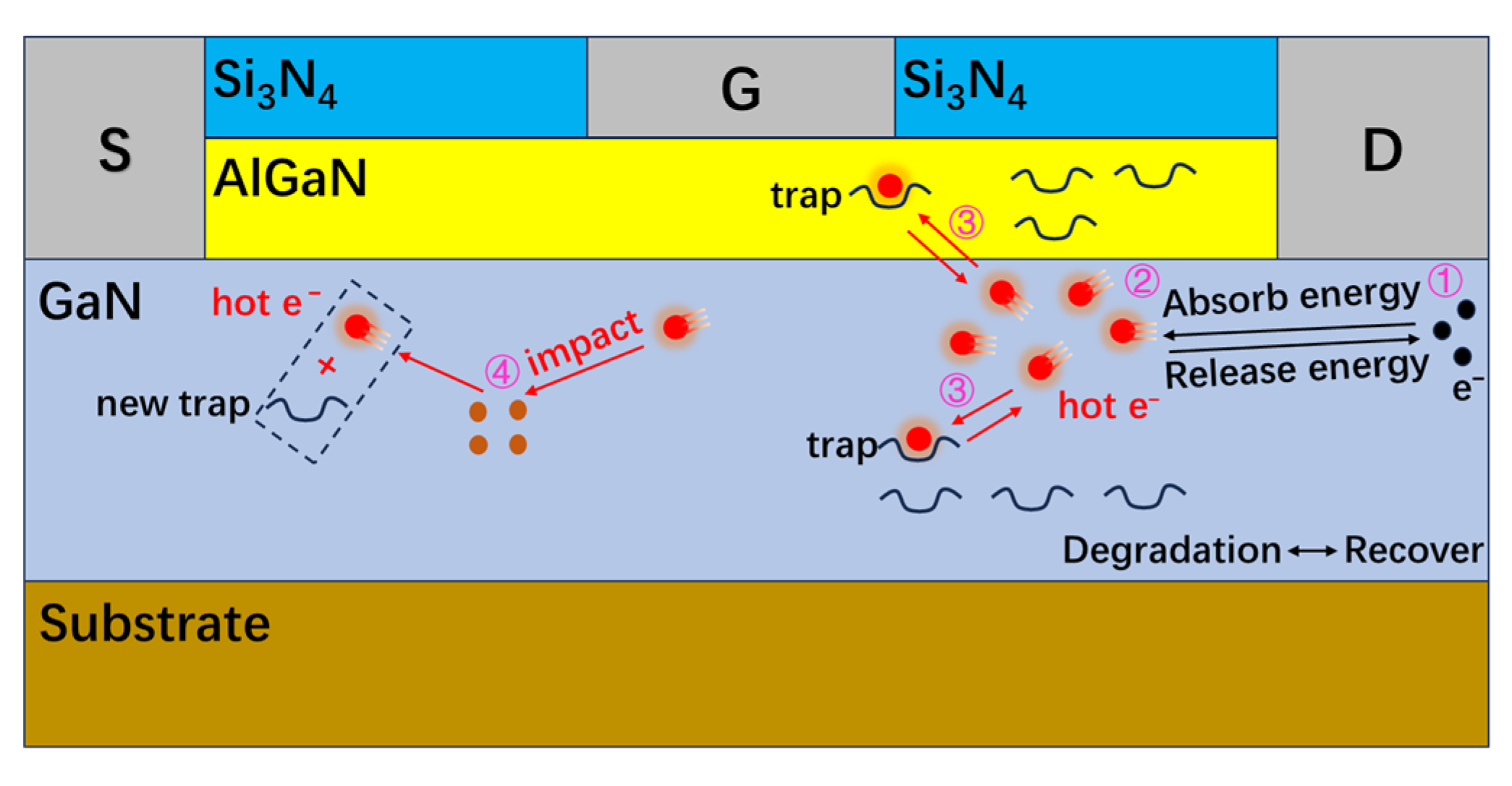

Figure 9 shows the transconductance degradation mechanism of GaN HEMT devices under off-state high-field stress.

In the off-state stress test, the MOS device and GaN HEMT device are both in the off-state. The entire circuit can be approximately two capacitors in the series together, and the drain voltage is shared by the MOS device and GaN HEMT device. Because the channel resistance of the GaN HEMT device is much larger than the channel resistance of the MOS device, the high field stress is mainly shared by the GaN HEMT device. As shown in

Figure 9 ①, a long time of high field stress will lead to a small number of leaking electrons under the drain electrode [

23]. When these electrons are near the drain, some electrons obtain enough energy to become hot electrons, as shown in

Figure 9 ②. Among them, the hot electrons with higher energy escape after being subjected to lattice elastic collisions, as shown in

Figure 9 ③. At the same time, high field stress will activate traps in the barrier layer and buffer layer of the GaN HEMT device. These traps capture the leaked electrons, causing the output current to decrease and the transconductance of the Cascode GaN HEMT power device to be reduced.

The degradation of the threshold voltage reduces the gate voltage required for MOS devices to turn on, but the change in the threshold voltage is relatively small. The change in the threshold voltage leads to a small change in the current output of the device and has a small impact on transconductance. Therefore, the decrease in transconductance is mainly caused by internal defects in GaN HEMT devices.

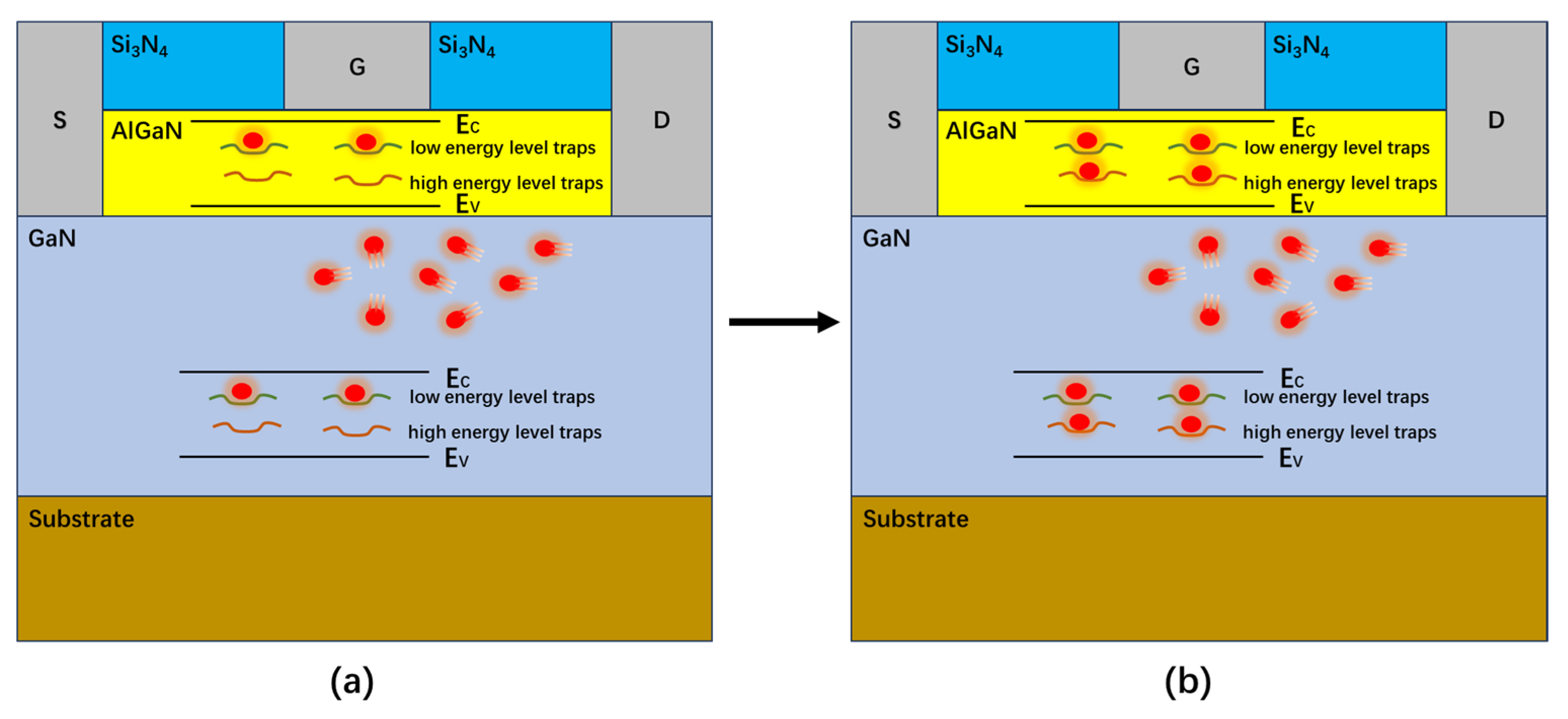

At the initial stage of stress application, the more easily activated low-energy-level traps in the device are activated.

Figure 10a shows the electrons are obtained by internal defects of the device during the rapid degradation stage of transconductance. Many electrons are captured by low-energy-level traps, and the transconductance degradation rate is fast. With the increase in time, the low-energy-level traps are all activated and have captured electrons, and the high-energy-level traps begin to be activated.

Figure 10b shows that the electrons are obtained by internal defects of the device during the saturation stage of transconductance degradation. The electrons begin to be captured by the high-energy-level traps, and the transconductance degradation rate slows down.

After the stress is removed, the low-energy-level traps, which are easier to deactivate, start to deactivate. The low-energy-level traps deactivate faster, and the transconductance recovery rate is faster. After a period, all low-energy-level traps are inactivated, while high-energy-level traps begin to be inactivated. The high-energy-level traps are slowly inactivated, and the transconductance recovery rate slows down. Because hot electrons will generate permanent new traps inside the device after escaping from the lattice collision, as shown by ④ in

Figure 9. The transconductance of the device still does not reach the initial level when recovering saturation. The high field stress causes permanent damage inside the device.

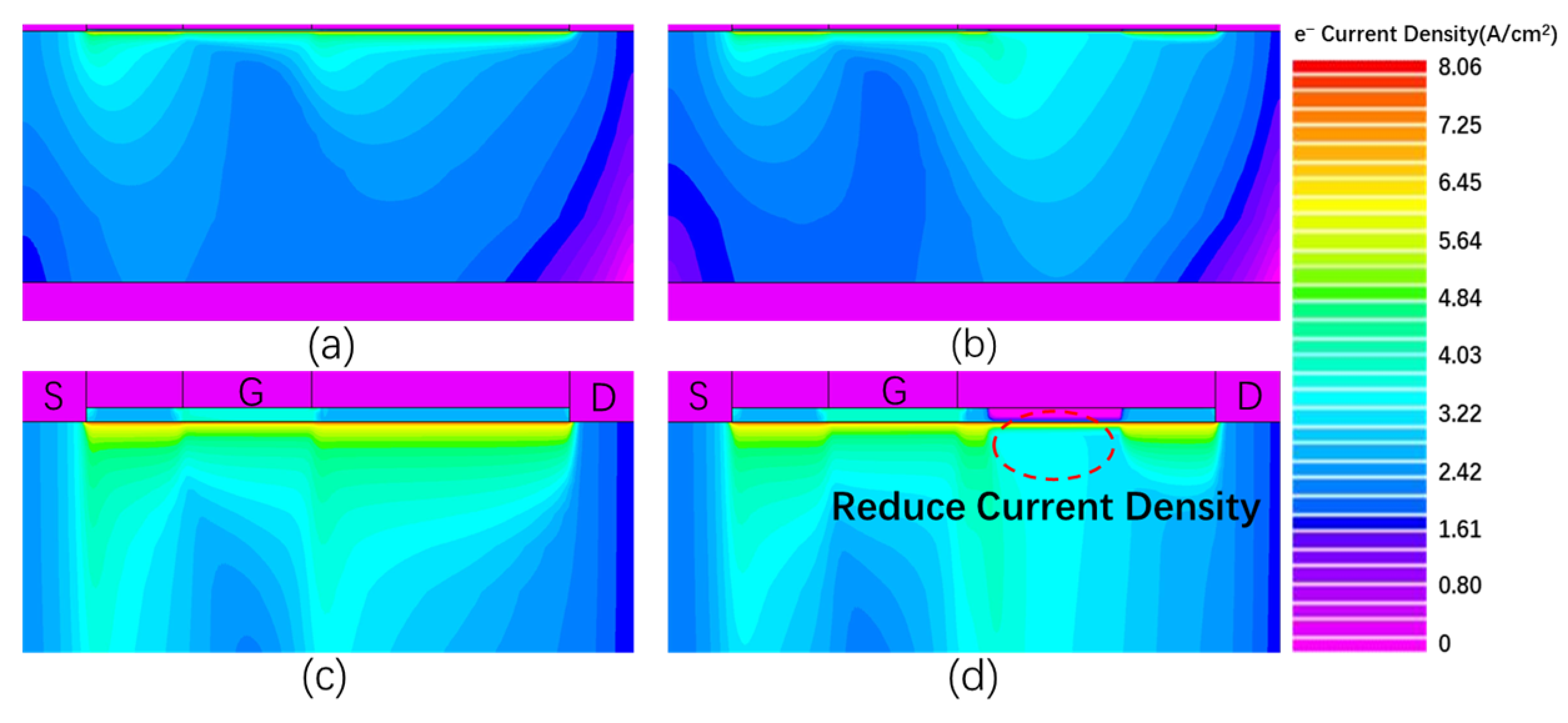

To verify the transconductance degradation mechanism of the GaN device in the cascade structure under the off-state and high field, the acceptor defects were added to the barrier layer and buffer layer to simulate the barrier layer traps and buffer layer traps trapping electrons. Because the drain current of the GaN device determines the drain current of the cascode. Hence, the drain current of a GaN device is a very important parameter. When the drain voltage and gate voltage are 5 V, the drain current of the GaN simulation model is 5.33 A, which is in good agreement with actual devices (5.35 A) under the same conditions. In the simulation, the gate length of the GaN device is 2 μm, the AlGaN barrier layer thickness is 15 nm, and the buffer layer thickness is 1.95 μm. To simulate practical conditions more realistically, appropriate physical models need to be selected in the simulation. The polarization model can simulate the polarization effect on GaN devices, using psp.scale, polar.scale, and piezo.scale to represent polarization charges caused by spontaneous polarization, total polarization, and piezoelectric polarization. Under the action of a high electric field, carriers collide with lattice atoms to generate more electron–hole pairs, and the impact self-model can well simulate this process. The Shockley–Read–Hall recombination model can effectively simulate the recombination process of partial electron–hole pairs with defects inside the device. Moreover, the Fermi–Dirac carrier number statistics model is suitable for scenarios requiring number statistics of many particles. Since carriers will generate many electron–hole pairs via impact ionization under high electric fields, introducing this model can more accurately count the number of carriers after ionization.

Figure 11 shows the comparison of electron concentration in the conventional GaN HEMT device and the device with defects. It can be seen from

Figure 11 that the addition of acceptor defects in barrier and buffer layers of the GaN HEMT device will reduce the concentration of channel electrons. Because electrons in the channels are obtained by the traps in the barrier layer and the buffer layer, which corresponds to ③ in

Figure 9. A decrease in channel electron concentration will reduce the output current and transconductance of the device. This is consistent with the transconductance degradation mechanism of the GaN HEMT device in

Figure 9.

3.2. Influence of Different Drain Voltages on Noise of Device

The noise test of Cascode GaN HEMT power devices before and after stress was carried out by the FS-Pro series semiconductor parameter test system, and the defects introduced by high field stress in the devices were indicated. In Cascode GaN HEMT power devices, the gate oxide layer traps of the MOS device and the traps in the barrier layer and the buffer layer of the GaN HEMT device will obtain electrons, causing changes in the number of electrons in the channel, which will cause the number of electrons in the channel to fluctuate. When a small voltage is applied to the drain, the change in the number of electrons will be shown by the change in drain current. In the noise test, constant small drain voltage is applied to the drain electrode, and the gate voltage gradually increases from around the threshold voltage. Because the gate voltage is near the threshold voltage and the device is in a half-open state, a small current will be generated inside the device, and the internal current of the device will change with the change in the gate voltage [

24]. The drain current, which included the noise current, can be processed to achieve a relationship between power spectral density (PSD) and frequency.

Figure 12 shows the normalized low-frequency noise curve of the device. It can be found from

Figure 12 that as the gate voltage increases, the noise gradually decreases. The value of the frequency index factor γ obtained through data fitting is 0.98, which is very close to 1, belonging to the characteristics of

1/f noise. Moreover, 1/f noise is caused by the change in the electron number within the channel. Defects in both the MOS and GaN devices trap electrons and can change the electrons’ number. The defects in the MOS device have an influence on the threshold voltage. The threshold voltage change will have an influence on the drain current. Moreover, the defects in the GaN device will trap the electrons in the channel, which also has an influence on the drain current.

According to the classical tunneling theory, the relationship between drain current Sid and flat-band voltage noise power spectral density

Svfb is as follows:

where

gm and

Ids are, respectively, device transconductance and drain current, which are obtained by the test system. The relationship between defect density

Nt and flat band voltage noise power spectral density

Svfb is as follows:

where

W,

L correspond to the width, length, and barrier layer capacitance of the device, respectively.

f is the test frequency.

q is the charge of the electron.

k is the Boltzmann constant.

T is the Kelvin temperature.

λ = 0.5 nm is the tunneling factor.

Svfb is flat band voltage noise power spectral density.

Nt is the defect density of the device.

It can be seen from Formula (3) that for the same device, the flat band voltage noise power spectral density Svfb is proportional to the defect density Nt of the device when the environment temperature and test frequency are unchanged.

To study the influence of off-state high field stress on the internal defect density of the device, the normalized drain current and transconductance of the same frequency in the low-frequency noise test of the Cascode GaN HEMT power device were extracted. The flat band voltage noise power spectral density

Svfb of the device with different drain currents was calculated, and its average value was taken to characterize the internal defect density of the device.

Figure 13 shows the flat band voltage noise power spectral density

Svfb and its average value of the device before and after stress application at a frequency of 10 Hz. It can be seen from

Figure 13 that applying high field stress to the drain will increase the flat band voltage noise power spectral density

Svfb of the device, and the defect density inside the device will increase. Moreover, the higher the drain voltage is, the higher the defect density inside the device will be. The analysis results of low-frequency noise are consistent with the mechanism analysis mentioned above.