A Method for Fabricating Cavity-SOI and Its Verification Using Resonant Pressure Sensors

Abstract

1. Introduction

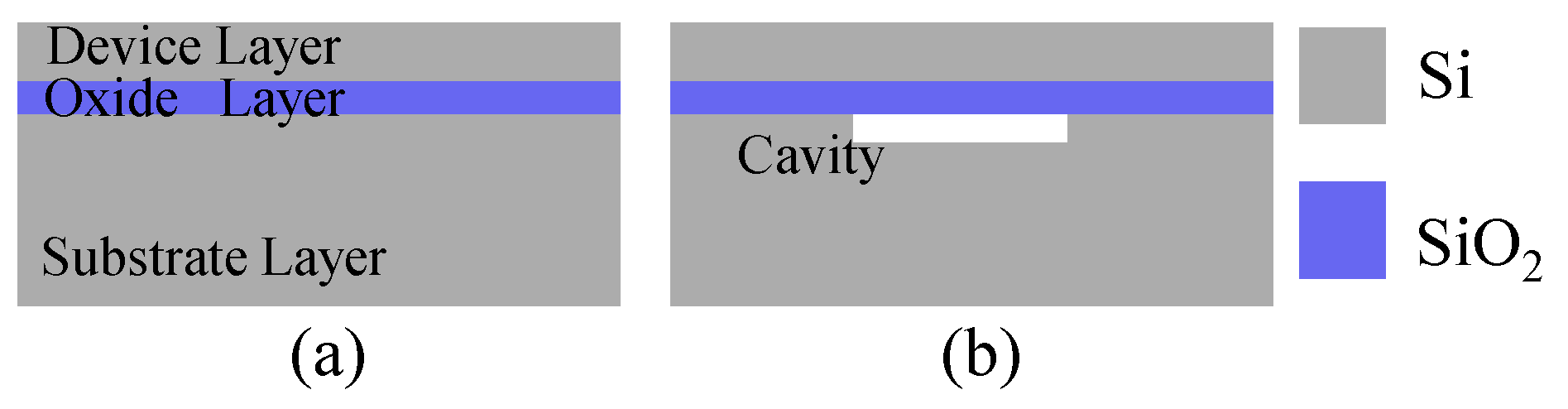

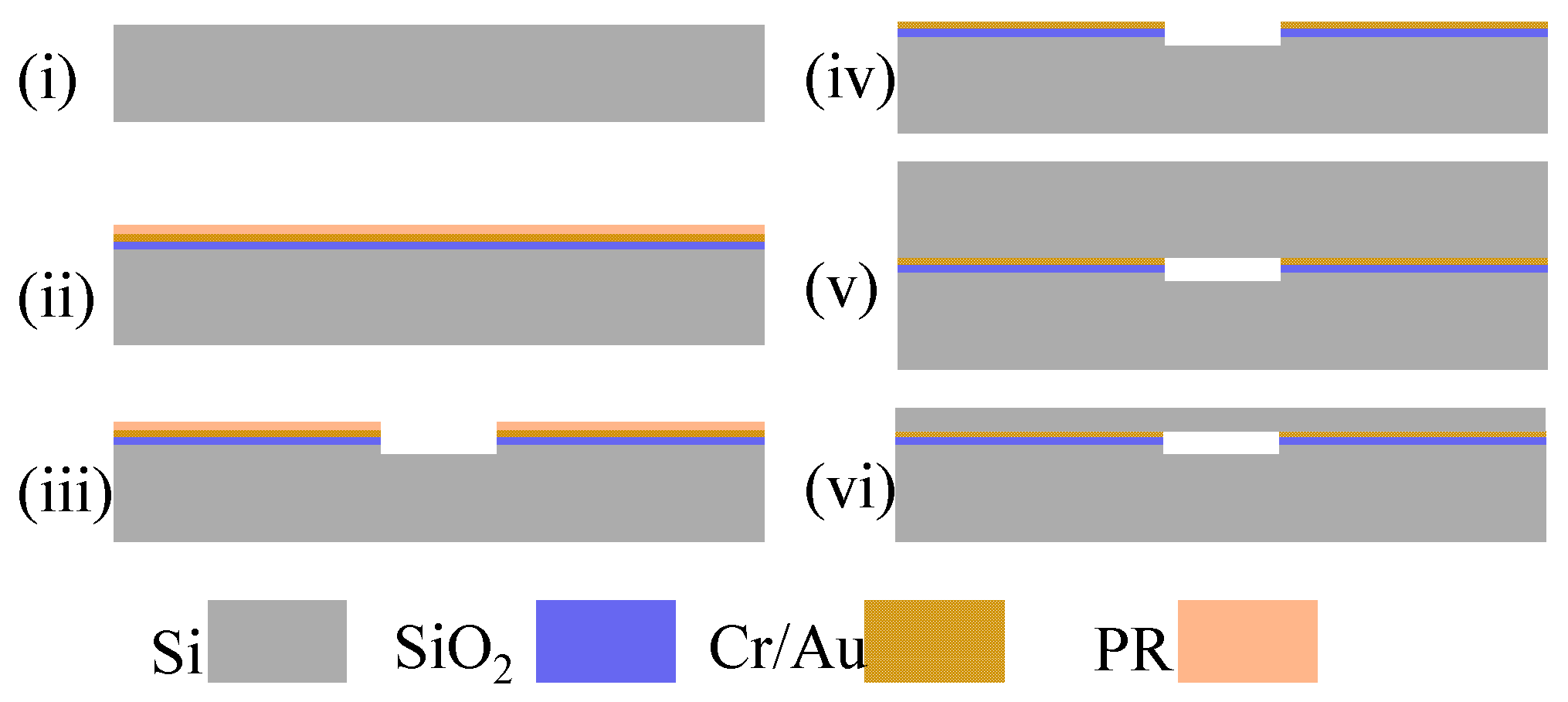

2. Fabrication of the Cavity-SOI

3. Verification of the Cavity-SOI

3.1. Sensor Design

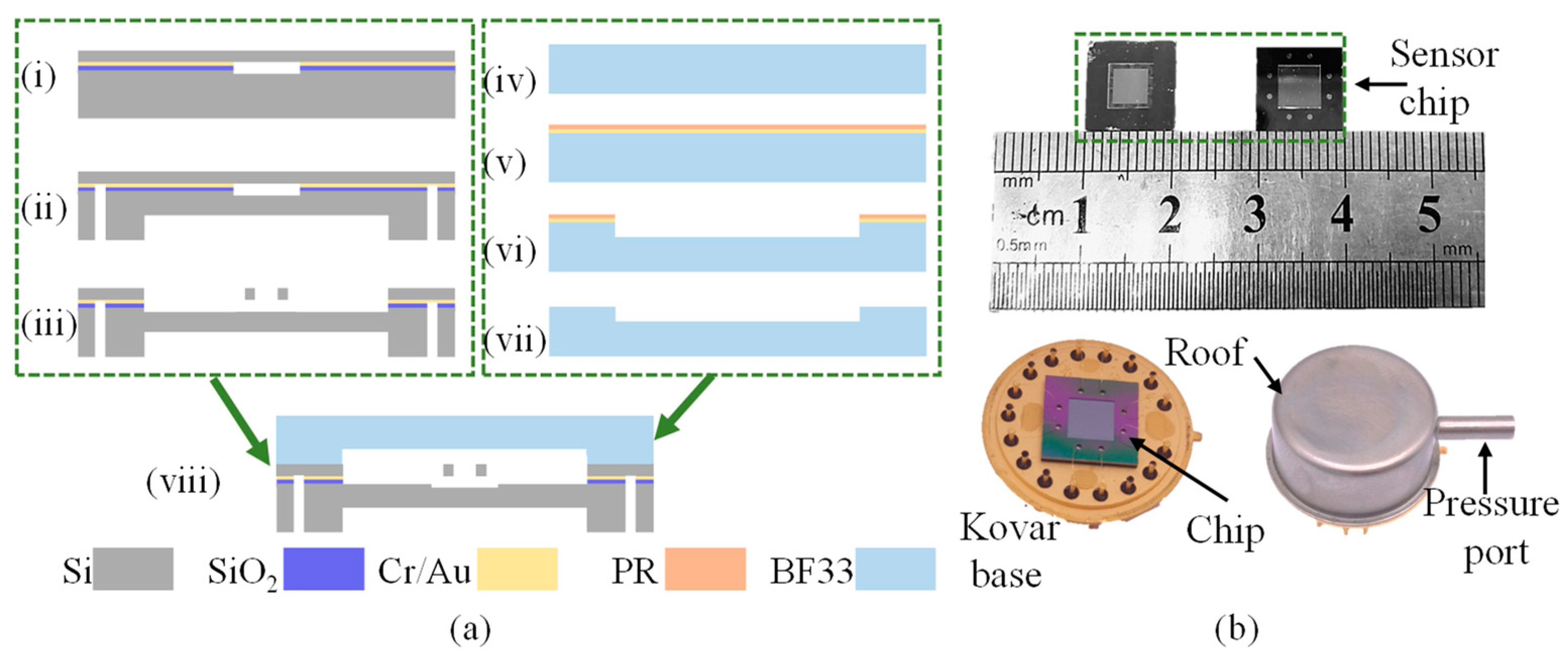

3.2. Sensor Fabrication

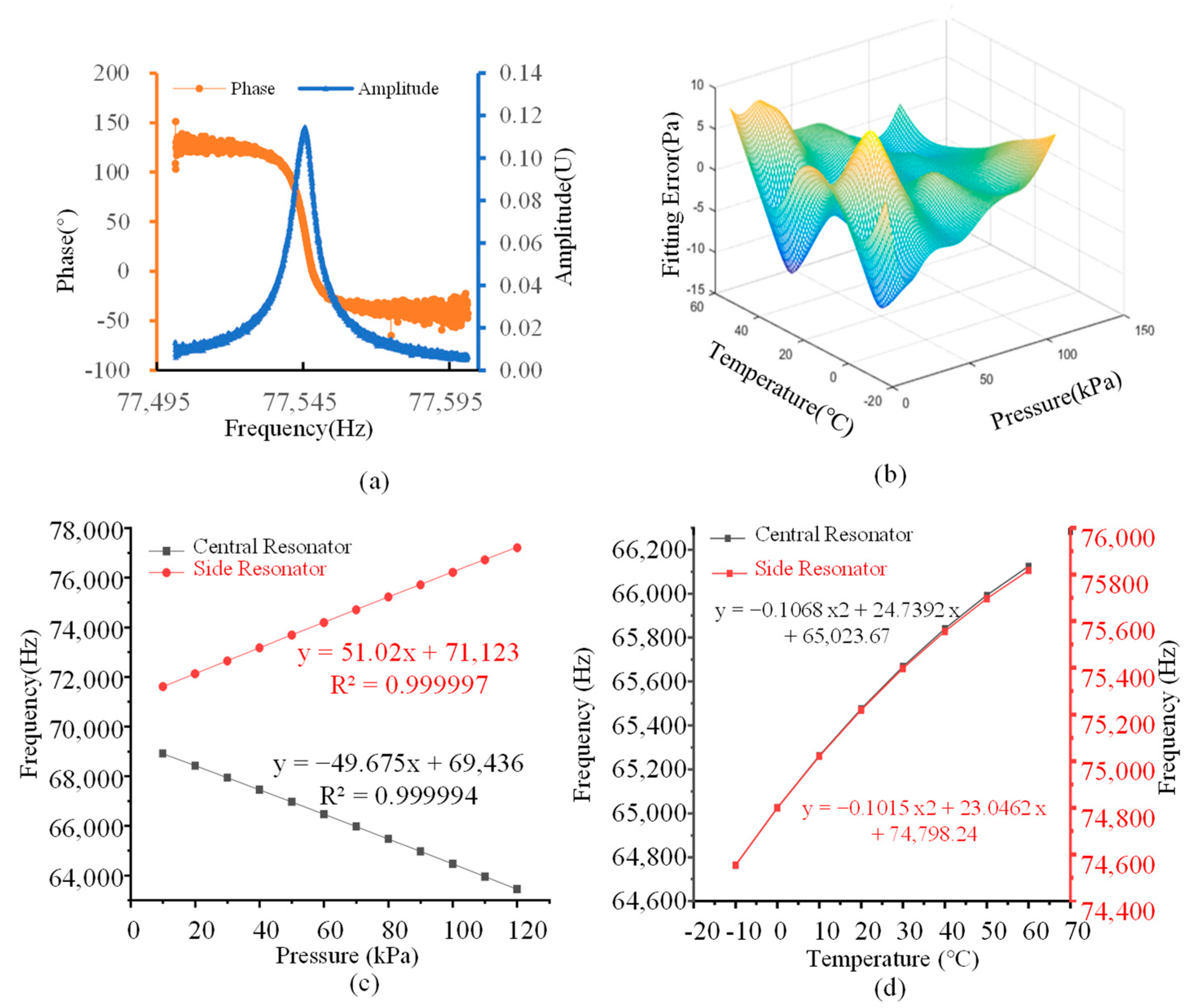

3.3. Sensor Performance

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Xie, B.; Xing, Y.H.; Wang, Y.S.; Chen, J.; Chen, D.Y.; Wang, J.B. A Lateral Differential Resonant Pressure Microsensor Based on SOI-Glass Wafer-Level Vacuum Packaging. Sensors 2015, 15, 24257–24268. [Google Scholar] [CrossRef] [PubMed]

- Li, Y.; Cheng, C.; Lu, Y.; Xie, B.; Chen, J.; Wang, J.; Chen, D. A High-Sensitivity Resonant Differential Pressure Microsensor Based on Bulk Micromachining. IEEE Sens. J. 2021, 21, 8927–8934. [Google Scholar] [CrossRef]

- Benjamin, E.; Maimon, R.; Ronen, A.; Yichie, E.; Krylov, S. Electrostatically Actuated SOI In-Plane Motion Platform for In-situ Calibration of Micro Gyroscopes. In Proceedings of the IEEE Sensors Conference, Vienna, Austria, 29 October–1 November 2023. [Google Scholar]

- Lin, D.; Macdonald, R.; Popp, J.; Alberda, M.; Andarawis, E.; Aimi, M. Low-Cost Navigation-grade MEMS Fabrication Platform to Enable PNT Innovations. In Proceedings of the IEEE/ION Position, Location and Navigation Symposium (PLANS), Monterey, CA, USA, 24–27 April 2023; pp. 1–5. [Google Scholar]

- Liang, T.X.; Peng, Z.; Li, C.Y.; Xia, C.; Xia, Y.L.; Wang, Z.Q. Multifunctional thermal biosensor based on silicon thermocouple junction and suspended microfluidic channel. In Proceedings of the 37th IEEE International Conference on Micro Electro Mechanical Systems (MEMS), Austin, TX, USA, 21–25 January 2024; pp. 1126–1129. [Google Scholar]

- Li, J.; Naaborg, J.; Louwerse, M.; Henneken, V.; Eugeni, C.; Dekker, R. Embedded High-Density Trench Capacitors for Smart Catheters. In Proceedings of the 8th IEEE Electronics System-Integration Technology Conference (ESTC), Vestfold, Norway, 15–18 September 2020. [Google Scholar]

- Kluba, M.M.; Li, J.; Parkkinen, K.; Louwerse, M.; Snijder, J.; Dekker, R. Cavity-BOX SOI: Advanced Silicon Substrate with Pre-Patterned BOX for Monolithic MEMS Fabrication. Micromachines 2021, 12, 414. [Google Scholar] [CrossRef] [PubMed]

- Wu, G.Q.; Xu, D.H.; Xiong, B.; Wang, Y.L. A high-performance bulk mode single crystal silicon microresonator based on a cavity-SOI wafer. J. Micromech. Microeng. 2012, 22, 8. [Google Scholar] [CrossRef]

- Zhang, Y.; Yang, C.; Meng, F.; Liu, G.; Gao, C.; Hao, Y. A Monolithic Integration Multifunctional MEMS Sensor Based on Cavity SOI Wafer. In Proceedings of the 13th IEEE Sensors Conference, Valencia, Spain, 2–5 November 2014; pp. 1952–1955. [Google Scholar]

- Liu, F.; Yang, J.; Liang, D.; Wu, H.; Ma, X.; Wang, X. Wafer bonding process research in manufacturing of Cavity-SOI for MEMS device application. Transducer Microsyst. Technol. 2022, 41, 58–61. [Google Scholar]

- Xu, J.H.; Zhang, X.L.; Fernando, S.N.; Chai, K.T.; Gu, Y.D. AlN-on-SOI platform-based micro-machined hydrophone. Appl. Phys. Lett. 2016, 109, 5. [Google Scholar] [CrossRef]

- Jang, W.I.; Choi, C.A.; Lee, M.L.; Jun, C.H.; Kim, Y.T. Fabrication of MEMS devices by using anhydrous HF gas-phase etching with alcoholic vapor. J. Micromech. Microeng. 2002, 12, 297–306. [Google Scholar] [CrossRef]

- Kanno, K.; Noro, M.; Mitsuhashi, T.; Yoshita, S.; Mishima, T.; Yoshida, T. A silicon resonant thermometer for high pressure and high temperature environment. In Proceedings of the 31st IEEE International Conference on Micro Electro Mechanical Systems (MEMS), Belfast, North Ireland, 21–25 January 2018; pp. 1100–1103. [Google Scholar]

- Liu, C.; Froemel, J.; Chen, J.L.; Tsukamoto, T.; Tanaka, S. Laterally vibrating MEMS resonant vacuum sensor based on cavity-SOI process for evaluation of wide range of sealed cavity pressure. Microsyst. Technol. 2019, 25, 487–497. [Google Scholar] [CrossRef]

- Heimala, P.; Harjanne, M.; Paul, S.; Kapulainen, M.; Sun, F.; Larismaa, J.; Aalto, T. Power-Efficient Thermo-Optic Phase Shifters with Cavity-SOI; SPIE: Bellingham, WA, USA, 2024; Volume 12891. [Google Scholar]

- Lee, M.M.O.; Moon, Y.H. A high density IC compatible microtransducer/diaphragm design on micro-cavity SOI technology. In Proceedings of the 1997 IEEE Hong Kong Electron Devices Meeting, Hong Kong, 30 August 1997; pp. 140–144. [Google Scholar]

- Luoto, H.; Henttinen, K.; Suni, T.; Dekker, J.; Mäkinen, J.; Torkkeli, A. MEMS on cavity-SOI wafers. Solid-State Electron. 2007, 51, 328–332. [Google Scholar] [CrossRef]

- Wang, M.; Li, W. Separation Method for Micro-Mechanical System (MEMS) Silicon Strain Sheet of High Voltage Sensor Field, Involves Taking Silicon Substrate Wafer with Cavity as Carrier for Storing and Transporting Strain Sheet. CN115028139-A. 16 May 2023. [Google Scholar]

- Yanagihara, A.; Yamaguchi, K.; Suzuki, K.; Moriwaki, O. Silica-Based Planar Lightwave Circuit Switch on a Cavity Structure for Reducing Power Consumption. In Proceedings of the IEEE-Photonics-Society Summer Topicals Meeting (SUM), Bridgetown, Barbados, 15–17 July 2024. [Google Scholar]

- Luo, Z.Y.; Li, Y.N.; Xie, B.; Chen, D.Y.; Wang, J.B. A self-temperature compensating barometer with dual doubly-clamped resonators. In Proceedings of the 18th International Conference on Solid-State Sensors, Actuators and Microsystems (TRANSDUCERS), Anchorage, AK, USA, 21–25 June 2015; pp. 153–156. [Google Scholar]

- Li, H.L.; Yang, Q.R.; Luo, H.X.; Gong, Y.; Yuan, Y.; Niu, P.F.; Liu, B.H.; Sun, C.L.; Zhang, M.L.; Pang, W. Aluminum Nitride MEMS Resonant Pressure Gauges Without Vacuum Packaging. IEEE Electron Device Lett. 2024, 45, 893–896. [Google Scholar] [CrossRef]

- Lu, Y.L.; Xie, B.; Li, C.H.; Chen, D.Y.; Wang, J.B.; Shang, Y.L. An Oil-Filled MEMS Resonant Pressure Sensor Based on Electrostatic Stiffness Modulation. IEEE Electron Device Lett. 2023, 44, 2027–2030. [Google Scholar] [CrossRef]

- Yu, H.S.; Wang, J.B.; Lu, Y.L.; Xie, B.; Shang, Y.L.; Liu, Z. A silicon resonant pressure sensor based on thermal stresses matched structures. In Proceedings of the 25th Annual Conference and 14th International Conference of the Chinese-Society-of-Micro-Nano-Technology (CSMNT), Chinese Soc Micro Nano Technol, Shenzhen, China, 20–23 October 2023. [Google Scholar]

- Yao, J.H.; Cheng, C.; Xue, H.; Li, X.Y.; Lu, Y.L.; Xie, B.; Wang, J.B.; Chen, D.Y.; Chen, J. A High-Sensitivity Resonant Differential Pressure Microsensor Based on Wafer-Level Eutectic Bonding. IEEE Trans. Electron Devices 2023, 70, 2481–2488. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xue, H.; Li, X.; Lu, Y.; Xie, B.; Chen, D.; Wang, J.; Chen, J. A Method for Fabricating Cavity-SOI and Its Verification Using Resonant Pressure Sensors. Micromachines 2025, 16, 297. https://doi.org/10.3390/mi16030297

Xue H, Li X, Lu Y, Xie B, Chen D, Wang J, Chen J. A Method for Fabricating Cavity-SOI and Its Verification Using Resonant Pressure Sensors. Micromachines. 2025; 16(3):297. https://doi.org/10.3390/mi16030297

Chicago/Turabian StyleXue, Han, Xingyu Li, Yulan Lu, Bo Xie, Deyong Chen, Junbo Wang, and Jian Chen. 2025. "A Method for Fabricating Cavity-SOI and Its Verification Using Resonant Pressure Sensors" Micromachines 16, no. 3: 297. https://doi.org/10.3390/mi16030297

APA StyleXue, H., Li, X., Lu, Y., Xie, B., Chen, D., Wang, J., & Chen, J. (2025). A Method for Fabricating Cavity-SOI and Its Verification Using Resonant Pressure Sensors. Micromachines, 16(3), 297. https://doi.org/10.3390/mi16030297