Investigation on the Isolation Approaches for High-Voltage GaN-on-Sapphire Monolithic Power Integrated Circuits

Abstract

1. Introduction

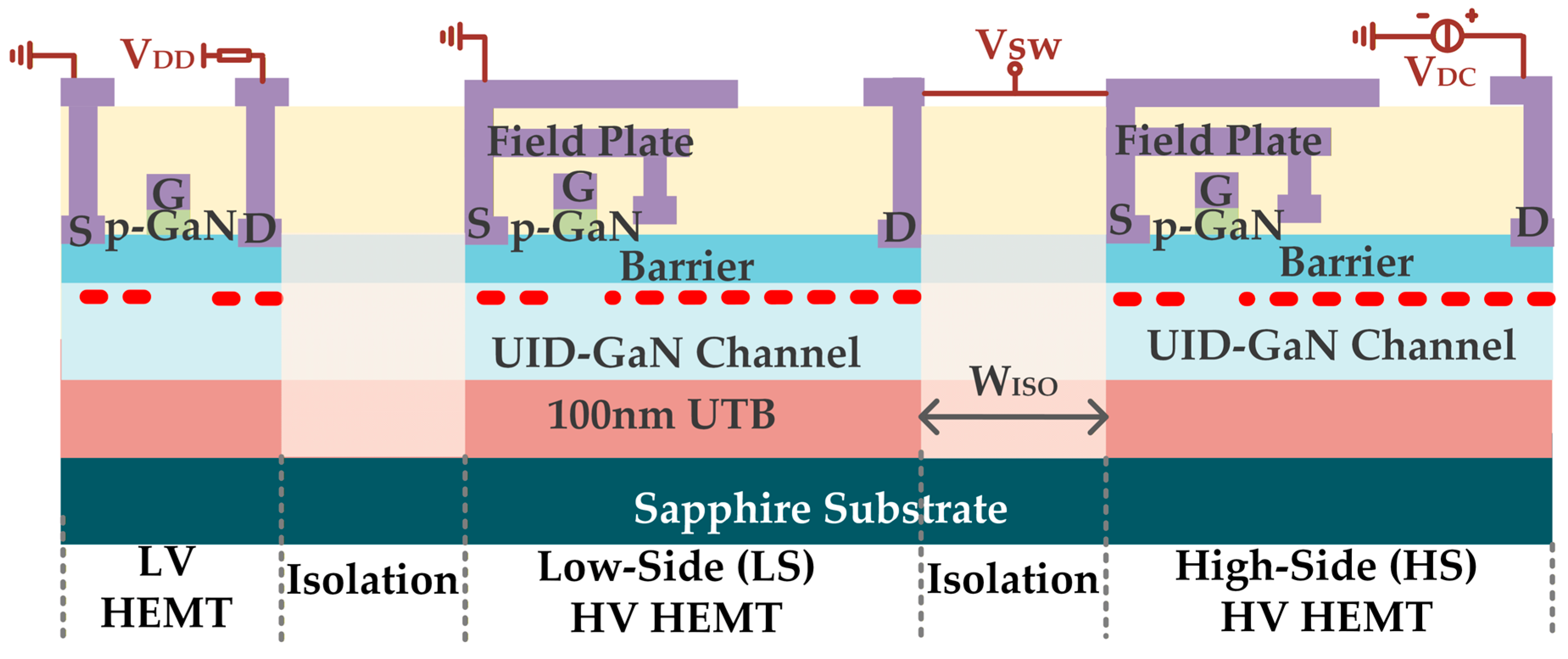

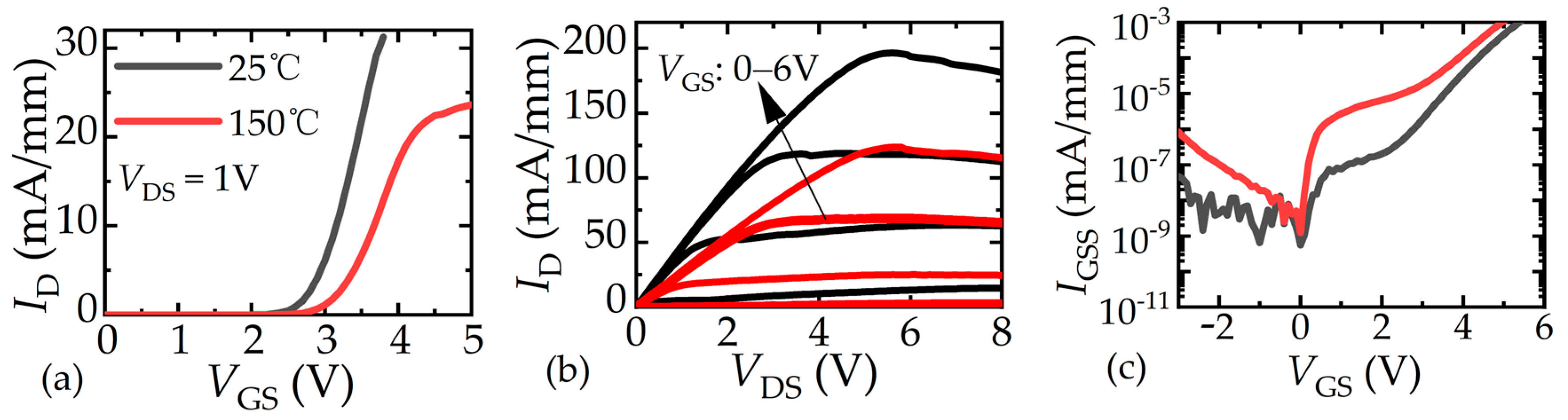

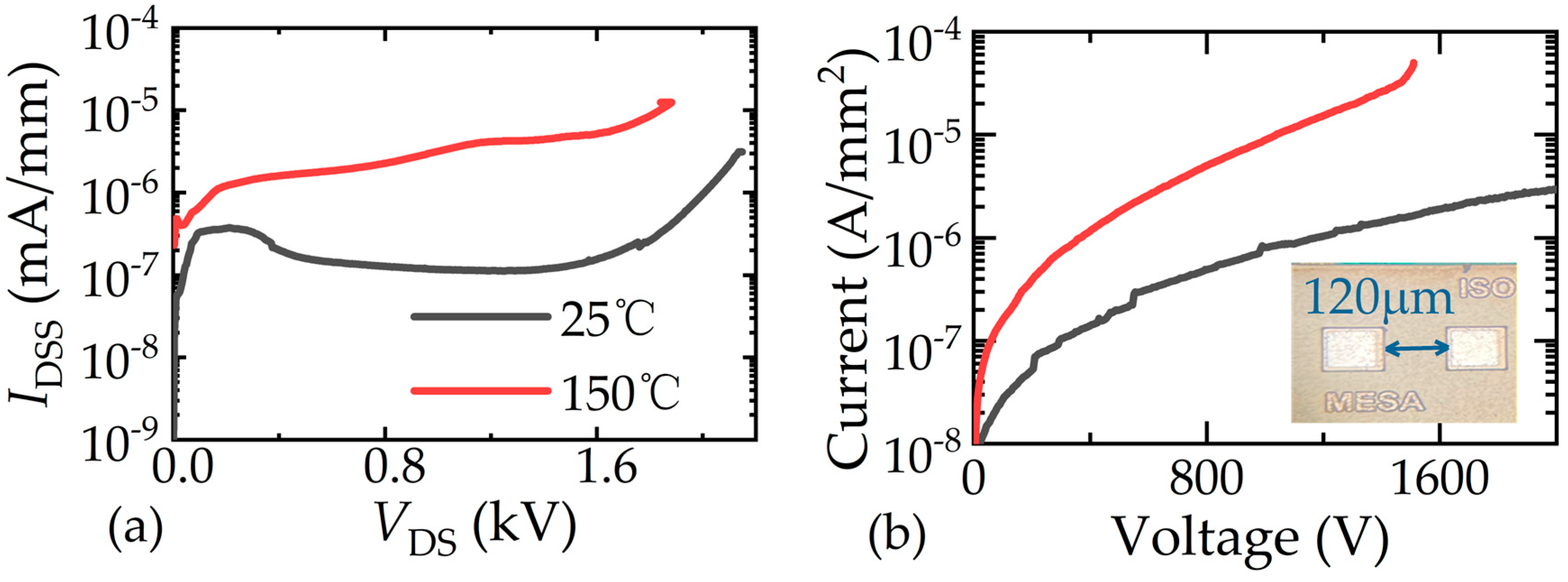

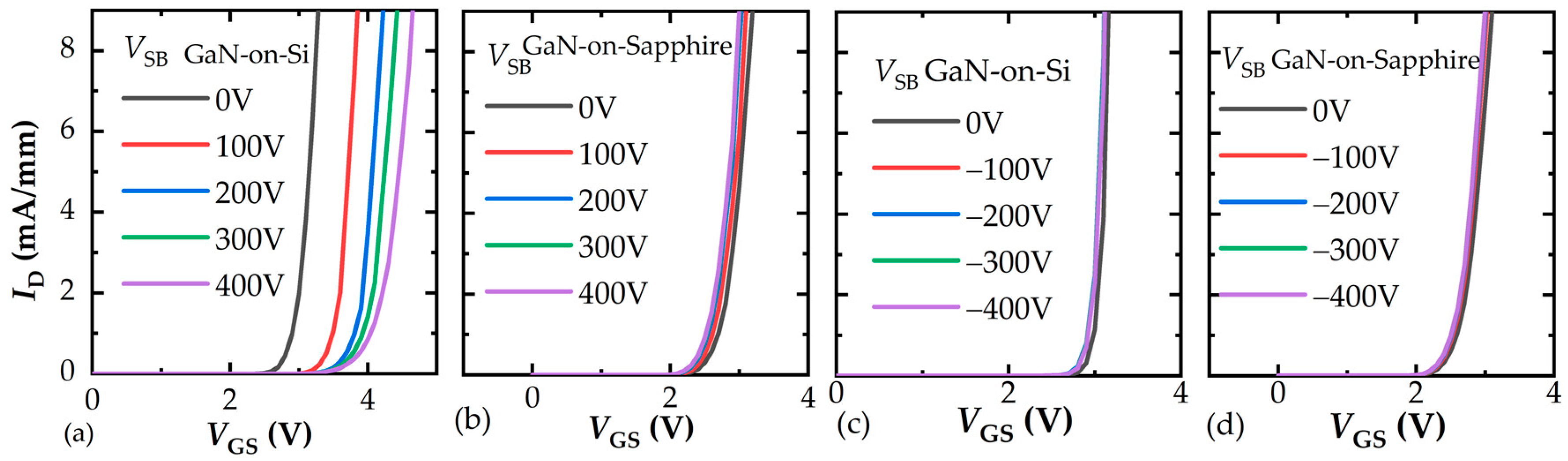

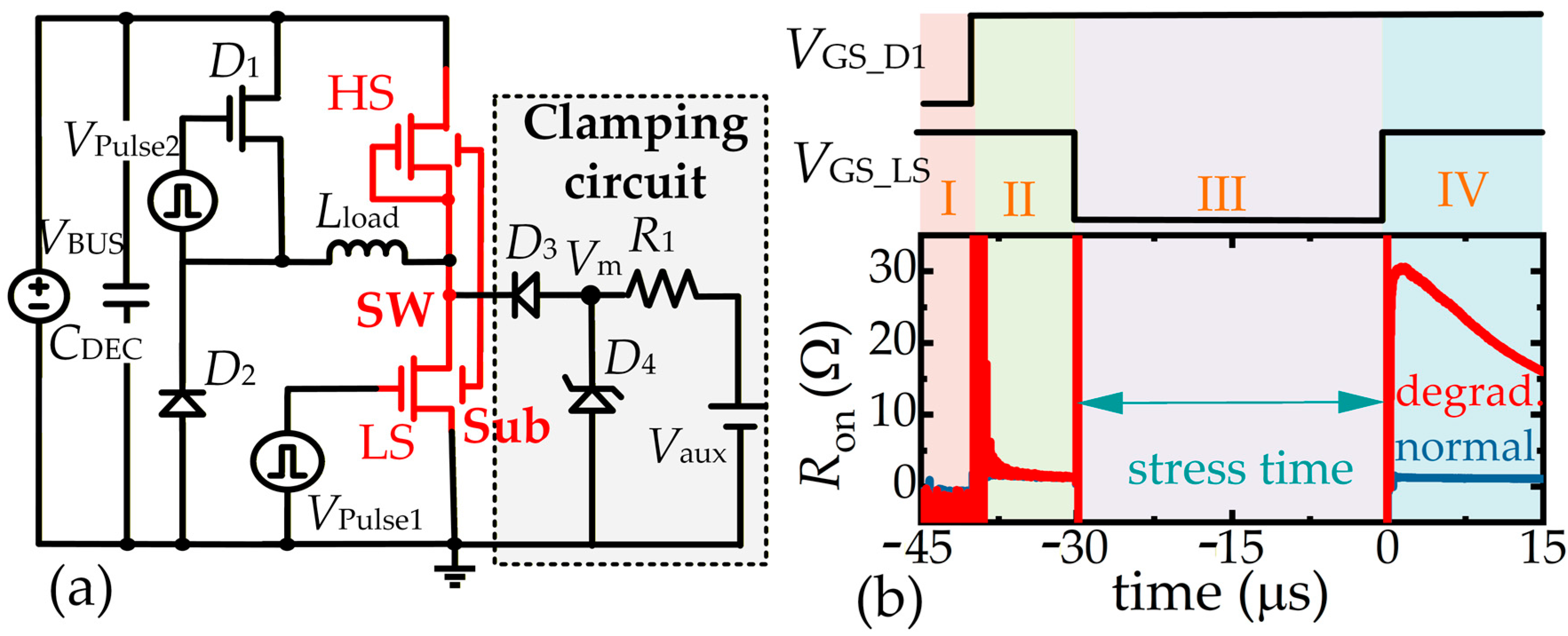

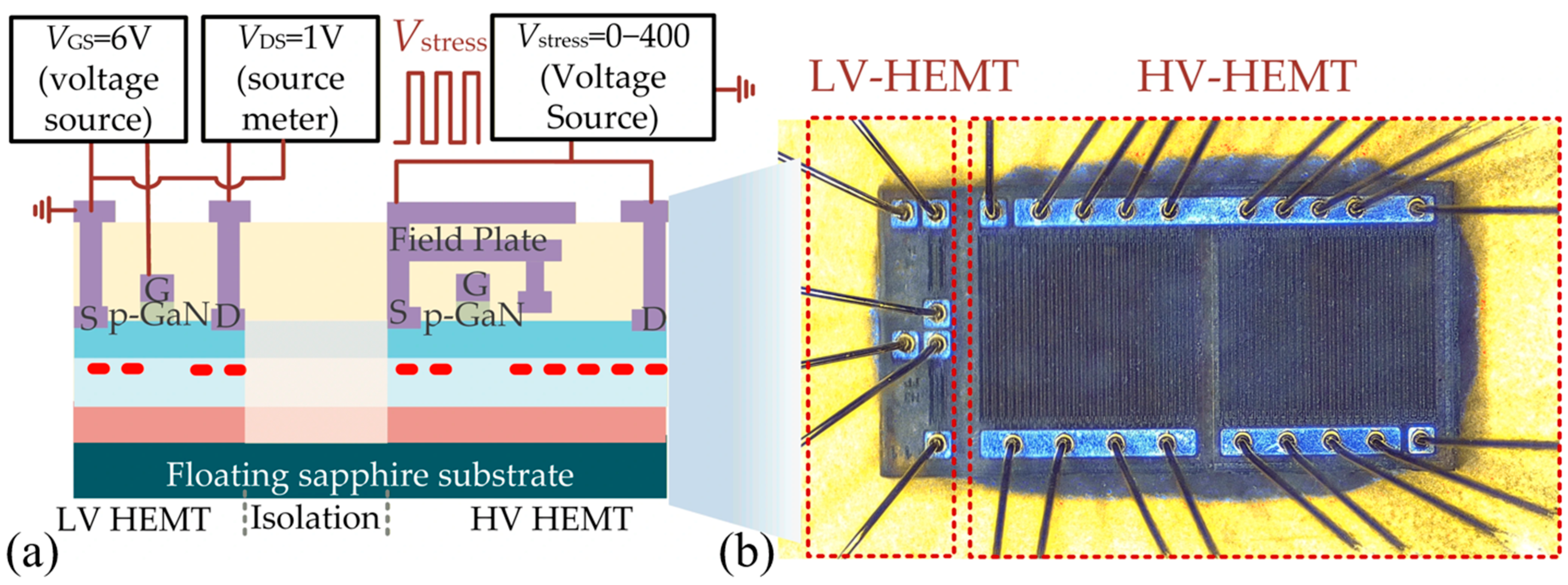

2. Device Fabrications and Characteristics

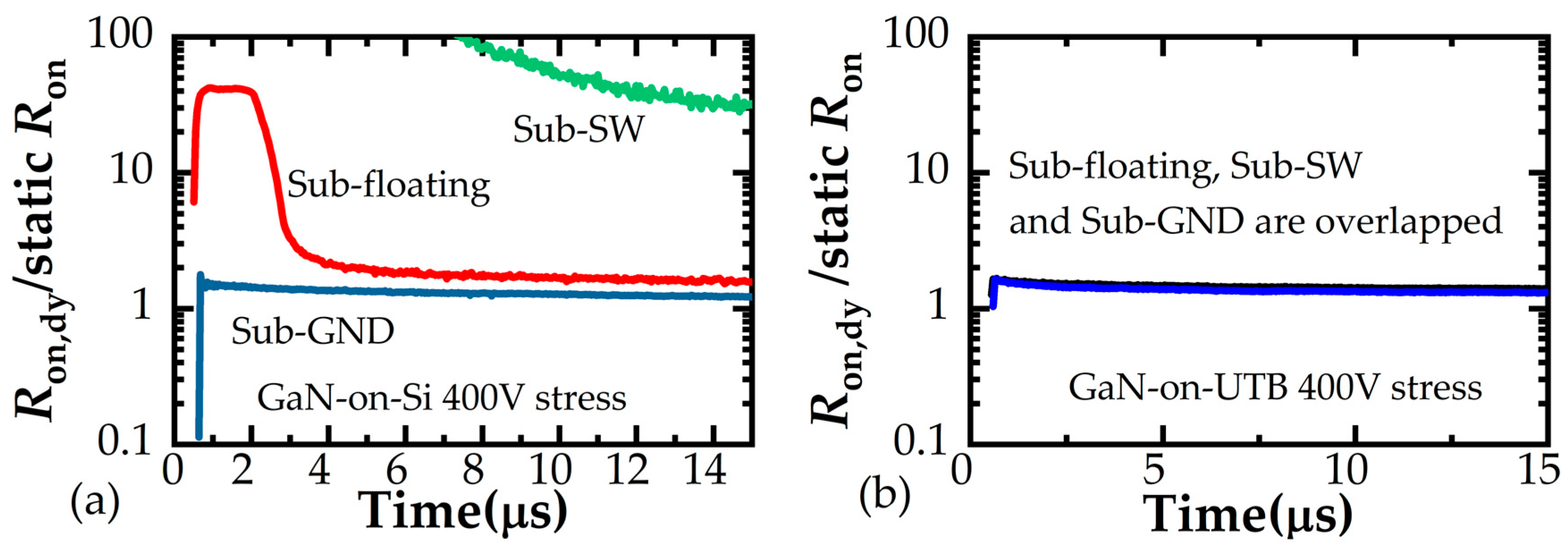

3. Results and Discussions

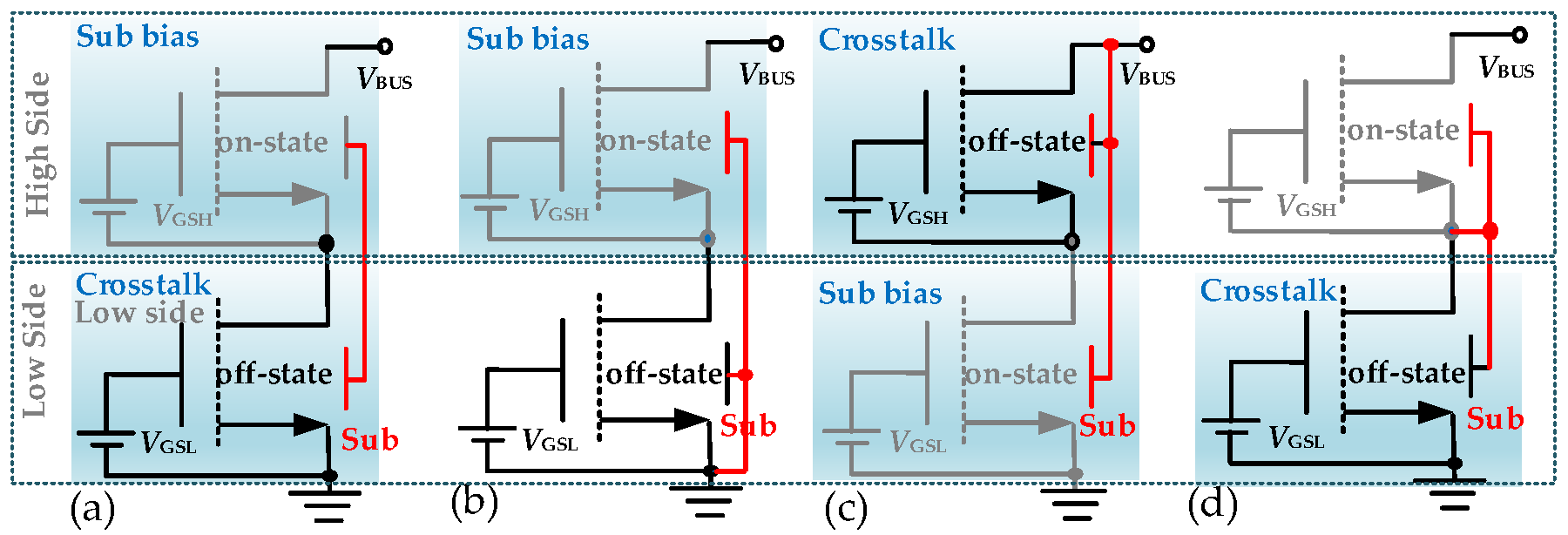

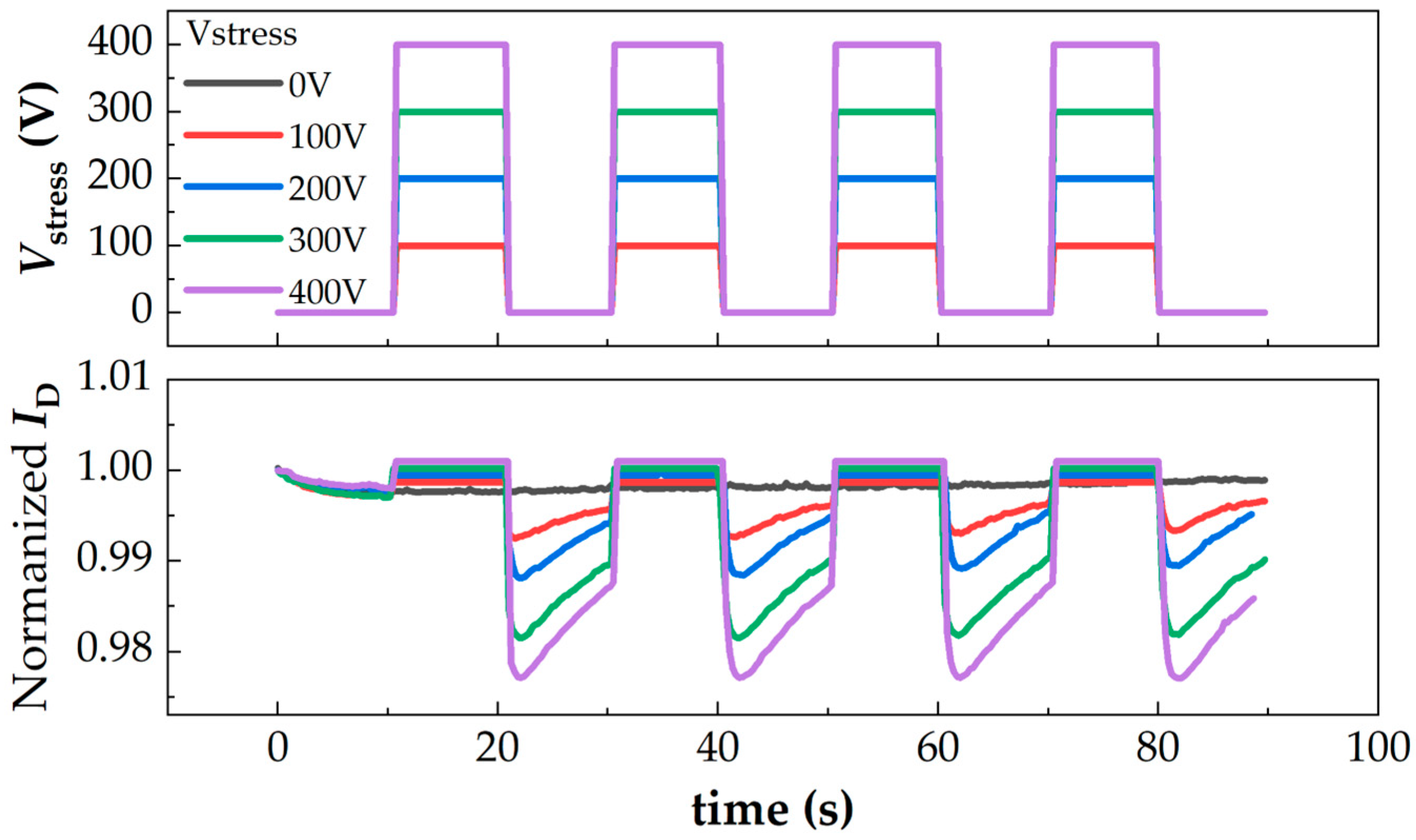

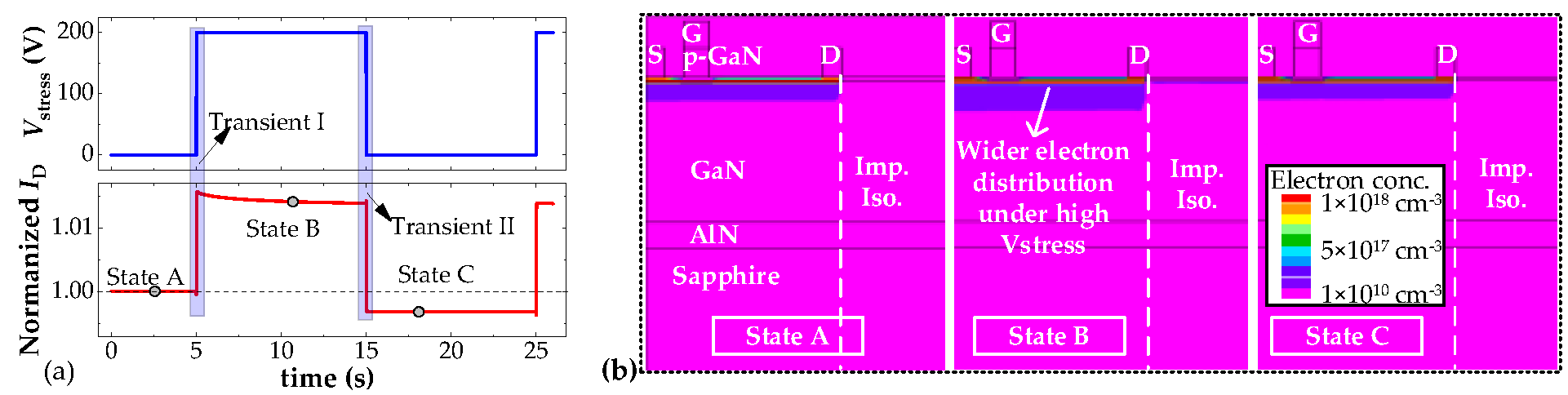

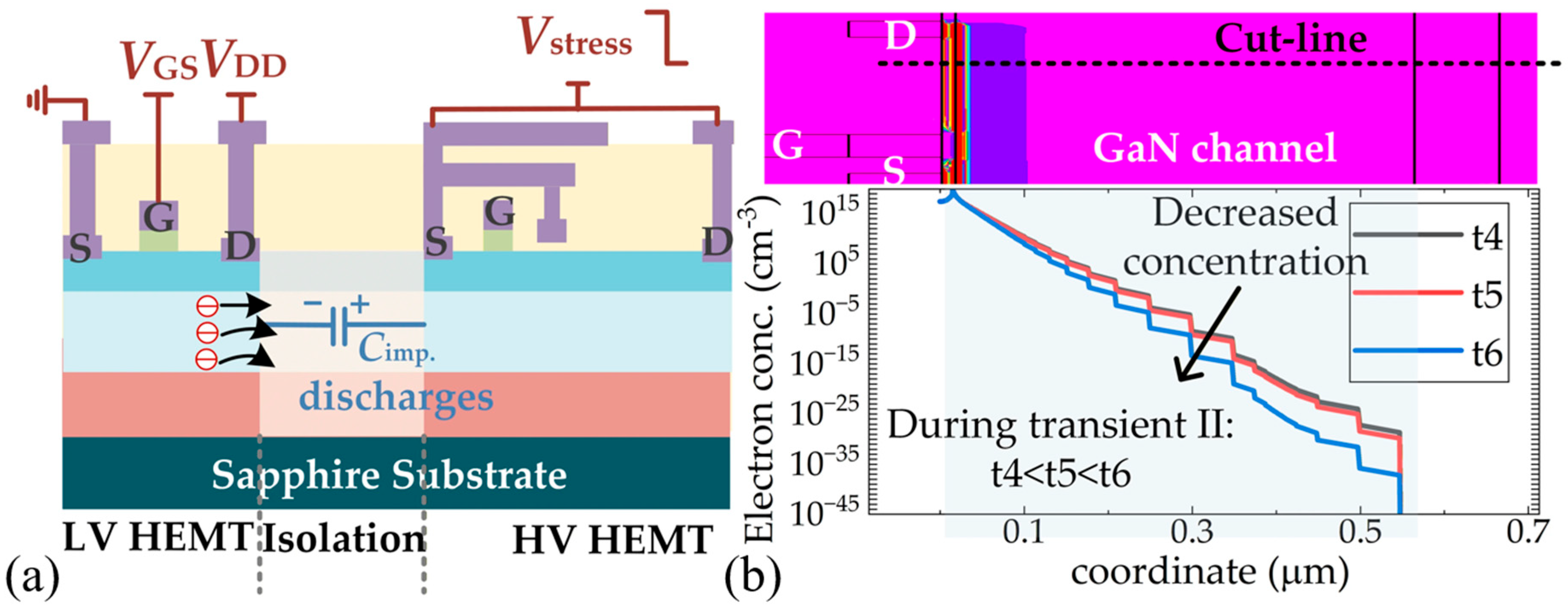

3.1. Isolation Between High Side Region and Low Side Region

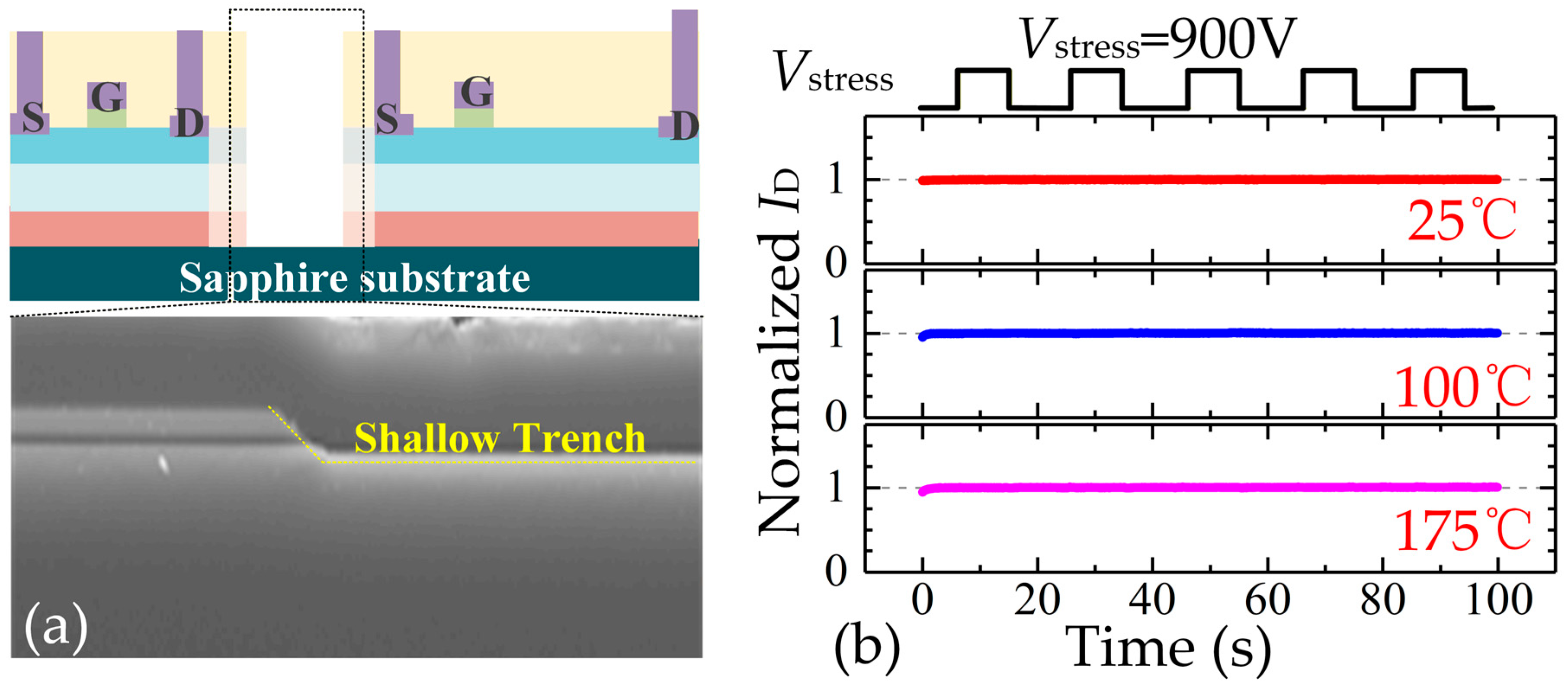

3.2. Isolation Between High-Voltage Devices and Low-Voltage Devices

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Yan, Y.; Wang, T.; Wang, Y.; Zhu, M.; Tang, H.; Qian, Q. Adaptive Dead-Time and Partial-ZVS Regulation for GaN-Based Active Clamp Flyback Converter With Predictive Hysteresis Current Mode Control. IEEE Trans. Electron. Power Elec. 2023, 38, 10782–10797. [Google Scholar] [CrossRef]

- Zheng, Y.; Li, B.; Dong, Q.; Song, D.; Zhu, J. A 200-V Half-Bridge Monolithic GaN Power IC With High-Speed Level Shifter and dVS/dt Noise Immunity Enhancement Structure. IEEE Trans. Electron. VLSI Syst. 2024, 32, 542–551. [Google Scholar] [CrossRef]

- Dong, Z.; Yan, H.; Fan, Y.; Wu, X.; Zhang, J. A 3-D Integrated Power Module of GaN HEMTs Based on Silver Sintering Processes. IEEE Trans. Electron. Power Elec. 2024, 39, 2932–2937. [Google Scholar] [CrossRef]

- Jiang, Q.; Tang, Z.; Zhou, C.; Yang, S.; Chen, K.J. Substrate-Coupled Cross-Talk Effects on an AlGaN/GaN-on-Si Smart Power IC Platform. IEEE Trans. Electron Devices 2014, 61, 3808–3813. [Google Scholar] [CrossRef]

- Wei, J.; Zhang, M.; Lyu, G.; Chen, K.J. GaN Integrated Bridge Circuits on Bulk Silicon Substrate: Issues and Proposed Solution. IEEE J. Electron Devices Soc. 2021, 9, 545–551. [Google Scholar] [CrossRef]

- Mönch, S.; Basler, M.; Reiner, R.; Benkhelifa, F.; Döring, P.; Sinnwell, M.; Müller, S.; Mikulla, M.; Waltereit, P.; Quay, R. GaN power converter and high-side IC substrate issues on Si, p-n junction, or SOI. E-Prime-Adv. Electr. Eng. Electron. Energy 2023, 4, 100171. [Google Scholar] [CrossRef]

- Li, X.; Hove, M.V.; Zhao, M.; Geens, K.; Guo, W.; You, S.; Stoffels, S.; Lempinen, V.-P.; Sormunen, J.; Groeseneken, G.; et al. Suppression of the Back gating Effect of Enhancement-Mode p-GaN HEMTs on 200-mm GaN-on-SOI for Monolithic Integration. IEEE Electron Device Lett. 2018, 39, 999–1002. [Google Scholar] [CrossRef]

- Lyu, G.; Wei, J.; Song, W.; Zheng, Z.; Zhang, L.; Zhang, J.; Cheng, Y.; Feng, S.; Ng, Y.H.; Chen, T.; et al. A GaN Power Integration Platform Based on Engineered Bulk Si Substrate with Eliminated Crosstalk between High-Side and Low-Side HEMTs. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021; pp. 5.2.1–5.2.4. [Google Scholar] [CrossRef]

- Sun, R.; Lai, J.; Chen, W.; Liu, C.; Wang, F.; Zhou, J. Crosstalk Suppression in Monolithic GaN Devices Based on Inverted E-Field Decoupling. IEEE Trans. Electron Devices 2021, 68, 1542–1549. [Google Scholar] [CrossRef]

- Li, S.; Ma, Y.; Lu, W.; Li, M.; Wang, L.; Zhang, Z.; Zhu, T.; Li, Y.; Wei, J.; Zhang, L.; et al. 1200V E-mode GaN Monolithic Integration Platform on Sapphire with Ultra-thin Buffer Technology. In Proceedings of the 2023 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 9–13 December 2023; pp. 1–4. [Google Scholar] [CrossRef]

- Zaidan, Z.; Al Taradeh, N.; Benjelloun, M.; Rodriguez, C.; Soltani, A.; Tasselli, J.; Isoird, K.; Phung, L.V.; Sonneville, C.; Planson, D.; et al. A Novel lsolation Approach for GaN-Based Power Integrated Devices. Micromachines 2024, 15, 1223. [Google Scholar] [CrossRef] [PubMed]

- Jiang, J.; Jiang, B.; Han, Z.; Zhang, Y.; Zhang, Y.; Zhang, M.; Ren, X. Suppressed Substrate-Coupled Cross-Talk Effects in GaN-on-Sapphire Platform Under High-Temperature and High-Voltage Applications. In Proceedings of the 2025 37th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Kumamoto, Japan, 1–5 June 2025; pp. 237–240. [Google Scholar] [CrossRef]

- Li, X.; Hove, M.V.; Zhao, M.; Geens, K.; Lempinen, V.; Sormunen, J.; Groeseneken, G.; Decoutere, S. 200 V Enhancement-Mode p-GaN HEMTs Fabricated on 200 mm GaN-on-SOI With Trench Isolation for Monolithic Integration. IEEE Electron Device Lett. 2017, 38, 918–921. [Google Scholar] [CrossRef]

- Wang, D.; Zheng, L.; Cheng, X.; Shen, L.; Liu, X.; Liu, S. Substrate Biasing Effect in a High-Voltage Monolithically-Integrated GaN-on-SOI Half Bridge with Partial Recessed-Gate HEMTs. IEEE Trans. Electron Devices 2023, 70, 2975–2980. [Google Scholar] [CrossRef]

- Jiang, W.L.; Murray, S.K.; Zaman, M.S.; De Vleeschouwer, H.; Roig, J.; Moens, P. Monolithic Integration of a 5-MHz GaN Half-Bridge in a 200-V GaN-on-SOI Process: Programmable dv/dt Control and Floating High-Voltage Level-Shifter. In Proceedings of the 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), Phoenix, AZ, USA, 14–17 June 2021; pp. 728–734. [Google Scholar] [CrossRef]

- Lyu, G.; Wei, J.; Song, W.; Zheng, Z.; Zhang, L.; Zhang, J. GaN on Engineered Bulk Si (GaN-on-EBUS) Substrate for Monolithic Integration of High-/Low-Side Switches in Bridge Circuits. IEEE Trans. Electron Devices 2022, 69, 4162–4169. [Google Scholar] [CrossRef]

- Lyu, G.; Wei, J.; Chen, T.; Zhang, J.; Chen, K.J. Substrate and Trench Design for GaN-on-EBUS Power IC Platform. IEEE Trans. Electron Devices 2022, 69, 3641–3647. [Google Scholar] [CrossRef]

- Lyu, G.; Wei, J.; Ng, Y.H.; Cheng, Y.; Feng, S.; Chen, K.J. Substrate and Trench Design for GaN-on-EBUS Power IC Platform Considering Output Capacitance and Isolation between High-side and Low-side Transistors. In Proceedings of the 2022 IEEE 34th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vancouver, BC, Canada, 22–25 May 2022; pp. 185–188. [Google Scholar] [CrossRef]

- Yang, J.; Liu, S.; Yu, J.; Cui, J.; Chang, H.; Li, T. 3-KV GaN Smart Power Integration Platform for High-Power-Density Conversion Systems Using Charge-Balanced Superjunction Technology. In Proceedings of the 2025 Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Kyoto, Japan, 8–12 June 2025; pp. 1–3. [Google Scholar] [CrossRef]

- Yu, J.; Yang, J.; Cui, J.; Chang, H.; Liu, S.; Lao, Y. 9-kV p-GaN Gate HEMT with Gate Termination Extension Demonstrated on Sapphire Substrate for Improved Breakdown Voltage. In Proceedings of the 2025 9th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), Hong Kong, China, 9–12 March 2025; pp. 1–3. [Google Scholar] [CrossRef]

- Yang, S.; Zhou, C.; Han, S.; Sheng, K.; Chen, K.J. Buffer trapping-induced RON degradation in GaN-on-Si power transistors: Role of electron injection from Si substrate. In Proceedings of the 2017 29th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Sapporo, Japan, 28 May–1 June 2017; pp. 101–104. [Google Scholar] [CrossRef]

- Wei, J.; Zheng, Z.; Tang, G.; Xu, H.; Lyu, G.; Zhang, L.; Chen, J.; Hua, M.; Feng, S.; Chen, T.; et al. GaN Power Integration Technology and Its Future Prospects. IEEE Trans. Electron Devices 2024, 71, 1365–1382. [Google Scholar] [CrossRef]

- Available online: https://silvaco.com/dynamicweb/jsp/downloads/DownloadDocStepsAction.do?req=download&nm=simstd_Q1_2012_a2.pdf (accessed on 1 January 2012).

- Yu, H.; Peralagu, U.; Alian, A.; Zhao, M.; Parvais, B.; Collaert, N. Parasitic side channel formation due to ion implantation isolation of GaN HEMT. MRS Adv. 2022, 7, 1274–1278. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, S.; Zhang, H.; Ma, Y.; Wang, Q.; Wang, K.; Xia, Y.; Wu, L.; Li, Y.; Zhu, T.; Ye, R.; et al. Investigation on the Isolation Approaches for High-Voltage GaN-on-Sapphire Monolithic Power Integrated Circuits. Micromachines 2025, 16, 1336. https://doi.org/10.3390/mi16121336

Li S, Zhang H, Ma Y, Wang Q, Wang K, Xia Y, Wu L, Li Y, Zhu T, Ye R, et al. Investigation on the Isolation Approaches for High-Voltage GaN-on-Sapphire Monolithic Power Integrated Circuits. Micromachines. 2025; 16(12):1336. https://doi.org/10.3390/mi16121336

Chicago/Turabian StyleLi, Sheng, Haiwei Zhang, Yanfeng Ma, Qinhan Wang, Ke Wang, Yuanyang Xia, Leke Wu, Yiheng Li, Tinggang Zhu, Ran Ye, and et al. 2025. "Investigation on the Isolation Approaches for High-Voltage GaN-on-Sapphire Monolithic Power Integrated Circuits" Micromachines 16, no. 12: 1336. https://doi.org/10.3390/mi16121336

APA StyleLi, S., Zhang, H., Ma, Y., Wang, Q., Wang, K., Xia, Y., Wu, L., Li, Y., Zhu, T., Ye, R., Wei, J., Zhang, L., Liu, S., & Sun, W. (2025). Investigation on the Isolation Approaches for High-Voltage GaN-on-Sapphire Monolithic Power Integrated Circuits. Micromachines, 16(12), 1336. https://doi.org/10.3390/mi16121336