1. Introduction

In recent years, with advances in chip and electronic component design and manufacturing technologies, electronic devices have been evolving toward higher density, greater integration, and miniaturization [

1,

2,

3]. However, this trend has increasingly exposed electronic systems to coupled thermo–mechanical–electrical (TME) multi-physics problems under harsh environments, which have become key factors affecting system reliability [

4,

5,

6,

7,

8]. Under harsh operating conditions, the combined effects of high temperature, mechanical vibration, and shock often lead to solder joint crack initiation and propagation, interconnection failure, and degradation of high-speed signal links, thereby substantially reducing the system’s overall reliability [

9,

10,

11]. Kanai et al. [

12] experimentally demonstrated that rapid thermal cycling induces equibiaxial stress in solder joints, leading to sequential formation and propagation of cross-shaped cracks; as crack density increases, mutual interference between cracks results in the formation of a fatigue crack network. Cheng et al. [

13], using finite element analysis coupled with the Anand constitutive model, revealed the failure mechanisms of solder layers in high-power laser diode microchannel cooling systems under thermal cycling and random vibration, showing that thermal cycling predominantly drives evolution of damage and substantially limits reliability. Jeyun Yeom et al. [

14] investigated the mechanical and microstructural degradation of solder joints made with different lead-free and SnPb solders under 3000 thermal cycles (−55 °C to +100 °C), revealing the correlation between crack and void evolution and shear strength degradation, thereby providing insights into developing highly reliable surface-mounted components for aerospace applications. Cui et al. [

15] studied the electromigration (EM) reliability and failure mechanisms of complex electronic components, finding through simulations and experiments that interconnect reliability under EM is significantly influenced by the formation of solder voids, IMC growth, and crack evolution. Fan et al. [

16] reported that the incorporation of Cu@Sn@Ag (CSA) core–shell particles into SAC305 solder joints significantly refines the microstructure and enhances tensile strength, while mitigating corrosion-induced degradation of mechanical properties over time. However, these studies primarily focused on single packages or isolated interconnects, often neglecting the system-level influence of coupled TME fields across the entire electronic assembly. As a result, the underlying mechanisms governing multiphysics-driven failure in complex systems, such as ruggedized computers, remain insufficiently understood.

In the field of multi-scale modeling, some researchers have proposed hierarchical modeling strategies for multi-chip packages and electronic components, in which models are established at the material, device, and system levels, and coupled computations are achieved through heterogeneous model transformation and information transfer [

17,

18]. Li et al. [

19] investigated the reliability of PCB under thermal cycling and random vibration. Wei Yu et al. [

20] presented how machine learning potentials and MD-to-FEM conversion facilitate multi-scale simulation with DFT accuracy. Wei Zheng et al. [

21] proposed a reliability prediction method based on multi-physics coupling and hybrid-precision simulation, which integrates electro–thermal–mechanical analysis with IBIS-based topology modeling to reveal the failure mechanisms and signal integrity degradation of key CMOS chips in mixed-signal electronic systems under complex operating conditions, thereby significantly improving the accuracy of failure mode prediction and system reliability evaluation. Kaixiang Peng et al. [

22] investigated the temperature-dependent electrical behavior of coaxial annular TSVs using a multi-physics approach, combining circuit and electromagnetic simulations, and proposed a metal–dielectric–metal TSV design to improve signal integrity across a wide temperature range. Although these studies improved modeling efficiency and cross-scale information transfer, they were mainly validated on simplified geometries and are difficult to extend to complex system-level assemblies containing chips, solder joints, and multi-layered motherboards.

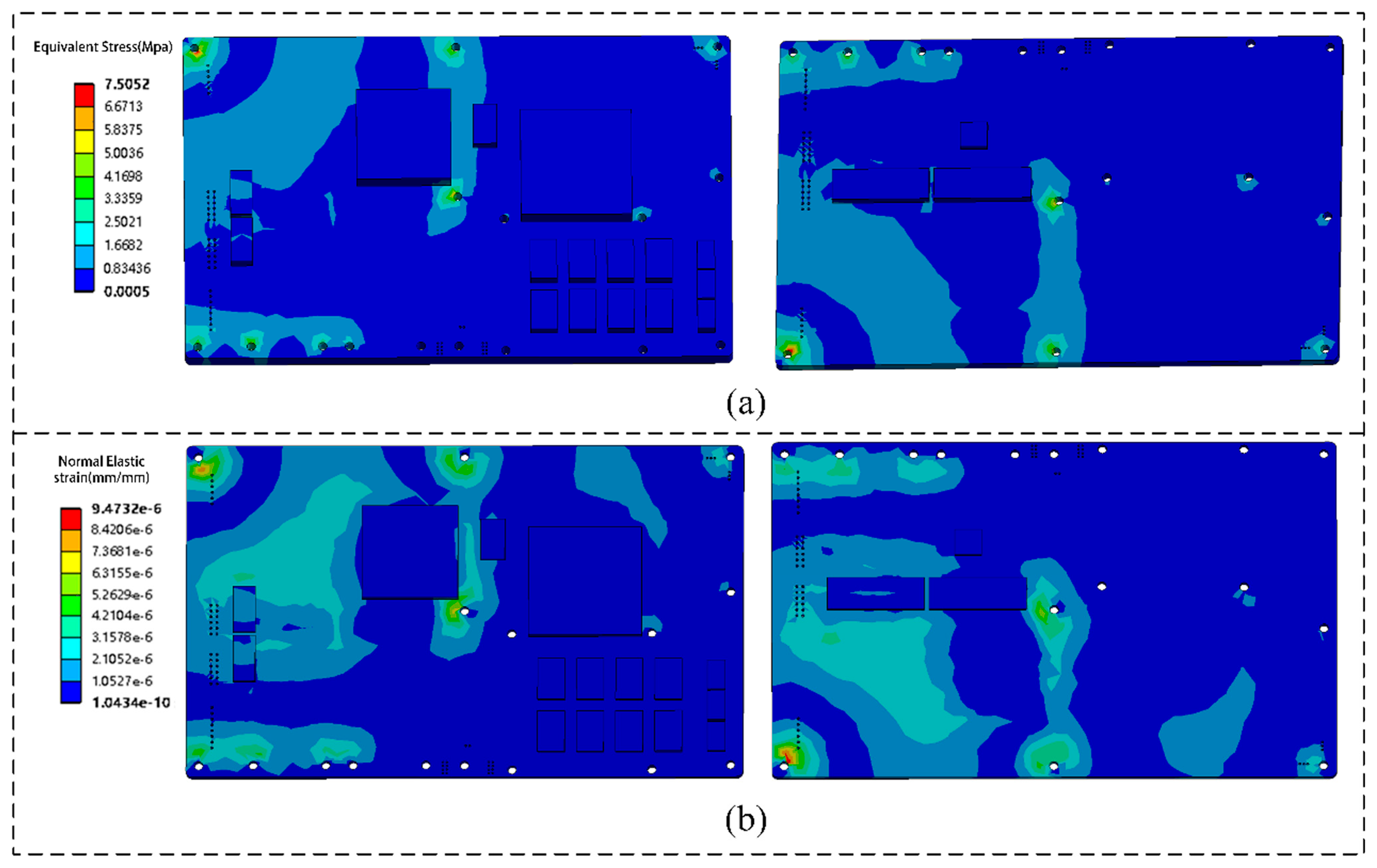

In the field of multiphysics coupling analysis, Yang et al. [

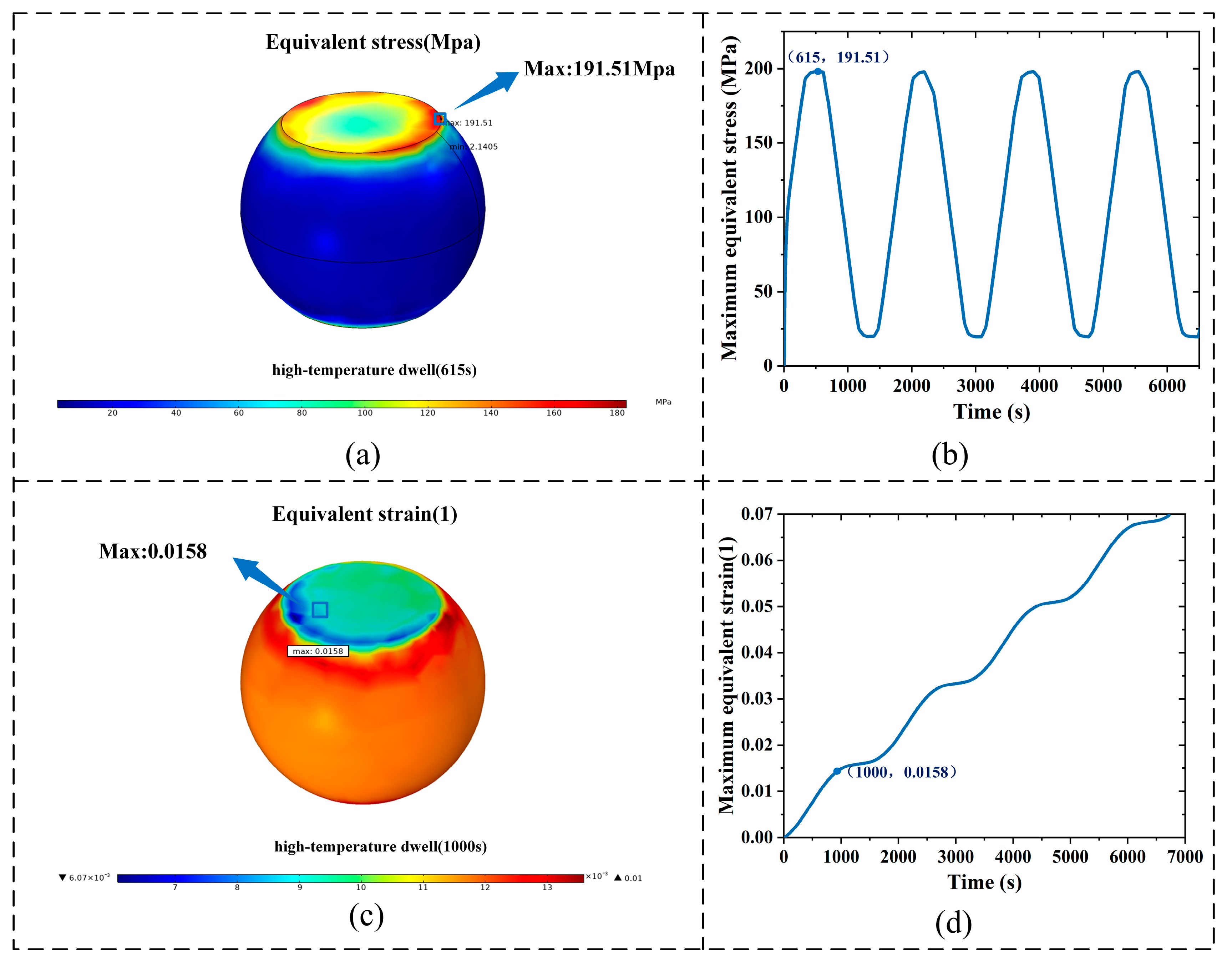

23] conducted thermo–mechanical coupling analysis of IGBT materials to predict the temperature distribution, equivalent stress, and equivalent strain of solder materials under actual operating conditions, thereby revealing the interaction mechanisms between thermal and mechanical effects. Chen et al. [

24] experimentally and numerically characterized the thermoelectric coupling behavior of ternary lithium-ion batteries, demonstrating its critical influence on battery performance and lifetime. Xiao et al. [

25] systematically studied the fatigue failure mechanisms and lifetime prediction methods of electronic devices under random vibration environments, proposing an integrated evaluation approach combining finite element analysis with experimental validation. Gao et al. [

26] explored the modeling and signal integrity analysis of silicon interposer channels, providing insights into the challenges and solutions in high-speed interconnects. In summary, existing research has mainly focused on single-field coupling, such as thermo–mechanical, thermo–electrical, and electro–mechanical interactions [

27,

28,

29,

30,

31], whereas comprehensive investigations of fully coupled thermo–electro–mechanical effects within high-density electronic systems are scarce. Furthermore, for ruggedized computers, direct full-scale modeling of all hierarchical structures would dramatically increase computational cost and model complexity [

32].

Therefore, it is essential to develop an efficient, scalable, and accurate multiscale TME modeling and analysis framework to provide deeper insight into Multiphysics interactions and to support both signal integrity (SI) and reliability assessments under extreme operating conditions.

The main contributions of this study are summarized as follows:

- (1)

It focuses on solder joints and interconnect structures under thermo–electro–mechanical (TME) Multiphysics coupling;

- (2)

It proposes a multi-scale modeling strategy spanning solder joint, board, and system-level analysis;

- (3)

It investigates microstructural evolution in solder joints and interconnects and its impact on signal integrity;

- (4)

It provides experimental validation and optimization insights, offering guidance for enhancing the reliability and performance of ruggedized computers.

2. Modeling

To accurately characterize the Multiphysics coupling behavior of electronic packaging structures under complex operating conditions, a Multiphysics coupling mathematical model is established in this section, together with a numerical information transfer method between heterogeneous models. The constructed coupling model encompasses typical physical interactions, including thermal–electrical, thermal–mechanical, and mechanical–electrical couplings, while incorporating atomic concentration migration effects to provide a theoretical basis for elucidating the interactions among thermal, electrical, and mechanical fields. Based on this framework, a heterogeneous model coupling strategy is further proposed, which includes substructure-based multiscale modeling, deformation information transfer, and multiscale simplification techniques. These methods enable efficient exchange of information between different physical fields and across multiple scales, balancing modeling accuracy with computational efficiency.

2.1. Multiphysics Coupling Mathematical Model

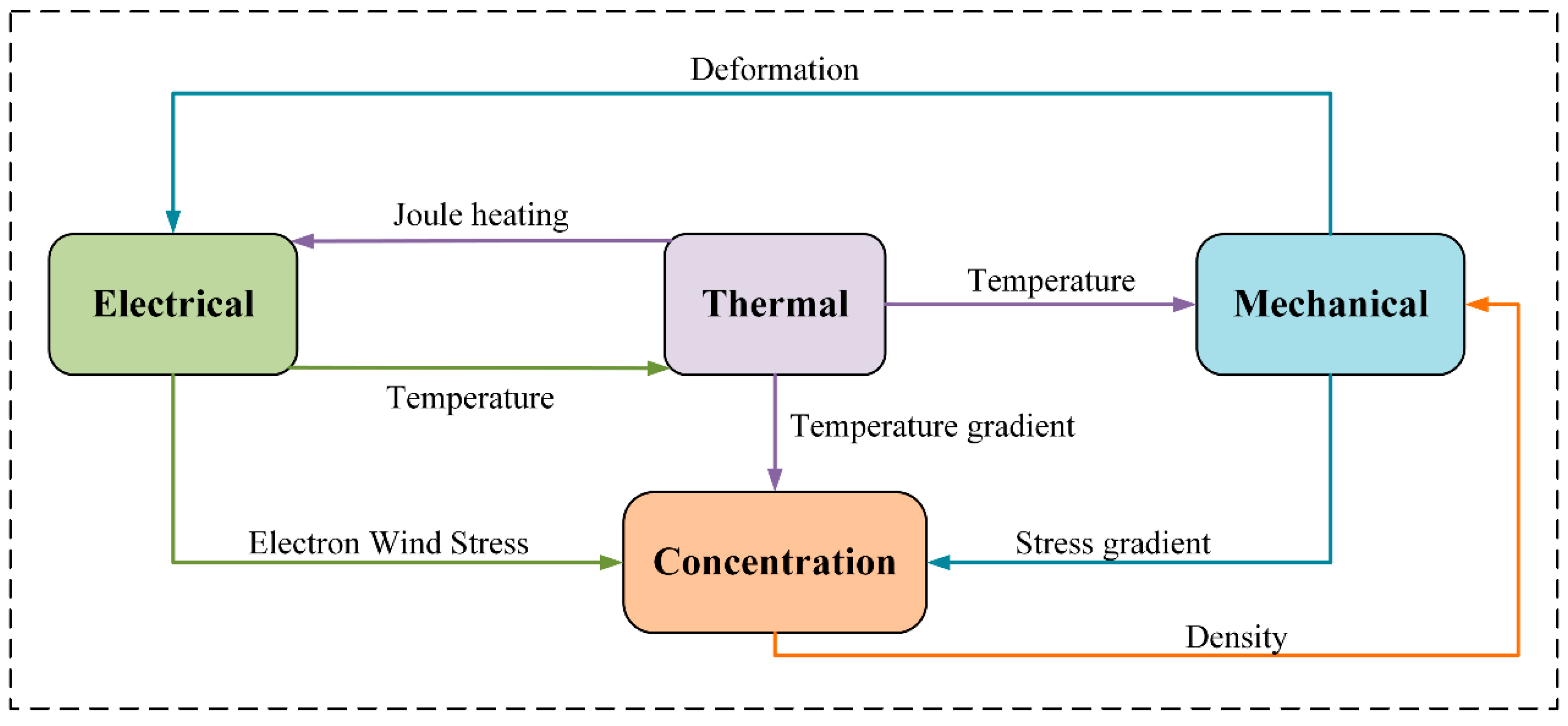

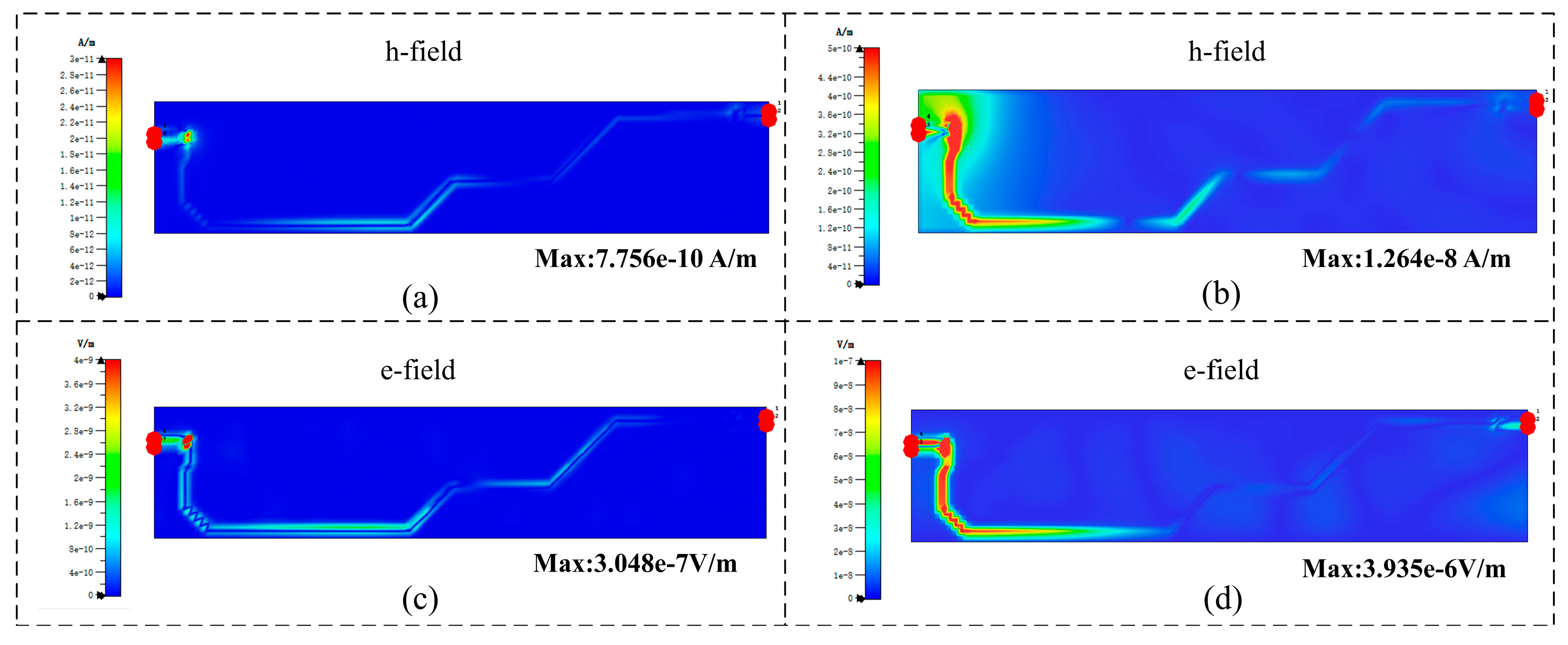

During the operational process of ruggedized computers, the coupled effects of thermal, mechanical, and electrical fields are highly pronounced, significantly affecting system reliability. In operation, the interactions among local heating, current distribution, and stress variations give rise to complex multiscale coupling phenomena. Therefore, conducting a systematic theoretical analysis of the Multiphysics coupling behavior of BGA solder balls is of great significance. This study mainly focuses on the interactions among the electric field, temperature field, stress field, and charge concentration field. As shown in

Figure 1, complex interactions exist among the electrical, thermal, mechanical, and concentration fields. The electrical field induces a local temperature rise through Joule heating and generates electron wind stress in the conductor. The thermal field is not only influenced by the electrical field but also affects the mechanical and concentration fields through temperature and temperature gradients. The mechanical field, driven by temperature, produces stress and deformation, and further develops stress gradients that drive the migration of the concentration field. The evolution of the concentration field is jointly influenced by both stress and temperature gradients, while its density variation, in turn, feeds back to the mechanical field. Such Multiphysics coupling relationships collectively determine the evolution behavior and service reliability of solder joints.

2.1.1. Thermo–Electrical Coupling Effect

During the operation of the computer, key components such as the CPU, DDR, and GPU generate significant Joule heat during data processing, resulting in local temperature rises. Meanwhile, the electrical conductivity of conductive materials on the PCB, including copper traces and solder joints, is temperature-dependent. Variations in temperature lead to changes in conductivity, which in turn affect the distribution of current density and electric field. The fundamental coupling between the thermal field (temperature field) and the electrical field is governed by the conservation of energy—including Joule heating and thermoelectric effects such as Peltier and Seebeck—and the conservation of charge, which accounts for temperature-dependent conductivity:

Charge conservation equation:

where

Φ is the electric potential,

σ(

T) is the temperature-dependent electrical conductivity,

S(

T) is the Seebeck coefficient, and

T denotes the temperature.

Energy Conservation Equation:

where

ρ is the material density,

cp is the specific heat capacity,

k(

T) is the temperature-dependent thermal conductivity,

Qmech is the power density generated by mechanical dissipation converted to heat, and

denotes the current density.

The effect of the temperature field on the electric field is expressed by Equation (3):

where

R is the electrical resistance,

T is the temperature, and

ρ0 is the conductor resistance at the reference temperature. Physically, this indicates that as the temperature of BGA solder joints increases, their electrical resistance correspondingly rises.

Furthermore, during high-speed signal transmission, the skin effect and dielectric losses cause heating of the computer traces, further exacerbating the nonuniformity of the temperature field. Localized overheating can affect the clock stability of the chips and may even lead to performance degradation or permanent damage to electronic components. The influence of the electric field on the temperature field is expressed by Equation (4):

where

Q is the Joule heat,

σcis the electrical conductivity, and

V denotes the electric potential. Physically, this means that when a conductor on the computer carries current, the generated Joule heat is proportional to the square of the electric potential gradient and also proportional to the electrical conductivity of the conductor.

2.1.2. Thermo–Mechanical Coupling Effect

During temperature variations in the computer, various components undergo thermal expansion or contraction [

20]. Due to the mechanical constraints inherent in computer structures, thermal deformation of the board is restricted, generating internal thermal stress. Furthermore, complex PCB comprises multiple materials such as copper, solder, and FR-4, which have different coefficients of thermal expansion (CTE), leading to stress gradients among components during thermal cycling. For instance, between the chip and PCB, the mismatch of CTEs between the solder and PCB can induce fatigue-induced cracks in solder joints under repeated temperature variations, reducing soldering reliability. Such thermal–mechanical coupling effects may also deform high-speed signal paths, thereby affecting signal integrity.

The effect of the temperature field on the structural field is expressed by Equation (5).

where

σ is the stress,

ε is the strain,

E is the elastic modulus,

β is the thermal expansion coefficient, and

denotes the temperature. Physically, temperature differences within the computer structure cause deformations of the elements, which in turn generate stress. In multi-physics coupling analysis, the feedback effect of the structural field on the thermal field is generally weak. In engineering practice, a one-way coupling assumption is often adopted to improve computational efficiency.

2.1.3. Mechanical–Electrical Coupling Effect

In practical operating environments, computer may be subjected to external vibrations or shocks. Due to the differing elastic moduli of components within the board-level circuitry, nonuniform mechanical loading can induce localized stress concentrations, leading to changes in electrical resistance. The influence of the structural field on the electrical resistance in the electric field can be expressed by Equation (6).

where

R0 is the initial resistance;

κρ is the temperature coefficient of resistance; Δ

T is the temperature change;

Gε is the gauge factor relating resistance to strain; and

ε denotes the linear strain. Physically, variations in strain within the structural field induce corresponding changes in electrical resistance.

When the computer is subjected to mechanical impact, solder joints and interconnects may undergo slight deformations. Under the combined influence of electric field, temperature, stress, and concentration gradients, metal atoms can migrate, alter current paths and locally increase current density, which may lead to electromigration. Driven by multiple migration forces, metal atoms within the solder joint move directionally, resulting in the formation of voids. Such changes impede current flow, restrict electrical transmission at the board level, and can ultimately cause circuit failure [

33].

Furthermore, high current density may induce migration of metal atoms within the solder joints, resulting in void formation that compromises the mechanical strength of the joints. After prolonged service, solder joints may crack or fail due to electromigration. The influence of the electric field on the structural field can be expressed by Equation (7):

where

f is the force vector per unit volume acting on the charge,

is the free charge density,

E is the electric field strength,

J is the current density vector and

B is the magnetic flux density vector. Physically, the combined effects of the electric and magnetic fields exert forces on the conductors within the computer, thereby influencing their mechanical behavior.

2.1.4. Concentration-Driven Atomic Migration

Atoms undergo directional motion under the combined effects of electron wind, thermal gradients, and stress gradients. As electromigration progresses, it leads to an imbalance in atomic concentration distribution. According to Le Chatelier’s principle, such nonuniform concentration generates a driving force that encourages atoms to move toward regions of lower concentration, thereby mitigating electromigration. The influence of this effect increases with the magnitude of the concentration gradient. Migration driven by atomic concentration gradients is referred to as chemical migration. For the concentration of metal atoms, the atomic diffusion flux can be expressed as follows:

where

is the concentration gradient;

is the atomic diffusion coefficient;

is the effective charge number;

is the elementary charge;

is the atomic volume;

is the hydrostatic stress;

is the activation energy for thermal migration;

is the Stefan-Boltzmann constant; and

T is the absolute temperature. The migration force acts in the direction of decreasing concentration.

Therefore, electromigration failure results from the combined action of driving forces such as electron wind, thermal gradients, stress gradients, and atomic concentration gradients. Consequently, the study of electromigration mechanisms should consider all these driving factors comprehensively, necessitating a multi-physics coupling analysis.

2.2. Numerical Information Transfer Method for Heterogeneous Model Coupling

In multi-physics coupling analysis, multiple data sources exhibit diverse types and complex interaction pathways, and uncertainties arising from these sources can significantly affect performance evaluation. On one hand, system-level performance assessment typically involves multidisciplinary analyses, such as thermal, mechanical, and electrical studies at different scales. The substantial differences in model formulations across disciplines and the heterogeneity of numerical solution schemes make the matching and sharing of mesh information between heterogeneous models challenging. Interaction of nodal information across physical fields must be based on unified numerical transfer rules, with mesh alignment serving as a prerequisite for ensuring data consistency. On the other hand, the types of coupled information are diverse, and not all data can be directly transferred via nodal information. Integrating and fusing certain information is complex and requires collaborative numerical methods to achieve indirect transfer.

2.2.1. Substructure Theory for Multiscale Modeling

In the field of finite element multiscale modeling, substructuring techniques are widely employed as a core method for packaging structure analysis. In this study, based on the structural characteristics of packaging components, the chip units and solder assemblies are identified as the core regions for substructure generation. The technical workflow mainly includes the following steps: First, a three-dimensional geometric model of the chip–solder composite structure is constructed using parametric modeling techniques. Next, a multiscale mesh generation strategy is established, ensuring mesh compatibility across scales through size control. On this basis, the determination of material constitutive parameters is emphasized, and an equivalent elastic mechanical parameter derivation method based on microstructural features is proposed, establishing a modulus correction model under multi-physics coupling conditions. Additionally, corresponding programs are developed to implement the substructuring of chip solder joints, enabling automated generation.

The substructure method can be regarded as an extension of the element concept. When the internal degrees of freedom are not condensed, a single substructure is equivalent to a “super element” containing numerous internal degrees of freedom. Prior to integrating the substructure into the global computation, the internal degrees of freedom are condensed to reduce the overall system size, retaining only the external nodes required for connection with other elements. The substructure method introduces the concepts of master degrees of freedom (DOF) nodes and slave DOF nodes. Master DOF nodes are those that connect the substructure element to other elements, while slave DOF nodes are those whose DOFs need to be condensed. Based on this concept, with appropriate node numbering, the stiffness matrix of the substructure, along with the corresponding nodal displacement and load vectors, can be expressed in the form shown in Equation (10):

where

is the displacement vector of the master DOF nodes, and

is the displacement vector of the slave DOF nodes.

Based on Equation (10), the resulting expressions are given in Equations (11) and (12):

By rearranging Equation (12), Equation (13) can be obtained.

By substituting Equation (13) into Equation (11), Equation (14) is obtained.

By rearranging Equation (14), Equation (15) can be obtained.

By defining

,

, the condensed equation can be expressed in the simplified form shown in Equation (16)

:This method reconstructs the equilibrium equations via a stiffness matrix reduction algorithm, reducing the computational burden of element matrices while maintaining the accuracy of the original system’s mechanical response. Based on this approach, a hierarchical substructure solution framework is established, which combines multilevel substructure decomposition with parallel computing architecture, enabling efficient handling of large-scale engineering models with millions of degrees of freedom and substantially improving computational efficiency.

2.2.2. Unified Error-Bound Mapping Method

In the multi-physics analysis of BGA solder joints in Ruggedized Computers, efficient transfer of deformation information across structural, thermal, and electromagnetic domains is critical. However, the solver architectures of these domains are inherently heterogeneous—structural solvers adopt finite element methods (FEM) with hybrid solid–shell elements, electromagnetic solvers employ frequency-domain FEM, time-domain finite-difference, or method-of-moments schemes, and thermal solvers use hexahedron-dominated finite volume meshes. Such numerical heterogeneity results in grid incompatibility, making unified cross-field data transfer highly challenging.

To overcome this issue, a unified error-bound mapping method is proposed as the core of this work. This method quantitatively establishes the correlation between mesoscale equivalent layers in mechanical deformation fields and electromagnetic signal integrity (SI) responses, enabling traceable, verifiable data propagation across physical domains.

Instead of directly interpolating deformation data, the proposed mapping introduces an error-bound model that constrains deformation–field translation within a defined tolerance range. By tracking equivalent nodal displacements and local strain energy densities at each layer interface, the framework evaluates cumulative deviations during the deformation-to-SI transformation. This quantitative verification bridges mechanical deformation and electromagnetic signal behavior, providing a physically consistent correlation that replaces empirical adjustment with rigorous cross-domain validation.

The framework integrates Ansys SpaceClaim2023 R1, Workbench2023 R1, Icepak2023 R1, AEDT2023 R1, and CST Studio Suite2023 to support this mapping process. Parametric geometries are first constructed in SpaceClaim; structural responses are computed in Workbench; thermal conditions are evaluated in Icepak; and electromagnetic characteristics are analyzed in AEDT and CST. Standardized data interfaces automate the transfer of geometric and physical quantities among solvers.

A cross-reference table (

Table 1) summarizes the detailed layer-wise mapping and verification workflows that support the proposed unified error-bound mapping method. The table outlines how deformation and field data are transferred and validated across geometric, thermal, thermo–mechanical, and electromagnetic layers. Specifically, geometry updating and solid–shell equivalence checks ensure structural consistency; temperature field mapping and thermal boundary verification maintain thermo–structural coherence; deformation-to-electromagnetic mapping with stress–strain verification secures mechanical–electrical correlation; and electromagnetic field–geometry consistency together with S-parameter validation (S11, S21) guarantees the accuracy of final signal integrity analysis.

This structured mapping and verification process ensures that deformation, thermal, and electromagnetic responses are physically correlated within an established error bound. The proposed unified error-bound mapping framework thus transforms multiphysics co-simulation from qualitative coupling into a quantitatively validated, reproducible methodology—offering a robust foundation for reliability assessment of Ruggedized Computers under complex service conditions.

2.2.3. Simplification Method for Multiscale Analysis of Heterogeneous Models

In the multiscale integrated analysis process, the key step is to identify critical local regions after the macroscopic-scale analysis and to perform equivalent simplification for these regions. In this study, an equivalence approach based on material properties is adopted, where a homogenized solid replaces the entire solder ball layer, possessing equivalent material parameters.

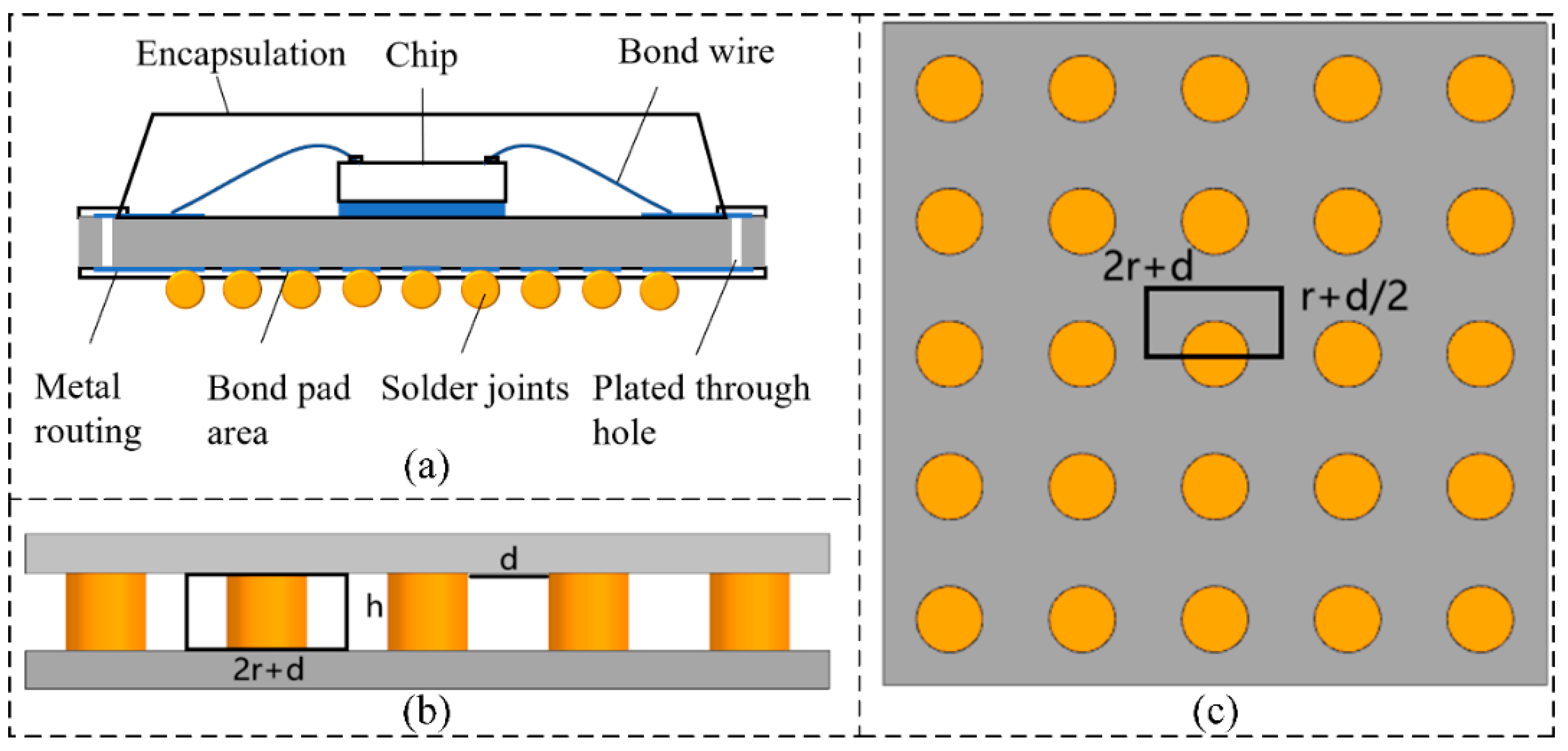

Figure 2a illustrates a schematic cross-sectional model of a flip-chip BGA. This section provides a detailed description of the material property equivalence theory for BGA solder balls, including the simplification methods for equivalent density, equivalent specific heat capacity, and equivalent thermal conductivity.

Assume that the chip solder ball is a cylinder with a base radius of

r, and that both the equivalent layer height and the solder ball height are ℎ. Subscripts

b and

e denote the solder ball and the equivalent layer, respectively, while subscript

a refers to the filler or air surrounding the solder ball.

V represents volume, and

A represents base area. The volume ratio can be expressed as follows:

where

is the volume fraction,

is the volume of the solder ball layer,

is the equivalent volume of the solder ball layer,

is the base area of the solder ball layer, and

is the equivalent base area of the solder ball layer. The equivalent volume is given by

.

- (1)

According to the principle of mass conservation, the density of the equivalent material is calculated using a volume-weighted averaging method and can be expressed as follows:

where

is the equivalent density of the solder ball layer,

is the equivalent mass of the solder ball layer,

and

are the masses of the surrounding filler and the solder ball, respectively, and

is the density of the filler. If the filler material (e.g., air) is neglected, the equivalent density simplifies to

.

- (2)

The derivation of the equivalent specific heat capacity is also based on the volume-weighted averaging method and can be expressed as follows:

where

is the equivalent specific heat capacity of the solder ball layer, and

and

are the specific heat capacities of the surrounding filler and the solder ball, respectively. If the filler material (e.g., air) is neglected, the equivalent specific heat capacity simplifies to

.

- (3)

Since the solder balls exhibit anisotropic distribution in both the in-plane and normal directions, the equivalent thermal conductivity must be considered separately for the normal and lateral directions. In the normal direction, the thermal conduction path of the solder balls can be simplified as a series model.

Figure 2b shows the normal equivalence schematic of the solder balls. Considering a subunit from the figure, with solder ball spacing

d, and assuming the thermal conductivity of the surrounding filler (or air) is

and that of the solder ball is

, the equivalent thermal conductivity in the normal direction can be expressed as follows:

If the filler material (e.g., air) is neglected, the equivalent thermal conductivity in the normal direction simplifies to .

In the lateral direction, the thermal conduction path of the solder balls can be simplified as a parallel model. The lateral equivalence of the solder balls is shown in

Figure 2c. The equivalent thermal conductivity in the lateral direction can be expressed as follows:

If the filler material (e.g., air) is neglected, the equivalent thermal conductivity in the lateral direction simplifies to

2.3. Multiscale Model of Ruggedized Computers

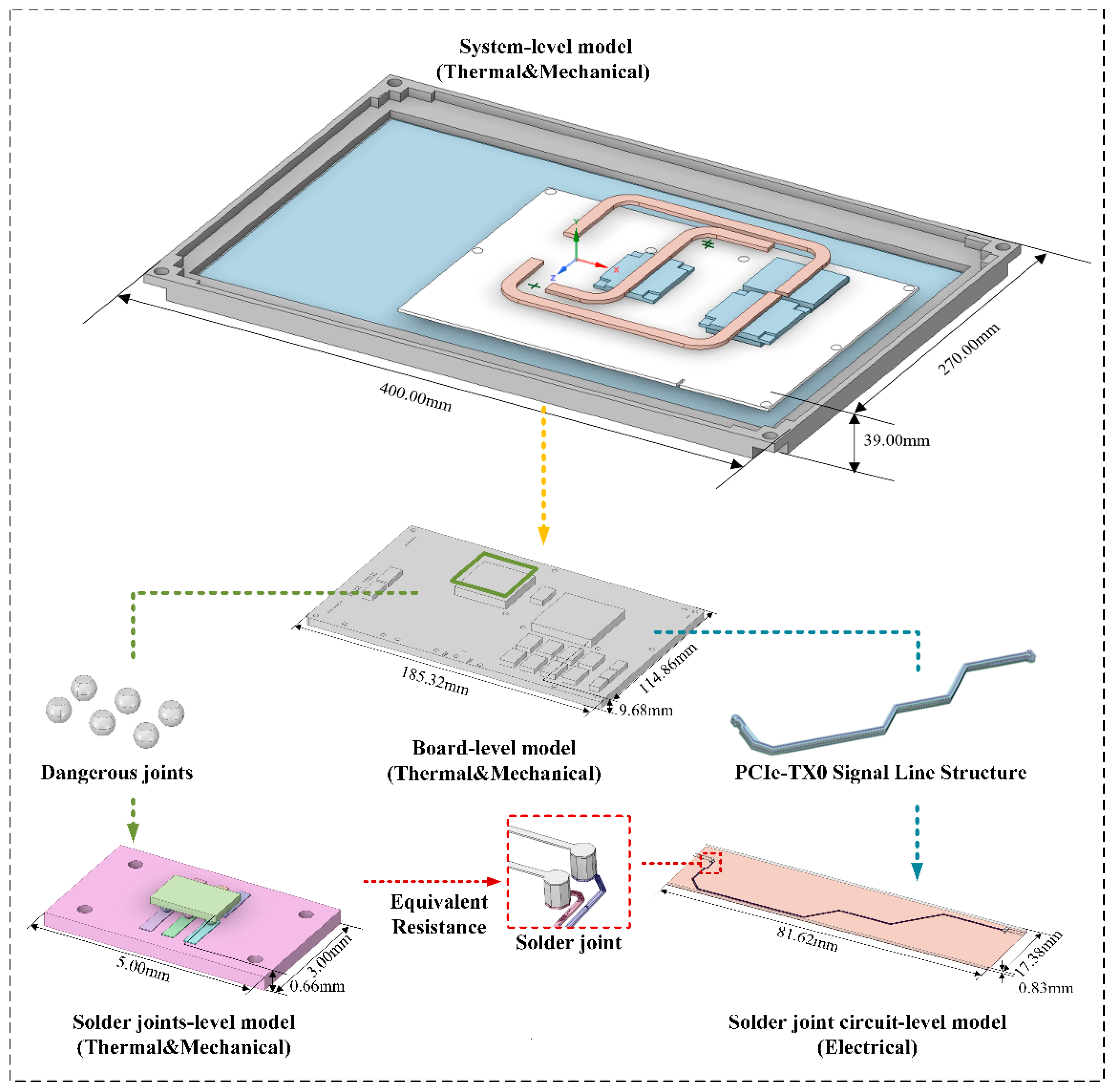

To verify the proposed efficient heterogeneous model coupling and multiscale modeling method, the ruggedized computer was selected as the research subject. Using parametric modeling techniques, a multiscale model of the ruggedized computer was constructed on the Ansys SpaceClaim platform, including the system-level model, the board-level model, the mesoscopic solder joint-level model, and the solder joint circuit-level model, as shown in

Figure 3. The system-level model adopts a sealed design that isolates the fan from the internal chassis. The simplified chassis model mainly consists of the display, motherboard, CPU, GPU, bridge chip, copper heat pipes, and aluminum heat sinks. The motherboard model is based on the LS3A5000 board. The mesoscopic solder joint model selects six critical solder joints from regions of high thermal stress concentration on the motherboard, with BGA solder balls of 0.5 mm diameter, 1 mm spacing, and 0.3 mm height. The solder joint–trace model specifically selects a pair of differential PCIe lines (PCIe_TX0_P/N) from the PCB file and constructs the corresponding connected chip solder joint model. The material properties of the models are listed in

Table 2 [

34,

35]. The temperature-dependent elastic modulus (

Y), Poisson’s ratio (

ν), and coefficient of thermal expansion (CTE) of Sn–3.0Ag–0.5Cu (wt.%) vary with temperature as shown in

Table 3. Considering that the melting point of SAC305 solder is approximately 217 °C, the thermal cycling range in this study (−55 °C to 150 °C) exceeds half of the melting temperature. It is imperative to account for the creep characteristics of the solder. In this context, the Anand viscoplastic unified model is selected to characterize the viscoplastic behavior of the solder.

Table 4 presents the nine pertinent parameters of the Anand viscoplastic unified model for Sn–3.0Ag–0.5Cu (wt.%).

The multi-level temperature cycling load is transmitted following the “chassis–motherboard–solder joint” hierarchical coupling principle, achieving multiscale correlation through stepwise mapping of thermal boundary conditions.

- (1)

System-Level Thermal Cycling Load

The complete chassis model transfers heat through natural convection and radiation. The natural convection heat transfer coefficient

h (W·m

−2·K

−1) is determined using the empirical correlation [

36] derived from the Rayleigh–Nusselt relation, as expressed in Equation (22). The detailed empirical correlations for natural convection are provided in

Appendix A. The coefficient

C = 1.31 W·m

−2·K

−4/3 is selected based on the correlation for natural convection over a vertical plate:

where

is the surface temperature and

is the ambient temperature.

Radiative heat transfer is calculated using the Stefan–Boltzmann law [

37], as expressed in Equation (23):

In Equation (23), the emissivity is taken as 0.85, and the Stefan–Boltzmann constant is 5.67 × 10−8 W/(m2·K4). The chip heat sources are applied with non-uniform distribution: the CPU center region has a heat flux density of 15 W/cm2, while the DDR memory is uniformly loaded with 4.2 W.

- (2)

Board-Level Thermal Cycling Load

The transient temperature field at the motherboard mounting surface is extracted from the chassis model and used as the input boundary condition, onto which the thermal cycling load is superimposed. The temperature loading function is expressed as follows:

where

Tchassis(

t) is the chassis temperature time history, and

Tstand(

t) represents the standard cyclic component. The detailed thermal cycling profile is shown in

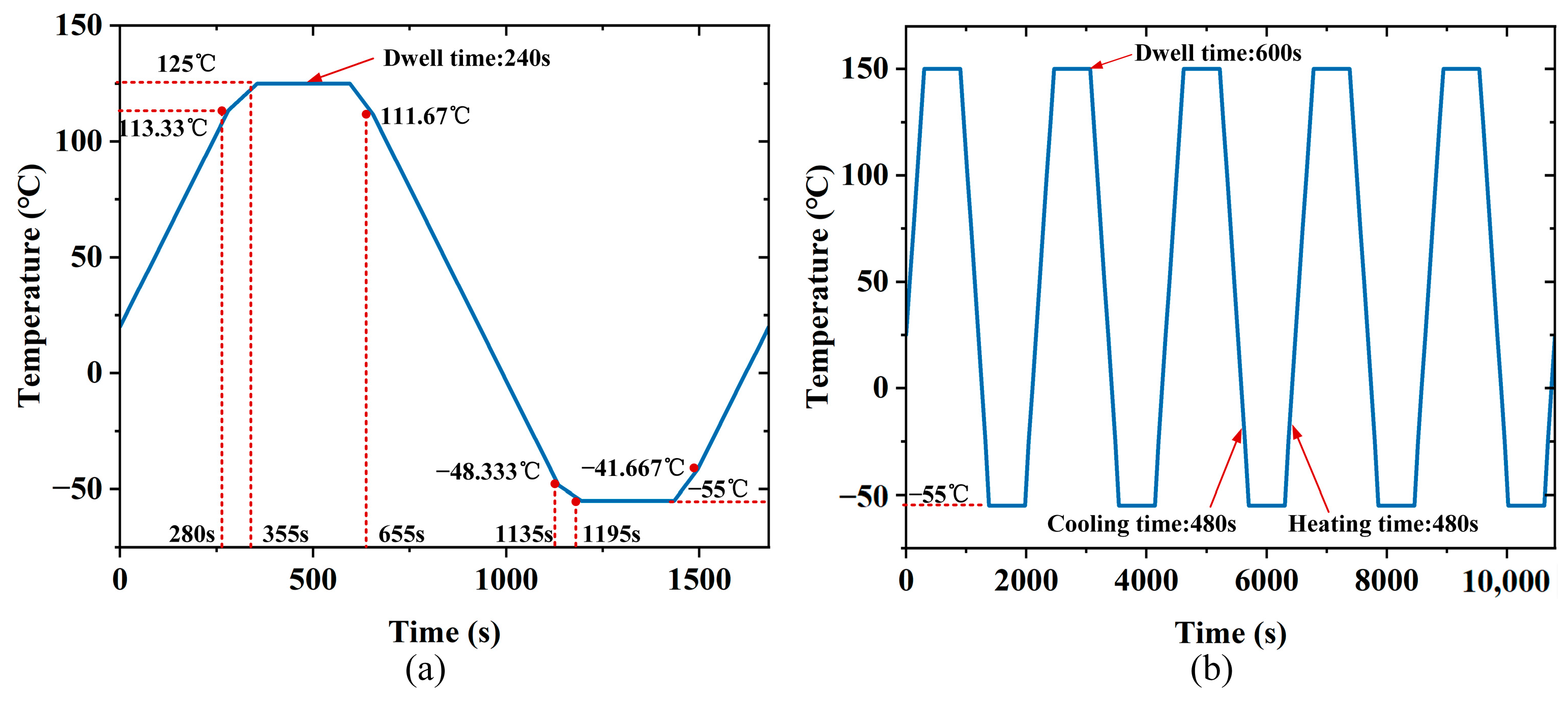

Figure 4a. The simulation starts at an ambient temperature of 20 °C. Each cycle consists of a 1200 s transition phase to capture the transient temperature change, followed by a 240 s dwell at 125 °C to represent high-temperature operating conditions, and a 240 s dwell at −55 °C to simulate thermal contraction under extreme cold conditions.

- (3)

Solder Joint–Trace Level Thermal Load Mapping

Using the Ansys sub-modeling technique, the motherboard-level temperature field was interpolated and mapped onto the mesoscopic solder joint model. To ensure consistency in boundary temperature transfer, a cubic spline interpolation algorithm was employed. To quantitatively evaluate the mapping accuracy, temperature data were sampled at corresponding nodes along critical component boundaries (GPU, PCIe connector, and DDR regions) in both the system-level and board-level models. The results show that the root-mean-square (RMS) error was 2 °C, confirming that the interpolation error remained within 2 °C. The fitted thermal cycling curve is shown in

Figure 4b.

- (4)

Mechanical Loads

Mechanical loads interact with the temperature field through sequential coupling. First, a transient thermomechanical analysis is performed, and the resulting temperature field is applied to the structural domain as thermal strain load. The resulting thermal deformation is used as the initial state, followed by the sequential application of random vibration and mechanical shock loads. A three-axis PSD vibration spectrum, as listed in

Table 5, is applied at the motherboard mounting holes, and a trailing peak sawtooth mechanical shock load, as listed in

Table 6, is applied on the six faces of the full system.

To overcome the limitations of analyzing a single solder ball, which cannot fully capture the system-level multi-physics coupling behavior, a multiscale integrated analysis method is proposed. First, the model is divided into four hierarchical levels according to the required analysis granularity. Second, methods for transferring data between mesh nodes at different scales are developed to ensure compatibility and consistency across the multiscale simulation process. Finally, based on performance evaluation requirements, a multi-level macro-to-mesoscopic simulation analysis is conducted to assess the thermo–mechanical–electrical coupled behavior of BGA solder joints under complex service environments, as illustrated in

Figure 5.

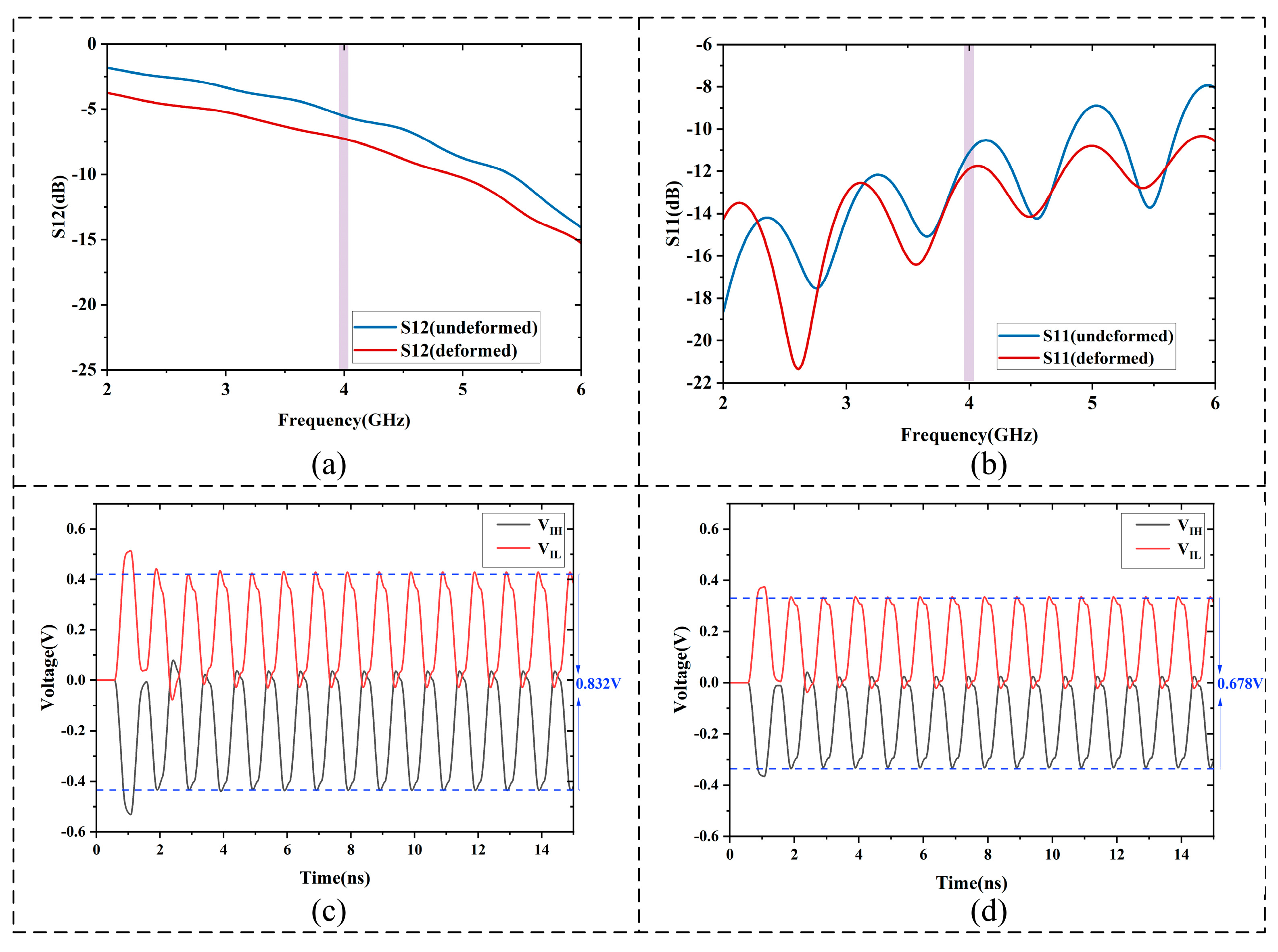

Model Validation

To verify the model correlation at 10 thermal cycles, a test platform was established as shown in

Figure 6a. The test system consists of a Root Complex, a Carrier Load Board (CLB), and a real-time oscilloscope. The PCIe CEM transmitter voltage test was performed using the compliance load board (CLB) connected to the system DUT through a 2-inch Tx trace, as illustrated in

Figure 6a.

Figure 6d,e compare the voltage waveforms at different ports before and after 10 thermal cycling: the peak-to-peak voltage of the differential signal at the receiver decreased from 0.832 V to 0.814 V, corresponding to a voltage drop (Δ

Vsim) of 0.018 V. Similarly,

Figure 6f,g show the oscilloscope-captured time-domain signals, where the peak-to-peak voltage decreased from 0.929 V to 0.913V, a drop of 0.016 V(Δ

Vexp) after 10 cycles.

The simulated voltage attenuation was compared with the experimental measurement, and the model accuracy was calculated using the voltage drop magnitudes (Δ

Vsim − Δ

Vexp), representing the relative error of the peak-to-peak differential voltage between simulation and experiment under 10 thermal cycles, where the reference channel is the PCIe differential receiver signal measured on the compliance load board (CLB) through a 50 Ω terminated coaxial channel.

where Δ

Vsim—voltage drop magnitude predicted by the numerical simulation, Δ

Vexp—voltage drop magnitude obtained from experimental measurement.

Using this definition, the model accuracy at 10 thermal cycles was calculated to be 88.89%. This result indicates that the multi-physics coupled model established in this work exhibits good accuracy.

5. Conclusions

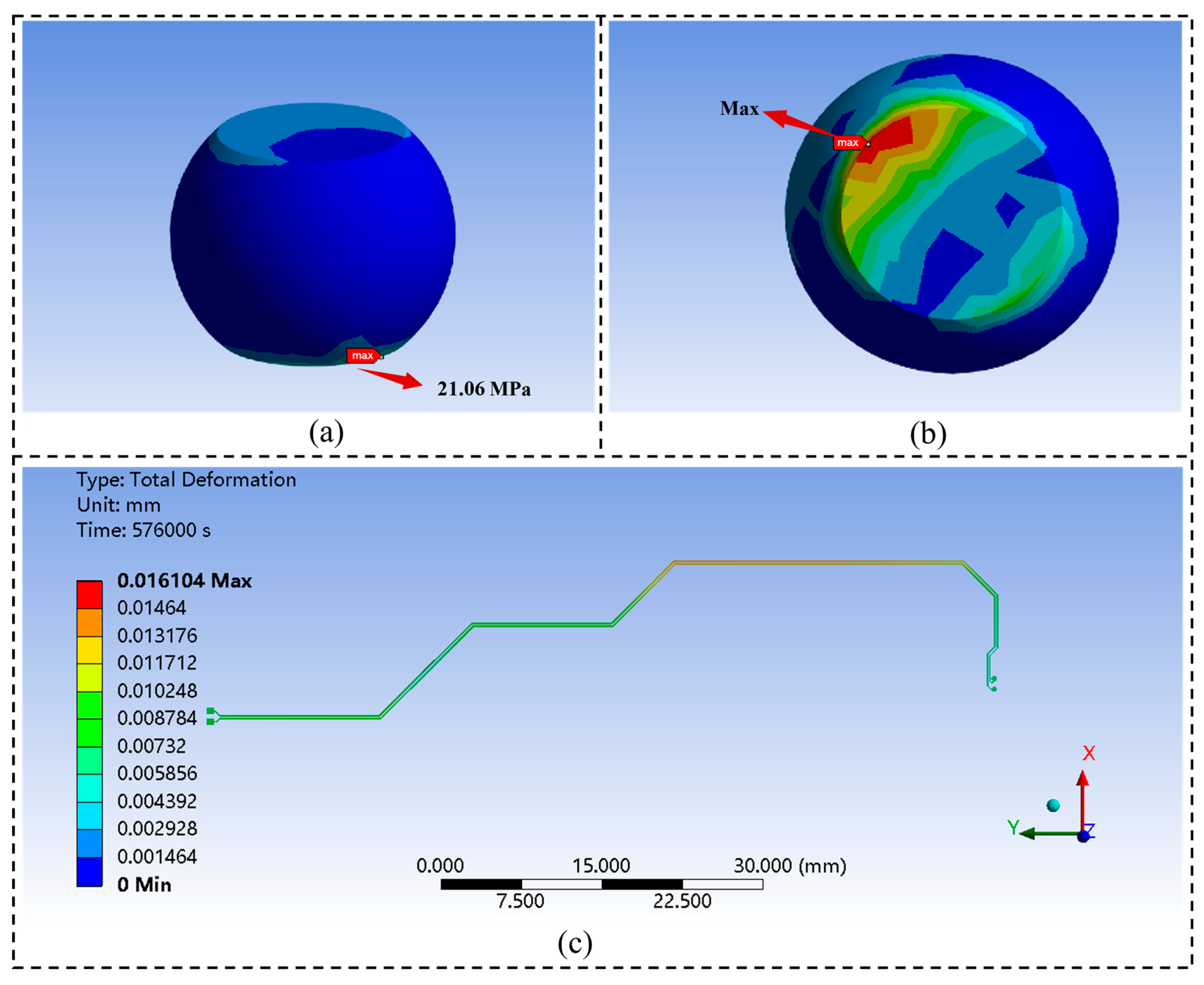

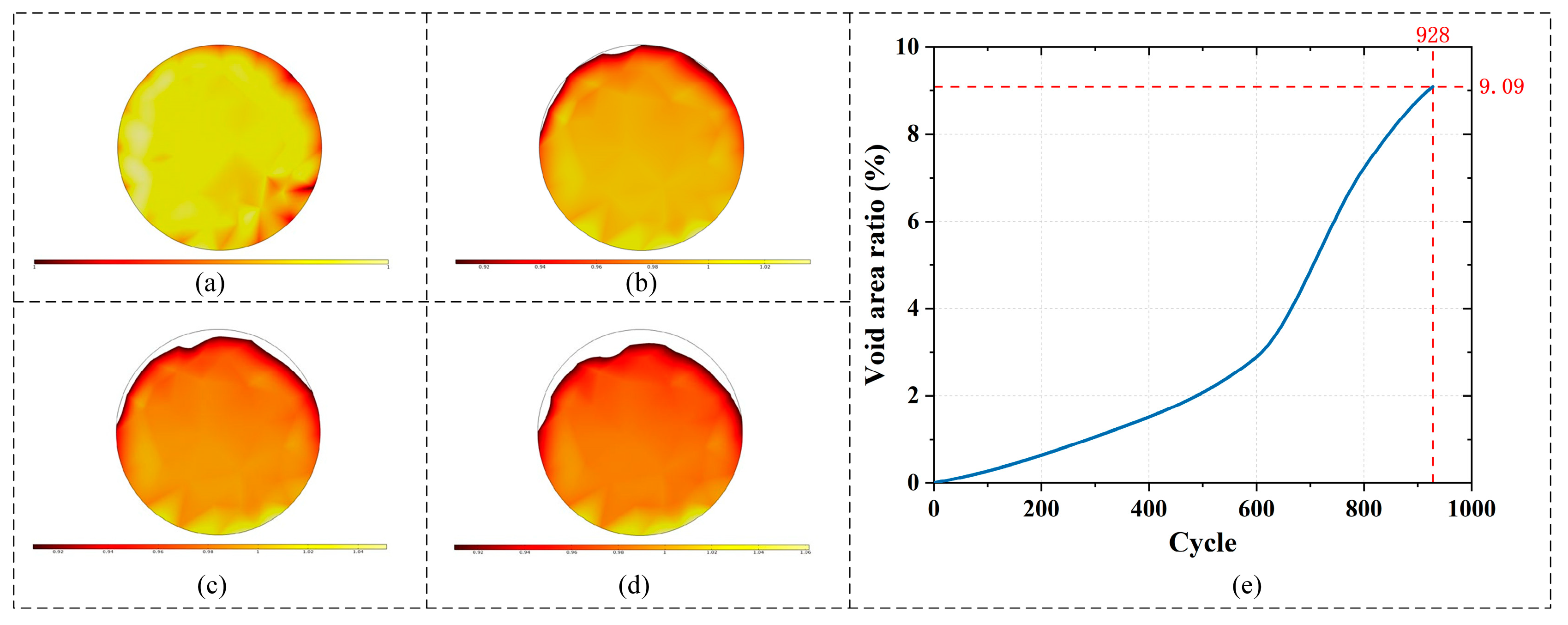

This study addresses the multi-physics coupling problems of solder joints in microelectronic systems of ruggedized computers under complex service environments and proposes a multiscale modeling and analysis method. A model correlation study under ten thermal cycling conditions demonstrated an accuracy of 88.89%, confirming the validity and applicability of the proposed model. The approach enables multi-level coupled investigations ranging from the full computer level, board level, and solder joint level to the solder joint–interconnect microstructure level. The results indicate that, within the microelectronic systems of ruggedized computers, solder joints generate thermal stress and deformation due to temperature rises, while the thermal field alters electrical conductivity, inducing electromigration and concentration evolution. These, in turn, couple with stress gradients to form thermo–electro–mechanical multi-physics effects. The coupling among thermal, electrical, and mechanical fields significantly aggravates the risk of electrical failure in the microelectronic systems of ruggedized computers. The critical solder joints exhibit equivalent stress concentration at the metal interconnection interface, with a maximum value of 191.51 MPa, accompanied by pronounced plastic strain accumulation. Meanwhile, PCIe high-speed interconnect experienced a maximum deformation of 16.104 μm and a voltage amplitude reduction of approximately 18.51% after 928 thermal cycles, exceeding the normal operating range. These findings provide reliable theoretical support and engineering references for the optimized design and reliability assessment of ruggedized computers. The proposed model is primarily applicable to thermal cycling environments ranging from −55 °C to 150 °C, high-frequency vibrations of approximately 405 Hz, and mechanical shock conditions of up to 40 g. However, environmental factors such as acoustic noise, dust contamination, and humid–thermal conditions were not considered in the current modeling framework. Future work will further consider environmental factors such as acoustic noise, dust contamination and thermo–hygroscopic coupling, to enhance the model’s applicability under more complex service conditions.