Abstract

In this study, the effects of switching on the two-dimensional electron gas (2-DEG) channel in an E-mode GaN-on-Si HEMT are investigated using a GS-065-004-1-L device that is commercially available for educational practice. A practical prototype with a reduced number of components is proposed, with empirical concepts used to explain its predictive performance when a coreless transformer is series-connected to the E-mode GaN-on-Si HEMT for switching-mode conduction. Conduction modes arising at the p-GaN/n-AlGaN/i-GaN heterojunction in accordance with specifications from the manufacturer’s datasheet were validated using a didactic physical-based model dependent on semiconductor parameters of gallium nitride (GaN). Test circuit-examined waveforms were analyzed, which confirmed that the switching conduction mode of the 2-DEG channel is dependent on physical parameters such as switching operating frequency, temperature, low-field electron mobility, and space charge capacitance.

1. Introduction

High-voltage GaN-on-Si transistors have been in development and the subject of intense research since 2015, when the first high-voltage solution was commercially released. These practical devices are based on a cascade configuration of a low-voltage Si-MOSFET in series connection with a high-voltage gallium nitride (GaN) MIS-HEMT, followed by enhancement-mode (E-mode) devices based on a p-doped GaN gate module for low-voltage GaN power transistors. In 2016, the first fully industrial qualified 600 V E-mode GaN power transistors were released by Panasonic and Infineon [1,2]. However, because GaN-based device technologies have been implemented with a standard silicon process to achieve economic balance, one of the biggest challenges when using GaN devices is their reliability [3].

Empirical methods have been established to understand how the formation of piezoelectric effects dependent on charge distribution can contribute to the presence of the conduction path in GaN HEMTs on a very thin (≤30 nm) sheet—called two-dimensional electron gas (2-DEG) in GaN-based devices—where donor states positively impact performance under high electric field conditions, inducing sheet charges at p-GaN/n-AlGaN and n-AlGaN/i-GaN interfaces [4,5]. Therefore, a simplified behavior model of switching effects on the 2-DEG channel is expected to encourage scholars who are researching switching-mode power circuits based on E-mode GaN-on-Si HEMTs, where mounting techniques are needed for long-term temperature cycles in real-world applications, and gate driver techniques with low impedance and high peak current are recommended for fast switching conduction [6]. To understand the physical behavior of a commercial E-mode GaN-based device, empirical concepts used to explain the performance of a test circuit are a valuable educational resource for undergraduate and graduate students.

It is well known that, although technology computer-aided design (TCAD) software packages for power circuit analysis can be a very useful tool for initial design, they are not a substitute for young professionals’ and experienced engineers’ understanding of the overall performance of GaN device-based circuits, because such packages provided by device manufacturers and researchers are usually commercially private and technologically protected. Consequently, to mitigate the lack of design skills and optimize reliability issues using E-mode GaN-on-Si HEMTs, a typical design process must usually begin with specifications for the circuit application, which can proceed based on previous silicon technology-based designs—including specific components and their tolerances—to achieve the best performance by evaluating some of their key physical parameters from a phenomenological viewpoint [7].

The remainder of this study is organized as follows. In Section 2, we provide general description of the experimental setup to present the effects of switching on the 2-DEG channel. In Section 3, we utilize a physics-based model focused on standard carrier conduction equations of silicon-based semiconductor devices for reducing the workload of parameter’s adjustment, and a test circuit and behavior analysis to examine how switching dependence of 2-DEG channel conduction in the commercial GS-065-004-1-L device occurs, particularly when it is driven at frequencies higher than 250 kHz using a coreless transformer in a test circuit. Conclusions about this work are presented in Section 4.

2. Experimental Procedure

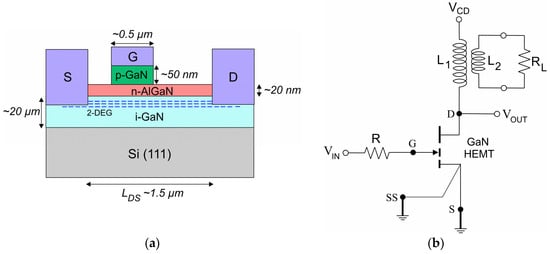

To understand how the effects of switching on the 2-DEG channel behave, an empirical study with accessible measurement instruments for the user is proposed. This study focuses on a physical-based model verified in a test circuit, where a commercial low-power GaN transistor from GaN Systems (Ottawa, ON, Canada) (with part number GS-065-004-1-L) is tested using a range of electrical specifications from the manufacturer’s datasheet. The dimensions for the commercial GS-065-004-1-L device (p-GaN gate structure) shown in Figure 1a comprises an i-GaN buffer, n-AlGaN barrier, p-GaN layer, and three electrodes—namely, drain, source, and gate—where the gate electrode is asymmetrically located at 1/5 LDS for low-power technology [8,9]. The test circuit in Figure 1b with a reduced number of components is proposed to understand how semiconductor parameters can influence switching effects in the commercial GS-065-004-1-L device.

Figure 1.

(a) Representation of the p-GaN gate structure of the commercial GS-065-004-1-L device; (b) schematic diagram of the test circuit for the experimental analysis.

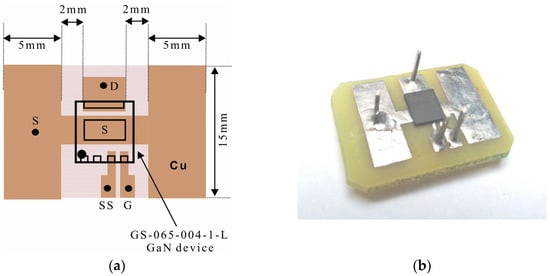

Although GaN-based devices behave differently to silicon MOSFETs because they can exhibit an average 2-DEG channel resistance during their turn-off time, they are designed to be cooled using the printed circuit board (PCB), where the source/thermal pad is internally connected [5,10]. Thus, to prevent thermal damage, the copper path on the PCB for distributing the gate drive signal was designed to be as short as possible, while copper paths to the source and drain signals were wider, as shown in Figure 2a. The device was mounted on 0.1 mm PCB thickness phenolic resin as the material, and the copper layer under the source/thermal pad was roughly 15 × 15 mm2, as shown in Figure 2b.

Figure 2.

(a) PCB layout and related sizes of the mounted GS-065-004-1-L device; (b) PCB used to experimentally test it.

3. Results and Discussion

3.1. Conduction Modes in the E-Mode GaN-on-Si HEMT

Conduction modes for GaN-based devices must be evaluated using semiconductor parameters (e.g., doping concentration, physical dimensions, and electrical characteristics) and well-known physical principles assembled in carrier conduction equations to study its effects with available mathematics software tools. This results in an educational model that could be useful for the predictive analysis of p-GaN/n-AlGaN/i-GaN heterojunctions. To theoretically analyze the conduction modes as a function of the physical parameters, useful specifications from the manufacturer’s datasheet are summarized in Table 1. Furthermore, semiconductor parameters for GaN at room temperature, as listed in Table 2 from data reported in the scientific literature, are taken into account to understand how conduction effects in the practical structure shown in Figure 1b can impact performance in switching-mode power electronics.

Table 1.

Specifications for commercial GS-065-004-1-L device.

Table 2.

Semiconductor parameters for GaN used to evaluate physics-based model [10,11].

Accordingly, to understand how the p-GaN/n-AlGaN heterojunction can affect 2-DEG channel conduction and transiently stimulate the n-AlGaN/i-GaN heterojunction for reliable conduction in an E-mode GaN-on-Si HEMT, standard equations for silicon devices governing static conduction modes can be established as follows.

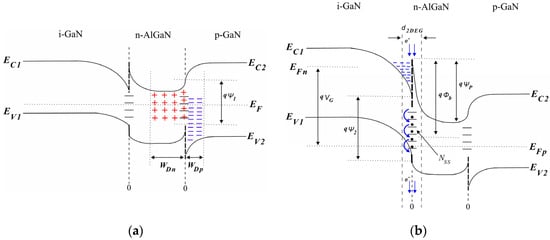

At the p-GaN/n-AlGaN heterojunction, where both sides of the heterojunction become the same material, it is supposed that the diffusion currents are similar to a regular p+-n junction and the carrier concentrations are relatively much higher inside the depletion region [12]. Therefore, a dipole layer is supported with the built-in potential,

and applied bias threshold voltage, where surface effects due to ionic charges can cause the formation of depletion regions

and

, giving rise to the high injection level that may occur under a relatively small forward bias condition, as shown in the energy band diagram in Figure 3a. The current/voltage characteristics are established using the following expression:

where k = 8.62 × 10−5 eVK−1 is the Boltzmann constant;

in degrees Kelvin, where TJ is the junction temperature in degrees Celsius for the analysis proposed in accordance with the manufacturer’s datasheet;

is a cross-section area for mobile carries across the p-GaN/n-AlGaN heterojunction;

the gate threshold voltage;

is the saturation current density which depends on

the intrinsic carrier concentration at room temperature; the carrier lifetime for holes is

and that for electrons is

; the diffusion length for holes is

and that for electrons is

; and the impurity concentration for the donor is

while that for the acceptor is

.

Figure 3.

Energy band diagram of the p-GaN/n-AlGaN/i-GaN heterojunction: (a) forward bias regime at n-AlGaN/p-GaN heterojunction; (b) high-injection regime at i-GaN/n-AlGaN interface under reverse bias condition.

For the n-AlGaN/i-GaN heterojunction, it can be supposed that the conduction mechanism is similar to that governed by thermionic emission where the electron’s conduction regime is influenced by the barrier height,

in which high-mobility electrons can be swept in a velocity saturation regime through the 2-DEG channel length [12,13]. Accordingly, the temperature-influenced current density at the n-AlGaN/i-GaN heterojunction can behave similarly to the metal/semiconductor junction given by

where

= 26.4 × 10−3 Acm−2K−2 is the pre-exponential factor (often expressed in terms of the effective Richardson constant for GaN material [11]),

is the built-in potential at the i-GaN/n-AlGaN interface,

is the cross-section area for mobile electrons across the 2-DEG channel, and

is the junction voltage at the gate-to-source heterojunction which obeys equation

[7,14], where the potential

is responsible for the trapping reduction and minimizing inactive surface donors at the n-AlGaN barrier of

(see Figure 1) as a function of the concentration of the ionized donor impurities

at the i-GaN/n-AlGaN interface, as shown in Figure 3b.

Because the i-GaN buffer is lightly doped, space charge effects independent of the electric field at the n-AlGaN/i-GaN heterojunction can be influenced by

, which is sufficient to fully enhance the conduction dominated by the velocity saturation regime. This is due to the presence of free carrier concentrations along the 2-DEG channel length when the gate voltage VG > VT, as shown by the energy band diagram in Figure 3b [8,12]. The drain current arising from flow inside the 2-DEG channel can be accurately given by

where

= 8.86 × 10−14 Fcm−1,

is the saturation velocity,

is the cross-section area across the 2-DEG channel length,

is the Debye length which defines the start-up for conduction limited by space charge effects inside the 2-DEG channel, and L = 1/2LDS, where

is initially computed using data from Table 1 and Table 2.

Semiconductor parameters for commercial devices are unrevealed by manufacturers and are very hard to determine. However, for the empirical adjustment of Equations (1)–(3), it is sufficient to know initial values of the manufacturer’s data summarized in Table 1 for the extraction of physical parameters

,

,

, and

to accurately reflect the characteristics of the commercial GS-065-004-1-L device. The values of the remaining physical parameters collected in Table 2 are adjusted in accordance with those reported in the scientific literature [10,11].

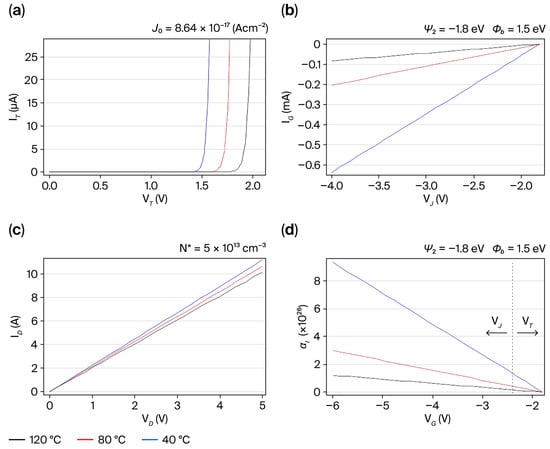

Based on the energy band diagram of Figure 3 for the p-GaN/n-AlGaN/i-GaN heterojunction, it is pertinent to understand how the junction temperature disturbs the threshold current, IT, as a function of forward threshold bias VT (

), as shown in Figure 3a, as well as gate current IG, as a function of reverse bias voltage VJ (

), together with ID (

) at the i-GaN/n-AlGaN interface, as shown in Figure 3b. Thus, because the maximum junction temperature for the commercial GS-065-004-1-L device is 150 °C, current/voltage curves are examined for three temperature values: 40 °C, 80 °C, and 120 °C.

The characteristics (IT–VT) depicted in Figure 4a show an initial bias current flow at the n-AlGaN/p-GaN heterojunction as a function of the built-in potential

, which is dependent on VT from 1.1 to 2.6 V, as declared in Table 1. In Figure 4b, for the characteristics (IG-VJ) under reverse bias at the i-GaN/n-AlGaN heterojunction, the current flow begins to increase in the gate-to-source region as a function of

in VJ ranging from −4 to −2 V when the drain current starts to flow across the drain-to-source distance, where the 2-DEG channel is created at a high injection level, as shown in the characteristics (ID-VD) presented in Figure 4c and governed by

and the built-in potential,

, dependent on VD from 0 to 5 V. Nevertheless, to determine how the switching conduction regime in the commercial GS-065-004-1-L device must be assisted, the evaluation of an injection level coefficient,

, as presented in Figure 4d, shows how dynamic conduction regime in the p-GaN/n-AlGaN/i-GaN heterojunction is dependent on the gate voltage, VG, as a pulse pattern applied in the gate electrode where, to achieve an enhanced injection level at the temperature lower than 80 °C, the VT/VG ratio must be lower than 0.3.

Figure 4.

Current/voltage characteristics as a function of the junction temperature and specifications from Table 1: (a) IT–VT curves; (b) IG–VJ curves; (c) ID–VD curves; (d)

–VG curves.

Because it is assumed that electrons travel near to the saturation velocity, transit time effects can enable the switching conduction mode through the dipole charge sheet (inside the 2-DEG channel) where current flow can lag behind the voltage based on the time-variant distribution of the electron’s density with respect to the ionized donor impurities’ concentration,

, similar to the space charge-limited conduction (SCLC) formalism for the commercial D-mode GaN-on-Si HEMT [7,12]. Therefore, the trapping of electrons occurs close to the n-AlGaN surface when they are displaced from the depleted i-GaN buffer at the i-GaN/n-AlGaN interface, as shown in the energy band diagram of Figure 3, exhibiting capacitance/frequency characteristics at the drain-to-source heterojunction through the gate width (LG~0.5 µm), establishing a connection between

and

according to

, assuming

. Substituting Equation (3) with

and

, taking into account that

, we can define a space charge capacitance equivalent to the depletion capacitance per unit area, given by

where

is the switching frequency;

is the drift velocity (average sound velocity), being proportional to the practical 2-DEG electron mobility,

, which is highly dependent on a lateral electric field

inside the gate-to-drain space, and caused by longitudinal and transverse strains at i-GaN buffer and scattering mechanisms at the n-AlGaN barrier [5,10,11].

Furthermore, the progressive reduction in

at the n-AlGaN/i-GaN interface and scattering mechanisms along the 2-DEG channel length can slightly impact electron mobility when the temperature rises, as shown in Figure 4c. This is because diffusion mechanisms in the drain-to-source space can occur due to the saturation of the surface state density, and the dependence of

on

rises during 2-DEG channel conduction.

3.2. Switching Dependence of Coreless Transformer

It is well known that the output power capability delivered by the coreless transformer to the load for square wave signal excitation [15] can be approximately defined from the stored energy density in the coreless transformer as follows:

where

is the core effective area in cm2; Bair is the air gap flux density;

is the switching frequency; and

is the current density of wires for low-power transformer windings operating at high frequencies, where surface eddy currents are supposed to reinforce the main current flow but oppose it toward the center of the winding [16]. As a result, the induced voltage at the secondary winding of the number of turns,

, could increase as

rises, being highly dependent on the primary inductance, L1, empirically given by

where

is the turn’s ratio and D is the duty cycle, defined as the turn-on time/full wave time ratio of a square wave signal with voltage supply

and average current flow

from the secondary winding.

Applying a pulse pattern of a short turn-on time at the gate, as deduced in Figure 4d, the power density transferred to the resistive load from the coreless transformer in Figure 1b could be improved [16,17]. Accordingly, as almost all magnetic energy is stored in air gaps and insulation between conductors, the current flowing around the windings’ surface must be taken into account in terms of skin effects to determine the distribution of Bair as a function of its depth,

, using an expression defined according to the empirical Faraday’s law and

definition, given by

where

is the number of turns for the primary winding of the coreless transformer,

is the core’s effective area in cm2,

is the permeability of vacuum, and

is the conductivity of the copper wire of the windings.

To achieve good power transfer from the input to the load and to circumvent power losses, optimized analysis has been commonly supported using TCAD software packages [14,18]. Nevertheless, instead of using these powerful computer programs for behavior analysis, from empirical Equations (5)–(7), governing the coreless transformer performance can be useful in manufacturing it, because power transfer from a phenomenological viewpoint as a function of physical parameters can be realized in specifications for a practical design, including dimensions, the number of primary and secondary turns, and their operating capabilities at high switching frequencies when series-connected to the depletion capacitance deduced from Equation (4) to understand how GaN-based devices must be operated in the real world and empirically model the drain-to-source heterojunction behavior of the commercial GS-065-004-1-L device intended to be operated in low-power electronics applications. Here, in a theoretical design for the test circuit in Figure 1b, operating specifications such as VCD = 100 V, D = 0.3, 100 µH < L1 < 400 µH, AE = 1 cm2, and n = 5 are assumed to ensure that a coreless transformer could be reliably developed [19]. The results in Figure 5a–c were computed using the MATHEMATICA 5 software to demonstrate the feasibility of the coreless transformer and space charge capacitance as a function of the switching frequency,

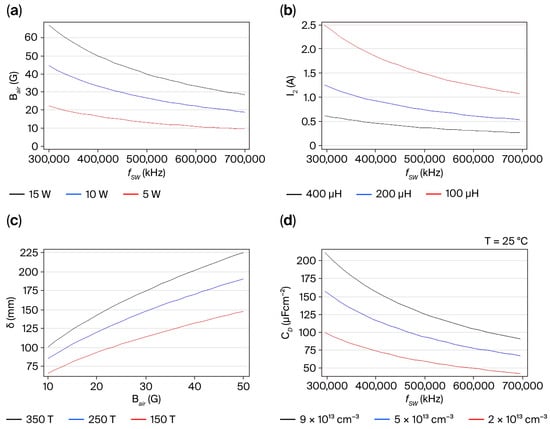

, in the range from 300 to 700 kHz using Equation (4), as shown in Figure 5d at room temperature.

Figure 5.

Predictive analysis of the coreless transformer performance at high-frequency switching conduction: (a) Bair–fSW curves; (b) I2–fSW curves; (c) δ–Bair curves; (d) capacitance/frequency characteristics for commercial GS-065-004-1-L device.

Figure 5a confirms that Bair increases when the power capability rises but, when using an

higher than 200 µH, as shown in Figure 5b, the

at the secondary winding might decrease at switching frequencies higher than 350 kHz. However, when the skin depth is taken into account, as shown in Figure 5c, where

is higher than 150 T (turns), the induced voltage at

inside the coreless transformer in Figure 1b might be creased within an acceptable Bair level. Hence, it is theoretically confirmed that the coreless transformer manufactured using conventional winding techniques may be applied for switching-mode power circuits at high frequencies, although the winding temperature should be lower than 50 °C for copper wires [18,19]. The depletion capacitance CD decreases as switching frequency rises, as shown in Figure 5d, but its variation as a function of the electron density trapped at three different N* concentrations, 2 × 1013 cm3, 5 × 1013 cm−3, and 9 × 1013 cm−3, is examined.

This confirmed that stable operations can be achieved only at a low injection level (N* = 2 × 1013 cm−3) to ensure an off-state condition at the VOUT in Figure 1b (though lower than ½ VDS; see Table 1), and quasi-resonance phenomena, observed with stored magnetic energy at L1 and stored electric energy inside the 2-DEG channel, can result in negligible electrical breakdown effects at switching frequencies higher than 300 kHz.

3.3. Analysis of Test Circuit

In accordance with the theoretical results in Figure 5, the test circuit in Figure 1b was built and its performance was experimentally evaluated by connecting a pulse pattern of the positive square-wave signal with D = 0.25 to VIN, where a series resistor R = 10 Ω was connected on the gate electrode. A coreless transformer series-connected to the drain electrode was built whose specifications are N1 = 200 T (L1~250 µH) of 26 AWG wire, N2 = 40 T of 22 AWG wire, AE~1 cm2. The load resistor RL = 26.6 Ω (small incandescent lamp for automobile application) was used. The input voltage, VIN, and output voltage, VOUT, waveforms were measured using a digital storage oscilloscope (Tektronix (Beaverton, OR, USA), TDS1012C 100 MHz) to determine the physical effects of switching conduction on the 2-DEG channel in the commercial GS-065-004-1-L device.

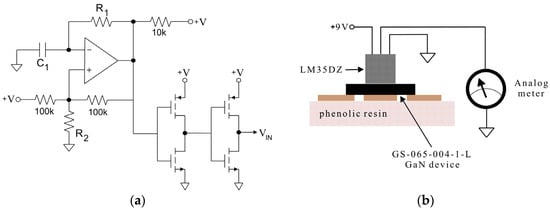

A typical driver circuit for the switching performance of GaN devices must comprise one comparator with a programmable turn-on time [20], where the resistor R2 can be used to adjust D in the range of 10 to 30%, and two CMOS logic inverter circuits, as shown in Figure 6a, where the capacitor C1 and resistor R1 are both used to adjust the chosen switching frequency. Because the driver circuit used for high-frequency operation requires a bias voltage (VGS = 6 V) at the gate-to-source heterojunction to ensure stable performance, the blocks specified in Figure 6a are integrated inside the 7555 timer circuit, which was implemented to provide signals, VIN, in the test circuit (see Figure 1b) for experimental analysis.

Figure 6.

(a) Diagram of the driver circuit to build the pulse pattern for switching conduction; (b) basic temperature sensing.

The precision integrated-circuit temperature sensor (type LM35DZ; Texas Instruments (Kuala Lumpur, Malaysia)) packaged in TO-92 plastic and designed for a full −55 °C to 150 °C range was chosen to evaluate heat dissipation. The test setup is shown in Figure 6b. It was assembled ensuring that the LM35DZ was as close as possible to the device surface soldered on the PCB and, due to the linear +10 mV per °C scale factor in the LM35DZ, it was easily applied to measure voltage linearly at its output pad using an analog meter.

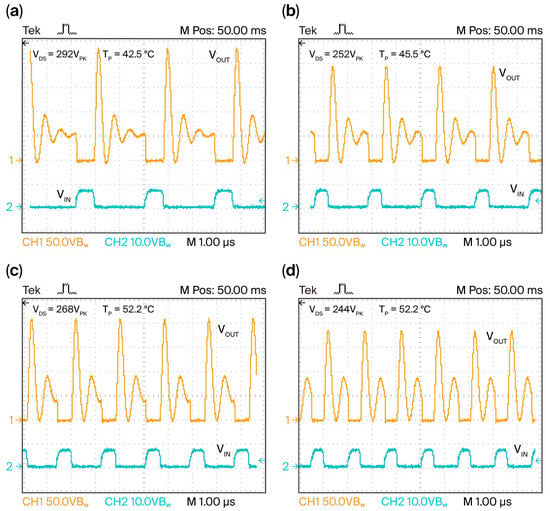

The experimental waveforms displayed in Figure 7a–d show how the commercial GS-065-004-1-L device behaves when the square wave signal with VIN = 6 V and

is in the range of 300 to 700 kHz; moreover, to avoid premature damage, VCD = 60 V was chosen for the test circuit shown in Figure 1b to satisfy acceptable output power capability, POUT, from Figure 5a and junction temperature, TJ, lower than 80 °C from Figure 4c; therefore, an equivalent series RON-L1-CD circuit was identified, where two voltage peaks in the VOUT signals are observed; the first surge peak is shorter in duration, which is related to the transient behavior of the series RON-L1 circuit where stored magnetic energy at L1 is fixed on the CD of the drain-to-source heterojunction and the second lower peak of the increasing width in time corresponds to the stored electric energy in the space charge capacitance, CD, with 60 V in magnitude. This behaves similarly to the series L1-CD quasi-resonant circuit due to the oscillating exchange energy between L1 and CD during the off-state, as shown in Figure 7.

Figure 7.

Input and output waveforms under four switching frequencies: (a) 350 kHz; (b) 450 kHz; (c) 550 kHz; (d) 650 kHz.

The test circuit’s performance results are as follows: At

= 350 kHz, an oscillating phenomenon is observed at the second peak with a negligible damping effect, but when

= 450 kHz, the oscillating phenomenon increases while the critical damping effect starts to become comparable to the first peak magnitude, resulting in deficient stored magnetic energy at L1 and lower induced voltage to the RL from the coreless transformer. Furthermore, the switching conduction mode was observed at

= 550 kHz and

= 650 kHz, where the oscillating event is more negligible, but there is still stored magnetic energy at L1 in the test circuit.

It was observed that the magnitude of the surge peak, VDS, decreases as the switching frequency increases, which means that the frequency response of the test circuit verified in Figure 7 is governed by resonance phenomena between L1 and CD at the commercial GS-065-004-1-L device and is strongly dependent on the electrical breakdown and strain effects of i-GaN buffer. This is because the turn-off protection (freewheeling diodes and snubber networks) in the test circuit is missing [19,21], but to retain the intention of the reduced number of components, its test circuit was securely operated at VCD < 100 V and the drain-to-source junction operated at VDS < 300 V, as confirmed in Figure 7.

Because reactivation of flux residues from no-clean soldering paste may cause unwanted conduction paths in GaN devices, scattering mechanisms on the surface of the n-AlGaN barrier under switching conditions as a function of the TJ can impact 2-DEG channel conduction [10,22]; therefore, it is aimed to understand how heat dissipation in the source pad on the bottom side of the commercial GS-065-004-1-L device behaves when the device package temperature, TP, remains below 100 °C during cooling cycles. The TP was measured as indicated by the experimental results in Figure 7, showing how the temperature dependence of the 2-DEG channel changed when TP increased from 40 to 55 °C and

increased, while the damping effects in the wide peak of lower magnitude became negligible, as the oscillating frequency of the equivalent series RON-L1-CD circuit began to be equal to the switching frequency of the pulse pattern applied to the gate. This suggests that critical strains due to the lattice and thermal expansion coefficient mismatches at the p-GaN/n-AlGaN/i-GaN heterojunction did not contribute to the presence of the surface donor states at the i-GaN/n-AlGaN interface based on anomalous piezoelectric effects [5,10,14] and the non-uniform distribution of the electric field peaks along the 2-DEG channel length [22].

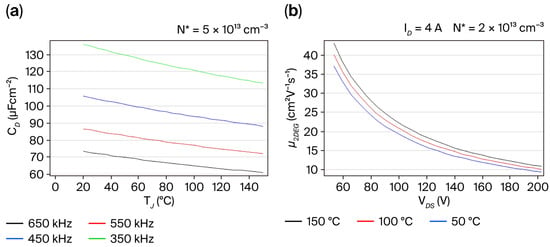

To know how the temperature-dependent dynamic conduction in the 2-DEG channel behaves, a theoretical analysis was evaluated for temperatures ranging from 25 °C to 150 °C, where the commercial GS-0D65-004-1-L device must operate reliably. Figure 8a shows curves describing how the depletion capacitance,

, from Equation (4) acts as a function of TJ for the four examined switching frequencies, providing useful confirmation of the charge fluctuations in the graphs in Figure 7, where

gradually reduces as TJ increases at a medium-ionized impurity level (N* = 5 × 1013 cm−3). However, low-field electron mobility,

, when

from Equation (3), results in VDS and TJ dependence of

= 1.5 eV under a low-ionized impurity level (N* = 2 × 1013 cm−3), whereas for the three different temperatures, namely, 50 °C, 100 °C, and 150 °C, shown in Figure 8b, it was found that

rapidly reduces as VDS increases, although it slightly decreases as TJ rises. For the empirical adjustment of Equation (3) describing

as a function of the VDS and TJ, the average values of

and

were used to accurately reflect the tendency in the curves of Figure 8b for the commercial GS-065-004-1-L device.

Figure 8.

Temperature dependence of conduction mode in 2-DEG channel for E-mode GaN-on-Si HEMT: (a) CD–TJ curves; (b) µ2DEG–VDS curves.

The above-mentioned results indicate that CD ≤ 100 µFcm−2 and

≥ 450 kHz, as well as

≥ 10 cm2 V−1 s−1, allowing us to provide a stable conduction mode with a surge VDS peak magnitude lower than 350 V and TJ < 100 °C in accordance with the current/voltage characteristics in Figure 4. The examined results in Figure 7 and predictive analysis in Figure 8 confirm the semiconductor parameters’ dependence of

,

,

,

, and

in the commercial GS-065-004-1-L device.

Furthermore, the curves in Figure 8 confirm that an ionization level, N*, between 2 × 1013 and 5 × 1013 cm−3 can be responsible for the stable conduction mode of the E-mode GaN-on-Si HEMT when switching conduction in the 2-DEG channel conforms to N*d2DEG >> NSS, but its package temperature can increase in a runaway manner above 150 °C generating conductive paths during turn-off time which occur between the drain and Si (111) substrate, as well as between the i-GaN/n-AlGaN interface and Si (111) substrate, which would presumably be responsible for unfavorable transient changes in the occupation of interface states determined by NSS, as shown in the energy band diagram in Figure 3b, leading to time-dependent breakdown effects as Si (111) is a material with 10 times lower

compared to GaN [10,18,22].

4. Conclusions

This research is focused on the effects of switching on the 2-DEG channel of an E-mode GaN-on-Si HEMT to understand how semiconductor parameter-dependent conduction modes can be influenced. Firstly, fine tuning of the current/voltage curves was performed using geometric dimensions

,

, and

. Secondly, a physical parameter-based test circuit was proposed and built within a coreless transformer series-connected to the drain-to-source junction of a commercial GS-065-004-1-L device. Using empirical equations and a simple experiment, reliable performance was demonstrated with a voltage supply lower than 100 V and switching frequencies higher than 300 kHz, validating acceptable heat dissipation in the commercial GS-065-004-1-L device during switching-mode conduction. Based on a didactic physical-based model, this investigation offers a suitable means for behavior analysis and further research to both students and experienced specialists who may face challenges when transitioning to GaN-based devices.

Funding

This research received no external funding, and the APC was funded by the author.

Data Availability Statement

All of the data are available in the manuscript. Ultimately, the intention of the author is to encourage scholars to explore new empirical research routes by using similar methodologies to those documented here.

Acknowledgments

I would like to acknowledge to the engineers Omar David Rivera-Reyes and Ángel Ismael Velázquez-López for their valuable expertise in designing the PCB circuits and technical support.

Conflicts of Interest

The author declares no conflicts of interest.

References

- Jones, E.A.; Wang, F.F.; Costinett, D. Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 707–719. [Google Scholar] [CrossRef]

- Zhong, Y.; Zhang, J.; Wu, S.; Jia, L.; Yang, X.; Liu, Y.; Zhang, Y.; Sun, Q.Y. A review on the GaN-on-Si power electronic devices. Fund. Res. 2022, 2, 462–475. [Google Scholar] [CrossRef] [PubMed]

- Ikeda, N.; Niiyama, Y.; Kambayashi, H.; Sato, Y.; Nomura, T.; Kato, S.; Yoshida, S. GaN power transistor on Si substrates for switching applications. Proc. IEEE 2010, 98, 1151–1161. [Google Scholar] [CrossRef]

- Meneghini, M.; Hilt, O.; Wuerfl, J.; Meneghesso, G. Technology and reliability of normally-off GaN HEMTs with p-type gate. Energies 2017, 10, 153. [Google Scholar] [CrossRef]

- Islam, N.; Packeer Mohamed, M.-F.; Jalaludin Khan, M.-F.-A.; Falina, S.; Kawarada, H.; Syamsul, M. Reliability, Applications and Challenges of GaN HEMT Technology for Modern Power Devices: A Review. Crystals 2022, 12, 1581. [Google Scholar] [CrossRef]

- Lim, S.; Otten, D.M.; Perreault, D.-J. New AC-DC Power Factor Correction Architecture Suitable for High-Frequency Operation. IEEE Trans. Power Electron. 2016, 31, 2937–2949. [Google Scholar] [CrossRef]

- Baca-Arroyo, R. Semiconductor parameters-depended dynamic behavior in commercial depletion-mode GaN on Si HEMT. e-Prime Adv. Electr. Eng. Electron. Energy 2025, 11, 100954. [Google Scholar] [CrossRef]

- Bhat, Z.; Ahsan, S.-A. A Physics-Based Analytical Model for p-GaN HMET. IEEE Trans. Electron. Devices 2024, 71, 6544–6551. [Google Scholar] [CrossRef]

- Wei, J.; Tang, G.; Xie, R.; Chen, K.-J. GaN power IC technology on p-GaN gate HEMT platform. JPN J. Appl. Phys. 2020, 59, SG0801. [Google Scholar] [CrossRef]

- Amano, H.; Baines, Y.; Beam, E.; Borga, M.; Bouchet, T.; Chalker, P.R.; Charles, M.; Chen, K.J.; Chowdhury, N.; Chu, R.J. The 2018 GaN power electronics roadmap. J. Phys. D Appl. Phys. 2018, 51, 163001. [Google Scholar] [CrossRef]

- Pearton, S.; Ren, F.; Zhang, A.; Lee, K.; Reports, E.R. Fabrication and performance of GaN electronic devices. Mater. Sci. Eng. R. 2000, 30, 55–212. [Google Scholar] [CrossRef]

- Sze, M.S.; Ng, K.K. Physics of Semiconductor Devices, 3rd ed.; John Wiley & Sons, Inc.: New York, NY, USA, 2007; pp. 28–50, 124–129, 401–407. [Google Scholar]

- Luo, H.; Hu, W.; Guo, Y. On large-signal modeling of GaN HEMTs: Past, development and future. Chip 2023, 2, 100052. [Google Scholar] [CrossRef]

- Vigneshwara-Raja, P.; Nallatamby, J.-C.; DasGupta, N.; DasGupta, A. Trapping effects on AlGaN/GaN HEMT characteristics. Solid-State Electron. 2021, 176, 107929. [Google Scholar] [CrossRef]

- Chryssis, G. High-Frequency Switching Power Supplies: Theory and Design, 2nd ed.; McGraw-Hill Publishing Company: Columbus, OH, USA, 1989; pp. 109–133. [Google Scholar]

- Chen, M.; Araghchini, M.; Afridi, K.-K.; Lang, J.-H.; Sullian, C.-R.; Perreault, D.-J. A Systematic Approach to Modeling Impedances and Current Distribution in Planar Magnetics. IEEE Trans. Power Electron. 2016, 31, 560–580. [Google Scholar] [CrossRef]

- Gattozzi, A.-L.; Pappas, J.-A. Circuits for Protecting and Triggering SCRs in High Power Converters. IEEE Trans. Magn. 2003, 39, 414–417. [Google Scholar] [CrossRef]

- Sun, S.; Xie, X.; Zhang, P.; Zhao, Z.; Wei, J.; Luo, X. Improvement of single event transients’ effect for a novel AlGaN/GaN HEMT with enhanced breakdown voltage. J. Sci. Adv. Mater. Devices 2024, 9, 100692. [Google Scholar] [CrossRef]

- Park, C.-W.; Han, S.-K. Analysis and design of an integrated magnetics planar transformer for high power density LLC resonant converter. IEEE Access 2021, 9, 499–511. [Google Scholar] [CrossRef]

- Sedra, A.S.; Smith, K.C. Microelectronics Circuits, 5th ed.; Oxford University Press Inc.: New York, NY, USA, 2004; pp. 1042–1090. [Google Scholar]

- Rashid, M.H. Power Electronics: Devices, Circuits, and Applications, 4th ed.; Pearson Education: Courier Westford, MA, USA, USA, 2014; pp. 931–955. [Google Scholar]

- Hein, L.; Goller, M.; Li, G.; Losner, M.; Lutz, J.; Basler, T. Investigation on the high temperature behaviour of p-GaN HEMTs by different temperature sensitive electrical parameters. Power Electron. Devices Compon. 2025, 12, 100103. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).