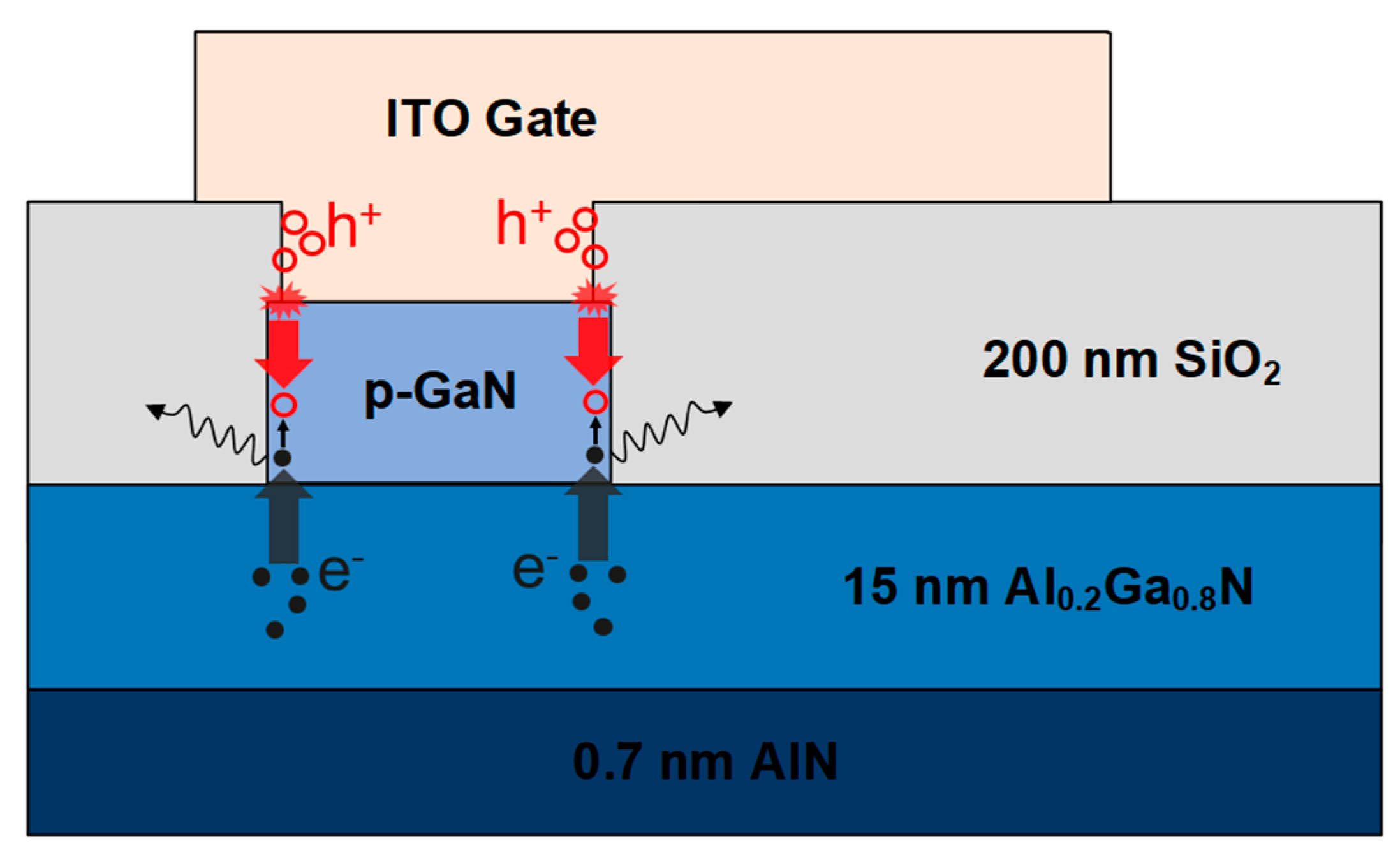

Investigating the Failure Mechanism of p-GaN Gate HEMTs under High Power Stress with a Transparent ITO Gate

Abstract

1. Introduction

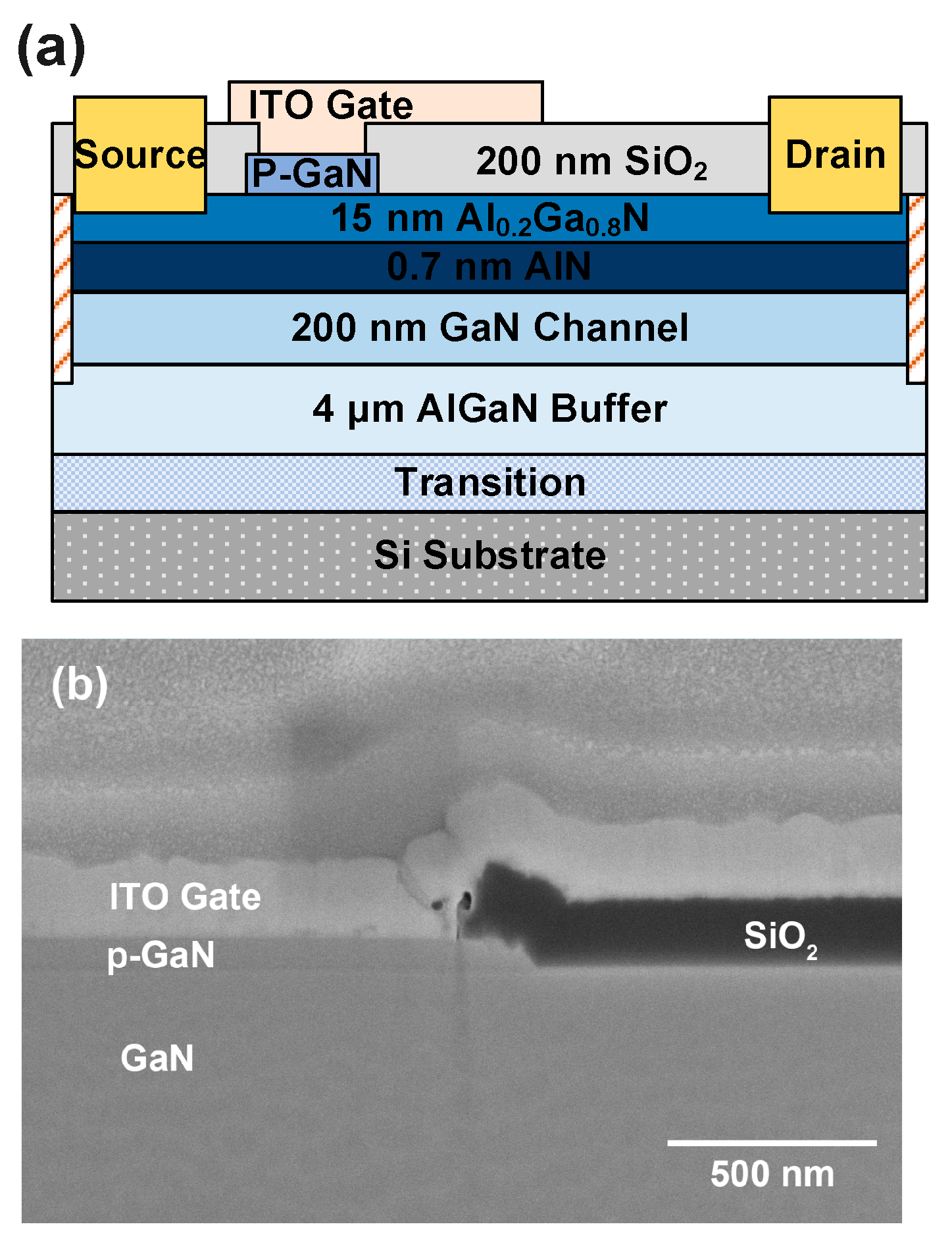

2. Materials and Methods

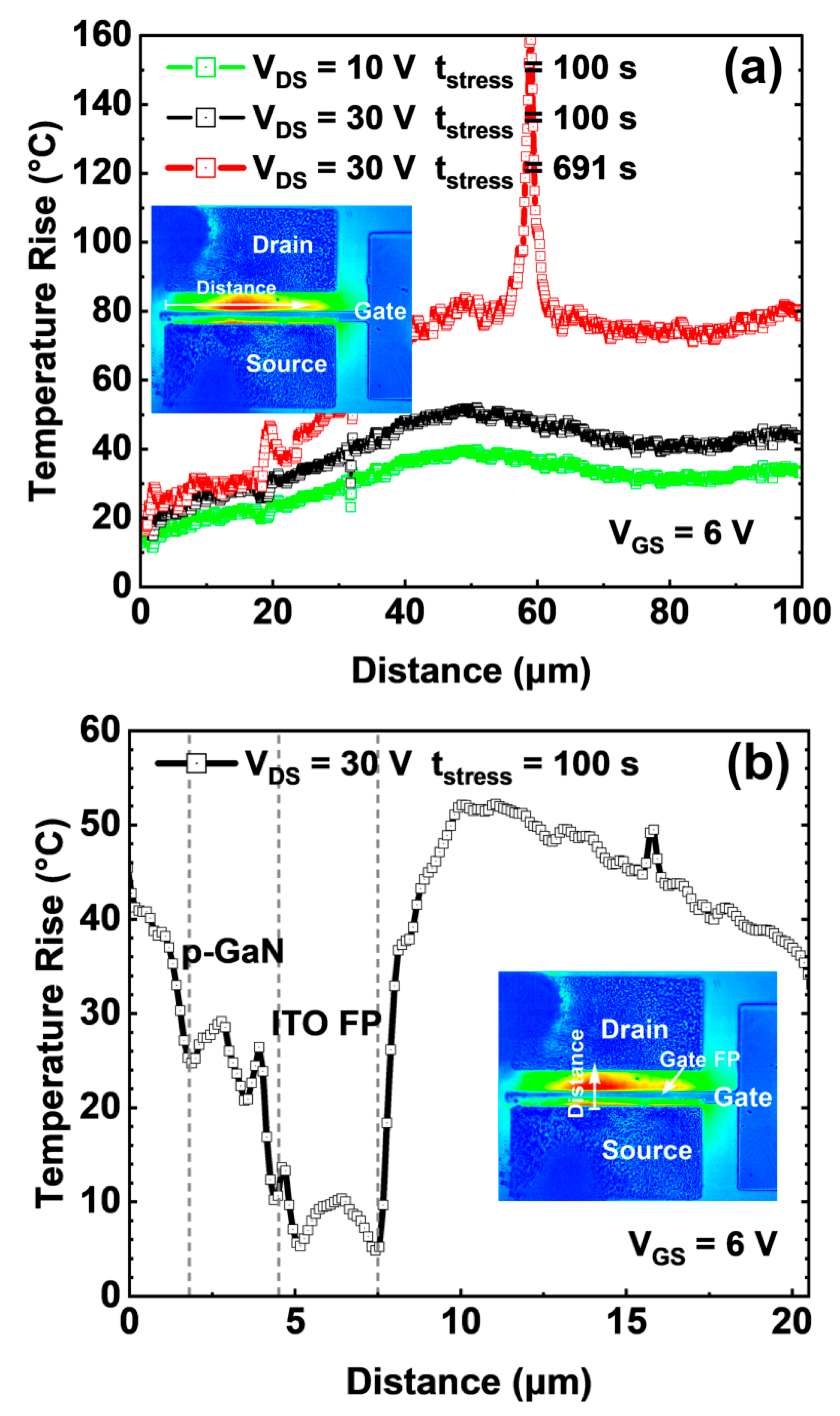

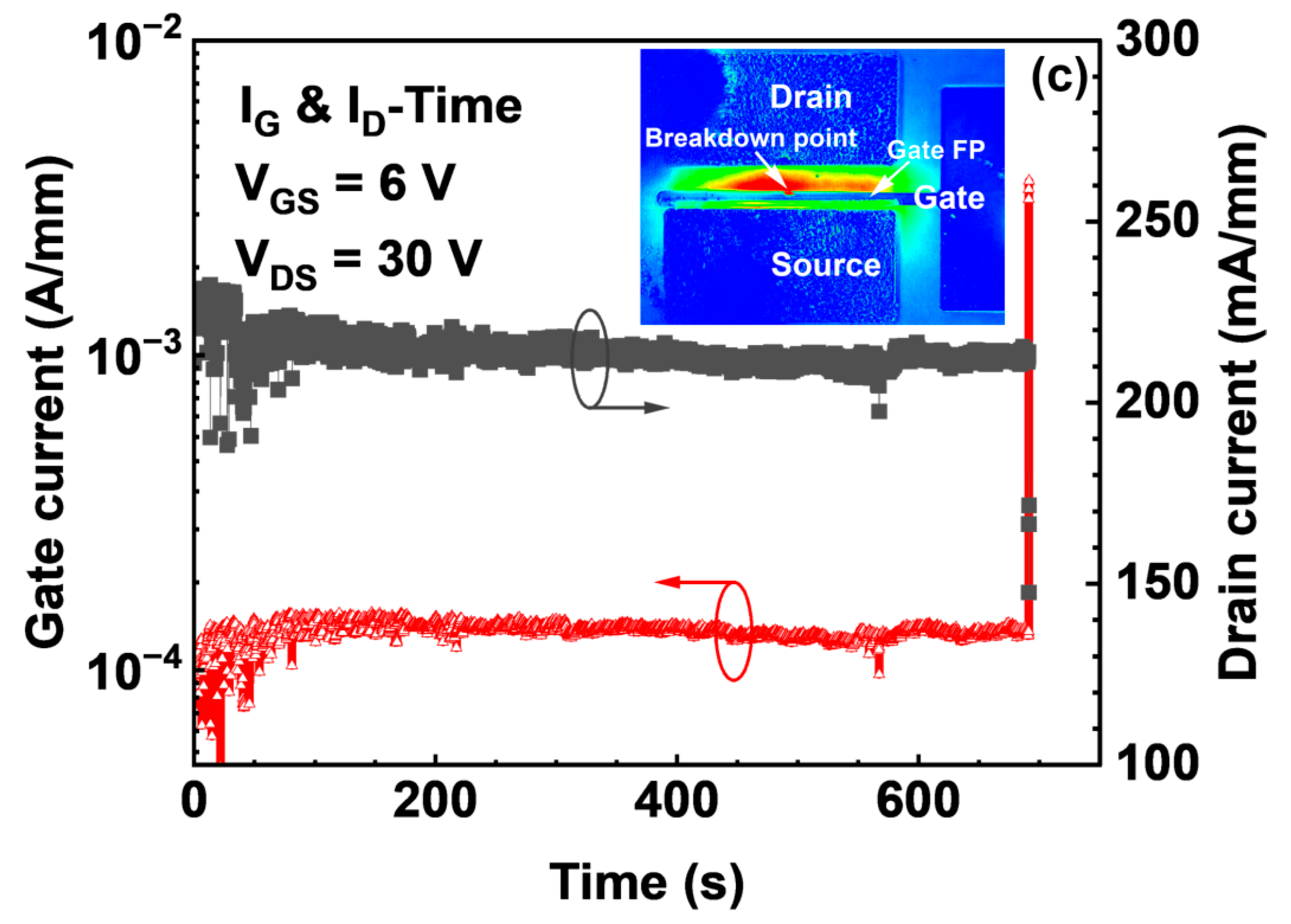

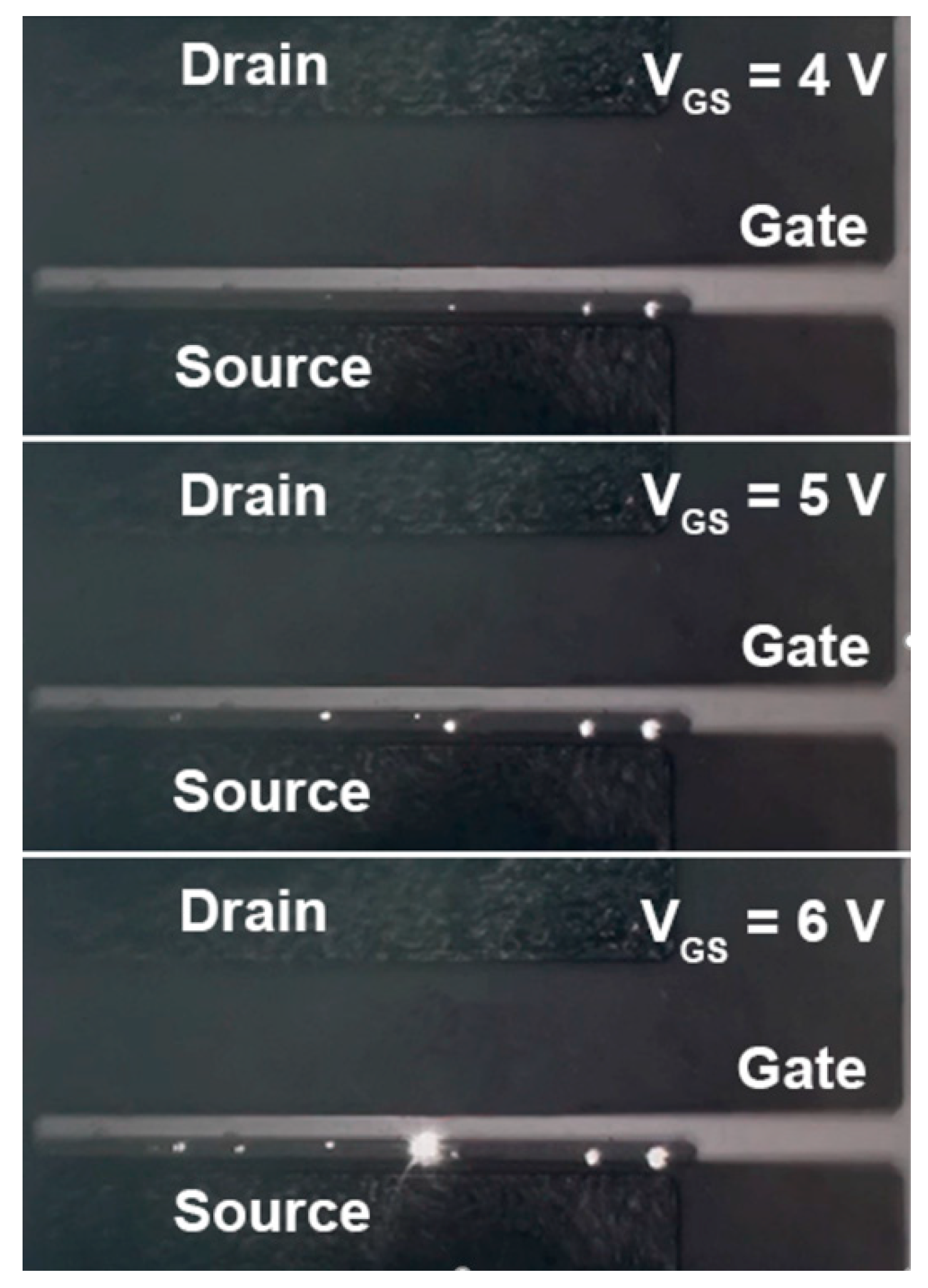

3. Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Chen, K.-J.; Yang, F.; Lu, D.; Huang, H.; Shih, H.-Y.; Lee, P.-C.; Wu, Y.-H.; Wu, C.-Y.; Chang, H.-Y.; Lee, C.-H. kV-class GaN-on-Si HEMTs enabling 99% efficiency converter at 800 V and 100 kHz. IEEE Electron. Device Lett. 2014, 35, 1056–1058. [Google Scholar] [CrossRef]

- DasGupta, S.; Chowdhury, S.; Rajagopal, P. The 2018 GaN power electronics roadmap. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 58–78. [Google Scholar] [CrossRef]

- GaN Systems. GS66502B Datasheet. 2018. Available online: https://gansystems.com/datasheets/GS66502B-DS-Rev1.pdf (accessed on 1 March 2023).

- Efficient Power Conversion. EPC2019 Datasheet. 2019. Available online: http://epc-co.com/epc/documents/datasheets/EPC2019_datasheet.pdf (accessed on 1 March 2023).

- Mandal, S.; DasGupta, S.; Pratap, R.; Rajagopal, P. Observation of dynamic VTH of p-GaN gate HEMTs by fast sweeping characterization. IEEE Trans. Electron Device 2012, 59, 2820–2827. [Google Scholar] [CrossRef]

- Lee, W.; Hsu, J.; Wu, C.; Lai, E.; Cheng, H. Gate architecture design for enhancement mode p-GaN gate HEMTs for 200 and 650 V applications. IEEE Trans. Electron Devices 2014, 61, 1489–1494. [Google Scholar] [CrossRef]

- Huang, Y.-C.; Chen, G.-R.; Chen, K.-M. 200 V enhancement-mode p-GaN HEMTs fabricated on 200 mm GaN-on-SOI with trench isolation for monolithic integration. IEEE J. Electron Devices Soc. 2017, 5, 10–16. [Google Scholar] [CrossRef]

- Chang, P.-H.; Huang, J.; Tsai, J. Wide energy bandgap electronic devices. J. Electron. Sci. Technol. China 2017, 15, 219–229. [Google Scholar] [CrossRef]

- Meneghesso, G.; Sabui, G.; Zanoni, E. Challenges for energy efficient wide band gap semiconductor power devices. IEEE Trans. Electron Devices 2017, 64, 3655–3667. [Google Scholar] [CrossRef]

- Wei, Y.-T.; Chou, H.-C.; Wu, Y.-H.; Yang, F.; Lee, C.-H. Demonstration of Schottky barrier diode integrated in 200 V power p-GaN HEMTs technology with robust stability. IEEE J. Electron Devices Soc. 2016, 4, 37–41. [Google Scholar] [CrossRef]

- Chow, T.-P.; Morkoç, H. GaN-on-Si power technology: Devices and applications. IEEE Trans. Electron Devices 2010, 57, 2245–2254. [Google Scholar] [CrossRef]

- Wang, J.; Li, P.; Yuan, Y.; Zhang, J.; Tian, Q.; Liu, Y.; Chen, J.; Li, X.; Zhao, T. Normally-off high-voltage p-GaN gate GaN HFET with carbon-doped buffer. IEEE Electron Device Lett. 2017, 38, 748–751. [Google Scholar] [CrossRef]

- Sasaki, T.; Otsuka, T.; Tsukahara, Y.; Nakano, Y. Enhancement-mode GaN-based high-electron mobility transistors on the Si substrate with a P-type GaN cap layer. IEEE Trans. Electron Devices 2015, 62, 3145–3150. [Google Scholar] [CrossRef]

- Xu, W.; Chen, D.; Wu, D.; Zhang, J.; Yang, Z.; Shen, B.; Zhang, J. Effects of annealing treatments on the properties of Al/Ti/p-GaN interfaces for normally off p-GaN HEMTs. Appl. Surf. Sci. 2017, 409, 66–71. [Google Scholar] [CrossRef]

- Wang, T.; Jiang, L.; Zhang, M.; Jiang, Y. A novel physics-based approach to analyze and model E-mode p-GaN power HEMTs. IEEE Trans. Power Electron. 2019, 34, 1524–1534. [Google Scholar] [CrossRef]

- Kim, J.; Lee, K.; Hwang, J.; Lee, M.; Lee, J.; Lee, S.; Kang, S.; Lee, J.; Nam, O.; Lee, H.; et al. High-voltage and low-leakage-current gate recessed normally-off GaN MIS-HEMTs with dual gate insulator employing PEALD-SiNx/RF-sputtered-HfO2. IEEE Trans. Electron Devices 2016, 63, 3476–3479. [Google Scholar] [CrossRef]

- Zhang, J.; Jang, J.; Kim, H.; Lee, J. Monolithic integration of lateral field-effect rectifier with normally-off HEMT for GaN-on-Si switch-mode power supply converters. IEEE Trans. Power Electron. 2015, 30, 2518–2523. [Google Scholar] [CrossRef]

- Chowdhury, S.; Mishra, U.; Deshpande, D. An overview of normally-off GaN-based high electron mobility transistors. Proc. IEEE 2012, 100, 2857–2871. [Google Scholar] [CrossRef]

- Xu, C.; Xu, Q.; Wang, M.; Liu, Y.; Zhang, Y.; Li, M.; Li, Y. Time-dependent failure of GaN-on-Si power HEMTs with p-GaN gate. IEEE Trans. Device Mater. Reliab. 2019, 19, 302–307. [Google Scholar] [CrossRef]

- Kim, C.; Cho, H.; Cho, N.; Lee, J. Gate current transport in enhancement-mode p-nJunction/AlGaN/GaN (PNJ) HEMT. J. Korean Phys. Soc. 2017, 71, 273–277. [Google Scholar] [CrossRef]

- Kim, M.; Oh, S.; Kim, S.; Kim, S.; Ju, S.; Hong, Y. Improved gate reliability normally-off p-GaN/AlN/AlGaN/GaN HEMT with AlGaN cap-layer. IEEE Electron Device Lett. 2017, 38, 1055–1058. [Google Scholar] [CrossRef]

- Krishnaswamy, N.; Sohal, M.; Palmour, J.W. Forward Bias Gate Breakdown Mechanism in Enhancement-Mode p-GaN Gate AlGaN/GaN High-Electron Mobility Transistors. IEEE Trans. Electron Devices 2018, 65, 3429–3434. [Google Scholar]

- Takeishi, T.; Muraguchi, M.; Katayama, R.; Tanaka, T. Gate injection transistor (GIT)—A normally-off AlGaN/GaN power transistor using conductivity modulation. Proc. IEEE Trans. Electron Devices 2008, 55, 1806–1813. [Google Scholar]

- Johnson, C.M. Reliability Issues in GaN and SiC Power Devices. In Proceedings of the IEEE Transactions on Device and Materials Reliability, Waikoloa, HI, USA, 1–5 June 2013; Volume 13, pp. 394–406. [Google Scholar]

- Kim, S.; Kim, S.; Kim, T.; Kim, G.; Kwon, H.-I.; Kwon, Y. Demonstration of p-GaN/AlGaN/GaN high electron mobility transistors with an indium-tin-oxide gate electrode. Appl. Phys. Lett. 2017, 110, 183503. [Google Scholar] [CrossRef]

- Yang, X.; Li, J.; Li, X.; Li, H.; Liang, S.; Du, S.; Zhou, S. Investigation on stability of p-GaN HEMTs with an indium-tin-oxide gate under forward gate bias. Microelectron. Reliab. 2019, 97, 155–159. [Google Scholar] [CrossRef]

- Wu, Y.; Chen, Q.; Zhang, C.; Yang, B.; Xu, J.; Zhang, Y.; Chen, Z.; Lu, J. Fully transparent AlGaN/GaN high electron mobility transistors fabricated with indium-tin-oxide electrodes. Appl. Phys. Lett. 2019, 114, 052103. [Google Scholar] [CrossRef]

- Verzellesi, G.; Meneghesso, G.; Zanoni, E.; Rampazzo, F.; Paccagnella, A.; Van Hove, M. Transient thermal characterization of AlGaN/GaN HEMTs under pulsed biasing. IEEE Trans. Electron Devices 2013, 60, 1705–1712. [Google Scholar] [CrossRef]

- Oh, H.; Kim, D.; Choi, M.; Kim, B.; Lee, H. Charge storage impact on input capacitance in p-GaN gate AlGaN/GaN power high-electron-mobility transistors. Jpn. J. Appl. Phys. 2014, 53, 04EC08. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Han, Z.; Li, X.; Wang, H.; Yuan, J.; Wang, J.; Wang, M.; Yang, W.; You, S.; Chang, J.; Zhang, J.; et al. Investigating the Failure Mechanism of p-GaN Gate HEMTs under High Power Stress with a Transparent ITO Gate. Micromachines 2023, 14, 940. https://doi.org/10.3390/mi14050940

Han Z, Li X, Wang H, Yuan J, Wang J, Wang M, Yang W, You S, Chang J, Zhang J, et al. Investigating the Failure Mechanism of p-GaN Gate HEMTs under High Power Stress with a Transparent ITO Gate. Micromachines. 2023; 14(5):940. https://doi.org/10.3390/mi14050940

Chicago/Turabian StyleHan, Zhanfei, Xiangdong Li, Hongyue Wang, Jiahui Yuan, Junbo Wang, Meng Wang, Weitao Yang, Shuzhen You, Jingjing Chang, Jincheng Zhang, and et al. 2023. "Investigating the Failure Mechanism of p-GaN Gate HEMTs under High Power Stress with a Transparent ITO Gate" Micromachines 14, no. 5: 940. https://doi.org/10.3390/mi14050940

APA StyleHan, Z., Li, X., Wang, H., Yuan, J., Wang, J., Wang, M., Yang, W., You, S., Chang, J., Zhang, J., & Hao, Y. (2023). Investigating the Failure Mechanism of p-GaN Gate HEMTs under High Power Stress with a Transparent ITO Gate. Micromachines, 14(5), 940. https://doi.org/10.3390/mi14050940