Machine Learning Algorithm for Efficient Design of Separated Buffer Super-Junction IGBT

Abstract

:1. Introduction

2. Structure and Methodology

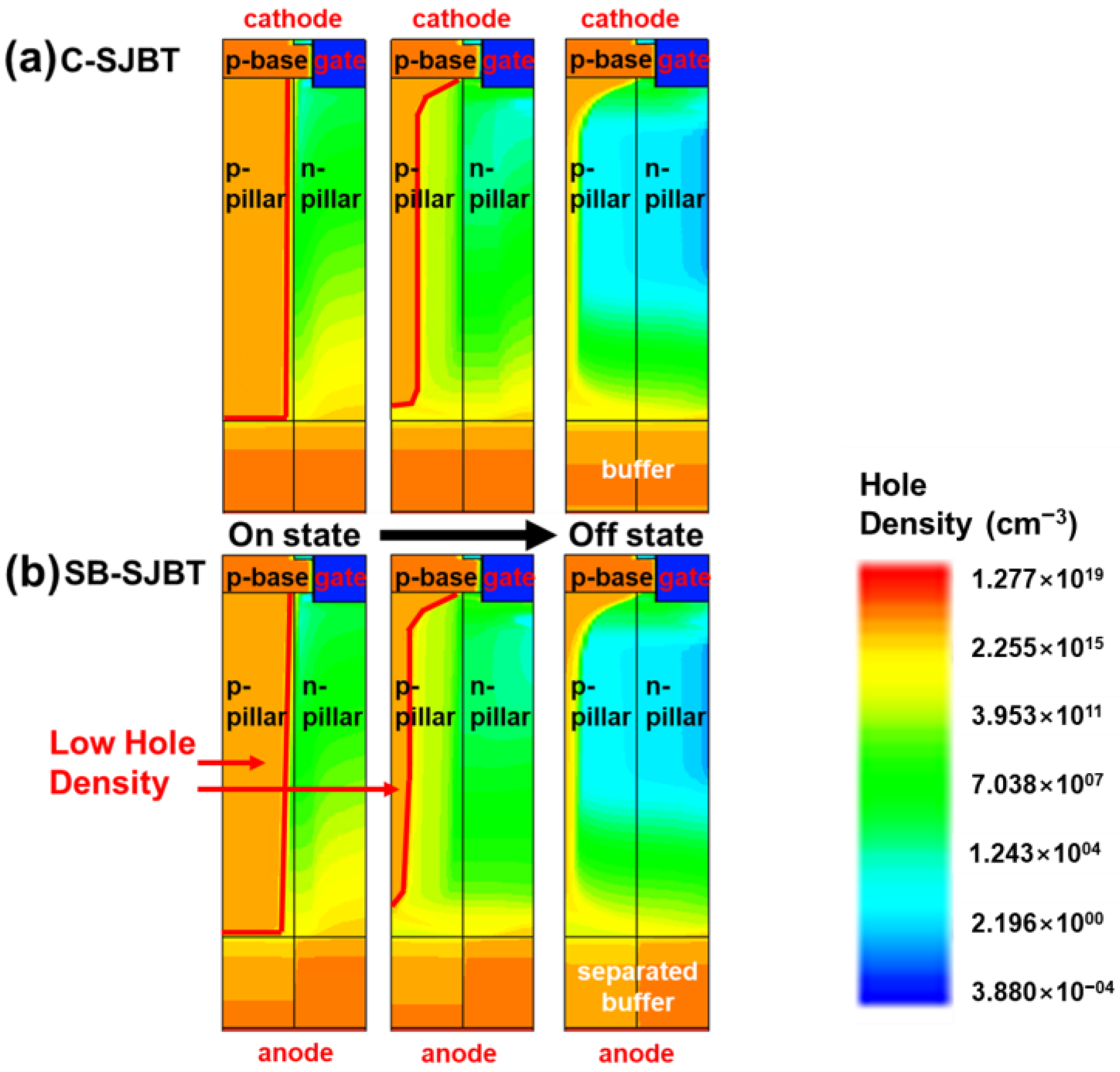

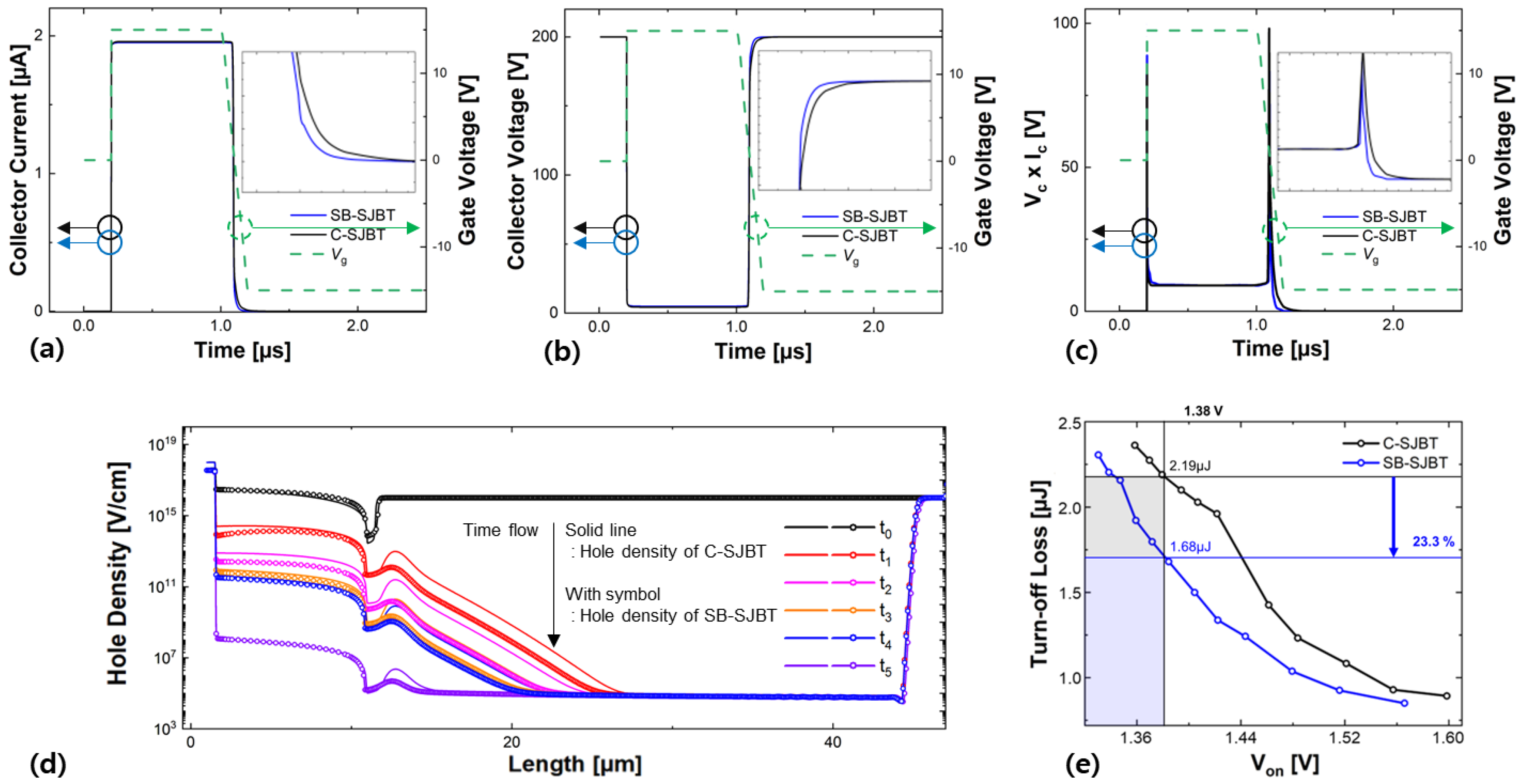

2.1. Proposed Structure and Characteristics

2.2. Designing ML Algorithm

3. Model Validation and Results

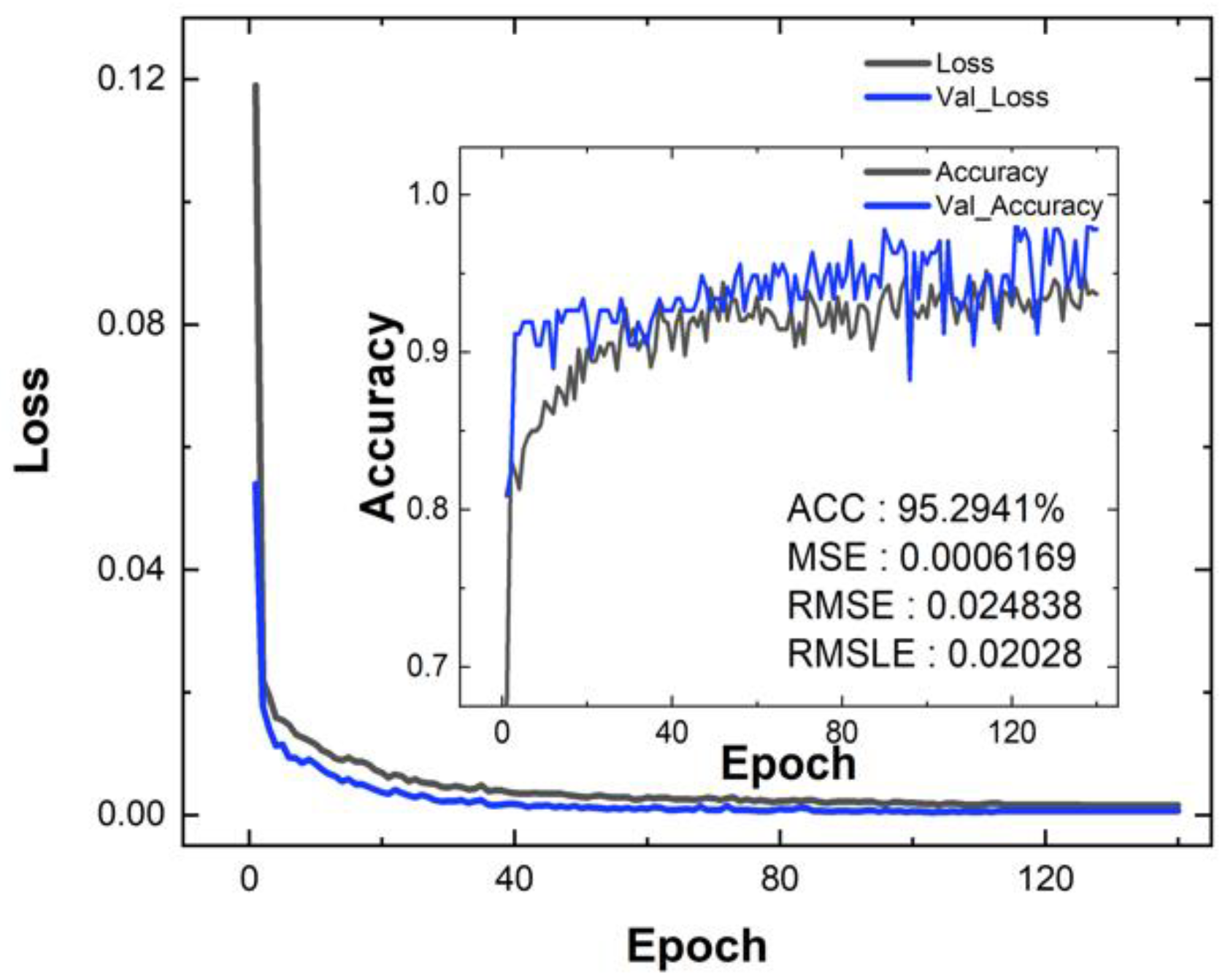

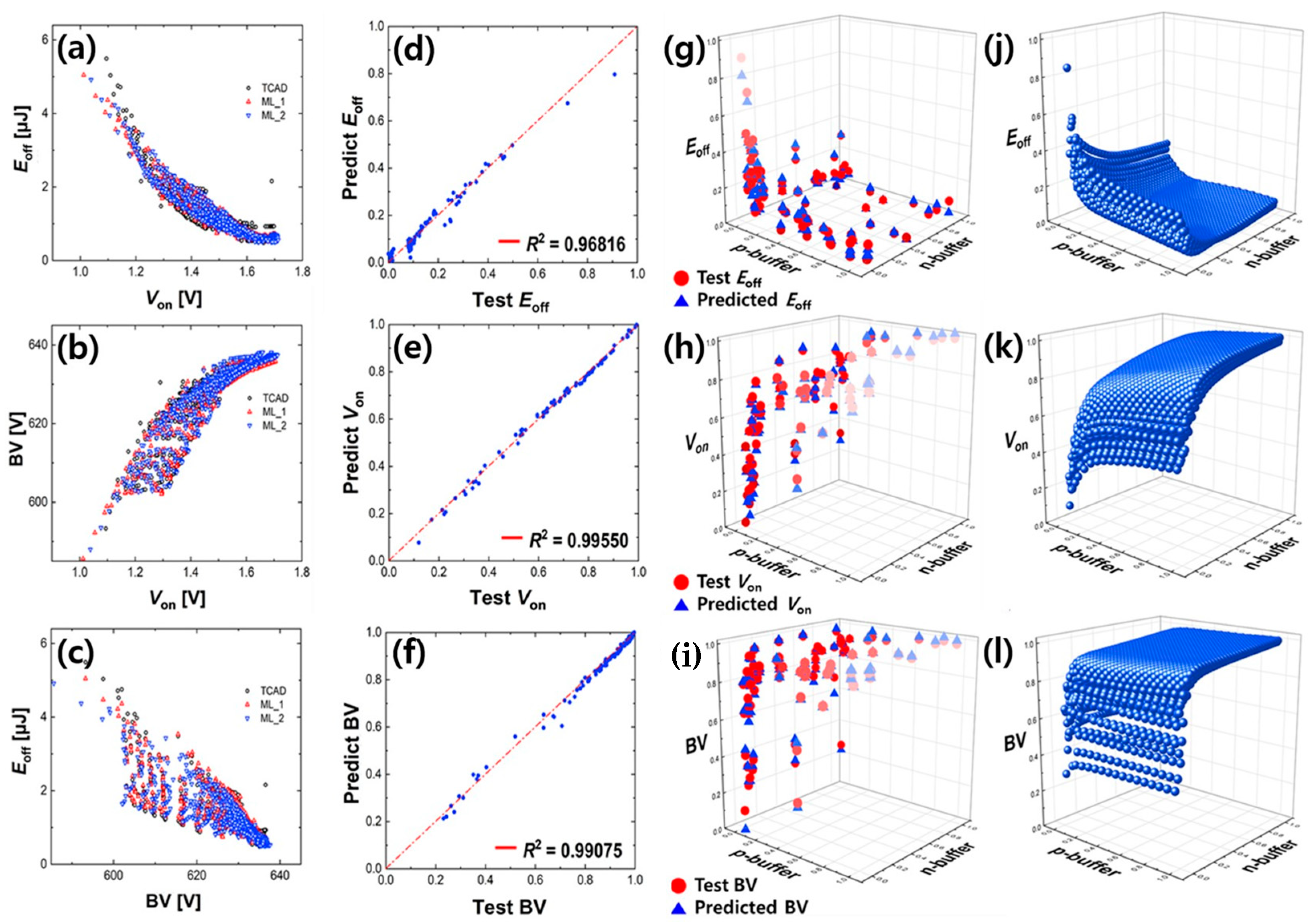

3.1. Verification of Model Reliability

- µ: mean;

- σ: standard deviation;

- n: number of samples in one set of data.

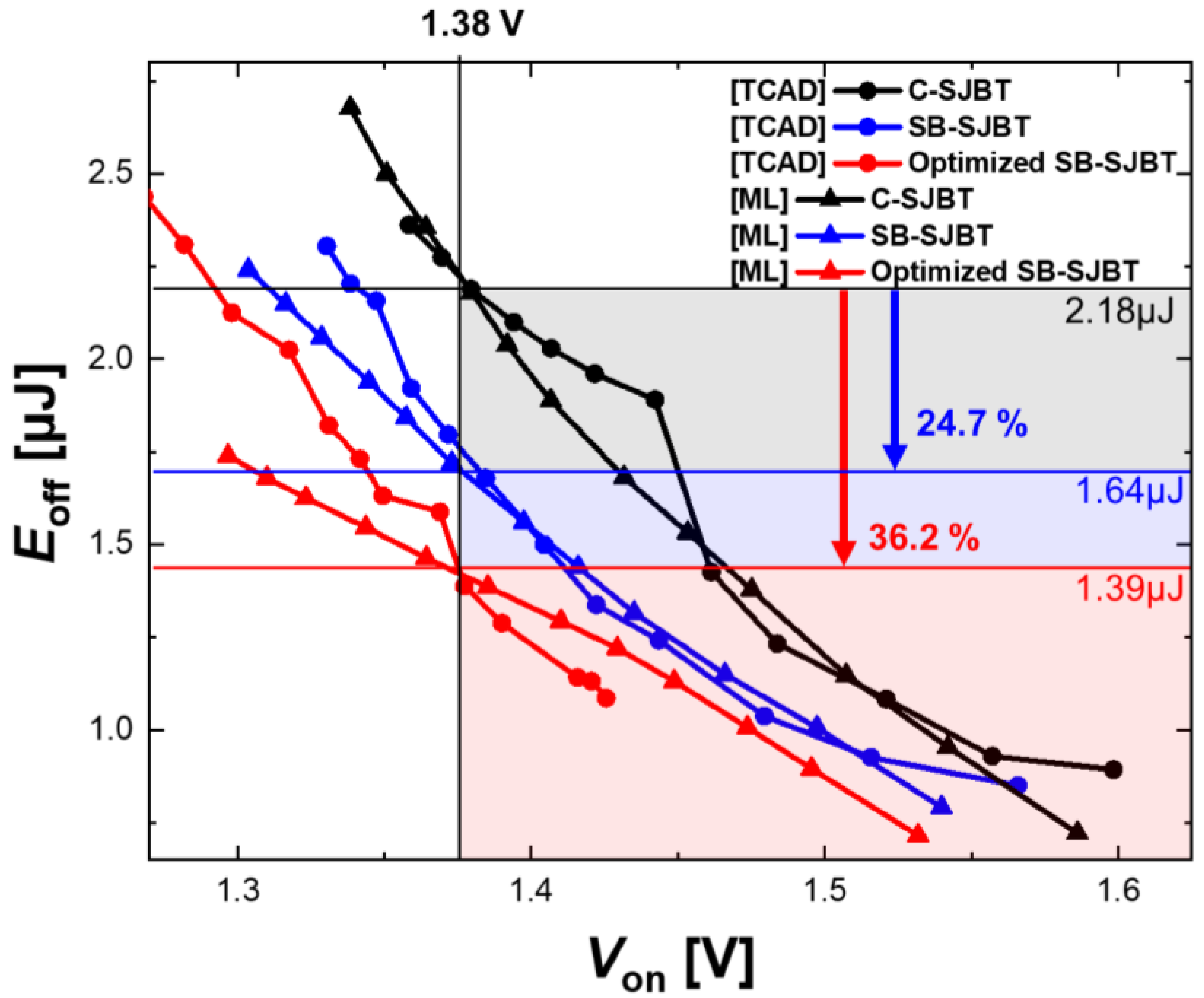

3.2. Optimization

3.3. Reverse Engineering by NN

4. Conclusions

Author Contributions

Funding

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Aghdam, M.G.H.; Thiringer, T. Comparison of SiC and Si Power Semiconductor Devices to Be Used in 2.5 Kw Dc/Dc Converter. In Proceedings of the International Conference on Power Electronics and Drive Systems, Taipei, Taiwan, 2–5 November 2009; pp. 1035–1040. [Google Scholar]

- Shimizu, H.; Harada, J.; Bland, C. Role of Optimized Vehicle Design and Power Semiconductor Devices to Improve the Performance of an Electric Vehicle. In Proceedings of the IEEE International Symposium on Power Semiconductor Devices & ICs (ISPSD), Yokohama, Japan, 23–25 May 1995; pp. 8–12. [Google Scholar]

- Wang, Y.; Li, Y.; Dai, X.; Zhu, S.; Jones, S.; Liu, G. Thermal Design of a Dual Sided Cooled Power Semiconductor Module for Hybrid and Electric Vehicles. In Proceedings of the Applied Power Electronics Conference and Exposition—APEC, Tampa, FL, USA, 26–30 March 2017; pp. 3068–3071. [Google Scholar]

- Bauer, F. The MOS Controlled Super Junction Transistor (SJBT): A New, Highly Efficient, High Power Semiconductor Device for Medium to High Voltage Applications. In Proceedings of the IEEE International Symposium on Power Semiconductor Devices and ICs (ISPSD), Santa Fe, NM, USA, 7 June 2002; pp. 197–200. [Google Scholar]

- Bauer, F.D. The Super Junction Bipolar Transistor: A New Silicon Power Device Concept for Ultra Low Loss Switching Applications at Medium to High Voltages. Solid. State. Electron. 2004, 48, 705–714. [Google Scholar] [CrossRef]

- Antoniou, M.; Udrea, F. Simulated Superior Performance of Superjuction Bipolar Transistors. In Proceedings of the International Semiconductor Conference, CAS, Lumpur, Malaysia, 29 November–1 December 2006; Volume 2, pp. 293–296. [Google Scholar]

- Laska, T.; Münzer, M.; Pfirsch, F.; Schaeffer, C.; Schmidt, T. The Field Stop IGBT (FS IGBT)—A New Power Device Concept with a Great Improvement Potential. In Proceedings of the IEEE International Symposium on Power Semiconductor Devices and ICs (ISPSD), Toulouse, France, 22–25 May 2000; pp. 355–358. [Google Scholar]

- Eicher, S.; Bauer, F.; Weber, A.; Zeller, H.R.; Fichtner, W. Punchthrough Type GTO with Buffer Layer and Homogeneous Low Efficiency Anode Structure. In Proceedings of the IEEE International Symposium on Power Semiconductor Devices & ICs (ISPSD), Maui, HI, USA, 23 May 1996; pp. 261–264. [Google Scholar]

- Eicher, S.; Bauer, F.; Zeller, H.R.; Weber, A.; Fichtner, W. Design Considerations for a 7kV/3kA GTO with Transparent Anode and Buffer Layer. In Proceedings of the PESC Record—IEEE Annual Power Electronics Specialists Conference, Baveno, Italy, 23–27 June 1996; Volume 1, pp. 29–34. [Google Scholar]

- Widjaja, I.; Kurnia, A.; Divan, D.; Shenai, K. Conductivity Modulation Lag During IGBT Turn On in Resonant Converter Applications. In Proceedings of the 52nd Annual Device Research Conference, Boulder, CO, USA, 20–22 June 1992. [Google Scholar]

- Shenoy, P.M.; Bhalla, A.; Dolny, G.M. Analysis of the Effect of Charge Imbalance on the Static and Dynamic Characteristics of the Super Junction MOSFET. In Proceedings of the IEEE International Symposium on Power Semiconductor Devices and ICs (ISPSD), Toronto, ON, Canada, 26–28 May 1999; pp. 99–102. [Google Scholar]

- Yamashita, J.; Yamada, T.; Uchida, S.; Yamaguchi, H.; Ishizawa, S. Relation between Dynamic Saturation Characteristics and Tail Current of Non-Punchthrough IGBT. In Proceedings of the Conference Record—IAS Annual Meeting (IEEE Industry Applications Society), San Diego, CA, USA, 6–10 October 1996; Volume 3, pp. 1425–1432. [Google Scholar]

- Suwa, T.; Hayase, S. Investigation of Tcad Calibration for Saturation and Tail Current of 6.5kv Igbts. In Proceedings of the International Conference on Simulation of Semiconductor Processes and Devices, SISPAD, Udine, Italy, 4–6 September 2019; Volume 2019, pp. 1–4. [Google Scholar]

- Wei, J.; Zhang, M.; Chen, K.J. Design of Dual-Gate Superjunction IGBT towards Fully Conductivity-Modulated Bipolar Conduction and Near-Unipolar Turn-Off. In Proceedings of the International Symposium on Power Semiconductor Devices and ICs, Vienna, Austria, 13–18 September 2020; Volume 2020, pp. 498–501. [Google Scholar]

- Luo, X.; Zhang, S.; Wei, J.; Yang, Y.; Su, W.; Fan, D.; Li, C.; Li, Z.; Zhang, B. A Low Loss and On-State Voltage Superjunction IGBT with Depletion Trench. In Proceedings of the International Symposium on Power Semiconductor Devices and ICs, Vienna, Austria, 13–18 September 2020; Volume 2020, pp. 130–133. [Google Scholar]

- Noh, J.S.; Lee, K.; Park, S.H.; Jeon, M.G.; Yoon, T.Y.; Kim, J.H. Improvement in Turn-off Loss Characteristic for The Super Junction IGBT with Separated n-Buffer Layers. In Proceedings of the Nano Korea, Goyang, Republic of Korea, 7–9 July 2021; p. 759. [Google Scholar]

- Li, W.; Wang, B.; Liu, J.; Zhang, G.; Wang, J. IGBT Aging Monitoring and Remaining Lifetime Prediction Based on Long Short-Term Memory (LSTM) Networks. Microelectron. Reliab. 2020, 114, 113902. [Google Scholar] [CrossRef]

- Tyagi, M.S.; Van Overstraeten, R. Minority Carrier Recombination in Heavily-Doped Silicon. Solid. State. Electron. 1983, 26, 577–597. [Google Scholar] [CrossRef]

- Agarap, A.F. Deep Learning Using Rectified Linear Units (Relu). arXiv 2018, arXiv:1803.08375. [Google Scholar]

- Kingma, D.P.; Ba, J.L. Adam: A Method for Stochastic Optimization. In Proceedings of the 3rd International Conference for Learning Representations, San Diego, CA, USA, 7–9 May 2015; pp. 1–15. [Google Scholar]

- Zeiler, M.D. ADADELTA: An Adaptive Learning Rate Method. arXiv 2012, arXiv:1212.5701. [Google Scholar]

- Ba, J.L.; Kiros, J.R.; Hinton, G.E. Layer Normalization. arXiv 2016, arXiv:1607.06450. [Google Scholar]

- Ahn, S.; Fessler, J.A. Standard Errors of Mean, Variance, and Standard Deviation Estimators; The University of Michigan: Ann Arbor, MI, USA, 2003; pp. 1–2. [Google Scholar]

- Ko, K.; Lee, J.K.; Kang, M.; Jeon, J.; Shin, H. Prediction of Process Variation Effect for Ultrascaled GAA Vertical FET Devices Using a Machine Learning Approach. IEEE Trans. Electron Devices 2019, 66, 4474–4477. [Google Scholar] [CrossRef]

- Lim, J.; Shin, C. Machine Learning (ML)-Based Model to Characterize the Line Edge Roughness (LER)-Induced Random Variation in FinFET. IEEE Access 2020, 8, 158237–158242. [Google Scholar] [CrossRef]

- Mehta, K.; Raju, S.S.; Xiao, M.; Wang, B.; Zhang, Y.; Wong, H.Y. Improvement of TCAD Augmented Machine Learning Using Autoencoder for Semiconductor Variation Identification and Inverse Design. IEEE Access 2020, 8, 143519–143529. [Google Scholar] [CrossRef]

| Parameter | C-SJBT | SB-SJBT |

|---|---|---|

| Width | 3.0 µm | 3.0 µm |

| Length | 50.0 µm | 50.0 µm |

| Gate depth | 5.0 µm | 5.0 µm |

| p/n-pillar width | 1.5 µm | 1.5 µm |

| p/n-side n-buffer width | - | 1.5 µm |

| n-buffer layer depth | 9.5 µm | 9.5 µm |

| p-base doping | cm−3 | cm−3 |

| n-source doping | cm−3 | cm−3 |

| p/n-pillar doping | cm−3 | cm−3 |

| n-buffer doping | cm−3 | - |

| p-collector doping | cm−3 | cm−3 |

| Data Set | Eoff [µJ] | Von [V] | BV [V] | ||||

|---|---|---|---|---|---|---|---|

| µ | σ | µ | σ | µ | σ | ||

| TCAD | 1.19 | 6.94 | 1.511 | 0.137 | 629.03 | 8.719 | |

| ML results 1 | 1.18 | 6.62 | 1.509 | 0.138 | 628.57 | 8.780 | |

| ML results 2 | 1.16 | 6.63 | 1.513 | 0.137 | 629.15 | 8.979 | |

| Confidence interval | Max | 1.24 | 7.27 | 1.571 | 0.142 | 629.63 | 10.489 |

| Min | 1.14 | 6.60 | 1.451 | 0.132 | 619.99 | 8.295 | |

| Structure | A | B | C | D |

|---|---|---|---|---|

| cm−3] | ||||

| cm−3] | ||||

| Eoff [μJ] | ||||

| Von [V] | 1.39 | 1.38 | 1.37 | 1.38 |

| BV [V] | 622.4 | 620.5 | 617.2 | 617.1 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, K.Y.; Hwang, T.H.; Song, Y.S.; Kim, H.; Kim, J.H. Machine Learning Algorithm for Efficient Design of Separated Buffer Super-Junction IGBT. Micromachines 2023, 14, 334. https://doi.org/10.3390/mi14020334

Kim KY, Hwang TH, Song YS, Kim H, Kim JH. Machine Learning Algorithm for Efficient Design of Separated Buffer Super-Junction IGBT. Micromachines. 2023; 14(2):334. https://doi.org/10.3390/mi14020334

Chicago/Turabian StyleKim, Ki Yeong, Tae Hyun Hwang, Young Suh Song, Hyunwoo Kim, and Jang Hyun Kim. 2023. "Machine Learning Algorithm for Efficient Design of Separated Buffer Super-Junction IGBT" Micromachines 14, no. 2: 334. https://doi.org/10.3390/mi14020334

APA StyleKim, K. Y., Hwang, T. H., Song, Y. S., Kim, H., & Kim, J. H. (2023). Machine Learning Algorithm for Efficient Design of Separated Buffer Super-Junction IGBT. Micromachines, 14(2), 334. https://doi.org/10.3390/mi14020334