Compact Physics Hot-Carrier Degradation Model Valid over a Wide Bias Range

Abstract

1. Introduction

2. Experimental

3. The Model

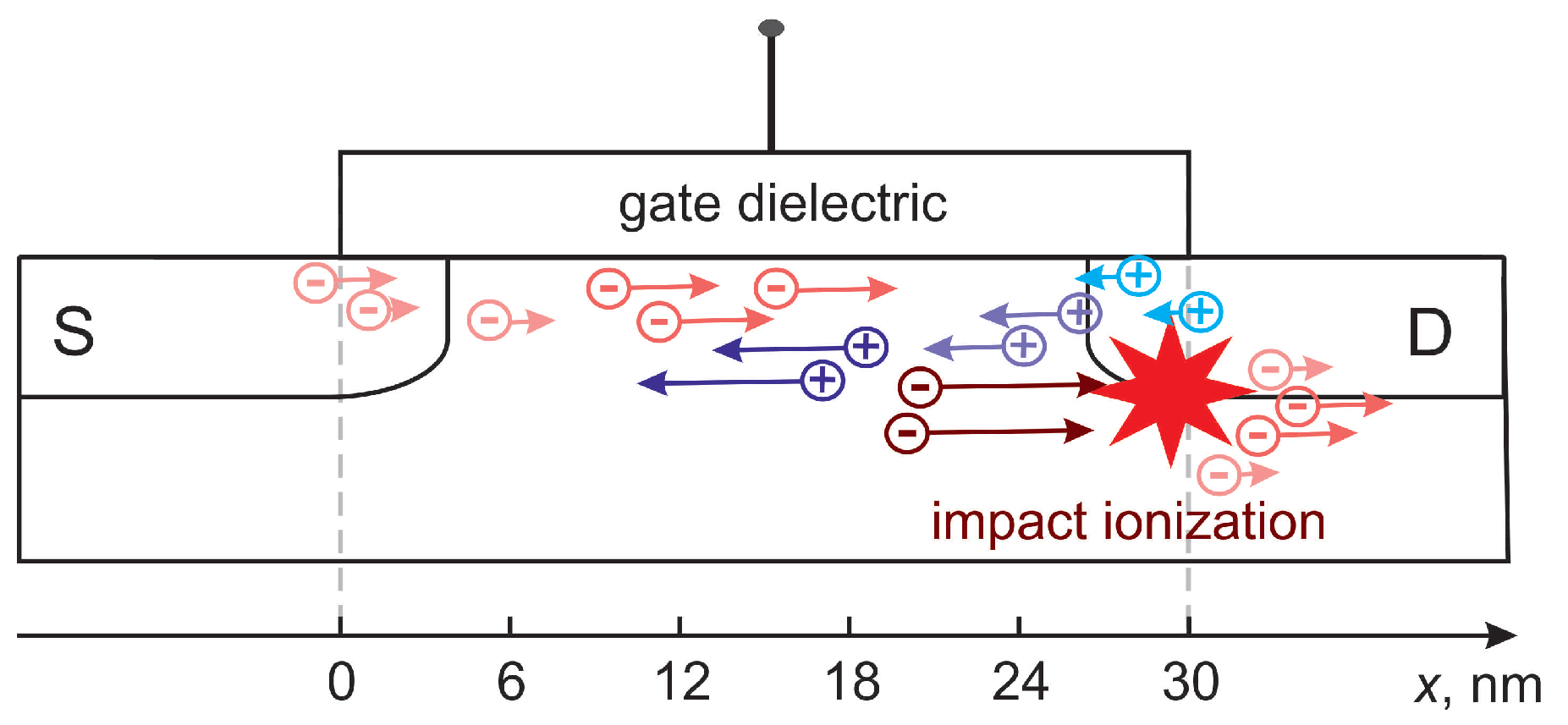

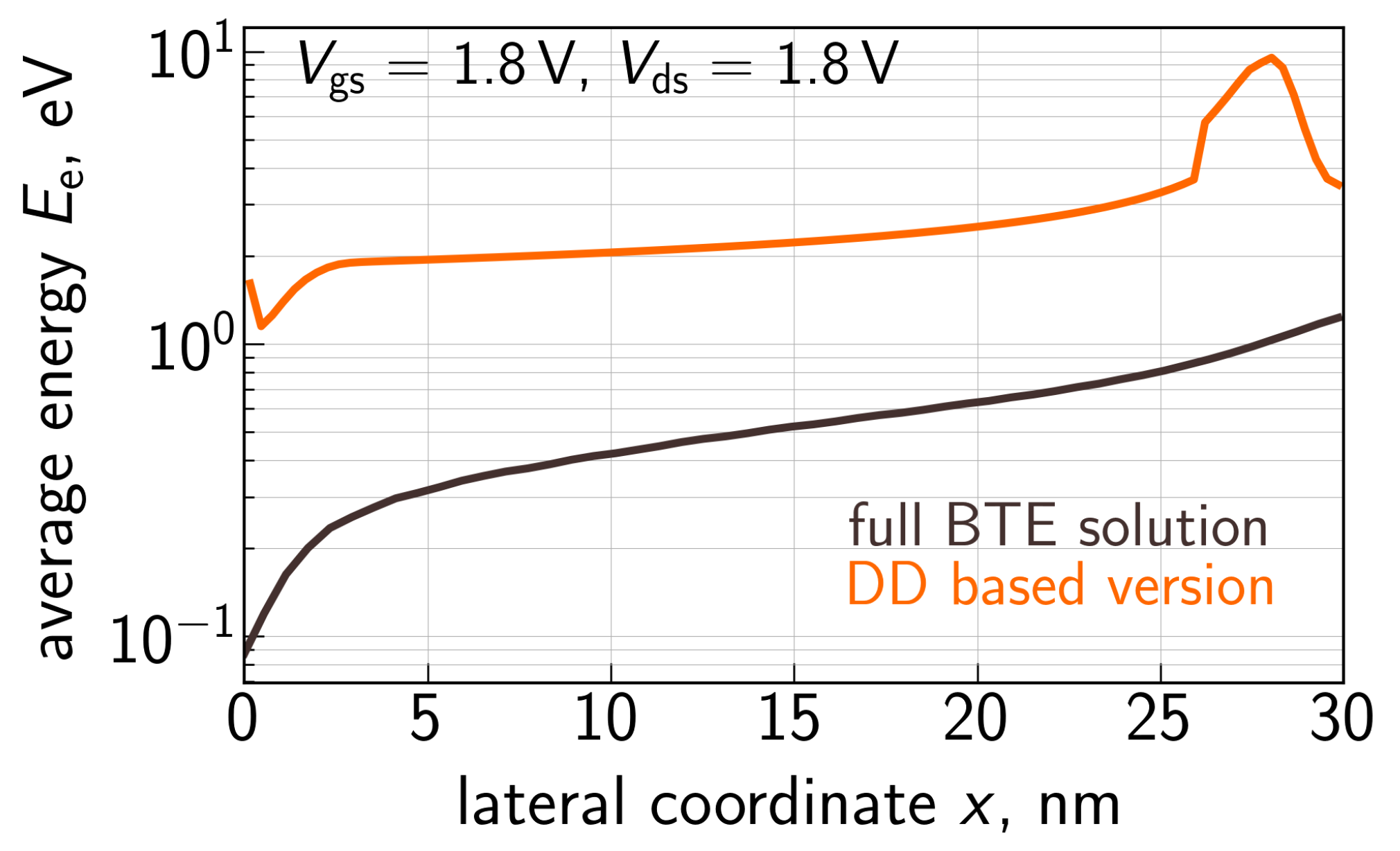

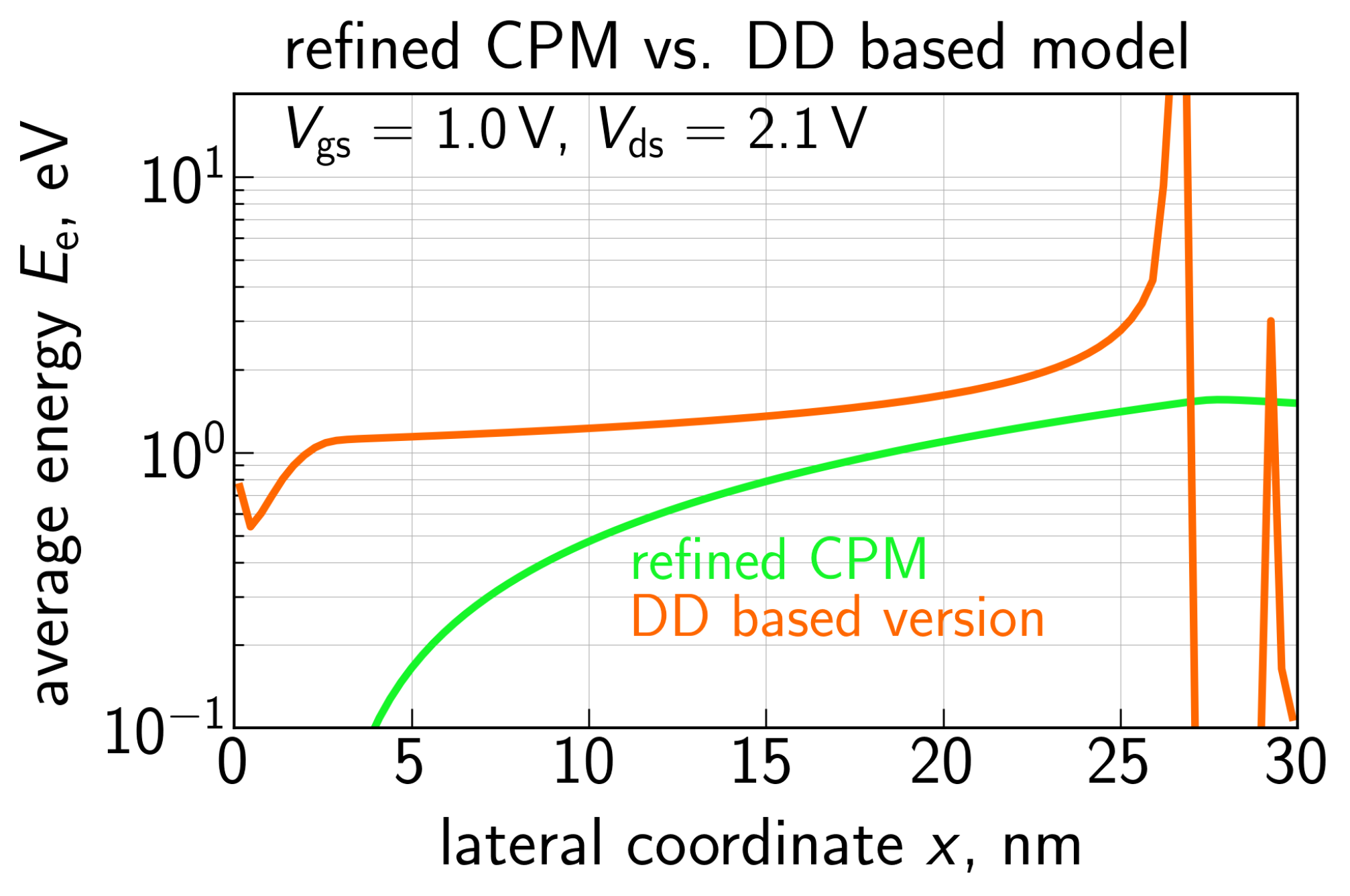

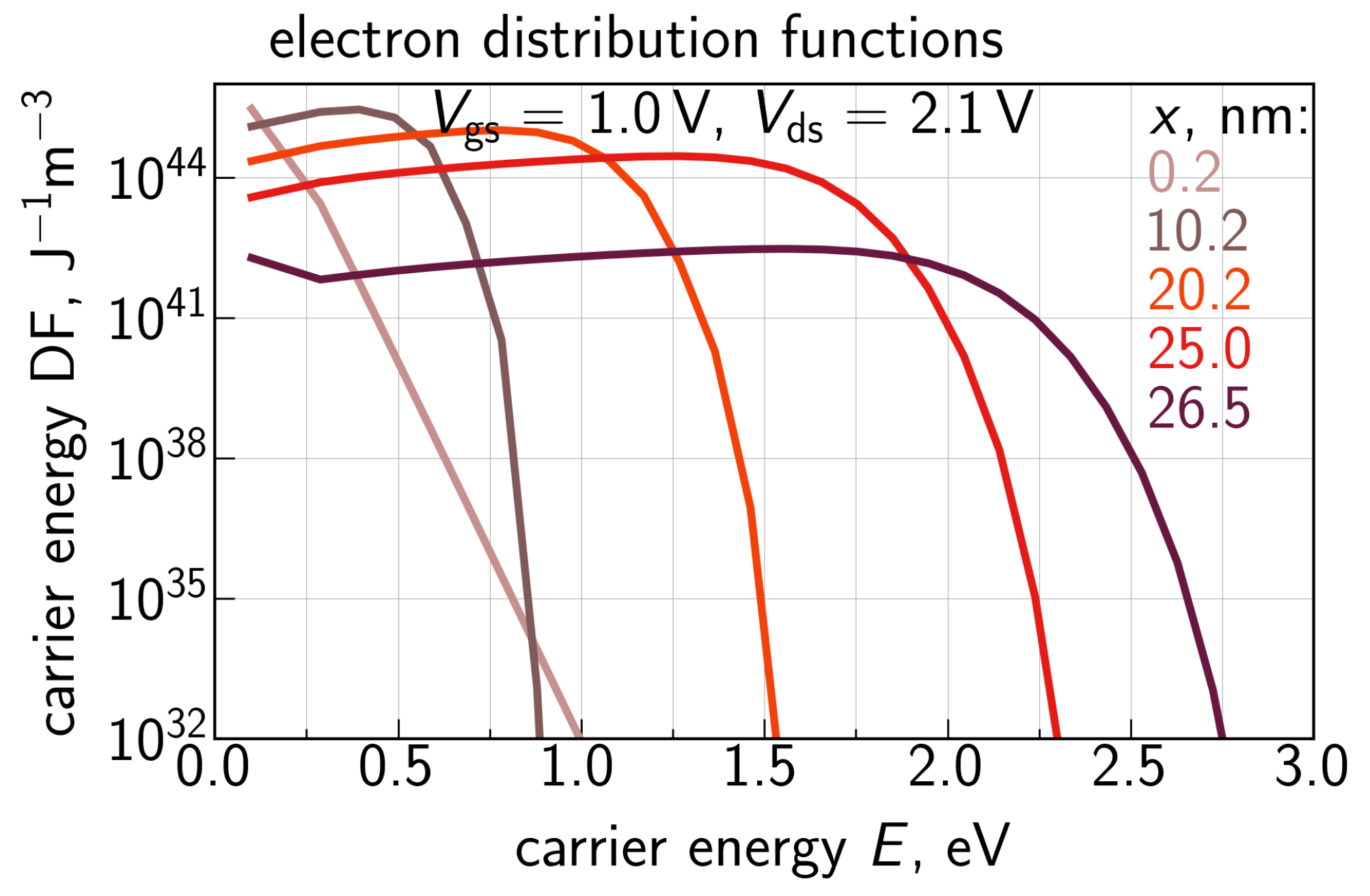

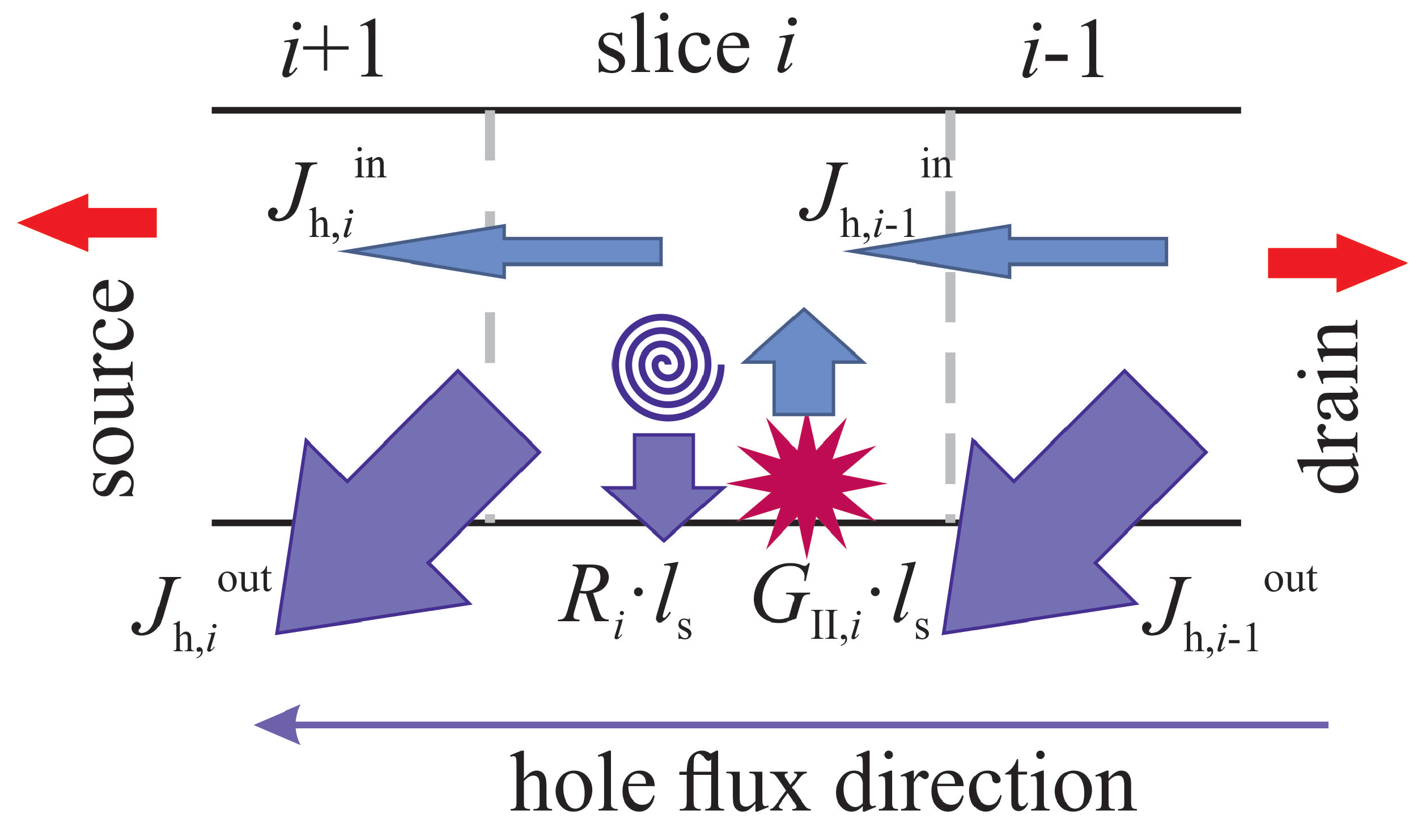

3.1. Transport of Primary Carriers

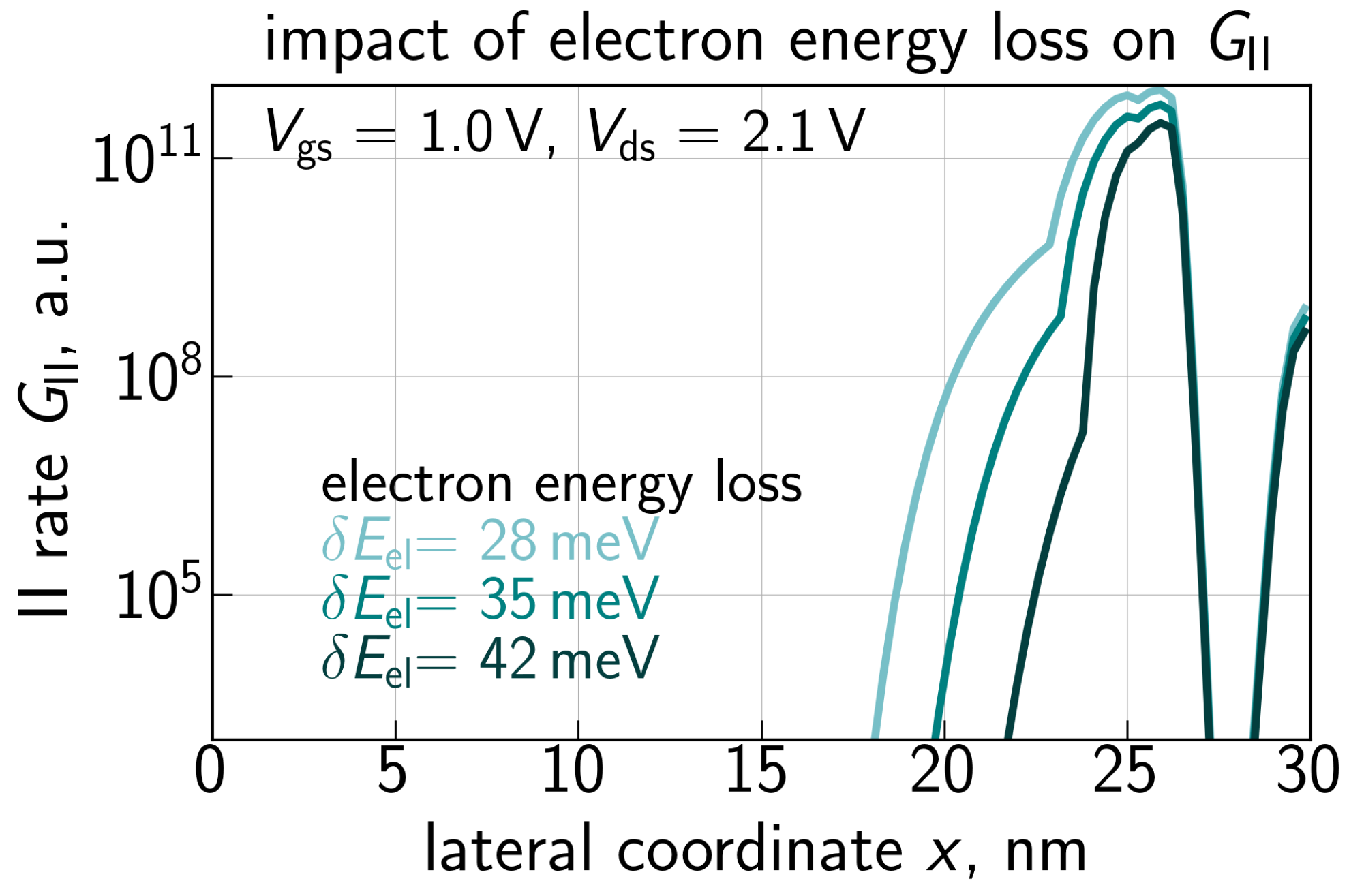

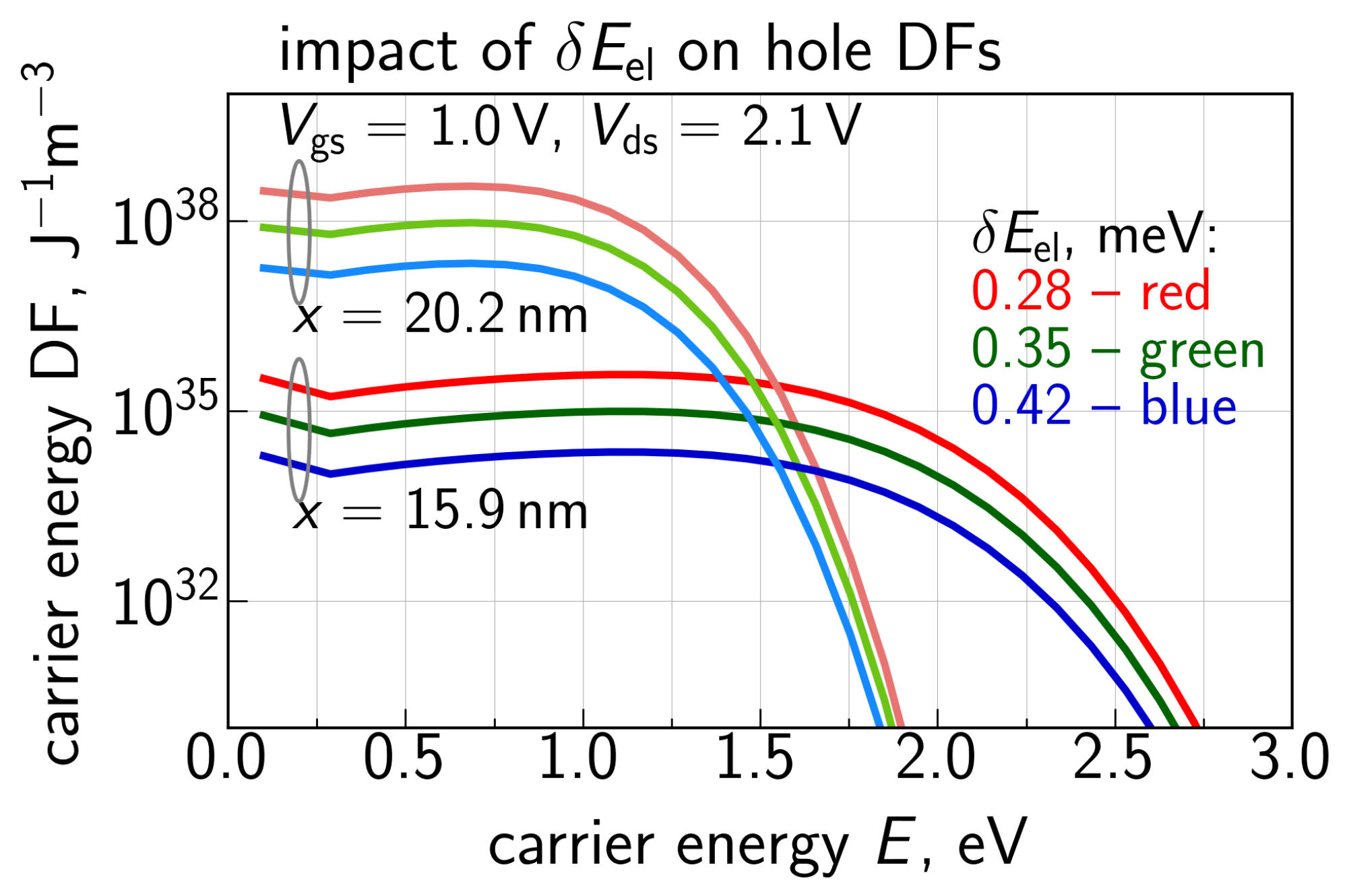

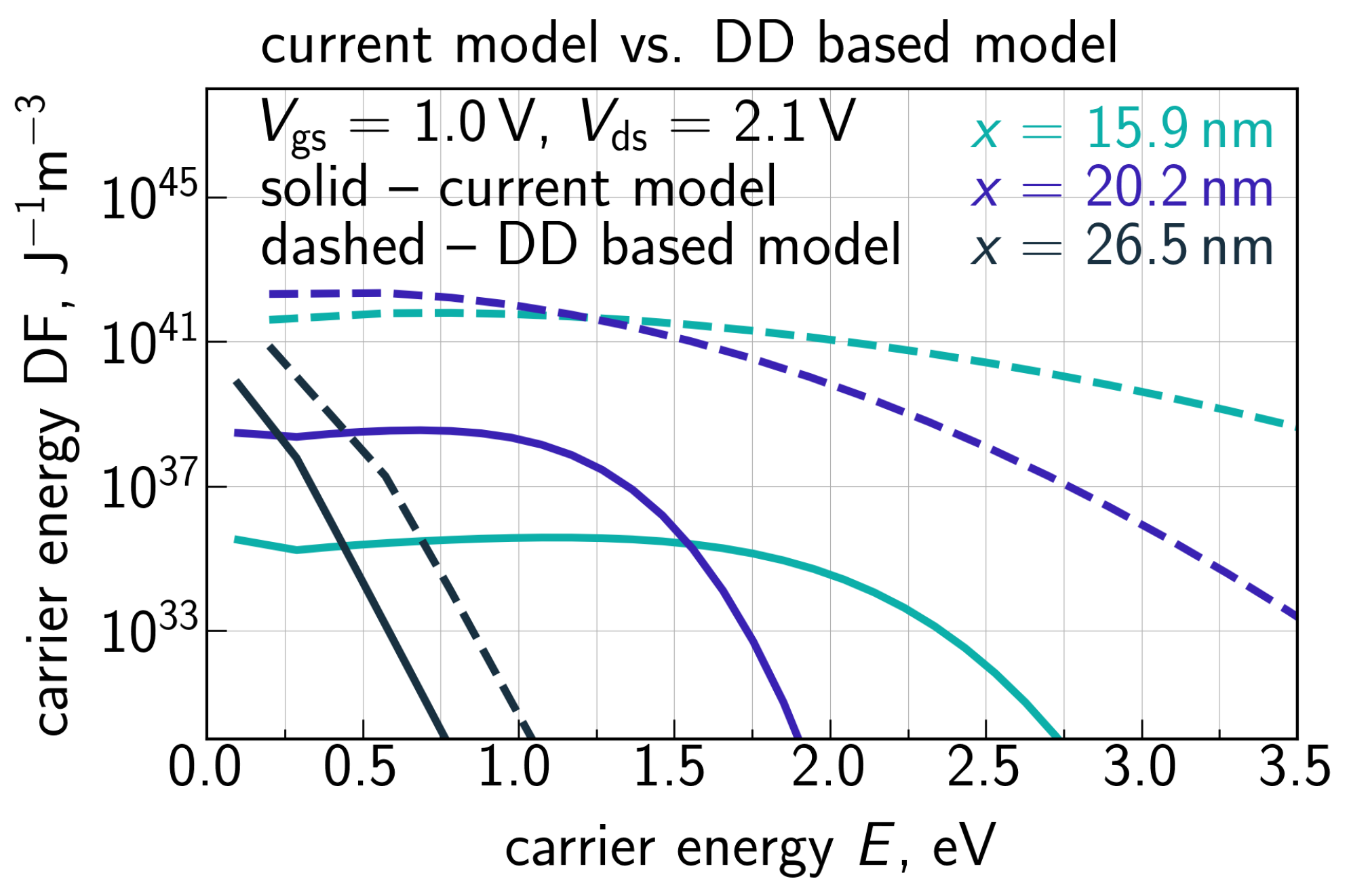

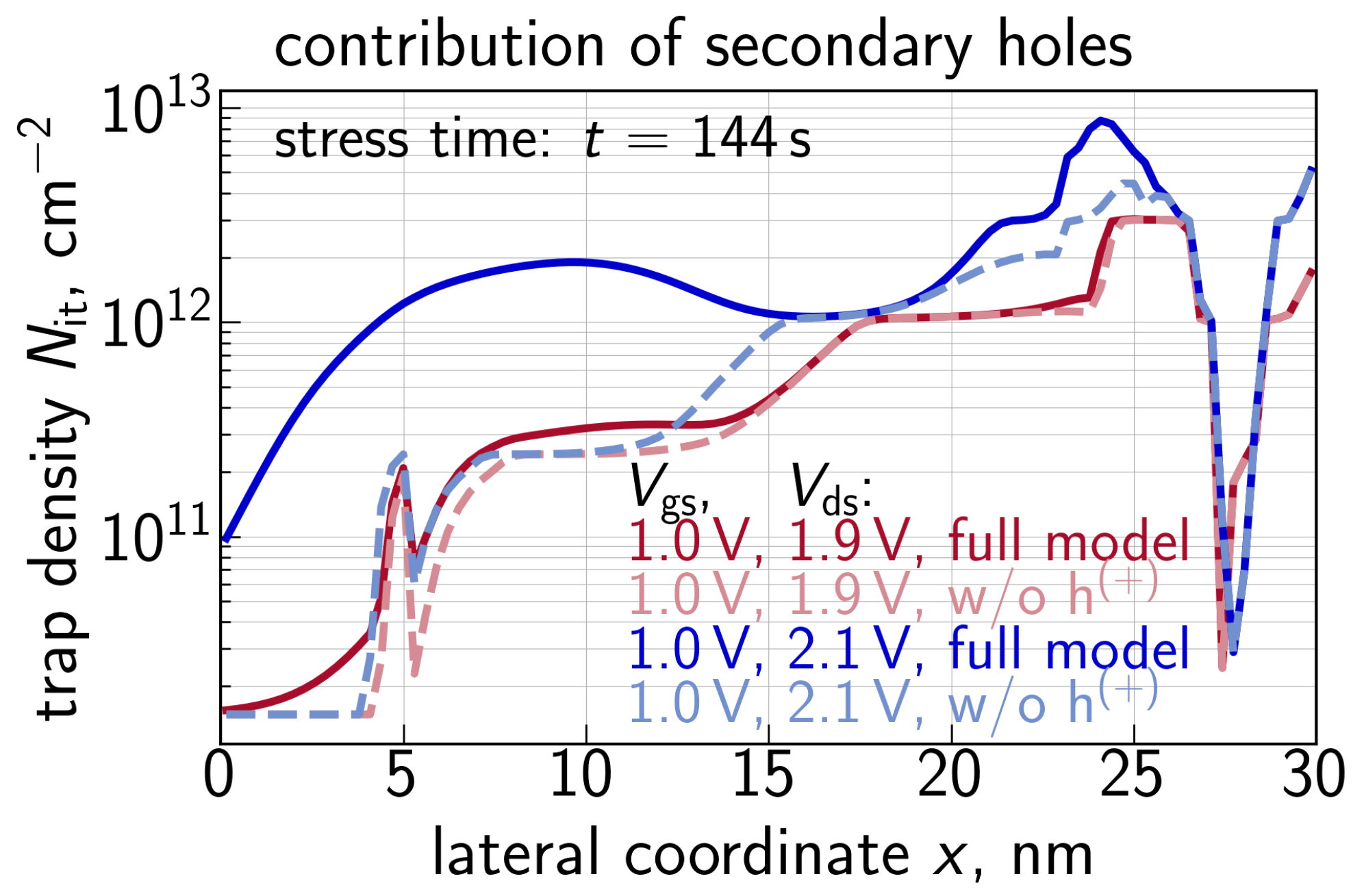

3.2. Transport of Secondary Carriers

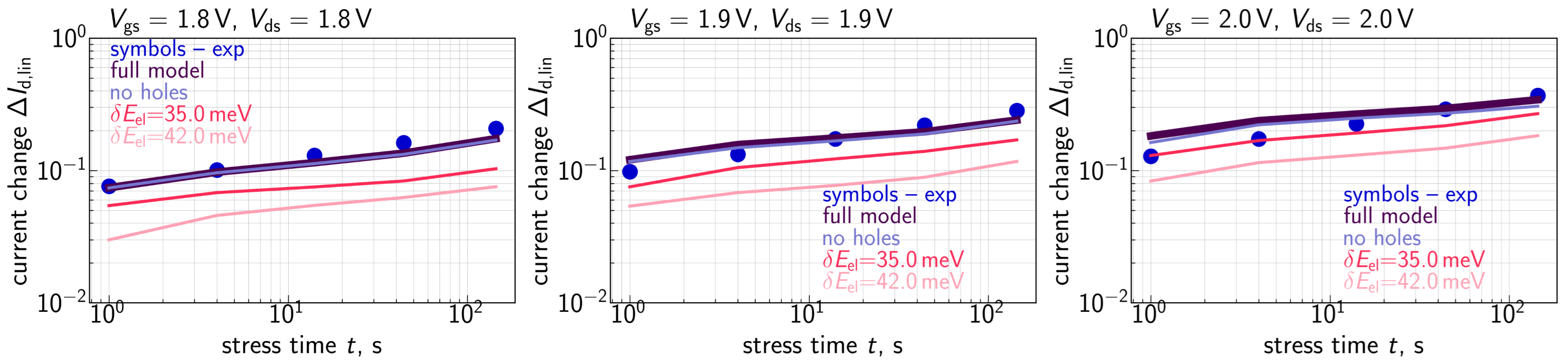

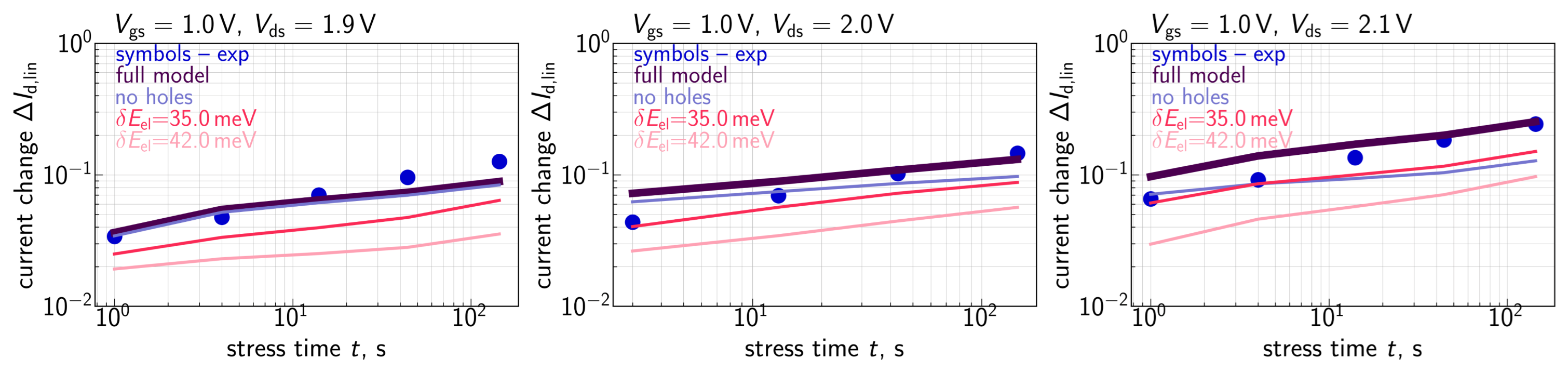

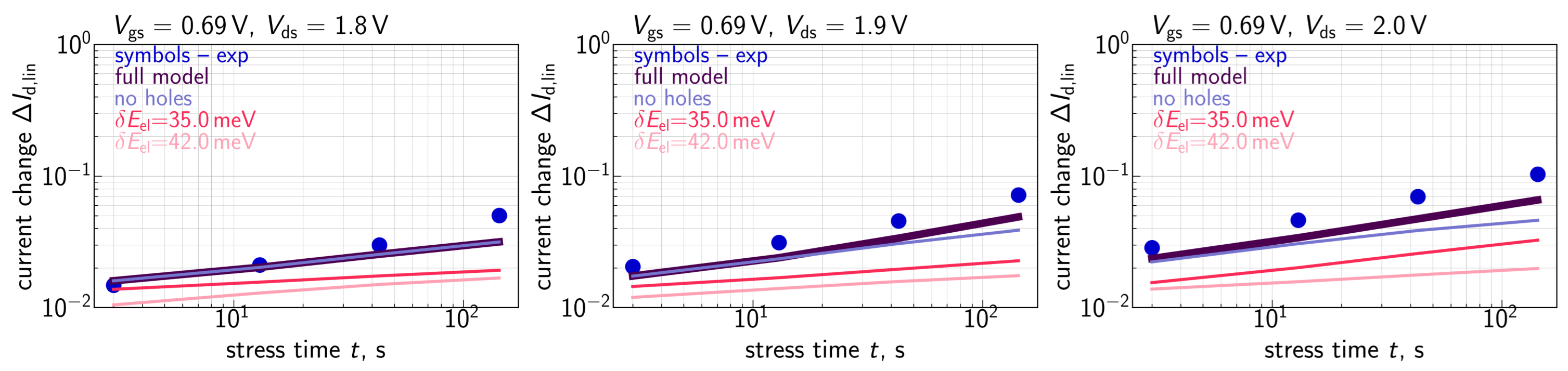

4. Degradation Characteristics

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| BTE | Boltzmann Transport Equation |

| BTI | Bias Temperature Instability |

| CPM | Compact Physics Model |

| HCD | Hot-Carrier Degradation |

| II | Impact Ionization |

| MC | Multiple-Carrier (mechanism of Si-H bond dissociation) |

| MOSFET | Metal-Oxide-Semiconductor Field Effect Transistor |

| SC | Single-Carrier (mechanism of Si-H bond dissociation) |

| WCC | Worst-Case Conditions (of hot-carrier degradation) |

References

- Ramey, S.; Ashutosh, A.; Auth, C.; Clifford, J.; Hattendorf, M.; Hicks, J.; James, R.; Rahman, A.; Sharma, V.; Amour, A.S.; et al. Intrinsic transistor reliability improvements from 22 nm tri-gate technology. In Proceedings of the 2013 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 14–18 April 2013; pp. 4C.5.1–4C.5.5. [Google Scholar] [CrossRef]

- Rahman, A.; Dacuna, J.; Nayak, P.; Leatherman, G.; Ramey, S. Reliability Studies of a 10 nm High-performance and Low-power CMOS Technology Featuring 3rd Generation FinFET and 5th Generation HK/MG. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018; pp. 6F.4-1–6F.4-6. [Google Scholar] [CrossRef]

- Paliwoda, P.; Chbili, Z.; Kerber, A.; Nigam, T.; Nagahiro, K.; Cimino, S.; Toledano-Luque, M.; Pantisano, L.; Min, B.W.; Misra, D. Self-Heating Effects on Hot Carrier Degradation and Its Impact on Logic Circuit Reliability. IEEE Trans. Device Mater. Reliab. 2019, 19, 249–254. [Google Scholar] [CrossRef]

- McMahon, W.; Matsuda, K.; Lee, J.; Hess, K.; Lyding, J. The Effects of a Multiple Carrier Model of Interface States Generation of Lifetime Extraction for MOSFETs. In Proceedings of the International Conference on Modeling and Simulation of Microsystem, San Juan, PR, USA, 23–25 April 2002; Volume 1, pp. 576–579. [Google Scholar]

- Haggag, A.; McMahon, W.; Hess, K.; Cheng, K.; Lee, J.; Lyding, J. High-performance Chip Reliability from Short-time-tests. In Statistical Models for Optical Interconnect and HCI/TDDB/NBTI Deep-Submicron Transistor Failures. In Proceedings of the International Reliability Physics Symposium (IRPS), Orlando, FL, USA, 30 April–3 May 2001; pp. 271–279. [Google Scholar]

- Reggiani, S.; Barone, G.; Poli, S.; Gnani, E.; Gnudi, A.; Baccarani, G.; Chuang, M.Y.; Tian, W.; Wise, R. TCAD Simulation of Hot-Carrier and Thermal Degradation in STI-LDMOS Transistors. IEEE Trans. Electron Devices 2013, 60, 691–698. [Google Scholar] [CrossRef]

- Reggiani, S.; Barone, G.; Gnani, E.; Gnudi, A.; Baccarani, G.; Poli, S.; Wise, R.; Chuang, M.Y.; Tian, W.; Pendharkar, S.; et al. Characterization and Modeling of Electrical Stress Degradation in STI-based Integrated Power Devices. Solid-State Electron. 2014, 102, 25–41. [Google Scholar] [CrossRef]

- Randriamihaja, Y.; Federspiel, X.; Huard, V.; Bravaix, A.; Palestri, P. New Hot Carrier Degradation Modeling Reconsidering the Role of EES in Ultra Short n-channel MOSFETs. In Proceedings of the International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 14–18 April 2013; pp. 1–5. [Google Scholar]

- Tyaginov, S.; Bina, M.; Franco, J.; Osintsev, D.; Triebl, O.; Kaczer, B.; Grasser, T. Physical Modeling of Hot-Carrier Degradation for Short- and Long-Channel MOSFETs. In Proceedings of the International Reliability Physics Symposium (IRPS), Waikoloa, HI, USA, 1–5 June 2014; pp. XT.16.1–XT.16.8. [Google Scholar]

- Zaka, A.; Rafhay, Q.; Iellina, M.; Palestri, P.; Clerc, R.; Rideau, D.; Garetto, D.; Singer, J.; Pananakakis, G.; Tavernier, C.; et al. On the accuracy of current TCAD hot carrier injection models in nanoscale devices. Solid State Electron. 2010, 54, 1669–1674. [Google Scholar] [CrossRef]

- Zaka, A.; Palestri, P.; Rafhay, Q.; Clerc, R.; Iellina, M.; Rideau, D.; Tavernier, C.; Pananakakis, G.; Jaouen, H.; Selmi, L. An Efficient Nonlocal Hot Electron Model Accounting for Electron-Electron Scattering. IEEE Trans. Electron Devices 2012, 59, 983–993. [Google Scholar] [CrossRef]

- Hu, C.; Tam, S.; Hsu, F.; Ko, P.K.; Chan, T.Y.; Terrill, K. Hot-electron-induced MOSFET Degradation Model, Monitor and Improvement. IEEE Trans. Electron Devices 1985, 48, 375–385. [Google Scholar]

- Hu, C.; Tam, S.; Hsu, F.C.; Ko, P.K.; Chan, T.Y.; Terrill, K. Hot-electron-induced MOSFET degradation—Model, monitor, and improvement. IEEE J. Solid State Circuits 1985, 20, 295–305. [Google Scholar]

- Moens, P.; van den Bosch, G.; Groeseneken, G. Competing Hot Carrier Degradation Mechanisms in Lateral n-type DMOS Transistors. In Proceedings of the International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 30 March–4 April 2003; pp. 214–221. [Google Scholar]

- Moens, P.; Bauwens, F.; Nelson, M.; Tack, M. Electron trapping and interface trap generation in drain extended pMOS transistors. In Proceedings of the International Reliability Physics Symposium (IRPS), San Jose, CA, USA, 17–21 April 2005; pp. 93–96. [Google Scholar]

- Moens, P.; van den Bosch, G. Characterization of total self-operating area of lateral DMOS transistors. IEEE Trans Electron Devices 2006, 6, 349–357. [Google Scholar]

- Penzin, O.; Haggag, A.; McMahon, W.; Lyumkis, E.; Hess, K. MOSFET Degradation Kinetics and Its Simulation. IEEE Trans. Electron Devices 2003, 50, 1445–1450. [Google Scholar] [CrossRef]

- Okhonin, S.; Hessler, T.; Dutoit, M. Comparison of gate-induced drain leakage and charge pumping measurements for determining lateral interface trap profiles in electrically stressed MOSFET’s. IEEE Trans. Electron Devices 1996, 43, 605–612. [Google Scholar] [CrossRef]

- Rauch, S.; La Rosa, G.; Guarin, F. Role of E-E Scattering in the Enhancement of Channel Hot Carrier Degradation of Deep-Submicron NMOSFETs at high Vgs Conditions. IEEE Trans. Device Material. Reliab. 2001, 1, 113–119. [Google Scholar] [CrossRef]

- Rauch, S.; Rosa, G.L. The Energy Driven Paradigm of NMOSFET Hot Carrier Effects. In Proceedings of the International Reliability Physics Symposium (IRPS), San Jose, CA, USA, 17–21 April 2005. [Google Scholar]

- Rauch, S.E.; Rosa, G.L. The energy-driven paradigm of NMOSFET hot-carrier effects. IEEE Trans. Device Mater. Reliab. 2005, 5, 701–705. [Google Scholar] [CrossRef]

- Tyaginov, S.; Grill, A.; Vandemaele, M.; Grasser, T.; Hellings, G.; Makarov, A.; Jech, M.; Linten, D.; Kaczer, B. A Compact Physics Analytical Model for Hot-Carrier Degradation. In Proceedings of the 2020 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April–30 May 2020; pp. 1–7. [Google Scholar] [CrossRef]

- Rzepa, G.; Franco, J.; O’Sullivan, B.; Subirats, A.; Simicic, M.; Hellings, G.; Weckx, P.; Jech, M.; Knobloch, T.; Waltl, M.; et al. Comphy—A compact-physics framework for unified modeling of BTI. Microelectron. Reliab. 2018, 85, 49–65. [Google Scholar] [CrossRef]

- Li, E.; Rosenbaum, E.; Tao, J.; Yeap, G.F.; Lin, M.; Fang, P. Hot-carrier Effects in nMOSFETs in 0.1 μm CMOS Technology. In Proceedings of the International Reliability Physics Symposium (IRPS), San Diego, CA, USA, 22–25 March 1999; pp. 253–258. [Google Scholar]

- Lin, C.; Biesemans, S.; Han, L.; Houlihan, K.; Schiml, T.; Schruefer, K.; Wann, C.; Markhopf, R. Hot Carrier Reliability for 0.13 μm CMOS Technology with Dual Gate Oxide Thickness. In Proceedings of the International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 10–13 December 2000; pp. 135–138. [Google Scholar]

- Woltjer, R.; Hamada, A.; Takeda, E. PMOSFET Hot Carrier Damage: Oxide Charge and Interface States. Semicond Sci. Technol. 1992, 7, B581–B584. [Google Scholar] [CrossRef]

- Tyaginov, S.; Starkov, I.; Enichlmair, H.; Park, J.; Jungemann, C.; Grasser, T. Physics-Based Hot-Carrier Degradation Models (invited). ECS Trans. 2011, 35, 321–352. [Google Scholar] [CrossRef]

- Lee, K.; Kaczer, B.; Kruv, A.; Gonzalez, M.; Degraeve, R.; Tyaginov, S.; Grill, A.; De Wolf, I. Hot-Electron-Induced Punch-Through (HEIP) Effect in p-MOSFET Enhanced by Mechanical Stress. IEEE Electron Device Lett. 2021, 42, 1424–1427. [Google Scholar] [CrossRef]

- Vandemaele, M.; Kaczer, B.; Tyaginov, S.; Stanojević, Z.; Makarov, A.; Chasin, A.; Bury, E.; Mertens, H.; Linten, D.; Groeseneken, G. Full (Vg, Vd) Bias Space Modeling of Hot-Carrier Degradation in Nanowire FETs. In Proceedings of the 2019 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 31 March–4 April 2019; pp. 1–7. [Google Scholar] [CrossRef]

- Jech, M.; Tyaginov, S.; Kaczer, B.; Franco, J.; Jabs, D.; Jungemann, C.; Waltl, M.; Grasser, T. First–Principles Parameter–Free Modeling of n– and p–FET Hot–Carrier Degradation. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 24.1.1–24.1.4. [Google Scholar] [CrossRef]

- Vuillaume, D.; Marchetaux, J.C.; Lippens, P.E.; Bravaix, A.; Boudou, A. A coupled study by floating-gate and charge-pumping techniques of hot carrier-induced defects in submicrometer LDD n-MOSFET’s. IEEE Trans. Electron Devices 1993, 40, 773–781. [Google Scholar] [CrossRef]

- Chen, J.; Chen, S.Y.; Wu, K.M.; Liu, C. Investigation of hot-carrier-induced degradation mechanisms in p-type high-voltage drain extended metal-oxide-semiconductor transistors. Jpn. J. Appl. Phys. 2009, 48, 04C039. [Google Scholar] [CrossRef]

- Starkov, I.; Enichlmair, H.; Tyaginov, S.; Grasser, T. Analysis of the Threshold Voltage Turn-Around Effect in High-Voltage n-MOSFETs due to Hot-Carrier Stress. In Proceedings of the International Reliability Physics Symposium (IRPS), Anaheim, CA, USA, 15–19 April 2012; p. 6. [Google Scholar]

- Starkov, I.; Starkov, A. Investigation of the threshold voltage turn-around effect in long-channel n-MOSFETs due to hot-carrier stress. Microelectron. Reliab. 2014, 54, 33–36. [Google Scholar] [CrossRef]

- Jung, S.G.; Lee, S.H.; Kim, C.K.; Yoo, M.S.; Yu, H.Y. Analysis of Drain Linear Current Turn-Around Effect in Off-State Stress Mode in pMOSFET. IEEE Electron Device Lett. 2020, 41, 804–807. [Google Scholar] [CrossRef]

- Cho, M.; Spessot, A.; Kaczer, B.; Aoulaiche, M.; Ritzenthaler, R.; Schram, T.; Fazan, P.; Horiguchi, N.; Linten, D. Off-state stress degradation mechanism on advanced p-MOSFETs. In Proceedings of the 2015 International Conference on IC Design Technology (ICICDT), Leuven, Belgium, 1–3 June 2015; pp. 1–4. [Google Scholar] [CrossRef]

- Spessot, A.; Aoulaiche, M.; Cho, M.; Franco, J.; Schram, T.; Ritzenthaler, R.; Kaczer, B. Impact of Off State Stress on advanced high-K metal gate NMOSFETs. In Proceedings of the 2014 44th European Solid State Device Research Conference (ESSDERC), Venice, Italy, 22–26 September 2014; pp. 365–368. [Google Scholar] [CrossRef]

- Jech, M.; Rott, G.A.; Reisinger, H.; Tyaginov, S.E.; Rzepa, G.; Grill, A.; Jabs, D.; Jungemann, C.; Waltl, M.; Grasser, T. Mixed Hot-Carrier/Bias Temperature Instability Degradation Regimes in Full {VG, VD} Bias Space: Implications and Peculiarities. IEEE Trans. Electron Devices 2020, 67, 3315–3322. [Google Scholar] [CrossRef]

- Gritsch, M. Numerical Modeling of Silicon-on-Insulator MOSFETs. Ph.D. Thesis, Technische Universität, Wien, Austria, 2002. [Google Scholar]

- Schenk, A. Advanced Physical Models for Silicon Device Simulations; Springer: Vienna, Austria, 1998. [Google Scholar]

- Lundstrom, M. Drift-diffusion and computational electronics—Still going strong after 40 years! In Proceedings of the 2015 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Washington, DC, USA, 9–11 September 2015; pp. 1–3. [Google Scholar] [CrossRef]

- Tyaginov, S.; Bury, E.; Grill, A.; Yu, Z.; Makarov, A.; De Keersgieter, A.; Vexler, M.; Vandemaele, M.; Wang, R.; Spessot, A.; et al. On The Contribution of Secondary Holes in Hot-Carrier Degradation—A Compact Physics Modeling Perspective. In Proceedings of the 7th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), Seoul, Republic of Korea, 7–10 March 2023; pp. 1–3. [Google Scholar] [CrossRef]

- Auth, C.; Allen, C.; Blattner, A.; Bergstrom, D.; Brazier, M.; Bost, M.; Buehler, M.; Chikarmane, V.; Ghani, T.; Glassman, T.; et al. A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors. In Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 12–14 June 2012; pp. 131–132. [Google Scholar] [CrossRef]

- Ferain, I.; Colinge, C.; Colinge, J.-P. Multigate transistors as the future of classical metal-oxide-semiconductor field-effect transistors. Nature 2011, 479, 310–316. [Google Scholar] [CrossRef] [PubMed]

- Colinge, J.-P.; Lee, C.-W.; Afzalian, A.; Akhavan, N.D.; Yan, R.; Ferain, I.; Razavi, P.; O’Neill, B.; Blake, A.; White, M.; et al. Nanowire transistors without junctions. Nat. Nano 2010, 5, 225–229. [Google Scholar] [CrossRef] [PubMed]

- Kuhn, K.J. Considerations for Ultimate CMOS Scaling. IEEE Trans. Electron Devices 2012, 59, 1813–1828. [Google Scholar] [CrossRef]

- Barraud, S.; Lapras, V.; Previtali, B.; Samson, M.P.; Lacord, J.; Martinie, S.; Jaud, M.A.; Athanasiou, S.; Triozon, F.; Rozeau, O.; et al. Performance and design considerations for gate-all-around stacked-NanoWires FETs. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 29.2.1–29.2.4. [Google Scholar] [CrossRef]

- Nagy, D.; Espiñeira, G.; Indalecio, G.; García-Loureiro, A.J.; Kalna, K.; Seoane, N. Benchmarking of FinFET, Nanosheet, and Nanowire FET Architectures for Future Technology Nodes. IEEE Access 2020, 8, 53196–53202. [Google Scholar] [CrossRef]

- Weckx, P.; Ryckaert, J.; Putcha, V.; De Keersgieter, A.; Boemmels, J.; Schuddinck, P.; Jang, D.; Yakimets, D.; Bardon, M.G.; Ragnarsson, L.Å.; et al. Stacked nanosheet fork architecture for SRAM design and device co-optimization toward 3 nm. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 20.5.1–20.5.4. [Google Scholar] [CrossRef]

- Zhang, J.; Frougier, J.; Greene, A.; Miao, X.; Yu, L.; Vega, R.; Montanini, P.; Durfee, C.; Gaul, A.; Pancharatnam, S.; et al. Full Bottom Dielectric Isolation to Enable Stacked Nanosheet Transistor for Low Power and High Performance Applications. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 11.6.1–11.6.4. [Google Scholar] [CrossRef]

- Ritzenthaler, R.; Mertens, H.; Eneman, G.; Simoen, E.; Bury, E.; Eyben, P.; Bufler, F.M.; Oniki, Y.; Briggs, B.; Chan, B.; et al. Comparison of Electrical Performance of Co-Integrated Forksheets and Nanosheets Transistors for the 2 nm Technological Node and Beyond. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 13–15 December 2021; pp. 26.2.1–26.2.4. [Google Scholar] [CrossRef]

- Ryckaert, J.; Schuddinck, P.; Weckx, P.; Bouche, G.; Vincent, B.; Smith, J.; Sherazi, Y.; Mallik, A.; Mertens, H.; Demuynck, S.; et al. The Complementary FET (CFET) for CMOS scaling beyond N3. In Proceedings of the 2018 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 18–22 June 2018; pp. 141–142. [Google Scholar] [CrossRef]

- Liebmann, L.; Smith, J.; Chanemougame, D.; Gutwin, P. CFET Design Options, Challenges, and Opportunities for 3D Integration. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 13–15 December 2021; pp. 3.1.1–3.1.4. [Google Scholar] [CrossRef]

- Bury, E.; Kaczer, B.; Chuang, K.; Franco, J.; Weckx, P.; Chasin, A.; Simicic, M.; Linten, D.; Groeseneken, G. Statistical assessment of the full VG/VD degradation space using dedicated device arrays. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017; pp. 2D–5.1–2D–5.6. [Google Scholar] [CrossRef]

- Grill, A.; Bury, E.; Michl, J.; Tyaginov, S.; Linten, D.; Grasser, T.; Parvais, B.; Kaczer, B.; Waltl, M.; Radu, I. Reliability and Variability of Advanced CMOS Devices at Cryogenic Temperatures. In Proceedings of the International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April–30 May 2020; pp. 5C.3.1–5C.3.1.6. [Google Scholar]

- Krick, J.; Lenahan, P.; Dunn, G. Direct observation of interfacial point defects generated by channel hot hole injection in nchannel metal oxide silicon field effect transistors. Appl. Phys. Lett. 1991, 59, 3437–3439. [Google Scholar] [CrossRef]

- Billman, C.; Lenahan, P.; Weber, W. Identification of the Microscopic Structure of New Hot Carrier Damage in Short Channel MOSFETs. Microelectron. Eng. 1997, 36, 271–272. [Google Scholar] [CrossRef]

- Lenahan, P. Atomic Scale Defects Involved in MOS Reliability Problems. Microelectron. Eng. 2003, 69, 173–181. [Google Scholar] [CrossRef]

- Helms, C.R.; Poindexter, E.H. The Silicon-Silicon Dioxide System: Its Microstructure and Imperfections. Rep. Prog. Phys. 1994, 57, 791. [Google Scholar] [CrossRef]

- Stesmans, A. Passivation of Pb0 and Pb1 Interface Defects in Thermal (100) Si/SiO2 with Molecular Hydrogen. Appl. Phys. Lett. 1996, 68, 2076–2078. [Google Scholar] [CrossRef]

- Pobegen, G.; Tyaginov, S.; Nelhiebel, M.; Grasser, T. Observation of Normally Distributed Activation Energies for the Recovery from Hot Carrier Damage. IEEE Electron Device Lett. 2013, 34, 939–941. [Google Scholar] [CrossRef]

- de Jong, M.J.; Salm, C.; Schmitz, J. Towards Understanding Recovery of Hot-Carrier Induced Degradation. Microelectron. Reliab. 2018, 88–90, 147–151. [Google Scholar] [CrossRef]

- de Jong, M.J.; Salm, C.; Schmitz, J. Effect of Ambient on the Recovery of Hot-Carrier Degraded Devices. In Proceedings of the 2020 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April–30 May 2020; pp. 1–6. [Google Scholar]

- Vandemaele, M.; Chuang, K.H.; Bury, E.; Tyaginov, S.; Groeseneken, G.; Kaczer, B. The Influence of Gate Bias on the Anneal of Hot-Carrier Degradation. In Proceedings of the International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April–30 May 2020; pp. 5A.3.1–5A.3.7. [Google Scholar] [CrossRef]

- Reisinger, H.; Blank, O.; Heinrigs, W.; Muhlhoff, A.; Gustin, W.; Schlunder, C. Analysis of NBTI Degradation- and Recovery-Behavior Based on Ultra Fast VT-Measurements. In Proceedings of the 2006 IEEE International Reliability Physics Symposium, San Jose, CA, USA, 26–30 March 2006; pp. 448–453. [Google Scholar] [CrossRef]

- Grasser, T.; Kaczer, B.; Gös, W.; Reisinger, H.; Aichinger, T.; Hehenberger, P.; Wagner, P.J.; Franco, J.; Toledano-Luque, M.; Nelhiebel, M. The Paradigm Shift in Understanding the Bias Temperature Instability: From Reaction-Diffusion to Switching Oxide Traps. IEEE Trans. Electron Devices 2011, 58, 3652–3666. [Google Scholar] [CrossRef]

- Grasser, T.; Kaczer, B.; Goes, W.; Reisinger, H.; Aichinger, T.; Hehenberger, P.; Wagner, P.J.; Schanowsky, F.; Franco, J.; Roussel, P.; et al. Recent Advances in Understanding the Bias Temperature Instability. In Proceedings of the International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 6–8 December 2010; pp. 82–85. [Google Scholar]

- Bravaix, A.; Guerin, C.; Huard, V.; Roy, D.; Roux, J.; Vincent, E. Hot-carrier Acceleration Factors for Low Power Management in DC-AC Stressed 40 nm NMOS Node at High Temperature. In Proceedings of the International Reliability Physics Symposium (IRPS), Montreal, QC, Canada, 26–30 April 2009; pp. 531–546. [Google Scholar] [CrossRef]

- Hess, K.; Register, L.; Tuttle, B.; Lyding, J.; Kizilyalli, I. Impact of Nanostructure Research on Conventional Solid-State Electronics: The Giant Isotope Effect in Hydrogen Desorption and CMOS Lifetime. Physica E 1998, 3, 1–7. [Google Scholar] [CrossRef]

- Sharma, P.; Tyaginov, S.; Jech, M.; Wimmer, Y.; Rudolf, F.; Enichlmair, H.; Park, J.M.; Ceric, H.; Grasser, T. The role of cold carriers and the multiple-carrier process of Si–H bond dissociation for hot-carrier degradation in n- and p-channel {LDMOS} devices. Solid State Electron. 2016, 115 Pt B, 185–191. [Google Scholar] [CrossRef]

- Tallarico, A.N.; Reggiani, S.; Depetro, R.; Torti, A.M.; Croce, G.; Sangiorgi, E.; Fiegna, C. Hot-Carrier Degradation in Power LDMOS: Selective LOCOS- Versus STI-Based Architecture. IEEE J. Electron Devices Soc. 2018, 6, 219–226. [Google Scholar] [CrossRef]

- Kerber, A.; Nigam, T.; Paliwoda, P.; Guarin, F. Reliability Characterization of Ring Oscillator Circuits for Advanced CMOS Technologies. IEEE Trans. Device Mater. Reliab. 2020, 20, 230–241. [Google Scholar] [CrossRef]

- Bravaix, A.; Huard, V.; Goguenheim, D.; Vincent, E. Hot-Carrier to Cold-Carrier Device Lifetime Modeling with Temperature for Low power 40 nm Si-Bulk NMOS and PMOS FETs. In Proceedings of the International Electron Devices Meeting (IEDM), Washington, DC, USA, 5–7 December 2011; pp. 622–625. [Google Scholar]

- Bina, M.; Tyaginov, S.; Franco, J.; Rupp, K.; Wimmer, Y.; Osinstev, D.; Kaczer, B.; Grasser, T. Predictive Hot-Carrier Modeling of n-channel MOSFETs. IEEE Trans. Electron Devices 2014, 61, 3103–3110. [Google Scholar] [CrossRef]

- Varghese, D.; Alam, M.A.; Weir, B. A generalized, IB-independent, physical HCI lifetime projection methodology based on universality of hot-carrier degradation. In Proceedings of the 2010 IEEE International Reliability Physics Symposium, Anaheim, CA, USA, 2–6 May 2010; pp. 1091–1094. [Google Scholar] [CrossRef]

- Yamagata, M.; Satoh, T.; Tango, H. Hot-Carrier-Induced Degradation under Current Saturation Bias in p-Channel Low-Temperature Polycrystalline Silicon Thin-Film Transistors. JPN J. Appl. Phys. 2007, 46, 5044. [Google Scholar] [CrossRef]

- Makarov, A.; Tyaginov, S.E.; Kaczer, B.; Jech, M.; Chasin, A.; Grill, A.; Hellings, G.; Vexler, M.I.; Linten, D.; Grasser, T. Hot-Carrier Degradation in FinFETs: Modeling, Peculiarities, and Impact of Device Topology. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 13.1.1–13.1.4. [Google Scholar] [CrossRef]

- Tyaginov, S.; Jech, M.; Franco, J.; Sharma, P.; Kaczer, B.; Grasser, T. Understanding and Modeling the Temperature Behavior of Hot-Carrier Degradation in SiON nMOSFETs. IEEE Electron Device Lett. 2016, 37, 84–87. [Google Scholar] [CrossRef]

- McMahon, W.; Haggag, A.; Hess, K. Reliability Scaling Issues for Nanoscale Devices. IEEE Trans. Nanotech. 2003, 2, 33–38. [Google Scholar] [CrossRef]

- Haggag, A.; Lemanski, M.; Anderson, G.; Abramowitz, P.; Moosa, M. Realistic Projections of Product Fmax Shift and Statistics due to HCI and NBTI. In Proceedings of the 2007 IEEE 45th Annual International Reliability Physics Symposium, Phoenix, AZ, USA, 15–19 April 2007; pp. 93–96. [Google Scholar] [CrossRef]

- ViennaSHE. 2014. Available online: http://viennashe.sourceforge.net/ (accessed on 5 October 2023).

- Rupp, K.; Jungel, A.; Grasser, T. Matrix compression for spherical harmonics expansions of the Boltzmann transport equation for semiconductors. J. Comput. Phys. 2010, 229, 8750–8765. [Google Scholar] [CrossRef]

- Rupp, K.; Grasser, T.; Jüngel, A. On the Feasibility of Spherical Harmonics Expansions of the Boltzmann Transport Equation for Three-Dimensional Device Geometries. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 34.1.1–34.1.4. [Google Scholar] [CrossRef]

- Rupp, K.; Jungemann, C.; Hong, S.M.; Bina, M.; Grasser, T.; Jüngel, A. A Review of Recent Advances in the Spherical Harmonics Expansion Method for Semiconductor Device Simulation. J. Comput. Electron. 2016, 15, 939–958. [Google Scholar] [CrossRef]

- Gnudi, A.; Ventura, D.; Baccarani, G. One-Dimensional Simulation of a Bipolar Transistor by means of Spherical Harmonics Expansion of the Boltzmann Transport Equation. In Proceedings of the Simulation of Semiconductor Devices and Processes (SISDEP), Zurich, Switzerland, 12–14 September 1991; Volume 4, pp. 205–213. [Google Scholar]

- Hong, S.M.; Jungemann, C. A fully coupled scheme for a Boltzmann-Poisson equation solver based on a spherical harmonics expansion. J. Comput. Electron. 2009, 8, 225–241. [Google Scholar] [CrossRef]

- Hong, S.M.; Pham, A.; Jungemann, C. Deterministic Solvers for the Boltzmann Transport Equation; Springer: Vienna, Austria, 2011. [Google Scholar]

- Grasser, T.; Kosina, H.; Heitzinger, C.; Selberherr, S. Accurate Impact Ionization Model which Accounts for Hot and Cold Carrier Populations. Appl. Phys. Lett. 2002, 80, 613–615. [Google Scholar] [CrossRef][Green Version]

- Selmi, L.; Sangiorgi, E.; Bez, R.; Ricco, B. Measurement of the hot hole injection probability from Si into SiO2 in p-MOSFETs. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 5–8 December 1993; pp. 333–336. [Google Scholar] [CrossRef]

- Tyaginov, S.; Bina, M.; Franco, J.; Wimmer, Y.; Osintsev, D.; Kaczer, B.; Grasser, T. A Predictive Physical Model for Hot-Carrier Degradation in Ultra-Scaled MOSFETs. In Proceedings of the Simulation of Semiconductor Processes and Devices (SISPAD), Yokohama, Japan, 9–11 September 2014; pp. 89–92. [Google Scholar]

- Vecchi, M.C.; Rudan, M. Modeling electron and hole transport with full-band structure effects by means of the Spherical-Harmonics Expansion of the BTE. IEEE Trans. Electron Devices 1998, 45, 230–238. [Google Scholar] [CrossRef]

- Fischetti, M.V.; Yoder, P.D.; Khatami, M.M.; Gaddemane, G.; Van de Put, M.L. “Hot Electrons in Si Lose Energy Mostly to Optical Phonons”: Truth or Myth? Appl. Phys. Lett. 2019, 114, 222104. [Google Scholar] [CrossRef]

- Tandon, N.; Albrecht, J.D.; Ram-Mohan, L.R. Electron-Phonon Interaction and Scattering in Si and Ge: Implications for Phonon Engineering. J. Appl. Phys. 2015, 118, 045713. [Google Scholar] [CrossRef]

- Qiu, B.; Tian, Z.; Vallabhaneni, A.; Liao, B.; Mendoza, J.M.; Restrepo, O.D.; Ruan, X.; Chen, G. First-Principles Simulation of Electron Mean-Free-Path Spectra and Thermoelectric Properties in Silicon. Europhys. Lett. 2015, 109, 57006. [Google Scholar] [CrossRef]

- Jungemann, C.; Meinerzhagen, B. Hierarchical Device Simulation; Springer: Wien, Austria, 2003. [Google Scholar]

- Jacoboni, C.; Lugli, P. The Monte Carlo Method for Semiconductor Device Simulation; Springer: Wien, Austria, 1989. [Google Scholar]

- Sze, S.; Ng, K. Physics of Semiconductor Devices; Wiley-Interscience: Hoboken, NJ, USA, 2007. [Google Scholar]

- Leblebici, Y.; Kang, S.M. Modeling of nMOS Transistors for Simulation of Hot-Carrier Induced Device and Circuit Degradation. IEEE Trans. Comput. Aided Des. 1992, 11, 235–246. [Google Scholar] [CrossRef]

- Acovic, A.; Rosa, G.L.; Sun, Y. A Review of Hot Carrier Degradation Mechanism in MOSFETs. Microel. Reliab. 1996, 36, 845–869. [Google Scholar] [CrossRef]

- Ancona, M.G.; Saks, N.S.; McCarthy, D. Lateral distribution of hot-carrier-induced interface traps in MOSFETs. IEEE Trans. Electron Devices 1988, 35, 2221–2228. [Google Scholar] [CrossRef]

- Varghese, D.; Kufluoglu, H.; Reddy, V.; Shichijo, H.; Krishnan, S.; Alam, M.A. Universality of Off-State Degradation in Drain Extended NMOS Transistors. In Proceedings of the 2006 International Electron Devices Meeting, San Francisco, CA, USA, 11–13 December 2006; pp. 1–4. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tyaginov, S.; Bury, E.; Grill, A.; Yu, Z.; Makarov, A.; De Keersgieter, A.; Vexler, M.; Vandemaele, M.; Wang, R.; Spessot, A.; et al. Compact Physics Hot-Carrier Degradation Model Valid over a Wide Bias Range. Micromachines 2023, 14, 2018. https://doi.org/10.3390/mi14112018

Tyaginov S, Bury E, Grill A, Yu Z, Makarov A, De Keersgieter A, Vexler M, Vandemaele M, Wang R, Spessot A, et al. Compact Physics Hot-Carrier Degradation Model Valid over a Wide Bias Range. Micromachines. 2023; 14(11):2018. https://doi.org/10.3390/mi14112018

Chicago/Turabian StyleTyaginov, Stanislav, Erik Bury, Alexander Grill, Zhuoqing Yu, Alexander Makarov, An De Keersgieter, Mikhail Vexler, Michiel Vandemaele, Runsheng Wang, Alessio Spessot, and et al. 2023. "Compact Physics Hot-Carrier Degradation Model Valid over a Wide Bias Range" Micromachines 14, no. 11: 2018. https://doi.org/10.3390/mi14112018

APA StyleTyaginov, S., Bury, E., Grill, A., Yu, Z., Makarov, A., De Keersgieter, A., Vexler, M., Vandemaele, M., Wang, R., Spessot, A., Chasin, A., & Kaczer, B. (2023). Compact Physics Hot-Carrier Degradation Model Valid over a Wide Bias Range. Micromachines, 14(11), 2018. https://doi.org/10.3390/mi14112018