Heterogeneous CMOS Integration of InGaAs-OI nMOSFETs and Ge pMOSFETs Based on Dual-Gate Oxide Technique

Abstract

1. Introduction

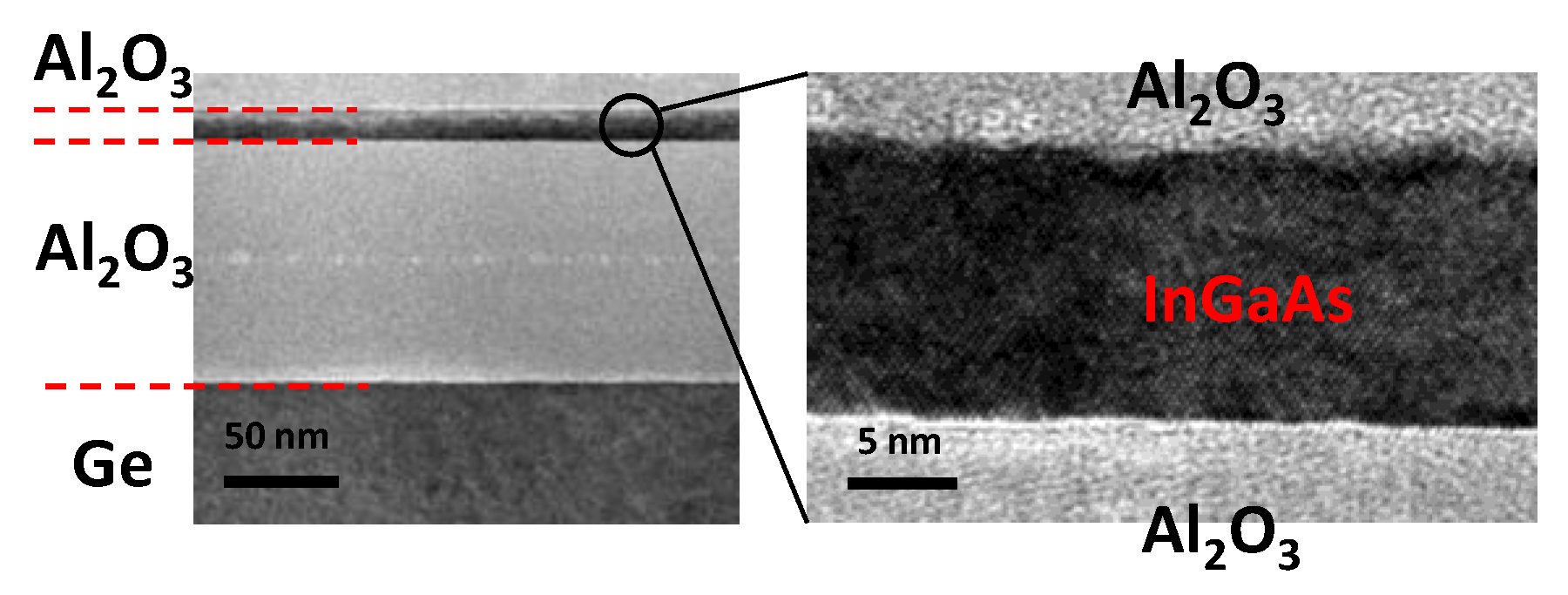

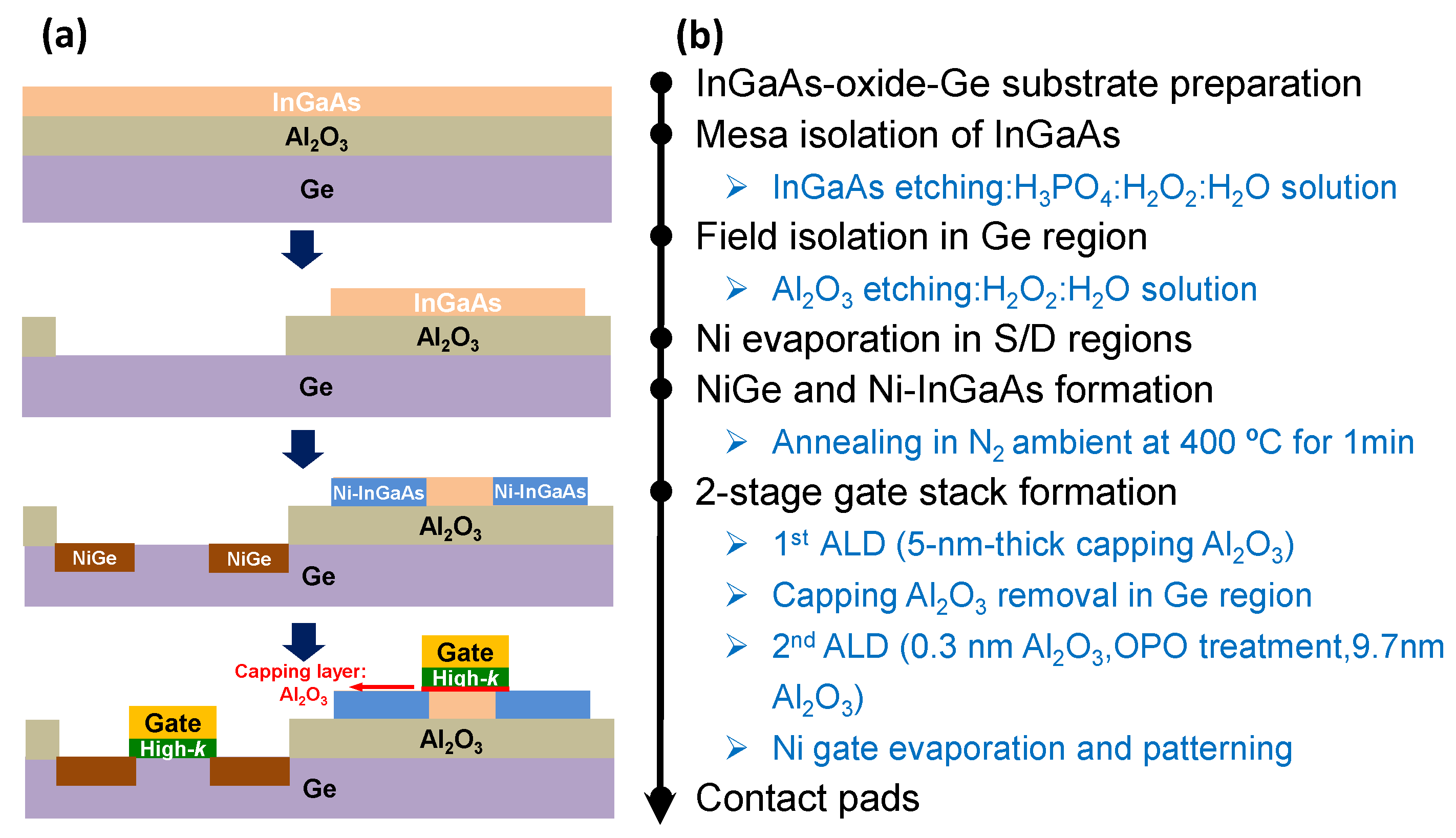

2. Experiments

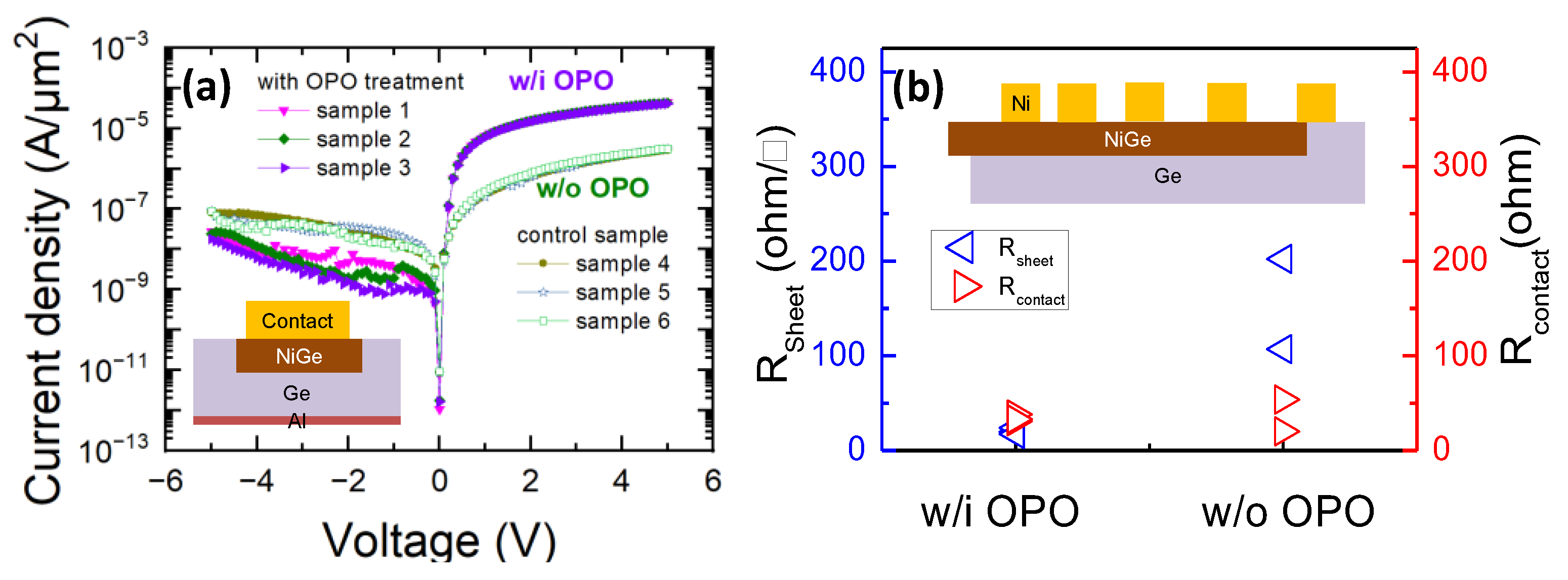

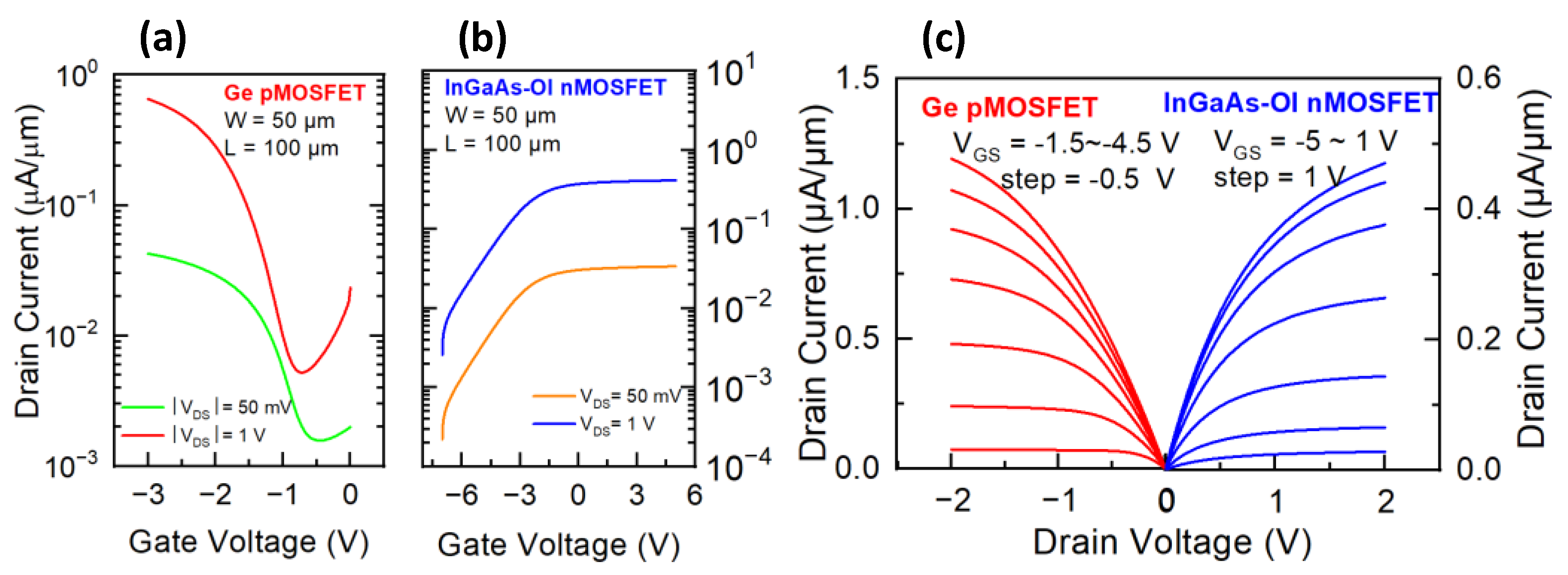

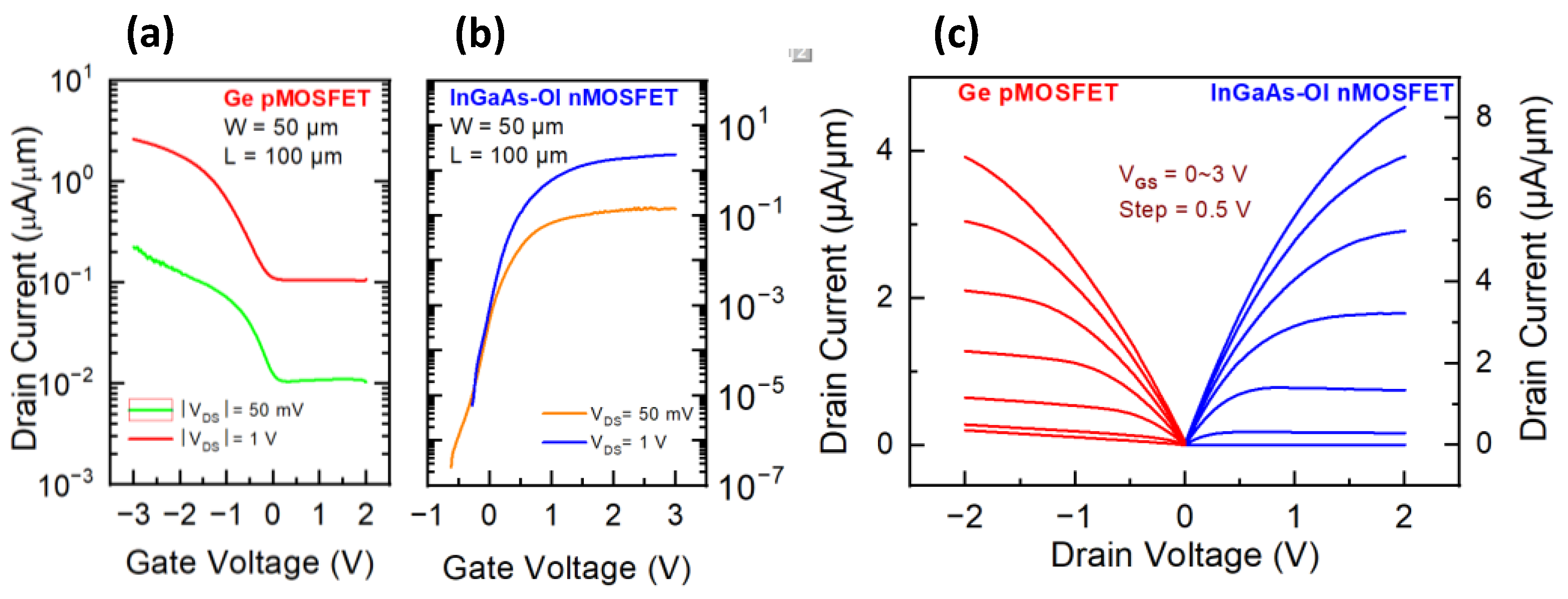

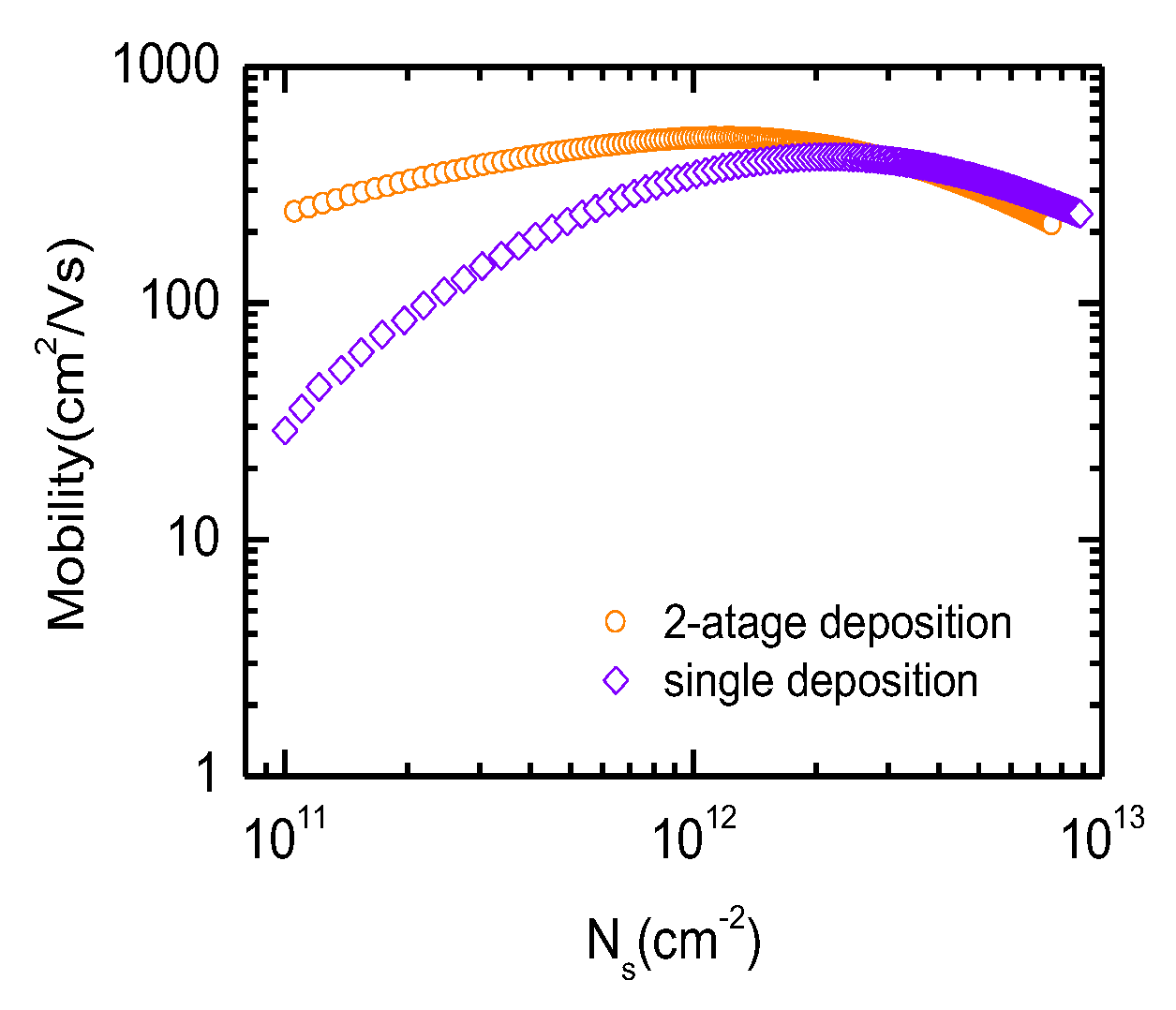

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Chu, C.L.; Wu, K.; Luo, G.L.; Chen, B.Y.; Chen, S.H.; Wu, W.F.; Yeh, W.K. Stacked Ge-Nanosheet GAAFETs Fabricated by Ge/Si Multilayer Epitaxy. IEEE Electron Devices Lett. 2018, 39, 1133–1136. [Google Scholar] [CrossRef]

- Memisevic, E.; Svensson, J.; Lind, E.; Wernersson, L.E. Vertical Nanowire TFETs With Channel Diameter Down to 10 nm and Point SMIN of 35 mV/Decade. IEEE Electron Devices Lett. 2018, 39, 1089–1091. [Google Scholar] [CrossRef]

- Llinas, J.P.; Fairbrother, A.; Borin Barin, G.; Shi, W.; Lee, K.; Wu, S.; Yong Choi, B.; Braganza, R.; Lear, J.; Kau, N.; et al. Short-channel field-effect transistors with 9-atom and 13-atom wide graphene nanoribbons. Nat. Commun. 2017, 8, 633. [Google Scholar] [CrossRef] [PubMed]

- Yakimets, D.; Eneman, G.; Schuddinck, P.; Bao, T.H.; Bardon, M.G.; Raghavan, P.; De Meyer, K. Vertical GAAFETs for the Ultimate CMOS Scaling. IEEE Trans. Electron Devices 2015, 62, 1433–1439. [Google Scholar] [CrossRef]

- Takagi, S.; Tezuka, T.; Irisawa, T.; Nakaharai, K.; Numata, T.; Usuda, K.; Sugiyama, N.; Suichijo, M.; Nakane, R.; Sugahara, S. Device structures and carrier transport properties of advanced CMOS using high mobility channels. Solid-State Electron. 2007, 51, 526–536. [Google Scholar] [CrossRef]

- Del Alamo, J.A. Nanometre-scale electronics with III-V compound semiconductors. Nature 2011, 479, 317–323. [Google Scholar] [CrossRef] [PubMed]

- Nishimura, T.; Kita, K.; Toriumi, A. Evidence for strong Fermi-level pinning due to metal-induced gap states at metal/germanium interface. Appl. Phys. Lett. 2007, 91, 123123. [Google Scholar] [CrossRef]

- Zhang, R.; Tang, X.; Yu, X.; Li, J.; Zhao, Y. Aggressive EOT Scaling of Ge pMOSFETs With HfO2/AlOx/GeOx Gate-Stacks Fabricated by Ozone Postoxidation. IEEE Electron Device Lett. 2016, 37, 831–834. [Google Scholar] [CrossRef]

- Lee, C.H.; Nishimura, T.; Nagashio, K.; Kita, K.; Toriumi, A. High-Electron-Mobility Ge/GeO2 n-MOSFETs With Two-Step Oxidation. IEEE Trans. Electron Devices 2011, 58, 1295–1301. [Google Scholar]

- Gu, J.J.; Liu, Y.Q.; Wu, Y.Q.; Colby, R.; Gordon, R.G.; Ye, P.D. First experimental demonstration of gate-all-around III–V MOSFETs by top-down approach. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 33–42. [Google Scholar]

- Irisawa, T.; Oda, M.; Kamimuta, Y.; Moriyama, Y.; Ikeda, K.; Mieda, E.; Jevasuwan, W.; Maeda, T.; Ichikawa, O.; Osada, T.; et al. Demonstration of InGaAs/Ge dual channel CMOS inverters with high electron and hole mobility using staked 3D integration. In Proceedings of the 2013 Symposium on VLSI Technology, Kyoto, Japan, 11–13 June 2013; pp. T56–T57. [Google Scholar]

- Maeda, T.; Urabe, Y.; Itatani, T.; Ishii, H.; Miyata, N.; Yasuda, T.; Yamada, H.; Hata, M.; Yokoyama, M.; Takenaka, M.; et al. Scalable TaN metal source/drain & gate InGaAs/Ge n/pMOSFETs. In Proceedings of the 2011 Symposium on VLSI Technology-Digest of Technical Papers, Kyoto, Japan, 14–16 June 2011; pp. 62–63. [Google Scholar]

- Yokoyama, M.; Kim, S.H.; Zhang, R.; Taoka, N.; Urabe, Y.; Maeda, T.; Takagi, H.; Yasuda, T.; Yamada, H.; Ichikawa, O.; et al. CMOS integration of InGaAs nMOSFETs and Ge pMOSFETs with self-align Ni-based metal S/D using direct wafer bonding. In Proceedings of the 2011 Symposium on VLSI Technology-Digest of Technical Papers, Kyoto, Japan, 14–16 June 2011; pp. 60–61. [Google Scholar]

- Czornomaz, L.; Deshpande, V.V.; O’Connor, E.; Caimi, D.; Sousa, M.; Fompeyrine, J. Bringing III-Vs into CMOS: From Materials to Circuits. ECS Trans. 2017, 77, 173. [Google Scholar] [CrossRef]

- Jevasuwan, W.; Urabe, Y.; Maeda, T.; Miyata, N.; Yasuda, T.; Yamada, H.; Hata, M.; Taoka, N.; Takenaka, M.; Takagi, S. Initial Processes of Atomic Layer Deposition of Al2O3 on InGaAs: Interface Formation Mechanisms and Impact on Metal-Insulator-Semiconductor Device Performance. Materials 2012, 5, 404–414. [Google Scholar] [CrossRef] [PubMed]

- Chang, C.H.; Chiou, Y.K.; Chang, Y.C.; Lee, K.Y.; Lin, T.D.; Wu, T.B.; Hong, M.; Kwo, J. Interfacial self-cleaning in atomic layer deposition of HfO2 gate dielectric on In0.15Ga0.85As. Appl. Phys. Lett. 2006, 89, 242911. [Google Scholar] [CrossRef]

- Kim, S.H.; Yokoyama, M.; Taoka, N.; Iida, R.; Lee, S.; Nakane, R.; Urabe, Y.; Miyata, N.; Yasuda, T.; Yamada, H.; et al. Self-aligned metal source/drain InxGa1− xAs n-MOSFETs using Ni-InGaAs alloy. In Proceedings of the 2010 International Electron Devices Meeting, Francisco, CA, USA, 6–8 December 2010; pp. 26–36. [Google Scholar]

- Tang, X.Y.; Lu, J.W.; Zhang, R.; Wu, W.R.; Liu, C.; Shi, Y.; Huang, Z.Q.; Kong, Y.C.; Zhao, Y. Positive Bias Temperature Instability and Hot Carrier Injection of Back Gate Ultra-thin-body In0.53Ga0.47As-on-Insulator n-Channel Metal-Oxide-Semiconductor Field-Effect Transistor. Chin. Phys. Lett. 2015, 32, 117302. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tang, X.; Hua, T.; Liu, Y.; Han, Z. Heterogeneous CMOS Integration of InGaAs-OI nMOSFETs and Ge pMOSFETs Based on Dual-Gate Oxide Technique. Micromachines 2022, 13, 1806. https://doi.org/10.3390/mi13111806

Tang X, Hua T, Liu Y, Han Z. Heterogeneous CMOS Integration of InGaAs-OI nMOSFETs and Ge pMOSFETs Based on Dual-Gate Oxide Technique. Micromachines. 2022; 13(11):1806. https://doi.org/10.3390/mi13111806

Chicago/Turabian StyleTang, Xiaoyu, Tao Hua, Yujie Liu, and Zhezhe Han. 2022. "Heterogeneous CMOS Integration of InGaAs-OI nMOSFETs and Ge pMOSFETs Based on Dual-Gate Oxide Technique" Micromachines 13, no. 11: 1806. https://doi.org/10.3390/mi13111806

APA StyleTang, X., Hua, T., Liu, Y., & Han, Z. (2022). Heterogeneous CMOS Integration of InGaAs-OI nMOSFETs and Ge pMOSFETs Based on Dual-Gate Oxide Technique. Micromachines, 13(11), 1806. https://doi.org/10.3390/mi13111806