Reduced Dislocation of GaAs Layer Grown on Ge-Buffered Si (001) Substrate Using Dislocation Filter Layers for an O-Band InAs/GaAs Quantum Dot Narrow-Ridge Laser

Abstract

1. Introduction

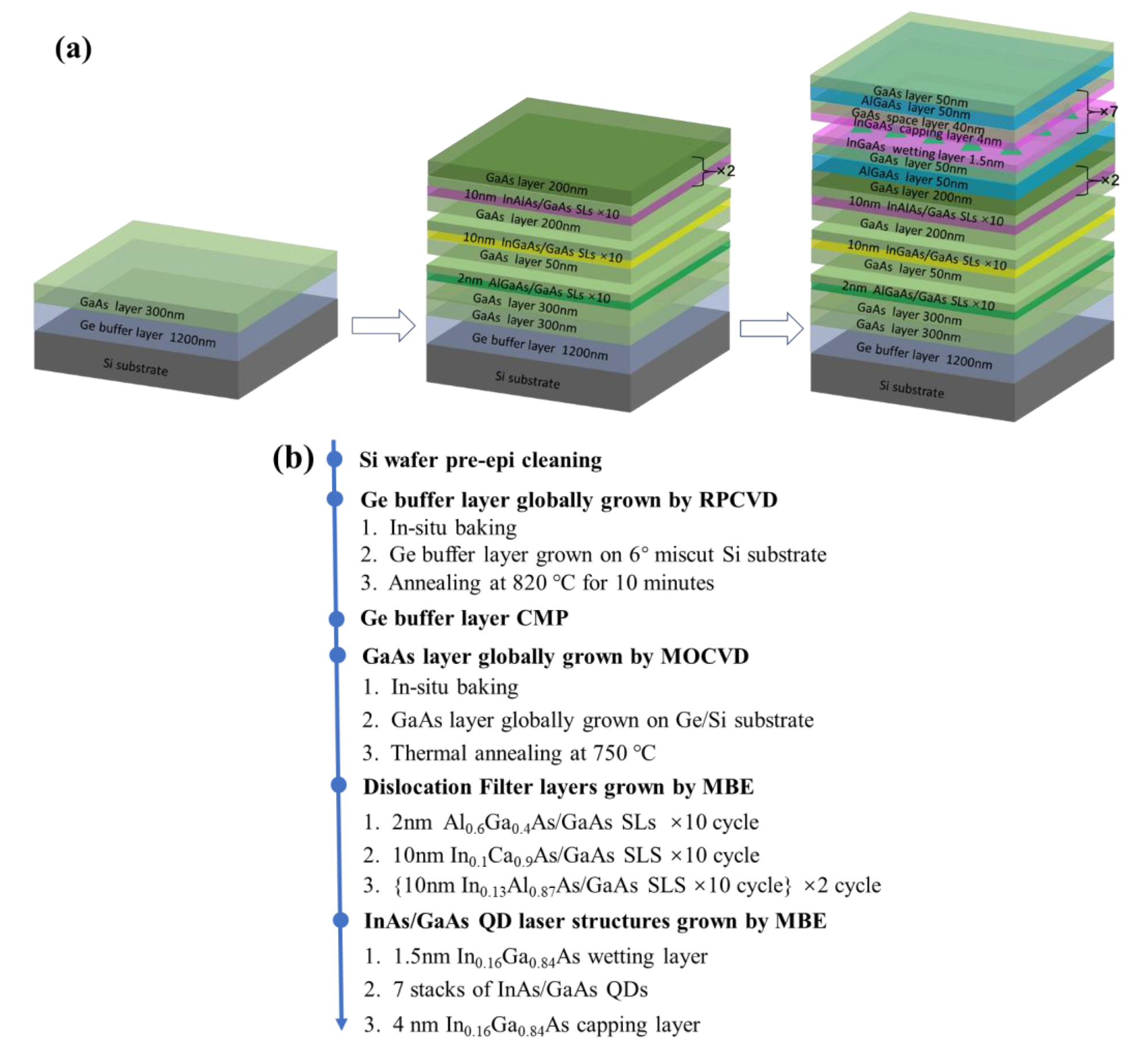

2. Experimental Details

3. Results and Discussion

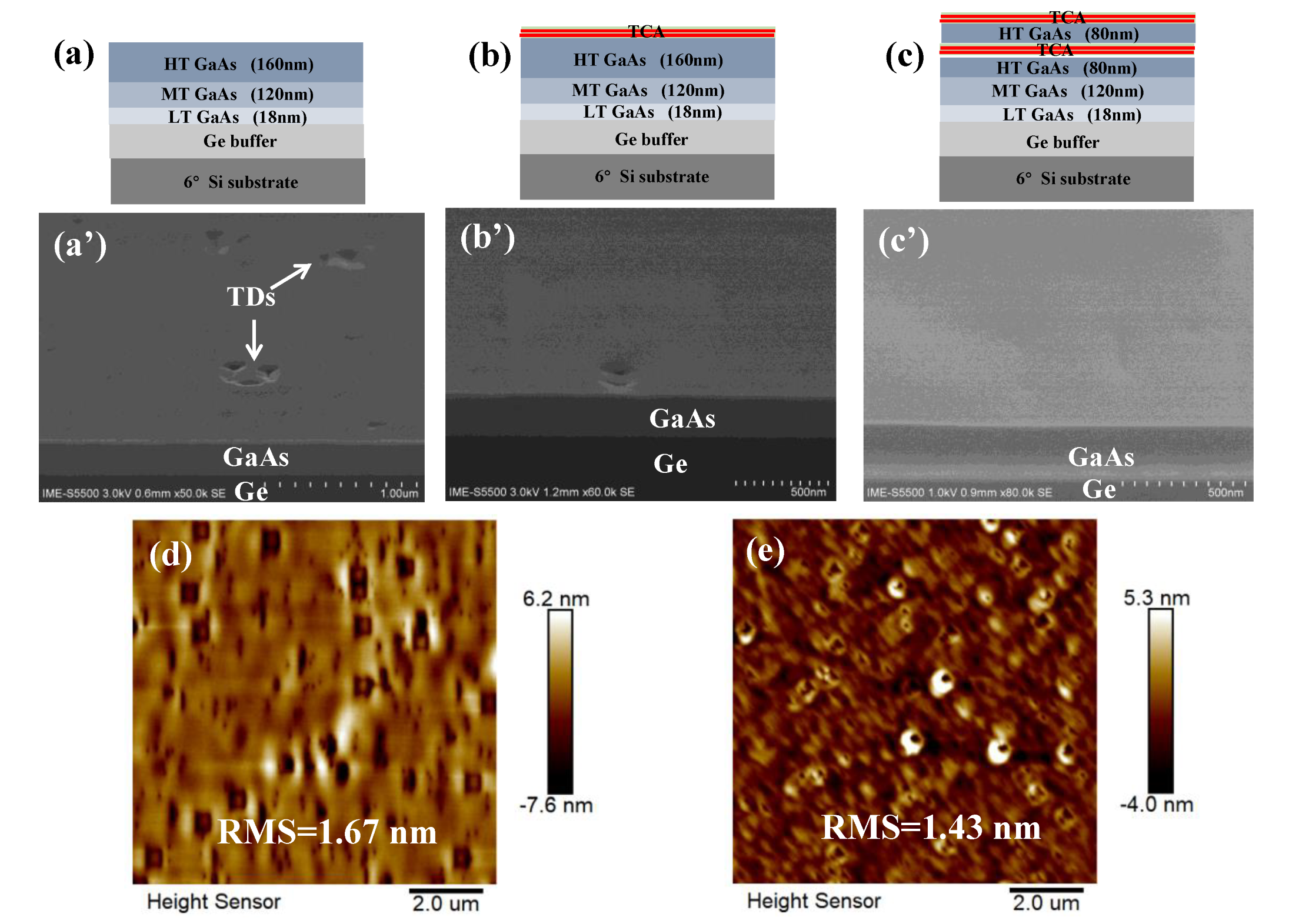

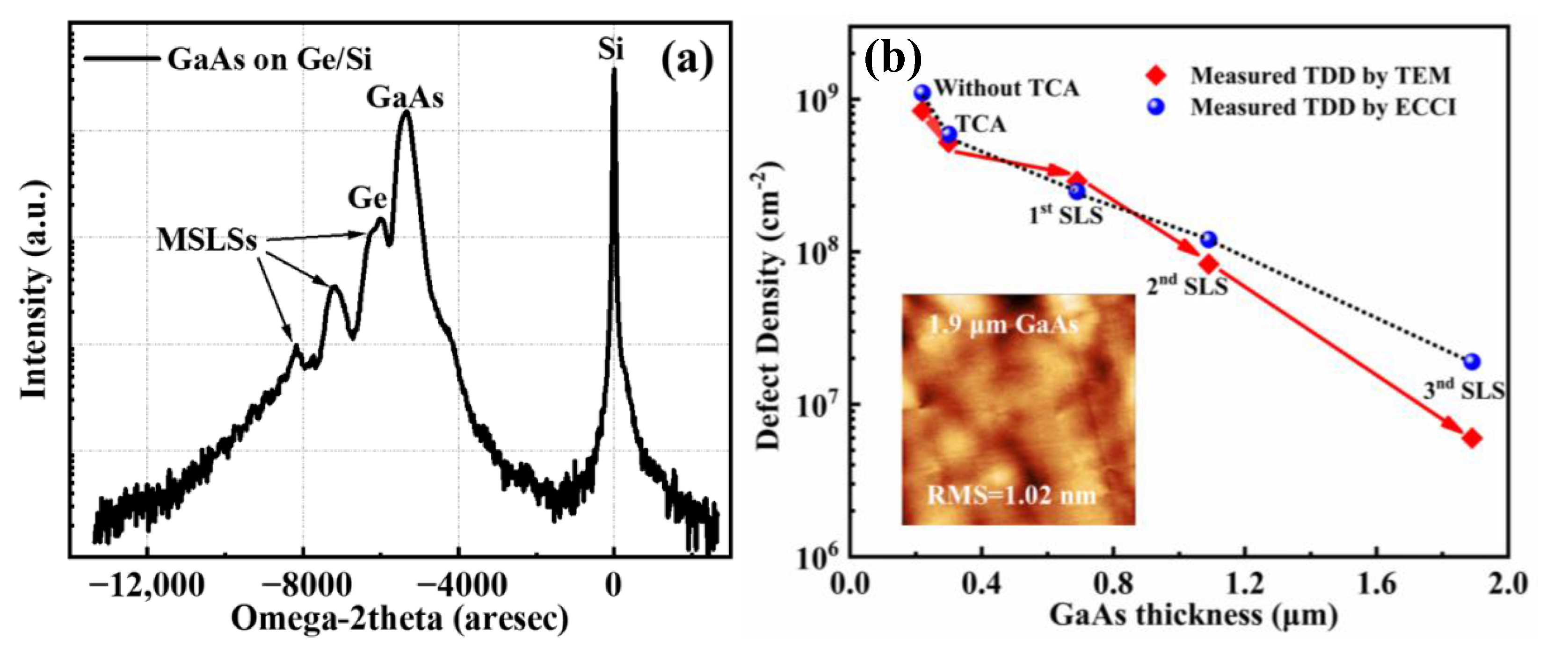

3.1. Thermal Cycle Annealing (TCA) Investigation

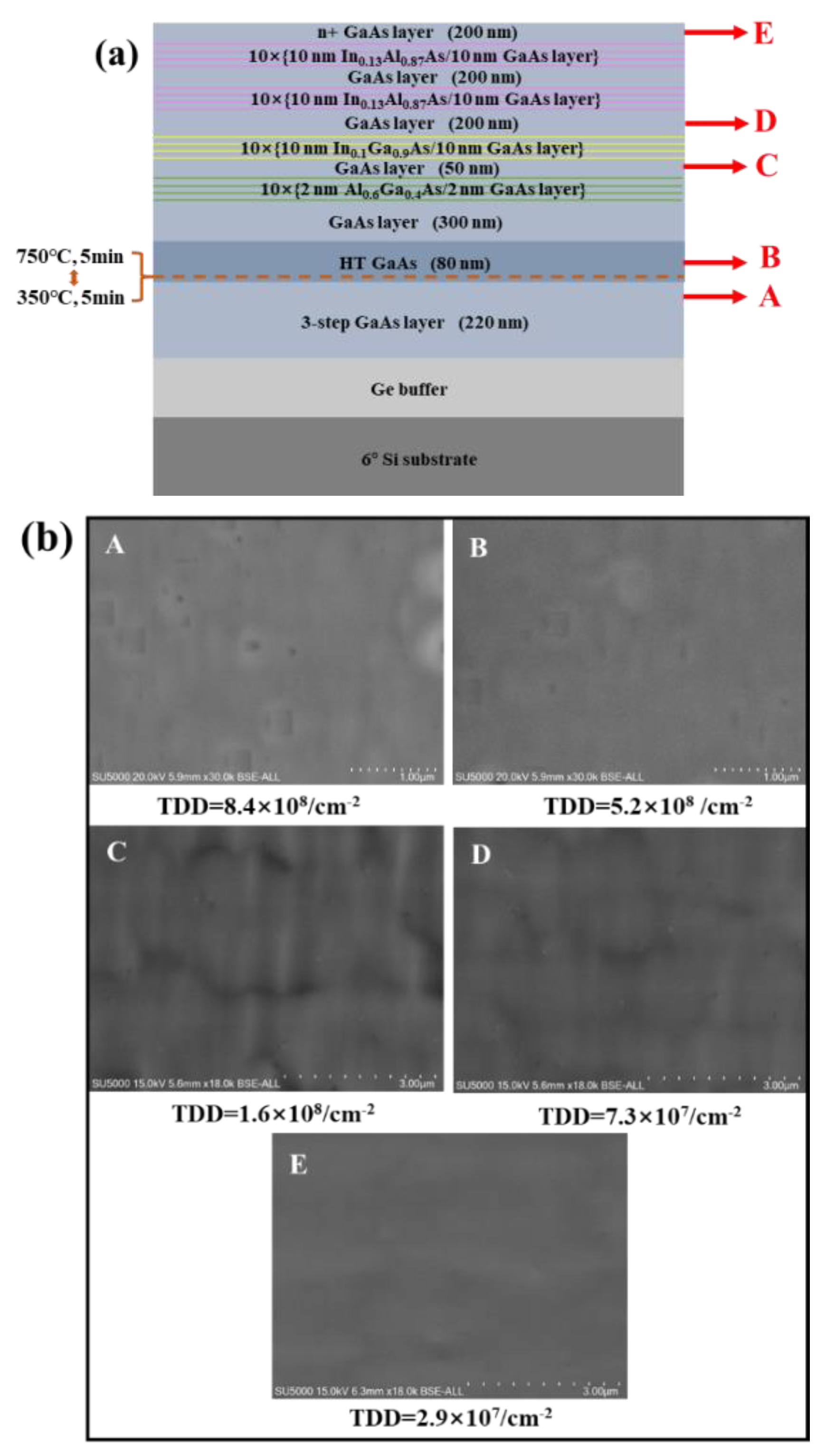

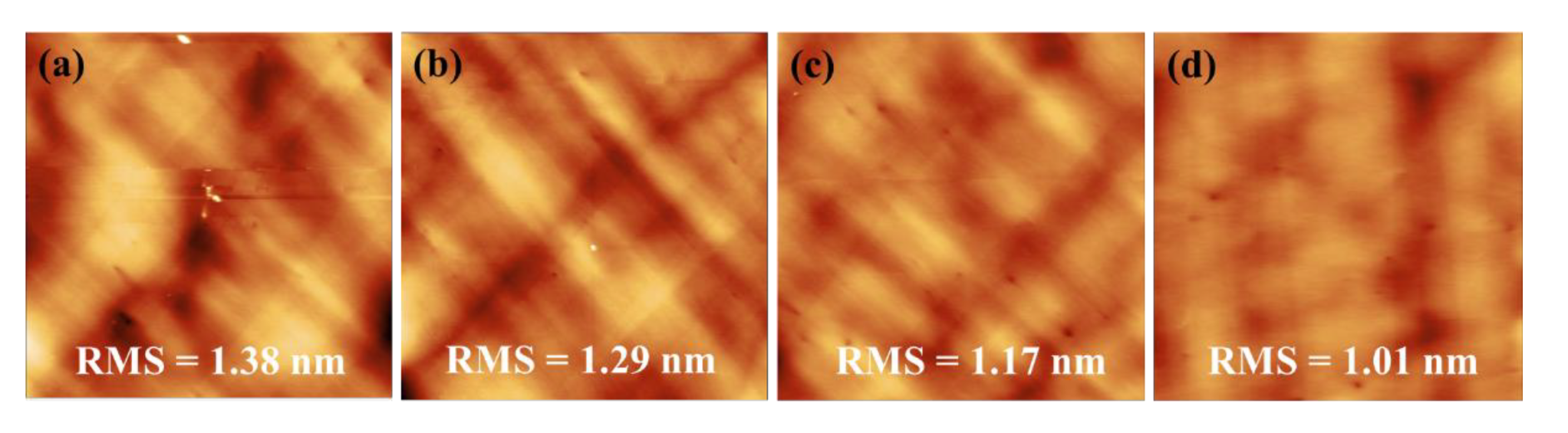

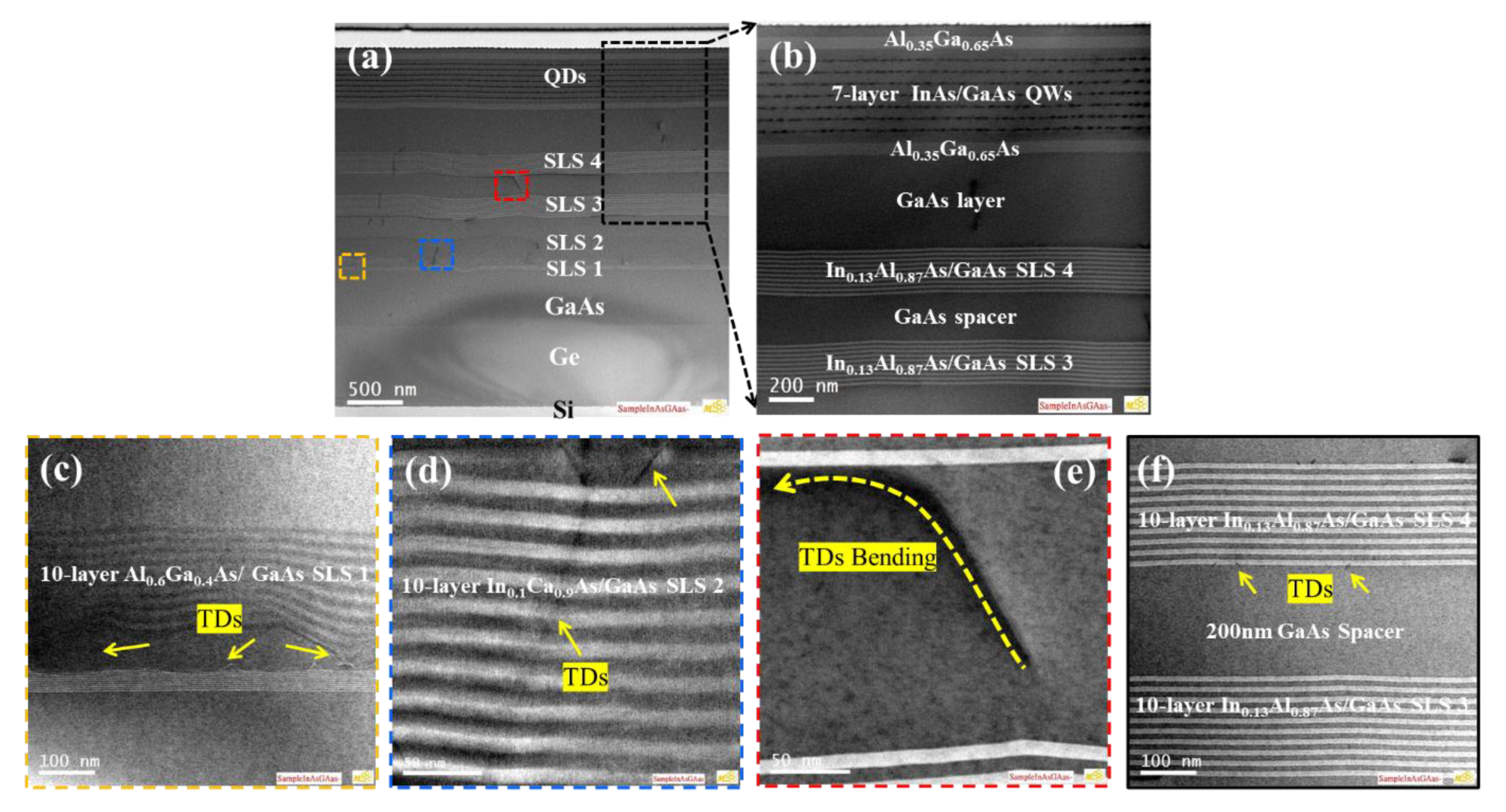

3.2. Dislocation Filter Layers (DFL) Efficiency

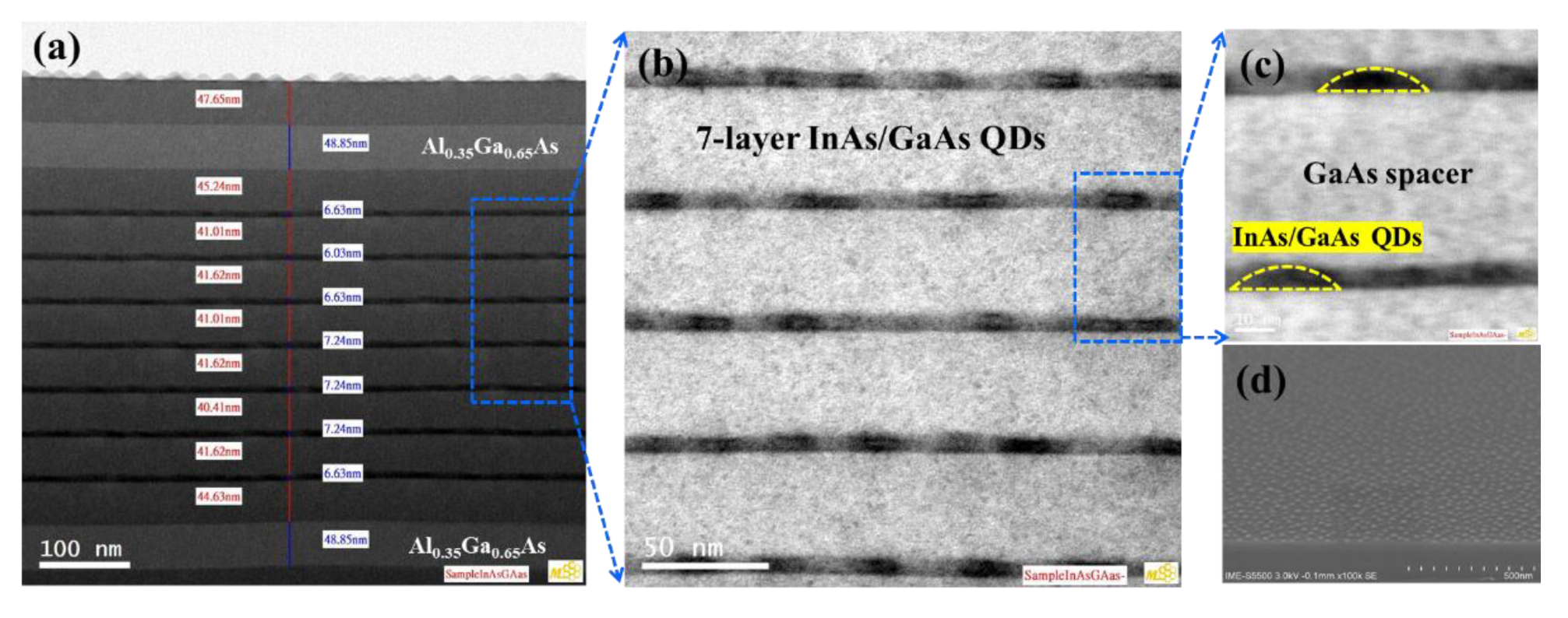

3.3. Growth of InAs QDs

3.4. Device Fabrication

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Aggerstam, T.; Lourdudoss, S.; Radamson, H.; Sjodin, M.; Lorenzini, P.; Look, D. Investigation of the interface properties of MOVPE grown AlGaN/GaN high electron mobility transistor (HEMT) structures on sapphire. Thin Solid Film. 2006, 515, 705–707. [Google Scholar] [CrossRef]

- Zhou, Z.; Yin, B.; Michel, J. On-chip light sources for silicon photonics. Light Sci. Appl. 2015, 4, e358. [Google Scholar] [CrossRef]

- Feng, Q.; Wei, W.; Zhang, B.; Wang, H.; Wang, J.; Cong, H.; Wang, T.; Zhang, J. O-Band and C/L-Band III-V Quantum Dot Lasers Monolithically Grown on Ge and Si Substrate. Appl. Sci. 2019, 9, 385. [Google Scholar] [CrossRef]

- Radamson, H.H.; Luo, J.; Simoen, E.; Zhao, C. CMOS Past, Present and Future; Woodhead Publishing: Cambridge, UK, 2018; ISBN 9780081021392. [Google Scholar]

- Radamson, H.H.; Zhu, H.; Wu, Z.; He, X.; Lin, H.; Liu, J.; Xiang, J.; Kong, Z.; Xiong, W.; Li, J.; et al. State of the Art and Future Perspectives in Advanced CMOS Technology. Nanomaterials 2020, 10, 1555. [Google Scholar] [CrossRef] [PubMed]

- Camacho-Aguilera, R.E.; Cai, Y.; Patel, N.; Romagnoli, M.; Kimerling, L.C.; Michel, J. An Electrically pumped germanium laser. Opt. Express 2012, 20, 11316–11320. [Google Scholar] [CrossRef]

- Asghari, M.; Krishnamoorthy, A.V. Silicon photonics: Energy efficient communication. Nat. Photonics 2011, 5, 268–270. [Google Scholar] [CrossRef]

- Reed, G.T.; Mashanovich, G.; Gardes, F.Y.; Thomson, D.J. Silicon optical modulators. Nat. Photonics 2010, 4, 518–526. [Google Scholar] [CrossRef]

- Xiao, X.; Xu, H.; Li, X.Y.; Li, Z.Y.; Chu, T.; Yu, Y.; Yu, J.Z. High-speed, low-loss silicon Mach–Zehnder modulators with doping optimization. Opt. Express 2013, 21, 4116–4125. [Google Scholar] [CrossRef] [PubMed]

- Zhao, X.; Moeen, M.; Toprak, M.; Wang, G.L.; Luo, J.; Ke, X.X.; Li, Z.H.; Liu, D.Q.; Wang, W.W.; Radamson, H.H. Design impact on the performance of Ge PIN photodetectors. J. Mater. Sci. Mater. Electron. 2020, 31, 18–25. [Google Scholar] [CrossRef]

- Zhao, X.; Wang, G.; Lin, H.; Du, Y.; Luo, X.; Kong, Z.Z.; Su, J.L.; Li, J.J.; Xiong, W.J.; Miao, Y.H.; et al. High Performance p-i-n Photodetectors on Ge-on-Insulator Platform. Nanomaterials 2021, 11, 1125. [Google Scholar] [CrossRef]

- Bonneau, D.; Lobino, M.; Jiang, P.; Natarajan, C.M.; Tanner, M.G.; Hadfield, R.H.; Dorenbos, S.N.; Zwiller, V.; Thompson, M.G.; O’Brien, J.L. Fast path and polarization manipulation of telecom wavelength single photons in lithium niobate waveguide devices. Phys. Rev. Lett. 2012, 108, 053601. [Google Scholar] [CrossRef] [PubMed]

- Tang, M.C.; Chen, S.M.; Wu, J.; Jiang, Q.; Kennedy, K.; Jurczak, P.; Liao, M.; Beanland, R.; Liu, H.Y. Optimizations of Defect Filter Layers for 1.3-μm InAs/GaAs Quantum-Dot Lasers Monolithically Grown on Si Substrates. IEEE J. Sel. Top. Quantum Electron. 2016, 22, 50–56. [Google Scholar] [CrossRef]

- Dai, D.; Bowers, J.E. Silicon-Based on-Chip Multiplexing Technologies and Devices for Peta-Bit Optical Interconnects. Nanophotonics 2014, 3, 283–311. [Google Scholar] [CrossRef]

- Jiang, J.; Xue, M.; Lu, C.Y.; Fenrich, C.S.; Morea, M.; Zang, K.; Gao, J.; Cheng, M.; Zhang, Y.; Kamins, T.I.; et al. Strain-Induced Enhancement of Electroluminescence from Highly Strained Germanium Light-Emitting Diodes. ACS Photonics 2019, 6, 915–923. [Google Scholar] [CrossRef]

- Pelant, I.; Kůsová, K. Towards a Germanium and Silicon Laser: The History and the Present. Crystals 2019, 9, 624. [Google Scholar] [CrossRef]

- Ni, W.X.; Joelsson, K.B.; Radamson, H.H.; Henry, A.; Shen, G.D.; Hansson, G.V. A silicon molecular beam epitaxy system dedicated to device-oriented material research. J. Cryst. Growth 1995, 157, 285–294. [Google Scholar] [CrossRef]

- Radamson, H.H.; Wang, G.L. Silicon Nanodevices. Nanomaterials 2022, 12, 1980. [Google Scholar] [CrossRef] [PubMed]

- Radamson, H.H.; Noroozi, M.; Jamshidi, A.; Thompson, P.E.; Ostling, M.; Harame, D.; Krishnamohan, T.; Miyazaki, S.; Reznicek, A.; Tillack, B.; et al. Strain engineering in GeSnSi materials. ECS Trans. 2012, 50, 527–531. [Google Scholar] [CrossRef]

- Miao, Y.; Wang, G.; Kong, Z.; Xu, B.Q.; Zhao, X.W.; Luo, X.; Lin, H.X.; Dong, Y.; Lu, B.; Dong, L.P.; et al. Review of Si-Based GeSn CVD Growth and Optoelectronic Applications. Nanomaterials 2021, 11, 2556. [Google Scholar] [CrossRef]

- Kong, Z.Z.; Wang, G.L.; Liang, R.R.; Su, J.L.; Xun, M.; Miao, Y.H.; Gu, S.A.; Li, J.J.; Cao, K.H.; Lin, H.X.; et al. Growth and Strain Modulation of GeSn Alloys for Photonic and Electronic Applications. Nanomaterials 2022, 12, 981. [Google Scholar] [CrossRef]

- Crowley, M.T.; Naderi, N.A.; Su, H.; Grillot, F.; Lester, L.F. GaAs-based quantum dot lasers. Semicond. Semimet. 2012, 86, 371–417. [Google Scholar]

- Senellart, P.; Solomon, G.; White, A. High-performance semiconductor quantum-dot single-photon sources. Nat. Nanotechnol. 2017, 12, 1026–1039. [Google Scholar] [CrossRef] [PubMed]

- Chen, S.M.; Li, W.; Wu, J.; Jiang, Q.; Tang, M.C.; Shutts, S.; Sobiesierski, A.; Ross, I.; Smowton, I.M.; Liu, H.-Y. Electrically pumped continuous-wave III–V quantum dot lasers on silicon. Nat. Photonics 2016, 10, 307. [Google Scholar] [CrossRef]

- Tang, M.; Chen, S.M.; Wu, J.; Jiang, Q.; Dorogan, V.G.; Benamara, M.; Mazur, Y.I.; Salamo, G.J.; Seeds, A.; Liu, H.Y.; et al. 1.3-µm InAs/GaAs quantum-dot lasers monolithically grown on Si substrates using InAlAs/GaAs dislocation filter layers. Opt. Express 2014, 22, 11528–11535. [Google Scholar] [CrossRef] [PubMed]

- Zhang, J.Y.; Wei, W.Q.; Cong, H.; Feng, Q.; Wang, Z.H.; Wang, T.; Zhang, J.J. Epitaxial growth of InAs/GaAs quantum dots on {113}-faceted Ge/Si (001) hollow substrate. Opt. Mater. Express 2020, 10, 1045. [Google Scholar] [CrossRef]

- Wang, Z.H.; Yao, R.Z.; Preble, S.F.; Lee, C.S.; Lester, L.F.; Guo, W. High performance InAs quantum dot lasers on silicon substrates by low temperature Pd-GaAs wafer bonding. Appl. Phys. Lett. 2015, 107, 261107. [Google Scholar] [CrossRef]

- Xu, B.; Wang, G.; Du, Y.; Miao, Y.H.; Li, B.; Zhao, X.; Lin, H.; Yu, J.; Su, J.; Dong, Y.; et al. Monolithic Integration of O-Band InAs Quantum Dot Lasers with Engineered GaAs Virtual Substrate Based on Silicon. Nanomaterials 2022, 12, 2704. [Google Scholar] [CrossRef]

- Du, Y.; Xu, B.; Wang, G.; Miao, Y.H.; Li, B.; Kong, Z.Z.; Dong, Y.; Wang, W.W.; Radamson, H.H. Review of Highly Mismatched III-V Heteroepitaxy Growth on (001) Silicon. Nanomaterials 2022, 12, 741. [Google Scholar] [CrossRef]

- Liu, A.; Herrick, R.W.; Petroff, P.M.; Bowers, J.E. Reliability of InAs/GaAs quantum dot lasers epitaxially grown on silicon. IEEE J. Sel. Top. Quantum Electron. 2015, 21, 1900708. [Google Scholar] [CrossRef]

- Selvidge, J.; Hughes, E.T.; Norman, J.C.; Shang, C.; Kennedy, M.J.; Dumont, M.; Netherton, A.M.; Zhang, Z.; Herrick, R.W.; Bowers, J.E.; et al. Reduced dislocation growth leads to long lifetime InAs quantum dot lasers on silicon at high temperatures. Appl. Phys. Lett. 2021, 118, 192101. [Google Scholar] [CrossRef]

- Alcotte, R.; Martin, M.; Moeyaert, J.; Cipro, R.; David, S.; Bassani, F.; Ducroquet, F.; Bogumilowicz, Y.; Sanchez, E.; Ye, Z.; et al. Epitaxial growth of antiphase boundary free GaAs layer on 300 mm Si (001) substrate by metal organic chemical vapour deposition with high mobility. APL Mater. 2016, 4, 046101. [Google Scholar] [CrossRef]

- Du, Y.; Xu, B.; Wang, G.; Gu, S.H.; Li, B.; Kong, Z.Z.; Yu, J.H.; Bai, G.B.; Li, J.J.; Wang, W.W.; et al. Growth of high-quality epitaxy of GaAs on Si with engineered Ge buffer using MOCVD. J. Mater. Sci. Mater. Electron. 2021, 32, 1–13. [Google Scholar] [CrossRef]

- Wan, Y.T.; Li, Q.; Geng, Y.; Shi, B.; Lau, K.M. InAs/GaAs quantum dots on GaAs-on-V-grooved-Si substrate with high optical quality in the 1.3 mu m band. Appl. Phys. Lett. 2015, 107, 081106. [Google Scholar] [CrossRef]

- George, I.; Becagli, F.; Liu, H.Y.; Wu, J.; Tang, M.; Beanland, R. Dislocation filters in GaAs on Si. Semicondut. Sci. Technol. 2015, 30, 114004. [Google Scholar] [CrossRef]

- Bogumilowicz, Y.; Hartmann, J.M.; Rochat, N.; Salaun, A.; Martin, S.M.; Bassani, F.; Baron, T.; David, S.; Bao, X.Y.; Sanchez, E. Threading dislocations in GaAs epitaxial layers on various thickness Ge buffers on 300 mm Si substrates. J. Cryst. Growth. 2016, 453, 180–187. [Google Scholar] [CrossRef]

- Yang, J.; Jurczak, P.; Cui, F.; Li, K.; Tang, M.; Billiald, L.; Beanland, R.; Sanchez, A.M.; Liu, H. Thin Ge buffer layer on silicon for integration of III-V on silicon. J. Cryst. Growth 2019, 514, 109–113. [Google Scholar] [CrossRef]

- Barrett, C.S.; Atassi, A.; Kennonet, E.L.; Weinrich, Z.; Haynes, K.; Bao, X.-Y.; Martin, P.; Jones, K.S. Dissolution of antiphase domain boundaries in GaAs on Si (001) via post-growth annealing. J. Mater. Sci. 2019, 54, 7028–7703. [Google Scholar] [CrossRef]

- Ko, Y.H.; Kim, K.J.; Han, W.S. Monolithic growth of GaAs laser diodes on Si (001) by optimal AlAs nucleation with thermal cycle annealing. Opt. Mater. Express 2021, 11, 943–951. [Google Scholar] [CrossRef]

- Du, Y.; Kong, Z.; Toprak, M.; Wang, G.L.; Miao, Y.H.; Xu, B.Q.; Yu, J.H.; Li, B.; Lin, H.X.; Han, J.H.; et al. Investigation of the Heteroepitaxial Process Optimization of Ge Layers on Si (001) by RPCVD. Nanomaterials 2021, 11, 928. [Google Scholar] [CrossRef]

- Xu, B.Q.; Du, Y.; Wang, G.L.; Xiong, W.J.; Kong, Z.Z.; Zhao, X.W.; Miao, Y.H.; Wang, Y.J.; Lin, H.X.; Su, J.L.; et al. Dual-Step Selective Homoepitaxy of Ge with Low Defect Density and Modulated Strain Based on Optimized Ge/Si Virtual Substrate. Materials 2022, 15, 3594. [Google Scholar] [CrossRef]

- Shi, B.; Lei Wang, L.; Taylor, A.A.; Brunelli, S.S.; Zhao, H.W.; Song, B.; Klamkin, J. MOCVD grown low dislocation density GaAs-on-V-groove patterned (001) Si for 1.3 μm quantum dot laser applications. Appl. Phys. Lett. 2019, 114, 172102. [Google Scholar] [CrossRef]

- Kwone, J.; Jang, B.Y.; Lee, J.; Kageyama, T.; Watanbe, K.; Arakawa, Y. All MBE grown InAs/GaAs quantum dot lasers on on-axis Si (001). Opt. Express 2018, 26, 11569. [Google Scholar] [CrossRef] [PubMed]

- Faucher, J.; Masuda, T.; Lee, M.L. Initiation strategies for simultaneous control of antiphase domains and stacking faults in GaAs solar cells on Ge. J. Vac. Sci. Technol. B 2016, 34, 041203. [Google Scholar] [CrossRef]

- Romanov, A.E.; Pompe, W.; Beltz, G.; Speck, J.S. Modeling of threading dislocation density reduction in heteroepitaxial layers I. Geometry and crystallography. Phys. Status Solidi 1996, 198, 599–613. [Google Scholar] [CrossRef]

- Deviprasad, V.P.; Panda, D.; Paul, S.; Mondal, S.; Saha, J.; Das, D.; Tongbram, B.; Gupta, K.D. Room temperature operation and low dark current of In0.15Ga0.85As/InAs/In0.15Ga0.85As dot-in-well short-wave infrared photodetector: Experimental and theoretical correlation. Superlattices Microstruct. 2021, 148, 106715. [Google Scholar] [CrossRef]

- Seger, J.; Jarmar, T.; Zhang, Z.B.; Radamson, H.; Ericson, F.; Smith, U.; Zhang, S.-L. Morphological instability of NiSi1-uGeu on single-crystal and polycrystalline Si1 − xGex. J. Appl. Phys. 2004, 96, 1919–1928. [Google Scholar] [CrossRef]

- Wei, W.Q.; Feng, Q.; Guo, J.J.; Guo, M.C.; Wang, J.H.; Wang, Z.H.; Wang, T.; Zhang, J.J. InAs/GaAs quantum dot narrow ridge lasers epitaxially grown on SOI substrates for silicon photonic integration. Opt. Express 2020, 28, 26555–26563. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Du, Y.; Wei, W.; Xu, B.; Wang, G.; Li, B.; Miao, Y.; Zhao, X.; Kong, Z.; Lin, H.; Yu, J.; et al. Reduced Dislocation of GaAs Layer Grown on Ge-Buffered Si (001) Substrate Using Dislocation Filter Layers for an O-Band InAs/GaAs Quantum Dot Narrow-Ridge Laser. Micromachines 2022, 13, 1579. https://doi.org/10.3390/mi13101579

Du Y, Wei W, Xu B, Wang G, Li B, Miao Y, Zhao X, Kong Z, Lin H, Yu J, et al. Reduced Dislocation of GaAs Layer Grown on Ge-Buffered Si (001) Substrate Using Dislocation Filter Layers for an O-Band InAs/GaAs Quantum Dot Narrow-Ridge Laser. Micromachines. 2022; 13(10):1579. https://doi.org/10.3390/mi13101579

Chicago/Turabian StyleDu, Yong, Wenqi Wei, Buqing Xu, Guilei Wang, Ben Li, Yuanhao Miao, Xuewei Zhao, Zhenzhen Kong, Hongxiao Lin, Jiahan Yu, and et al. 2022. "Reduced Dislocation of GaAs Layer Grown on Ge-Buffered Si (001) Substrate Using Dislocation Filter Layers for an O-Band InAs/GaAs Quantum Dot Narrow-Ridge Laser" Micromachines 13, no. 10: 1579. https://doi.org/10.3390/mi13101579

APA StyleDu, Y., Wei, W., Xu, B., Wang, G., Li, B., Miao, Y., Zhao, X., Kong, Z., Lin, H., Yu, J., Su, J., Dong, Y., Wang, W., Ye, T., Zhang, J., & Radamson, H. H. (2022). Reduced Dislocation of GaAs Layer Grown on Ge-Buffered Si (001) Substrate Using Dislocation Filter Layers for an O-Band InAs/GaAs Quantum Dot Narrow-Ridge Laser. Micromachines, 13(10), 1579. https://doi.org/10.3390/mi13101579