E/D-Mode GaN Inverter on a 150-mm Si Wafer Based on p-GaN Gate E-Mode HEMT Technology

Abstract

1. Introduction

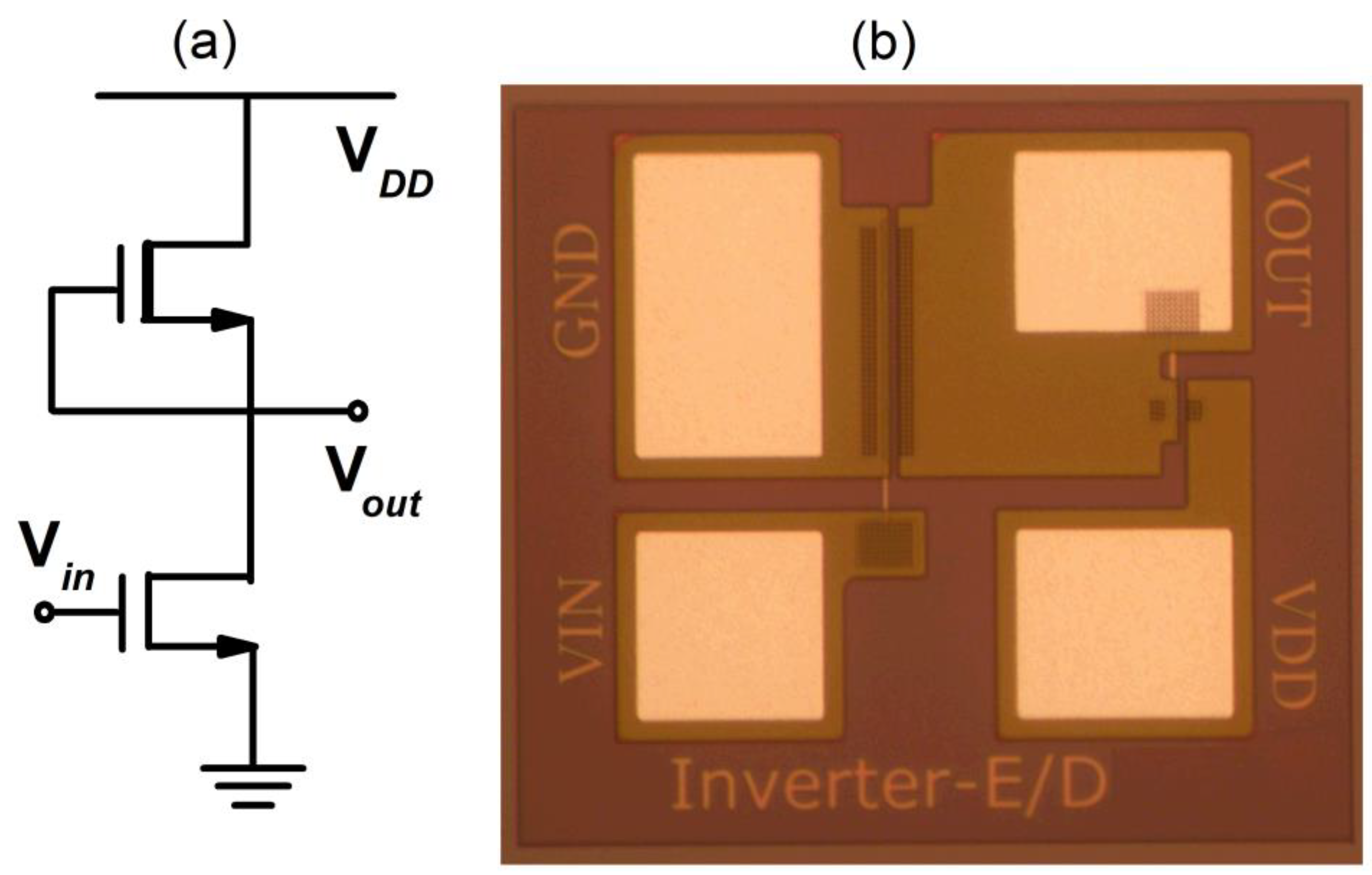

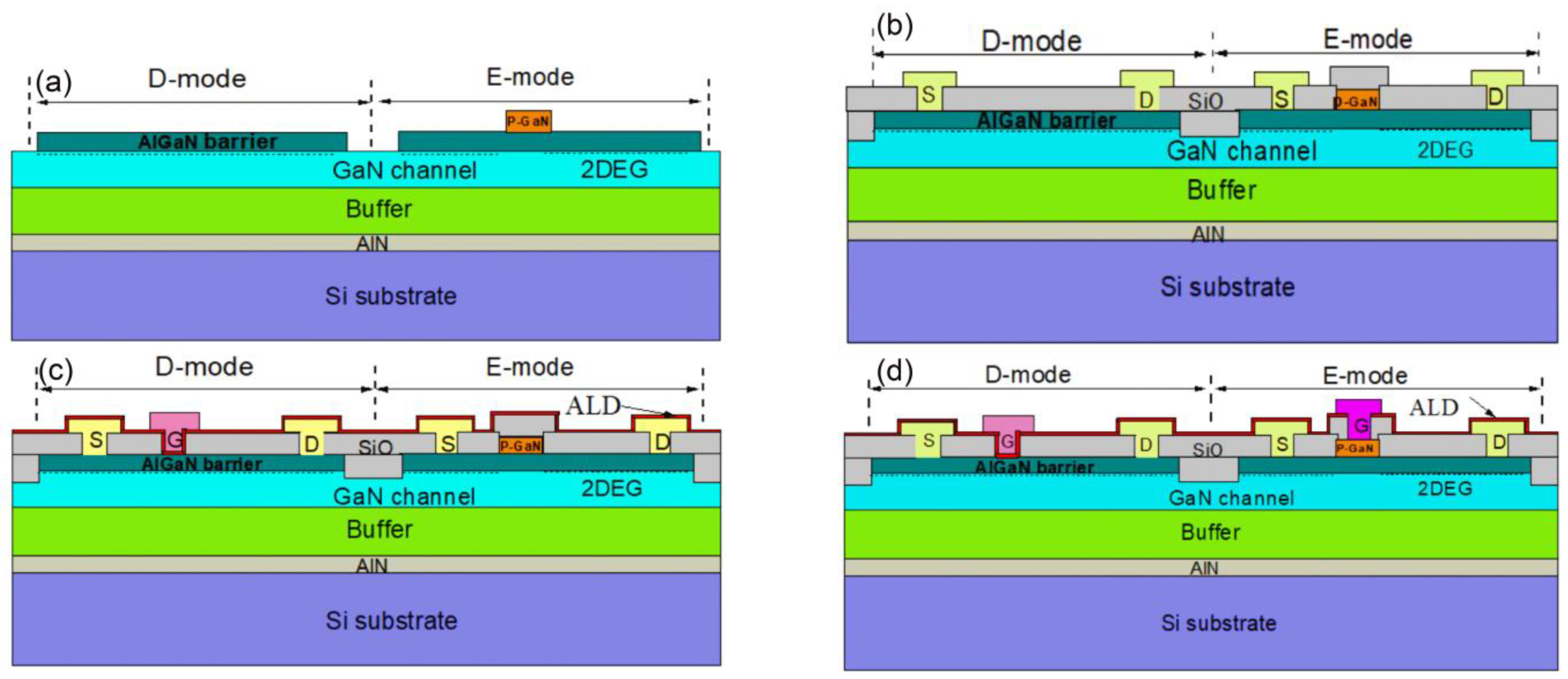

2. Materials and Methods

3. Results

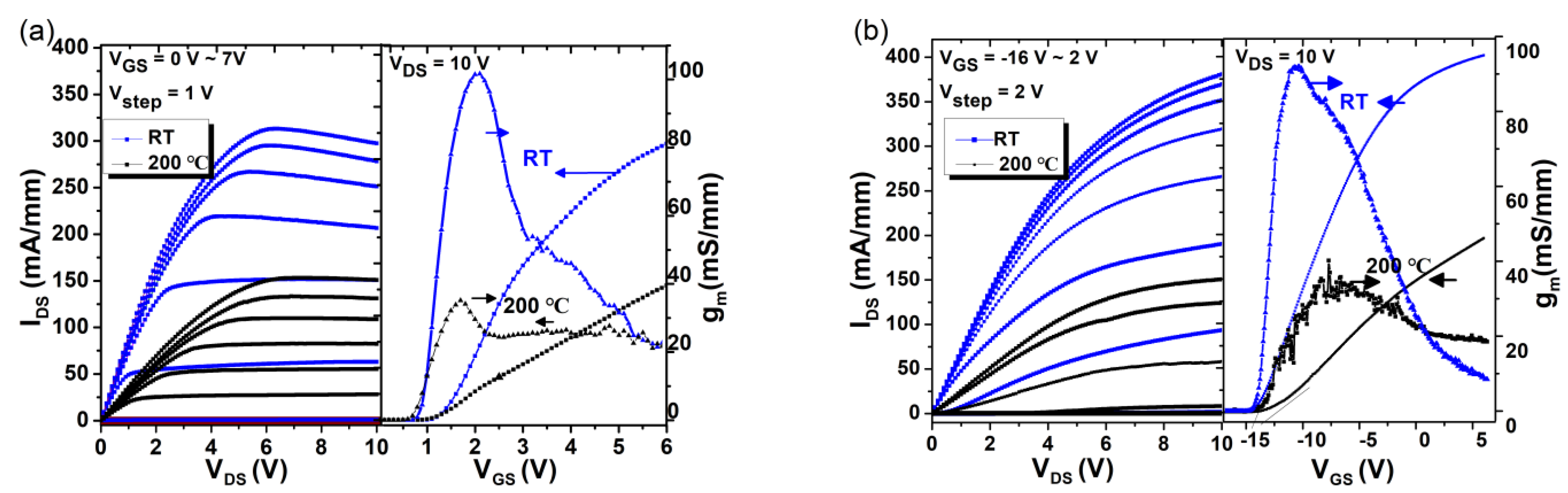

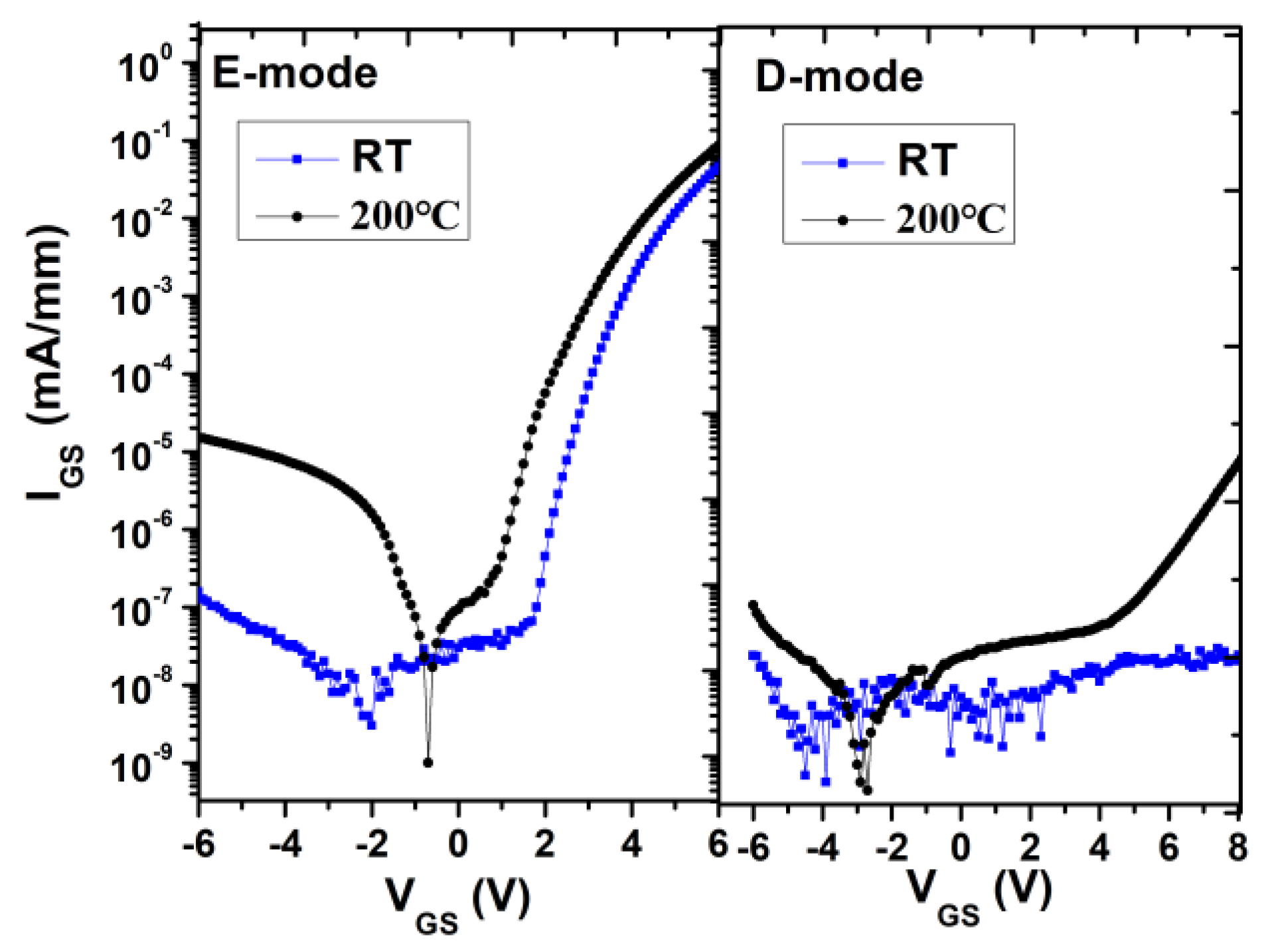

3.1. E/D-Mode GaN HEMTs

3.2. E/D GaN Inverters

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Chen, K.J.; Häberlen, O.; Lidow, A.; Tsai, C.L.; Ueda, T.; Uemoto, Y.; Wu, Y. GaN-on-Si Power Technology Devices and Applications. IEEE Trans. Electron Devices 2017, 64, 779–795. [Google Scholar] [CrossRef]

- Lidow, A. Gallium Nitride Integration: Going Where Silicon Power Can’t Go. IEEE Power Electron. Mag. 2018, 5, 70–72. [Google Scholar] [CrossRef]

- Wong, K.; Kwan, M.H.; Yao, F.W.; Tsai, M.W.; Lin, Y.; Chang, Y.; Chen, P.; Su, R.; Yu, J.; Yang, F.; et al. A next generation CMOS-compatible GaN-on-Si transistors for high efficiency energy systems. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 229–232. [Google Scholar]

- Frolov, F.; Lettl, J. Design of High Efficiency and High Frequency GaN DC/DC Converter. In Proceedings of the 2020 21st International Scientific Conference on Electric Power Engineering (EPE), Prague, Czech Republic, 19–21 October 2020; pp. 1–4. [Google Scholar]

- Wang, B.; Riva, M.; Bakos, J.D.; Monti, A. Integrated circuit implementation for a GaN HFET driver circuit. IEEE Trans. Ind. Appl. 2010, 46, 2056–2067. [Google Scholar] [CrossRef]

- Zhu, M.; Matioli, E. Monolithic integration of GaN-based NMOS digital logic gate circuits with E-mode power GaN MOSHEMTs. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 236–239. [Google Scholar]

- Micovic, M.; Tsen, T.; Hu, M.; Hashimoto, P.; Willadsen, P.J.; Milosavljevic, I.; Schmitz, A.; Antcliffe, M.; Zhender, D.; Moon, J.S.; et al. GaN enhancement/depletion-mode FET logic for mixed signal applications. IEEE Electron Device Lett. 2014, 35, 336–338. [Google Scholar] [CrossRef]

- Xu, Z.; Wang, J.; Cai, Y.; Liu, J.; Yang, Z.; Li, X.; Wang, M.; Yu, M.; Xie, B.; Wu, W.G.; et al. High Temperature Characteristics of GaN-Based Inverter Integrated with Enhancement-Mode (E-Mode) MOSFET and Depletion-Mode (D-Mode) HEMT. IEEE Electron Device Lett. 2014, 35, 33–35. [Google Scholar] [CrossRef]

- Tang, Y.; Saunier, P.; Wang, R.; Ketterson, A.; Gao, X.; Guo, S.; Snider, G.; Jena, D.; Xing, H.; Fay, P. High-performance monolithically-integrated E/D mode InAlN/AlN/GaN HEMTs for mixed-signal applications. In Proceedings of the 2010 International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 684–687. [Google Scholar]

- Cai, Y.; Cheng, Z.; Tang, W.C.; Lau, K.M.; Chen, K.J. Monolithically Integrated Enhancement/Depletion-Mode AlGaN/GaN HEMT Inverters and Ring Oscillators Using CF4 Plasma Treatment. IEEE Trans. Electron Devices 2006, 53, 2223–2230. [Google Scholar] [CrossRef]

- Posthuma, N.E.; You, S.; Stoffels, S.; Wellekens, D.; Liang, H.; Zhao, M.; De Jaeger, B.; Geens, K.; Ronchi, N.; Decoutere, S.; et al. An industry-ready 200 mm p-GaN E-mode GaN-on-Si power technology. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 284–287. [Google Scholar]

- Zhou, D.C.; Chiu, H.C.; Zhang, J.; Wong, R.K.; Zhao, T.; Zhang, F.; Zhang, M.; Zou, Y.; Chen, L. A Massive Adoption Ready 200mm 40V-650V E-mode GaN-on-Si Power HEMTs Technology. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, 15–19 March 2020; pp. 636–639. [Google Scholar]

- Tang, G.; Kwan, A.M.; Wong, R.K.; Lei, J.; Su, R.Y.; Yao, F.W.; Lin, Y.M.; Yu, J.L.; Tsai, T.; Tuan, H.C.; et al. Digital integrated circuits on an e-mode gan power hemt platform. IEEE Electron Device Lett. 2017, 38, 1282–1285. [Google Scholar] [CrossRef]

- Moench, S.; Reiner, R.; Waltereit, P.; Müller, S.; Quay, R.; Ambacher, O.; Kallfass, I. A 600V p-GaN Gate HEMT with Intrinsic Freewheeling Schottky-Diode in a GaN Power IC with Bootstrapped Driver and Sensors. In Proceedings of the 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 13–18 September 2020; pp. 254–257. [Google Scholar]

- Sun, R.; Liang, Y.C.; Yeo, Y.C.; Zhao, C.; Chen, W.; Zhang, B. All-gan power integration: Devices to functional subcircuits and converter ics. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 31–41. [Google Scholar] [CrossRef]

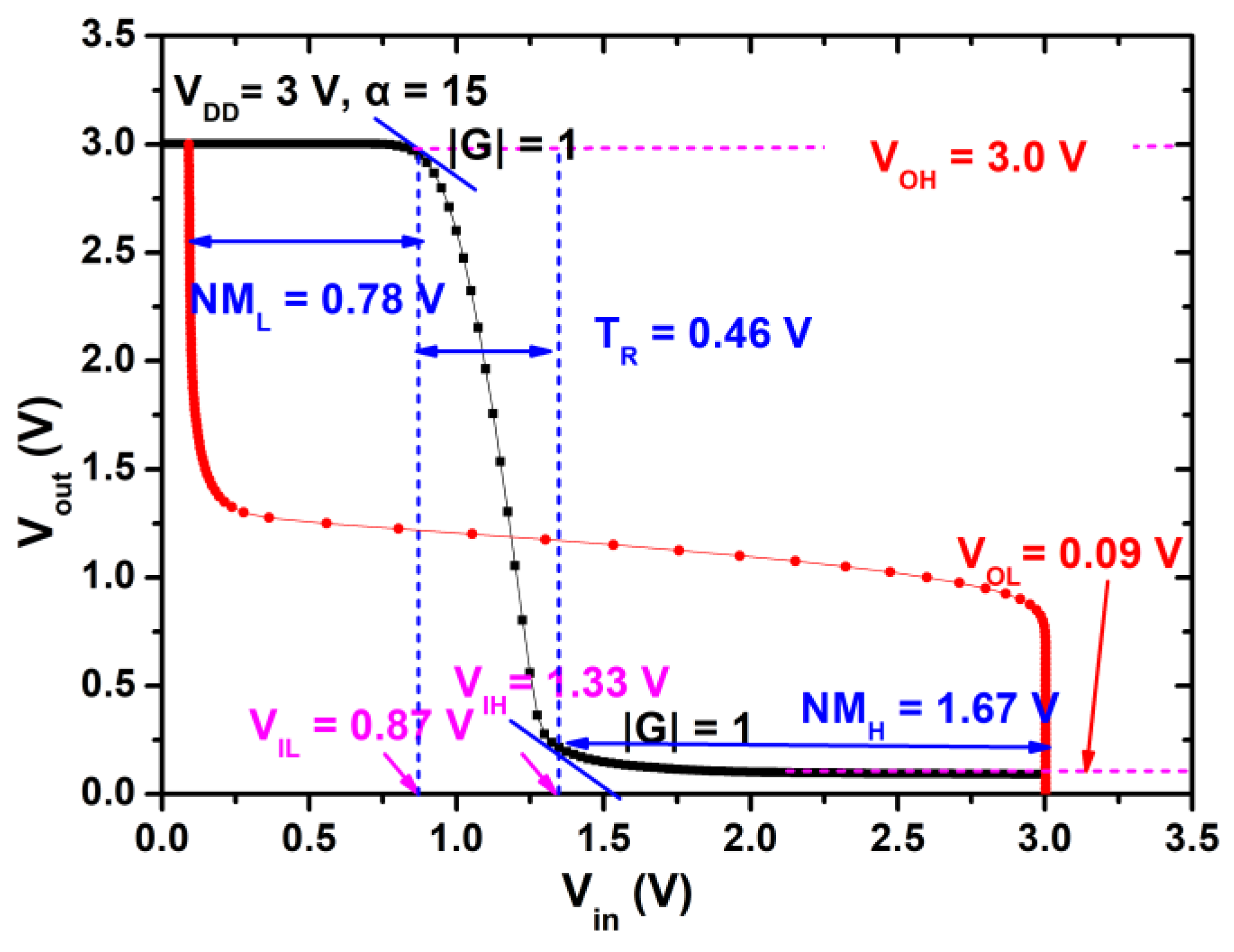

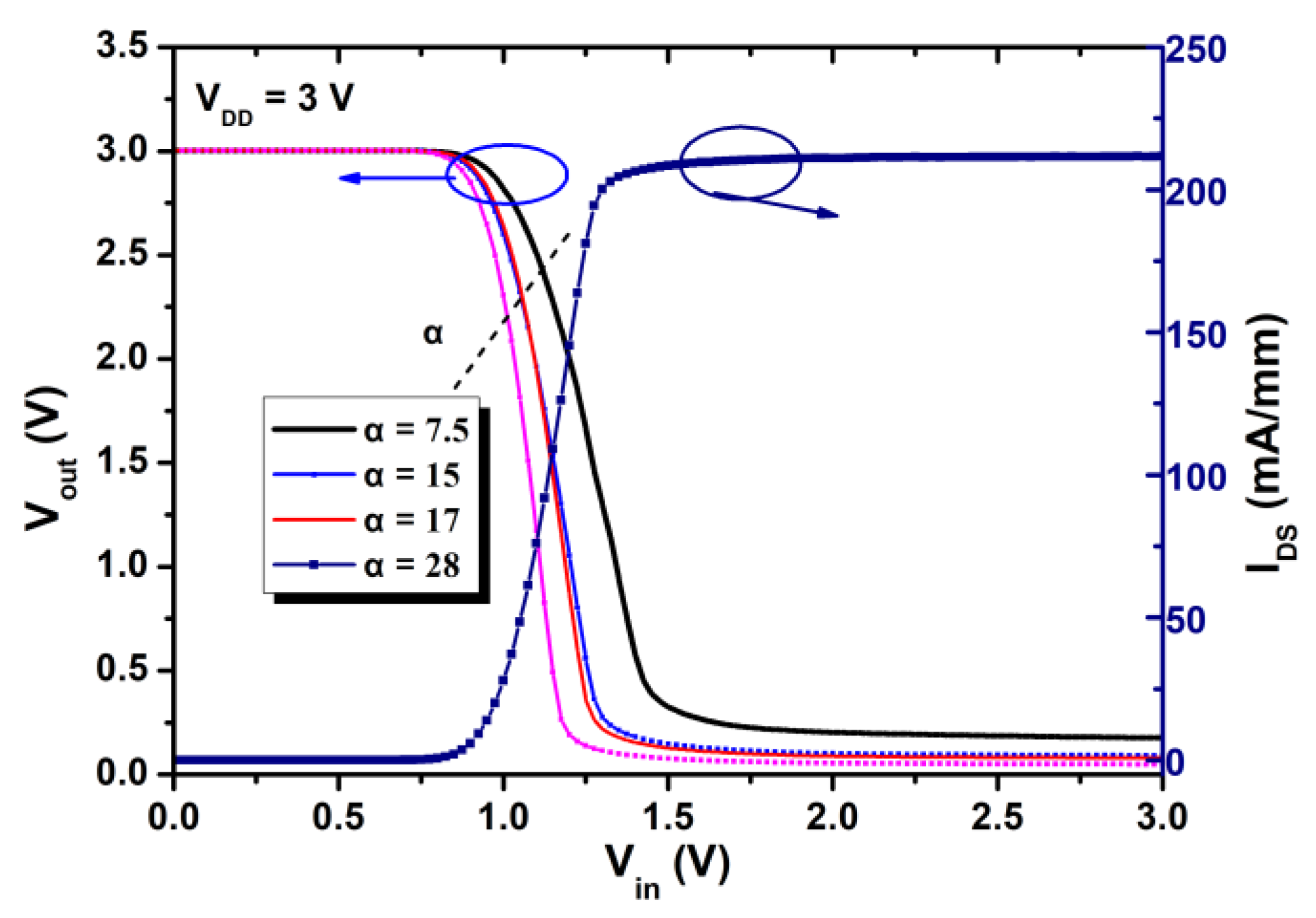

| α | VOH (V) | VOL (V) | Output Swing (V) | VTH (V) | G | NML (V) | NMH (V) |

|---|---|---|---|---|---|---|---|

| 7.5 | 3.0 | 0.17 | 2.83 | 1.30 | 5.5 | 0.76 | 1.53 |

| 15 | 3.0 | 0.09 | 2.91 | 1.18 | 6.8 | 0.78 | 1.67 |

| 17 | 3.0 | 0.07 | 2.93 | 1.17 | 6.9 | 0.79 | 1.70 |

| 28 | 3.0 | 0.05 | 2.95 | 1.11 | 8.3 | 0.80 | 1.80 |

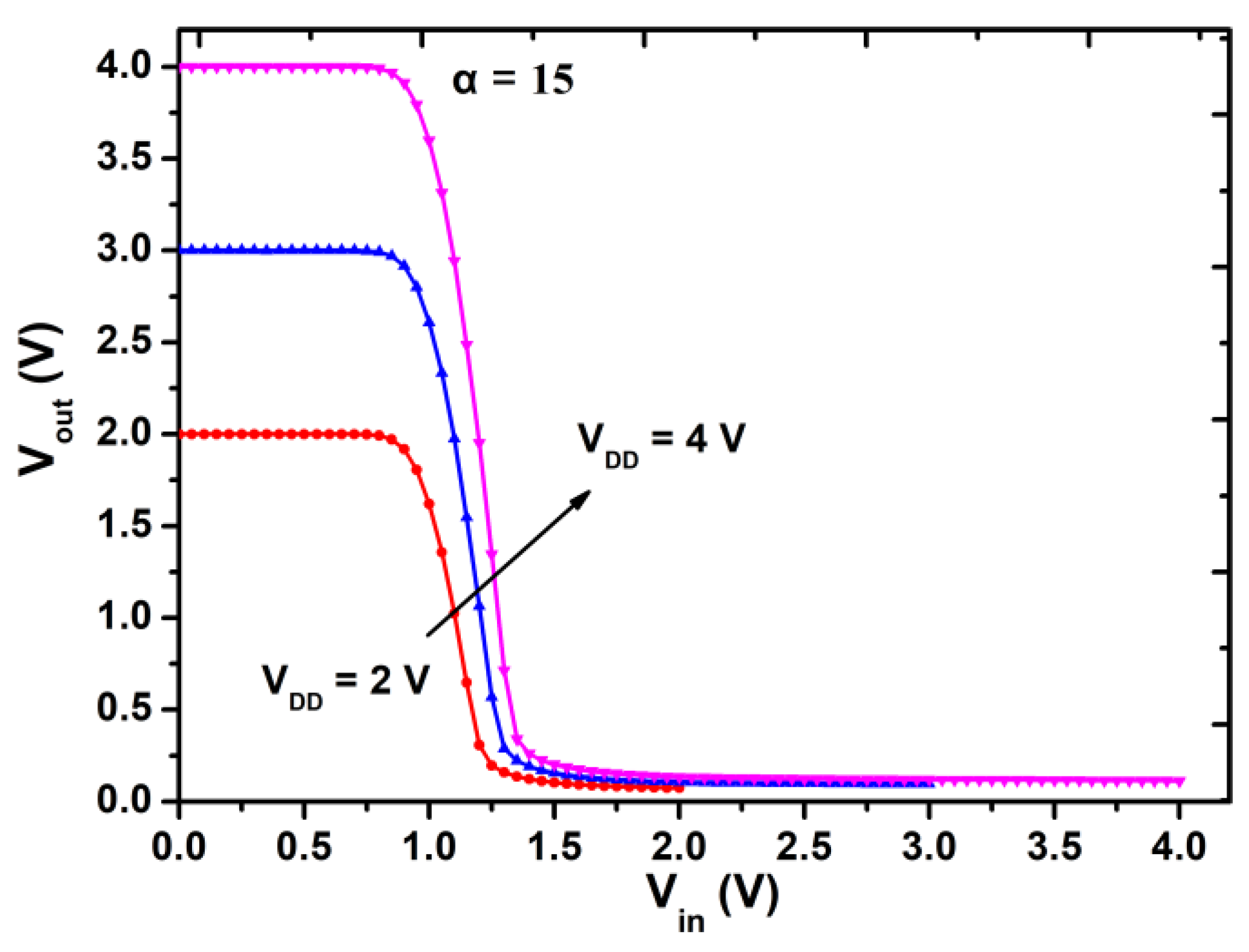

| VDD (V) | VOH (V) | VOL (V) | Output Swing (V) | VTH (V) | G | NML (V) | NMH (V) |

|---|---|---|---|---|---|---|---|

| 2 | 2.0 | 0.07 | 1.93 | 1.08 | 5.2 | 0.77 | 0.75 |

| 3 | 3.0 | 0.09 | 2.91 | 1.18 | 6.8 | 0.78 | 1.63 |

| 4 | 4.0 | 0.11 | 3.89 | 1.25 | 7.1 | 0.80 | 2.59 |

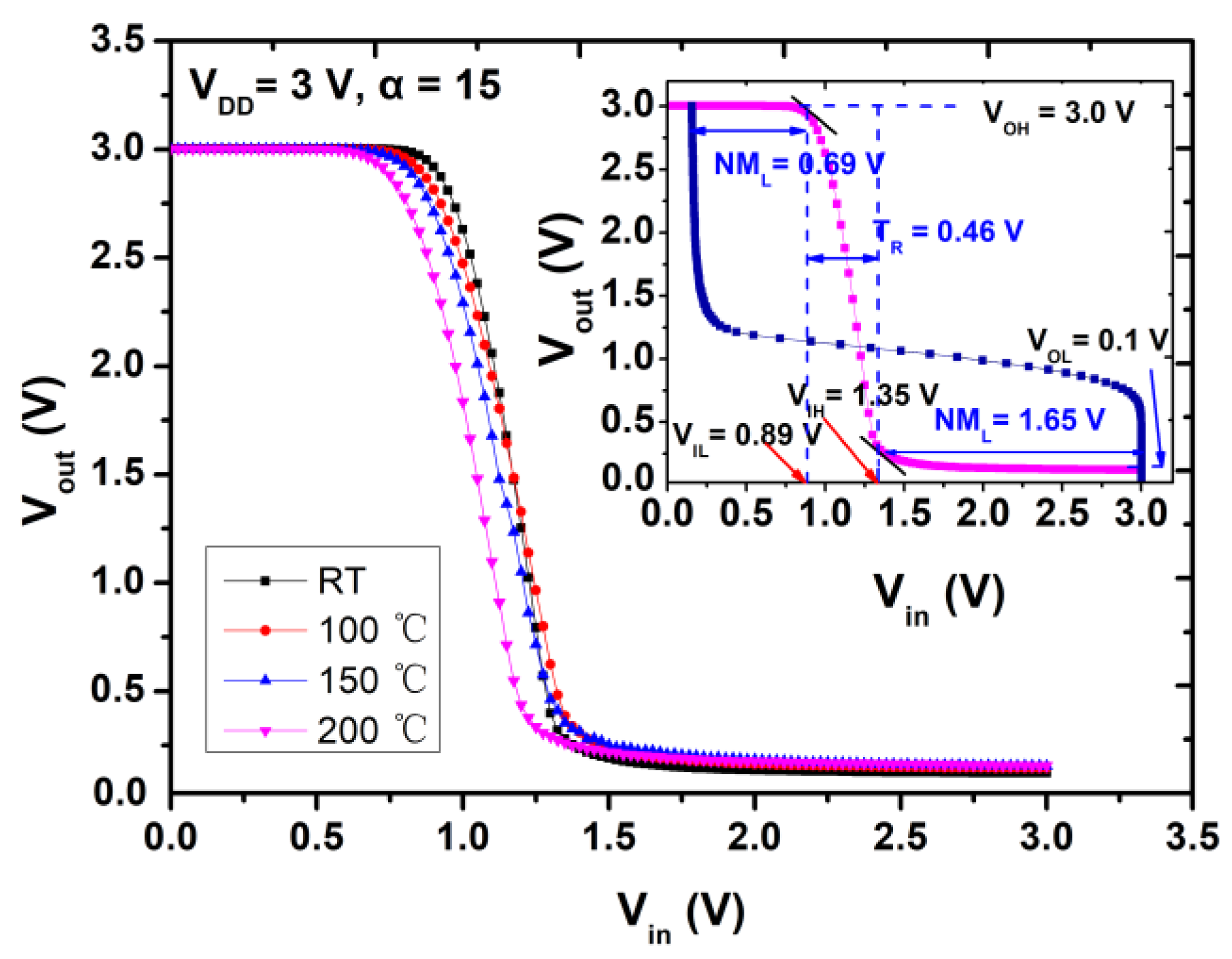

| T (°C) | VOH (V) | VOL (V) | Output Swing (V) | VTH (V) | G | NML (V) | NMH (V) |

|---|---|---|---|---|---|---|---|

| RT | 3.0 | 0.09 | 2.91 | 1.18 | 6.8 | 0.78 | 1.67 |

| 100 | 3.0 | 0.09 | 2.91 | 1.21 | 5.8 | 0.80 | 1.63 |

| 150 | 3.0 | 0.12 | 2.88 | 1.17 | 6.9 | 0.67 | 1.58 |

| 200 | 3.0 | 0.11 | 2.89 | 1.09 | 6.8 | 0.68 | 1.72 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jia, L.-F.; Zhang, L.; Xiao, J.-P.; Cheng, Z.; Lin, D.-F.; Ai, Y.-J.; Zhao, J.-C.; Zhang, Y. E/D-Mode GaN Inverter on a 150-mm Si Wafer Based on p-GaN Gate E-Mode HEMT Technology. Micromachines 2021, 12, 617. https://doi.org/10.3390/mi12060617

Jia L-F, Zhang L, Xiao J-P, Cheng Z, Lin D-F, Ai Y-J, Zhao J-C, Zhang Y. E/D-Mode GaN Inverter on a 150-mm Si Wafer Based on p-GaN Gate E-Mode HEMT Technology. Micromachines. 2021; 12(6):617. https://doi.org/10.3390/mi12060617

Chicago/Turabian StyleJia, Li-Fang, Lian Zhang, Jin-Ping Xiao, Zhe Cheng, De-Feng Lin, Yu-Jie Ai, Jin-Chao Zhao, and Yun Zhang. 2021. "E/D-Mode GaN Inverter on a 150-mm Si Wafer Based on p-GaN Gate E-Mode HEMT Technology" Micromachines 12, no. 6: 617. https://doi.org/10.3390/mi12060617

APA StyleJia, L.-F., Zhang, L., Xiao, J.-P., Cheng, Z., Lin, D.-F., Ai, Y.-J., Zhao, J.-C., & Zhang, Y. (2021). E/D-Mode GaN Inverter on a 150-mm Si Wafer Based on p-GaN Gate E-Mode HEMT Technology. Micromachines, 12(6), 617. https://doi.org/10.3390/mi12060617