Investigation of Normally-Off p-GaN/AlGaN/GaN HEMTs Using a Self-Terminating Etching Technique with Multi-Finger Architecture Modulation for High Power Application

Abstract

1. Introduction

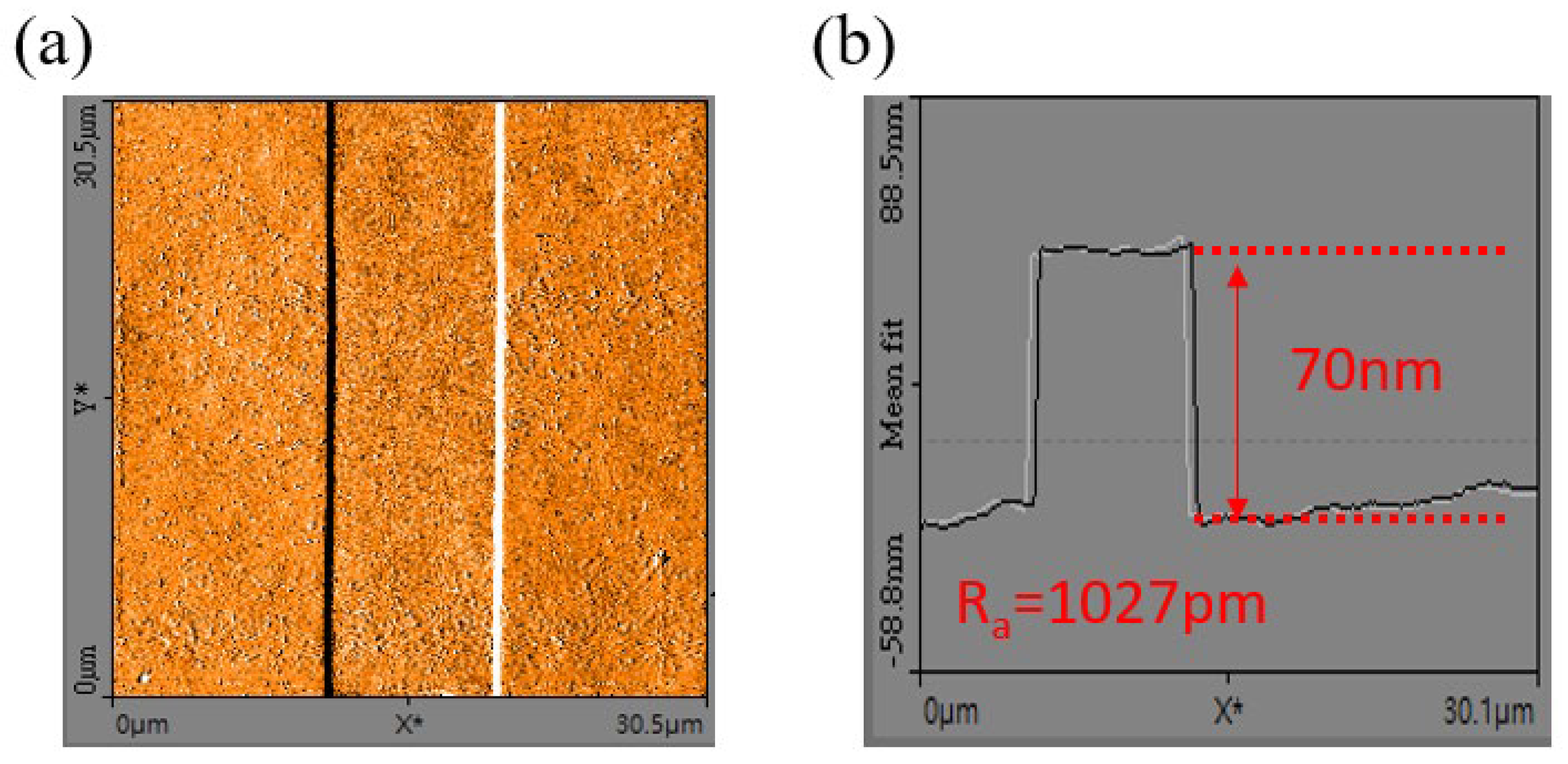

2. Materials and Methods

3. Results and Discussion

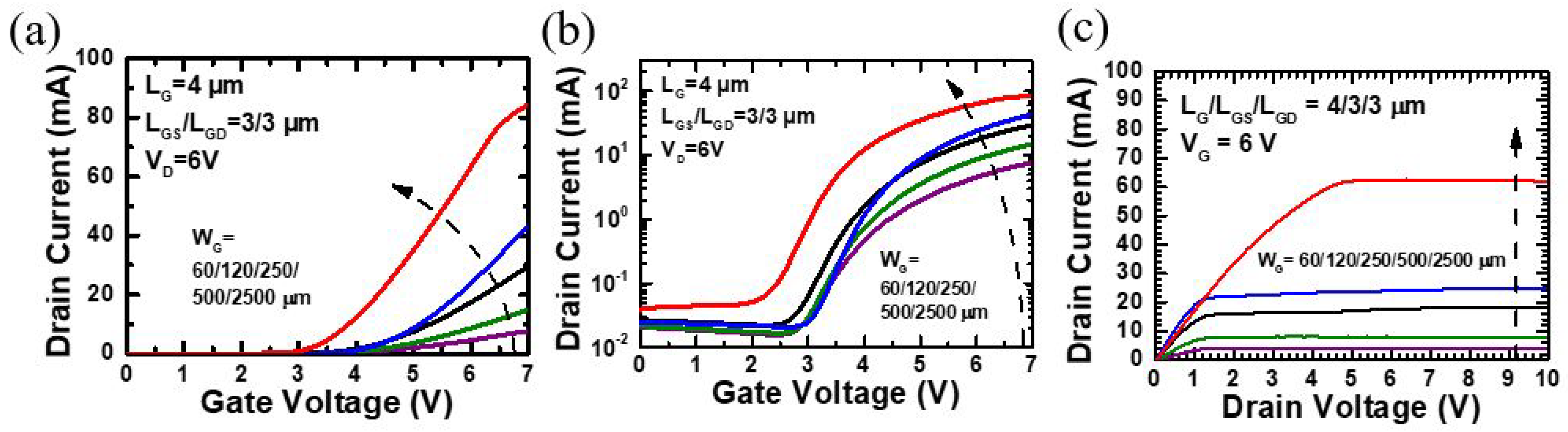

3.1. Single Finger Devices with Different WG

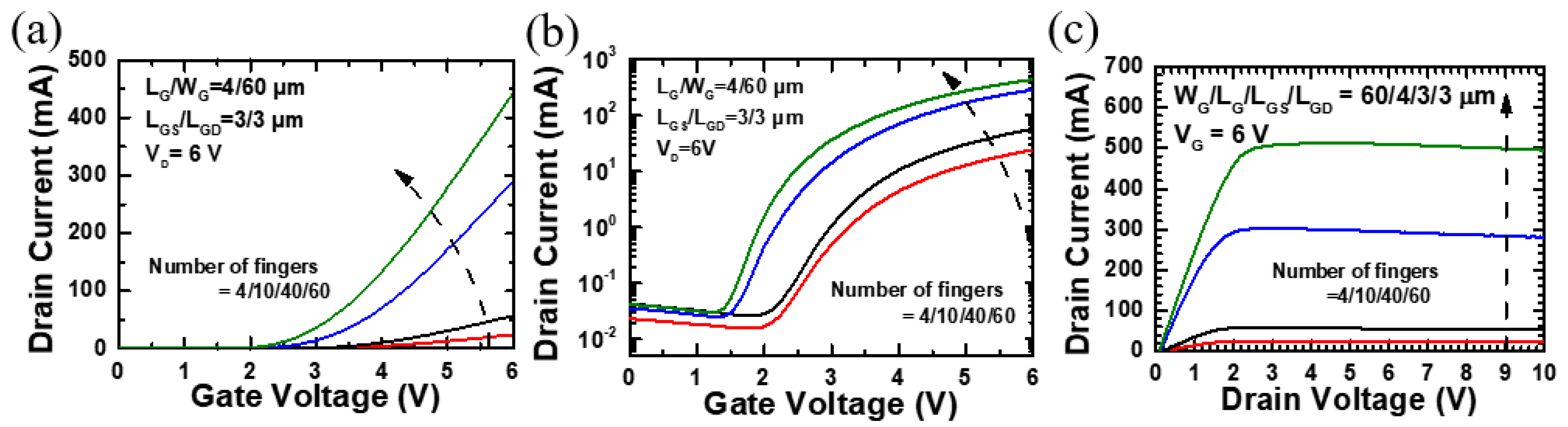

3.2. WG = 60 μm Devices with Different Number of Fingers

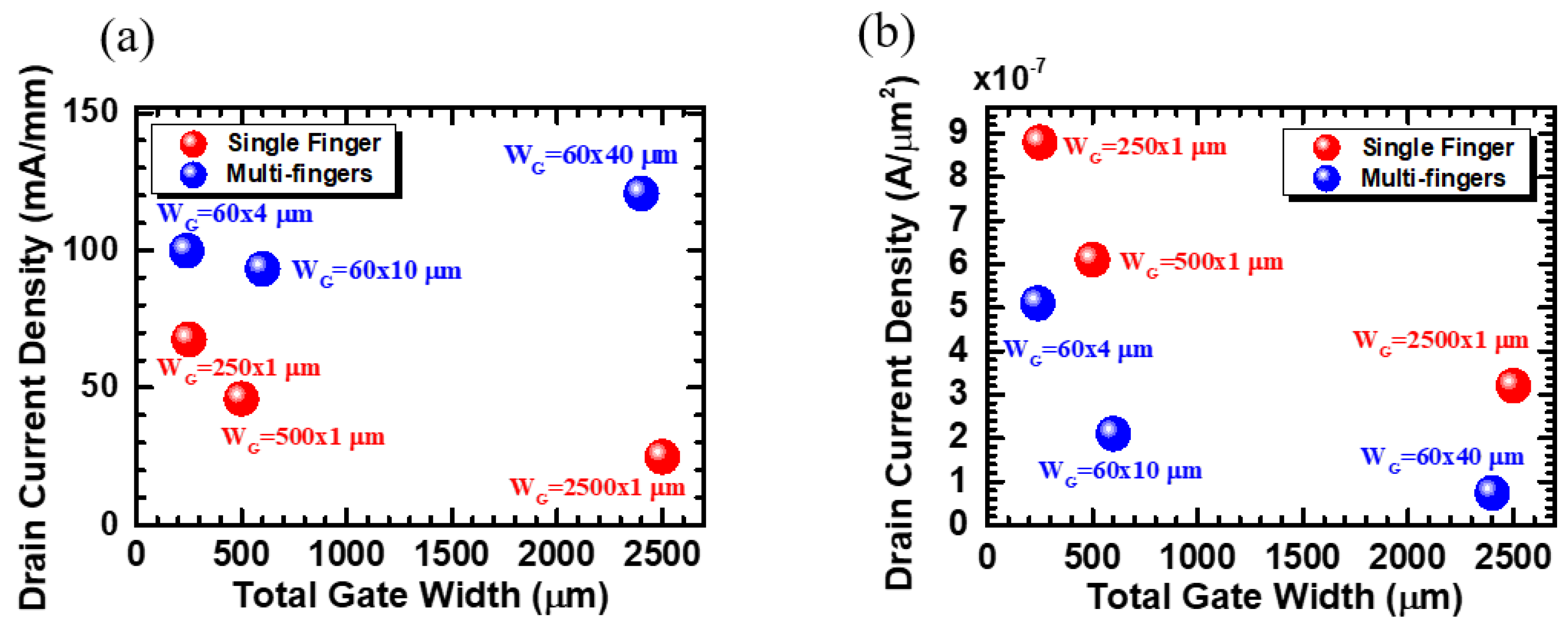

3.3. Summary of the Multi-Finger Layout Devices

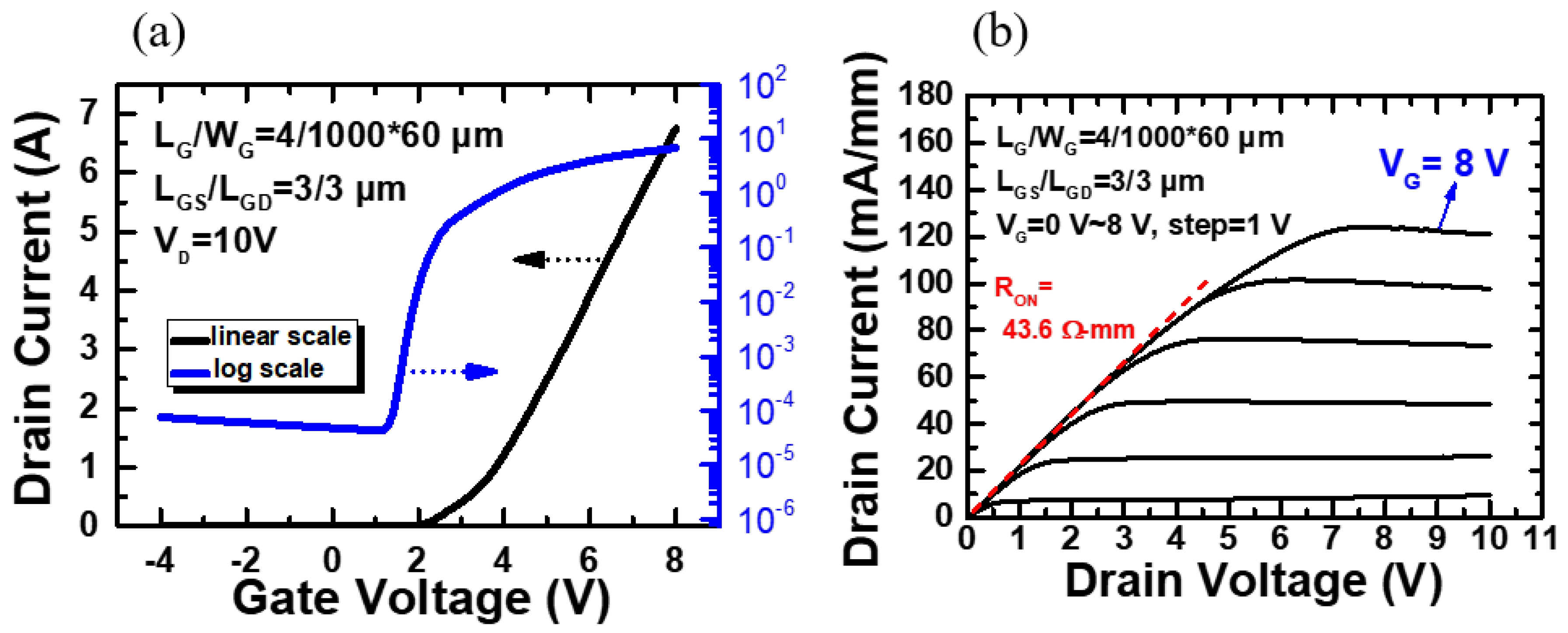

3.4. Large-Area p-GaN HEMT with High Drain Current Power Device Performance

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Ding, X.; Zhou, Y.; Cheng, J. A review of gallium nitride power device and its applications in motor drive. CES Trans. Electr. Mach. Syst. 2019, 3, 54–64. [Google Scholar] [CrossRef]

- Millan, J.; Godignon, P.; Perpina, X.; Perez-Tomas, A.; Rebollo, J. A Survey of Wide Bandgap Power Semiconductor Devices. IEEE Trans. Power Electron. 2014, 29, 2155–2163. [Google Scholar] [CrossRef]

- Chen, K.J.; Haberlen, O.; Lidow, A.; Tsai, C.L.; Ueda, T.; Uemoto, Y.; Wu, Y. GaN-on-Si Power Technology: Devices and Applications. IEEE Trans. Electron Devices 2017, 64, 779–795. [Google Scholar] [CrossRef]

- Wu, Y.-F.; Gritters, J.; Shen, L.; Smith, R.P.; Swenson, B. kV-Class GaN-on-Si HEMTs Enabling 99% Efficiency Converter at 800 V and 100 kHz. IEEE Trans. Power Electron. 2014, 29, 2634–2637. [Google Scholar] [CrossRef]

- Meneghesso, G.; Meneghini, M.; Zanoni, E. Breakdown mechanisms in AlGaN/GaN HEMTs: An overview. Jpn. J. Appl. Phys. 2014, 53, 100211. [Google Scholar] [CrossRef]

- Cai, Y.; Zhou, Y.; Chen, K.J.; Lau, K.M. High-performance enhancement-mode AlGaN/GaN HEMTs using fluoride-based plasma treatment. IEEE Electron Device Lett. 2005, 26, 435–437. [Google Scholar] [CrossRef]

- Chu, R.; Corrion, A.; Chen, M.; Li, R.; Wong, D.; Zehnder, D.; Hughes, B.; Boutros, K. 1200-V Normally Off GaN-on-Si Field-Effect Transistors With Low Dynamic on -Resistance. IEEE Electron Device Lett. 2011, 32, 632–634. [Google Scholar] [CrossRef]

- Lee, C.-H.; Lin, W.-R.; Lee, Y.-H.; Huang, J.-J. Characterizations of Enhancement-Mode Double Heterostructure GaN HEMTs With Gate Field Plates. IEEE Trans. Electron Devices 2018, 65, 488–492. [Google Scholar] [CrossRef]

- Cai, Y.; Zhou, Y.; Lau, K.M.; Chen, K.J. Control of Threshold Voltage of AlGaN/GaN HEMTs by Fluoride-Based Plasma Treatment: From Depletion Mode to Enhancement Mode. IEEE Trans. Electron Devices 2006, 53, 2207–2215. [Google Scholar] [CrossRef]

- Huang, S.; Liu, X.; Wang, X.; Kang, X.; Zhang, J.; Fan, J.; Shi, J.; Wei, K.; Zheng, Y.; Gao, H.; et al. Ultrathin-Barrier AlGaN/GaN Heterostructure: A Recess-Free Technology for Manufacturing High-Performance GaN-on-Si Power Devices. IEEE Trans. Electron Devices 2018, 65, 207–214. [Google Scholar] [CrossRef]

- Saito, W.; Takada, Y.; Kuraguchi, M.; Tsuda, K.; Omura, I. Recessed-gate structure approach toward normally off high-Voltage AlGaN/GaN HEMT for power electronics applications. IEEE Trans. Electron Devices 2006, 53, 356–362. [Google Scholar] [CrossRef]

- Uemoto, Y.; Hikita, M.; Ueno, H.; Matsuo, H.; Ishida, H.; Yanagihara, M.; Ueda, T.; Tanaka, T.; Ueda, D. Gate Injection Transistor (GIT)—A Normally-Off AlGaN/GaN Power Transistor Using Conductivity Modulation. IEEE Trans. Electron Devices 2007, 54, 3393–3399. [Google Scholar] [CrossRef]

- Wang, H.; Wei, J.; Xie, R.; Liu, C.; Tang, G.; Chen, K.J. Maximizing the Performance of 650-V p-GaN Gate HEMTs: Dynamic RON Characterization and Circuit Design Considerations. IEEE Trans. Power Electronics 2017, 32, 5539–5549. [Google Scholar] [CrossRef]

- Tang, X.; Li, B.; Amini, H.; Tanner, P.; Han, J.; Dimitrijev, S. Mechanism of Threshold Voltage Shift in p -GaN Gate AlGaN/GaN Transistors. IEEE Electron Device Lett. 2018, 39. [Google Scholar] [CrossRef]

- Suzuki, Y.; Tone, K.; Asubar, J.T.; Tokuda, H.; Kuzuhara, M. High drain current and low on-resistance in AlGaN/GaN HEMTs with Au-plated ohmic electrodes. In Proceedings of the 2015 IEEE International Meeting for Future of Electron Devices, Kansai (IMFEDK), Kyoto, Japan, 4–5 June 2015; pp. 52–53. [Google Scholar]

- Zhang, N.; Mehrotra, V.; Chandrasekaran, S.; Moran, B.; Shen, L.; Mishra, U.; Etzkorn, E.; Clarke, D. Large area GaN HEMT power devices for power electronic applications: Switching and temperature characteristics. In Proceedings of the IEEE 34th Annual Conference on Power Electronics Specialist, PESC ’03, Acapulco, Mexico, 15–19 June 2003. [Google Scholar]

- Reiner, R.; Waltereit, P.; Benkhelifa, F.; Muller, S.; Wespel, M.; Quay, R.; Schlechtweg, M.; Mikulla, M.; Ambacher, O. Benchmarking of Large-Area GaN-on-Si HFET Power Devices for Highly-Efficient, Fast-Switching Converter Applications. In Proceedings of the 2013 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), Monterey, CA, USA, 13–16 October 2013. [Google Scholar]

- Posthuma, N.; You, S.; Liang, H.; Ronchi, N.; Kang, X.; Wellekens, D.; Saripalli, Y.; Decoutere, S. Impact of Mg out-diffusion and activation on the p-GaN gate HEMT device performance. In Proceedings of the 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Prague, Czech Republic, 12–16 June 2016; pp. 95–98. [Google Scholar]

- Xin, X.; Shi, J.; Liu, L.; Edwards, J.; Swaminathan, K.; Pabisz, M.; Murphy, M.; Eastman, L.F.; Pophristic, M. Demonstration of low-leakage-current low-on-resistance 600-V 5.5-A GaN/AlGaN HEMT. IEEE Electron Device Lett. 2009, 30, 1027–1029. [Google Scholar]

- Chvála, A.; Marek, J.; Príbytný, P.; Šatka, A.; Stoffels, S.; Posthuma, N.; Decoutere, S.; Donoval, D. Analysis of multifinger power HEMTs supported by effective 3-D device electrothermal simulation. Microelectron. Reliab. 2017, 78, 148–155. [Google Scholar] [CrossRef]

- Lukens, G.; Hahn, H.; Kalisch, H.; Vescan, A. Self-Aligned Process for Selectively Etched p-GaN-Gated AlGaN/GaN-on-Si HFETs. IEEE Trans/ Electron Devices 2018, 65, 3732–3738. [Google Scholar] [CrossRef]

- Chiu, H.-C.; Chang, Y.-S.; Li, B.-H.; Wang, H.-C.; Kao, H.-L.; Chien, F.-T.; Hu, C.-W.; Xuan, R. High Uniformity Normally-OFF p-GaN Gate HEMT Using Self-Terminated Digital Etching Technique. IEEE Trans. Electron Devices 2018, 65, 4820–4825. [Google Scholar] [CrossRef]

- Burnham, S.D.; Boutros, K.; Hashimoto, P.; Butler, C.; Wong, D.W.S.; Hu, M.; Micovic, M. Gate-recessed normally-off GaN-on- Si HEMT using a new O2-BCl3 digital etching technique. Phys. Status Solidi C 2010, 7, 2010–2012. [Google Scholar] [CrossRef]

- Lin, Y.; Lin, Y.C.; Lumbantoruan, F.; Dec, C.F.; Majilis, B.Y.; Chang, E.Y. A Novel Digital Etch Technique for p-GaN Gate HEMT. In Proceedings of the 2018 IEEE International Conference on Semiconductor Electronics (ICSE), Kuala Lumpur, Malaysia, 15–17 August 2018. [Google Scholar]

- Hahn, H.; Lükens, G.; Ketteniss, N.; Kalisch, H.; Vescan, A. Recessed-Gate Enhancement-Mode AlGaN/GaN Heterostructure Field-Effect Transistors on Si with Record DC Performance. Appl. Phys. Express 2011, 4, 114102. [Google Scholar] [CrossRef]

- Green, R.T.; Luxmoore, I.J.; Lee, K.B.; Houston, P.A.; Ranalli, F.; Wang, T.; Parbrook, P.J.; Uren, M.J.; Wallis, D.J.; Martin, T. Characterization of gate recessed GaN/AlGaN/GaN high electron mobility transistors fabricated using a SiCl4/SF6 dry etch recipe. J. Appl. Phys. 2010, 108, 013711. [Google Scholar] [CrossRef]

- Wong, J.C.; Micovic, M.; Brown, D.F.; Khalaf, I.; Williams, A.; Corrion, A. Selective anisotropic etching of GaN over AlGaN for very thin films. J. Vac. Sci. Technol A Vac. Surfaces Films 2018, 36, 030603. [Google Scholar] [CrossRef]

- Zhou, S.; Cao, B.; Liu, S. Dry etching characteristics of GaN using Cl2/BCl3 inductively coupled plasmas. Appl. Surface Sci. 2010, 257, 905–910. [Google Scholar] [CrossRef]

- Tülek, R.; Ilgaz, A.; Gökden, S.; Teke, A.; Öztürk, M.K.; Kasap, M.; Özçelik, S.; Arslan, E.; Özbay, E. Comparison of the transport properties of high quality AlGaN/AlN/GaN and AlInN/AlN/GaN two-dimensional electron gas heterostructures. J. Appl. Phys. 2009, 105, 013707. [Google Scholar] [CrossRef]

| Devices | A | B | C | D | E |

|---|---|---|---|---|---|

| Total gate width (μm) | 60 | 120 | 250 | 500 | 2500 |

| Single WG (μm) | 60 | 120 | 250 | 500 | 2500 |

| # of fingers | 1 | 1 | 1 | 1 | 1 |

| Active area (μm2) | 4560 | 9120 | 19,000 | 38,000 | 190,000 |

| IDS,on (mA/mm) | 73.39 | 69.735 | 67.608 | 46.012 | 24.875 |

| IDS,on (mA/μm2) | 9.7 × 10−4 | 9.2 × 10−4 | 8.8 × 10−4 | 6.1 × 10−4 | 3.2 × 10−4 |

| Devices | F | G | H | I |

|---|---|---|---|---|

| Total gate width (μm) | 240 | 600 | 2400 | 3600 |

| Single WG (μm) | 60 | 60 | 60 | 60 |

| # of fingers | 4 | 10 | 40 | 60 |

| Active area (μm2) | 11,760 | 36,160 | 98,160 | 146,160 |

| IDS,on (mA/mm) | 99.87 | 93.29 | 120.7 | 140.56 |

| IDS,on (mA/μm2) | 5.1 × 10−4 | 2.1 × 10−4 | 7.4 × 10−5 | 5.8 × 10−5 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chang, Y.-C.; Ho, Y.-L.; Huang, T.-Y.; Huang, D.-W.; Wu, C.-H. Investigation of Normally-Off p-GaN/AlGaN/GaN HEMTs Using a Self-Terminating Etching Technique with Multi-Finger Architecture Modulation for High Power Application. Micromachines 2021, 12, 432. https://doi.org/10.3390/mi12040432

Chang Y-C, Ho Y-L, Huang T-Y, Huang D-W, Wu C-H. Investigation of Normally-Off p-GaN/AlGaN/GaN HEMTs Using a Self-Terminating Etching Technique with Multi-Finger Architecture Modulation for High Power Application. Micromachines. 2021; 12(4):432. https://doi.org/10.3390/mi12040432

Chicago/Turabian StyleChang, Ya-Chun, Yu-Li Ho, Tz-Yan Huang, Ding-Wei Huang, and Chao-Hsin Wu. 2021. "Investigation of Normally-Off p-GaN/AlGaN/GaN HEMTs Using a Self-Terminating Etching Technique with Multi-Finger Architecture Modulation for High Power Application" Micromachines 12, no. 4: 432. https://doi.org/10.3390/mi12040432

APA StyleChang, Y.-C., Ho, Y.-L., Huang, T.-Y., Huang, D.-W., & Wu, C.-H. (2021). Investigation of Normally-Off p-GaN/AlGaN/GaN HEMTs Using a Self-Terminating Etching Technique with Multi-Finger Architecture Modulation for High Power Application. Micromachines, 12(4), 432. https://doi.org/10.3390/mi12040432