Improving the Performance of the ToGoFET Probe: Advances in Design, Fabrication, and Signal Processing

Abstract

1. Introduction

2. Re-Design of the ToGoFET Probe

2.1. Operating Principle

2.2. Structural Design Modification

3. Fabrication

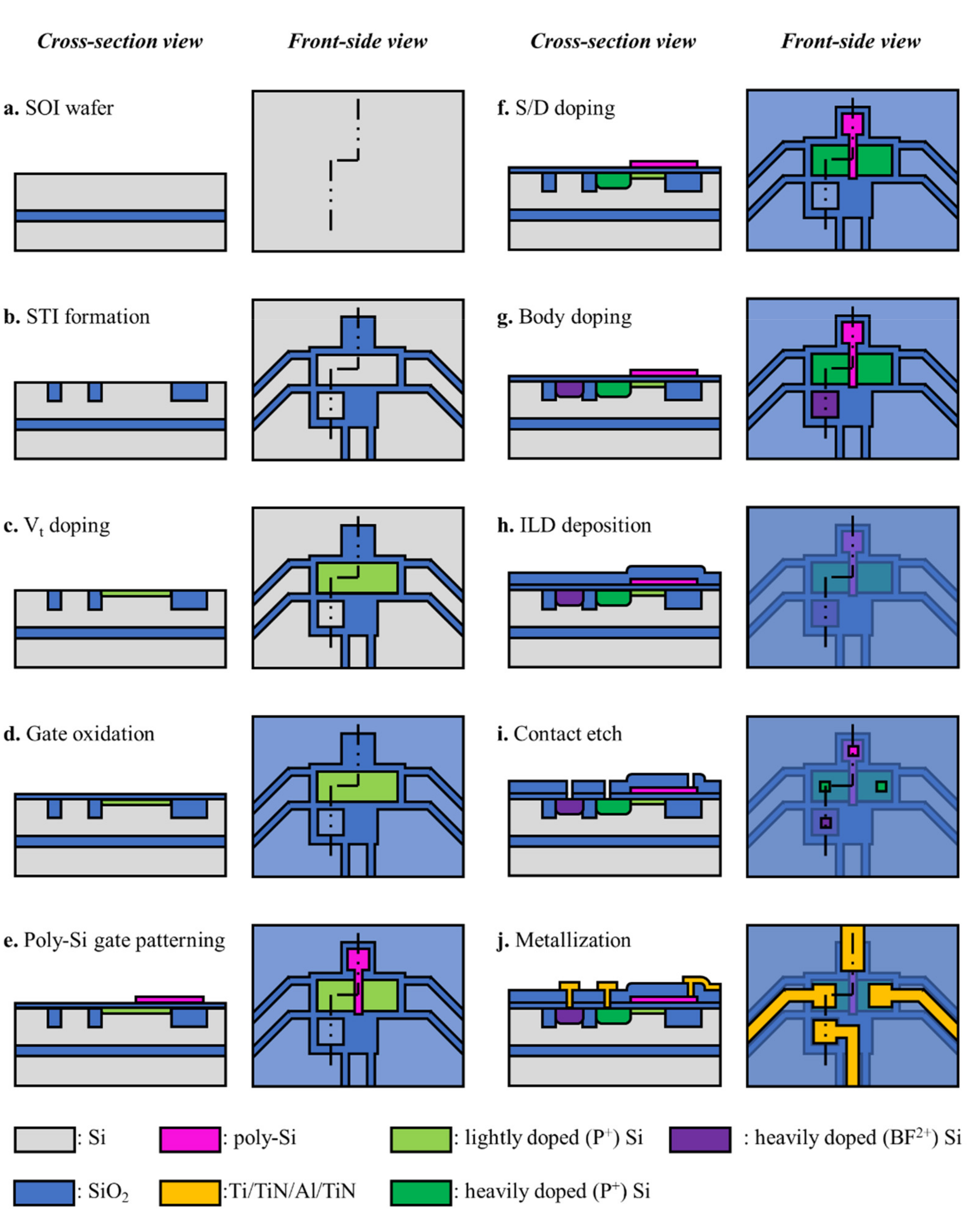

3.1. The Standard CMOS Process

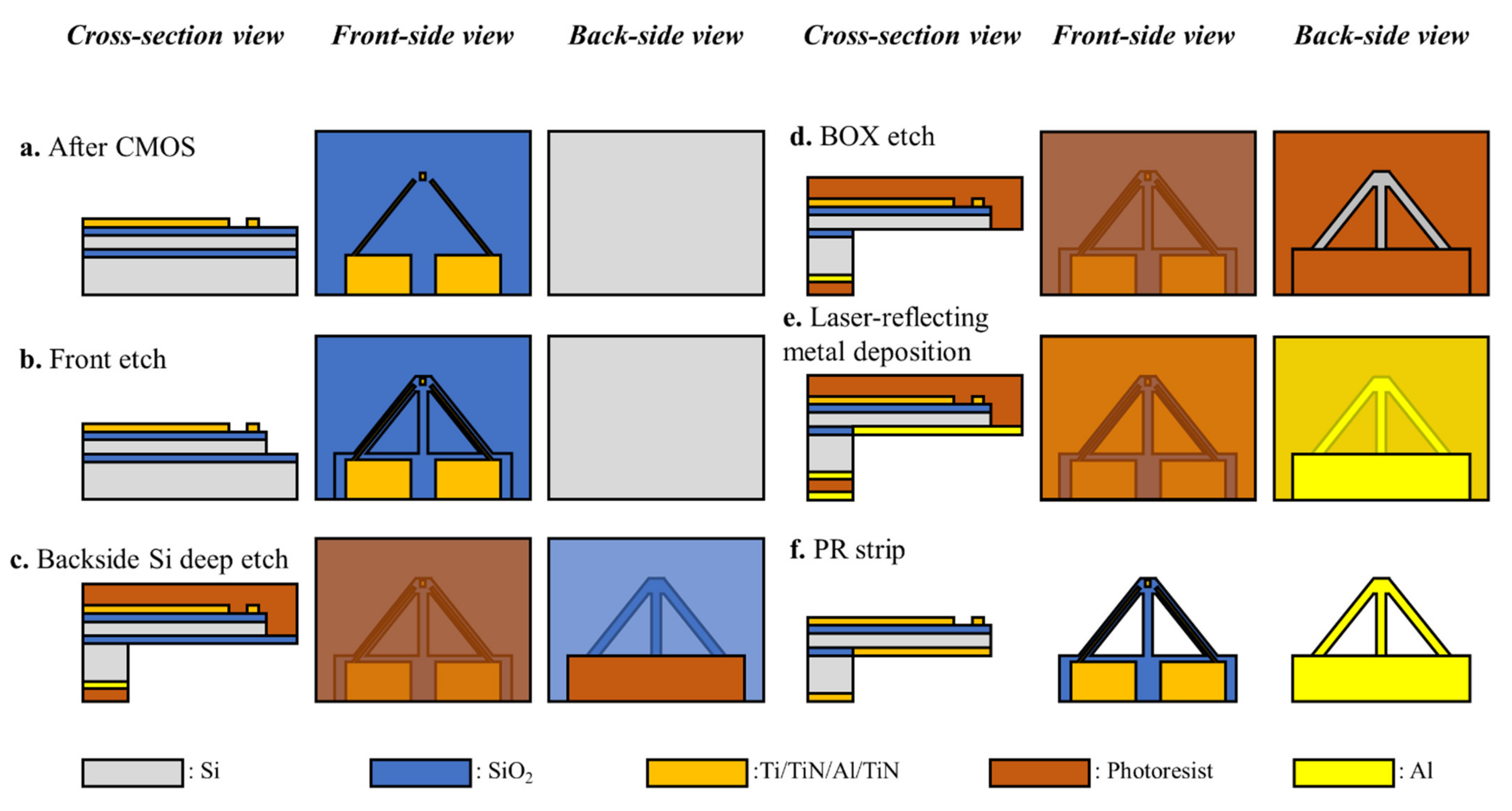

3.2. Cantilever Release

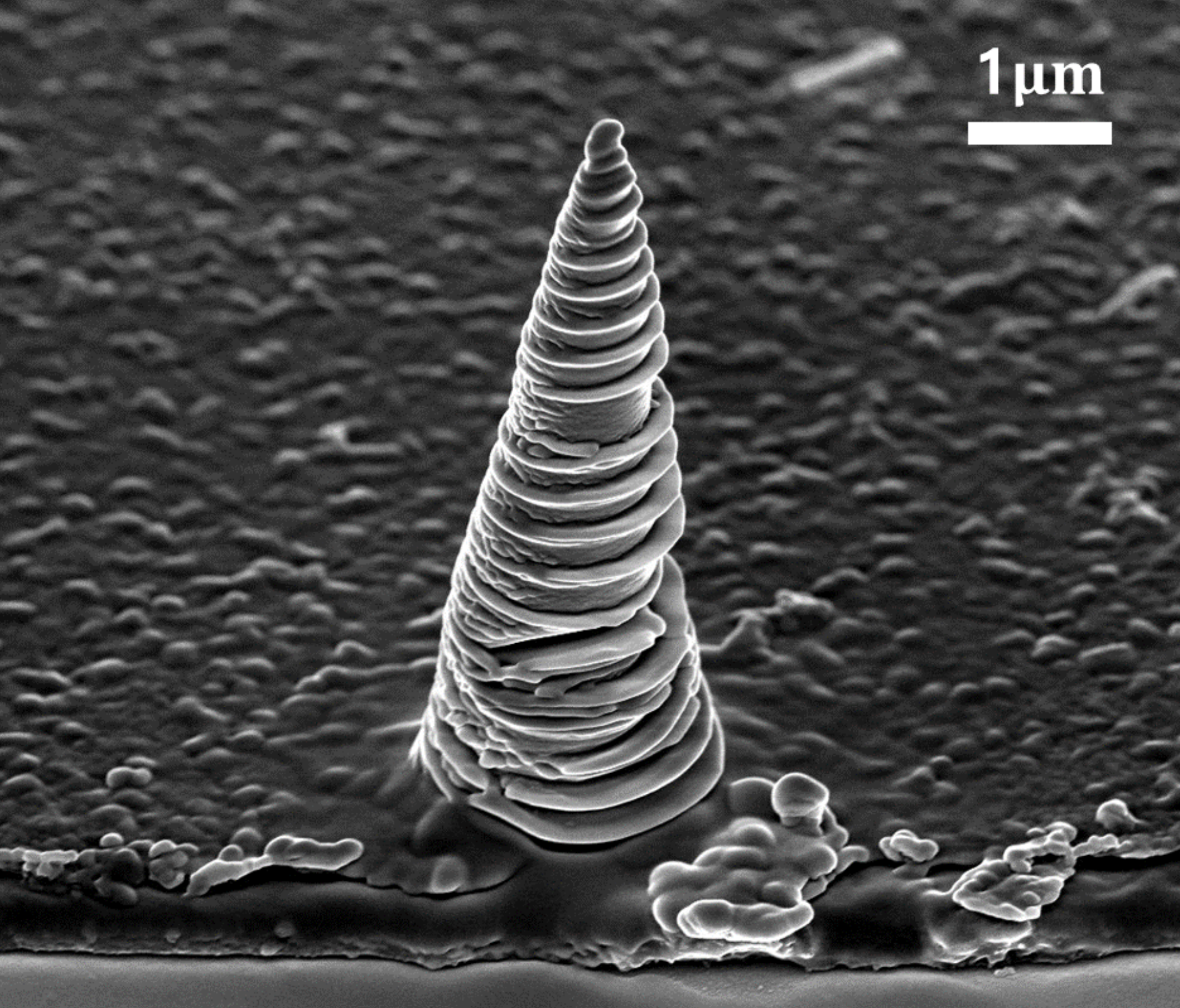

3.3. Conductive Tip Fabrication

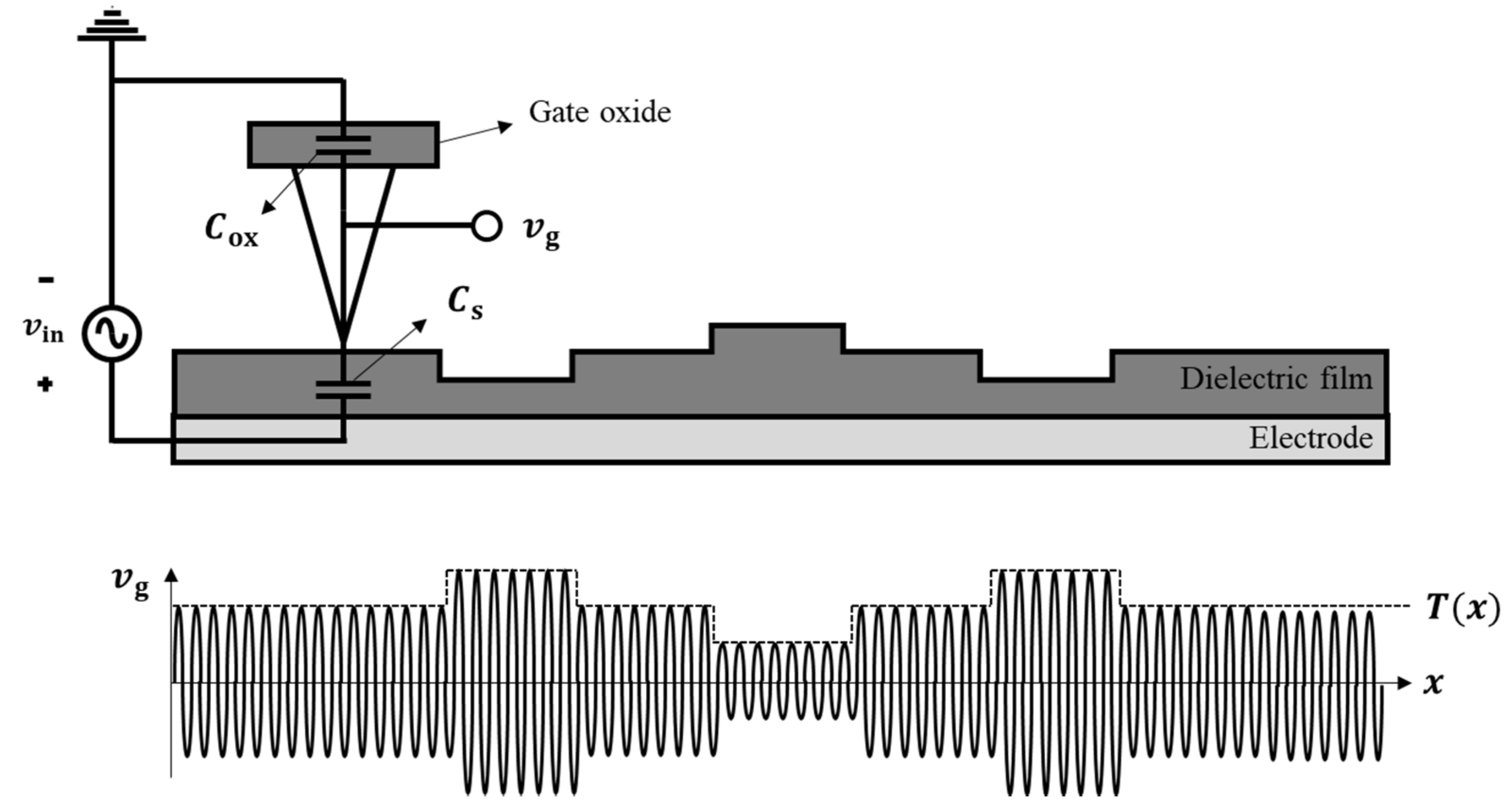

4. Signal Processing and Measurement Set-Up

4.1. Amplitude Modulation

4.2. Circuits for the Demodulation

4.3. Measurement Set-Up

5. Measurements

5.1. I-V Characteristics of Inbuilt MOSFET

5.2. Sample Information

5.3. Frequency Response

5.4. Buried Electrode Imaging

5.5. Discussion

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Binnig, G.; Quate, C.F.; Gerber, C. Atomic force microscope. Phys. Rev. Lett. 1986, 56, 930–933. [Google Scholar] [CrossRef]

- Martin, Y.; Abraham, D.W.; Wickramasinghe, H.K. High-resolution capacitance measurement and potentiometry by force microscopy. Appl. Phys. Lett. 1988, 52, 1103–1105. [Google Scholar] [CrossRef]

- Nonnenmacher, M.; O’Boyle, M.; Wickramasinghe, H.K. Kelvin probe force microscopy. Appl. Phys. Lett. 1991, 58, 2921–2923. [Google Scholar] [CrossRef]

- Matey, J.; Blanc, J. Scanning capacitance microscopy. J. Appl. Phys. 1985, 57, 1437–1444. [Google Scholar] [CrossRef]

- Williams, C.; Wickramasinghe, H. Scanning thermal profiler. Microelectron. Eng. 1986, 5, 509–513. [Google Scholar] [CrossRef]

- Martin, Y.; Wickramasinghe, H.K. Magnetic imaging by ‘‘force microscopy’’with 1000 Å resolution. Appl. Phys. Lett. 1987, 50, 1455–1457. [Google Scholar] [CrossRef]

- Abraham, D.W.; Williams, C.; Slinkman, J.; Wickramasinghe, H. Lateral dopant profiling in semiconductors by force microscopy using capacitive detection. J. Vac. Sci. Technol. B 1991, 9, 703–706. [Google Scholar] [CrossRef]

- Fumagalli, L.; Gramse, G.; Esteban-Ferrer, D.; Edwards, M.; Gomila, G. Quantifying the dielectric constant of thick insulators using electrostatic force microscopy. Appl. Phys. Lett. 2010, 96, 183107. [Google Scholar] [CrossRef]

- Kikukawa, A.; Hosaka, S.; Imura, R. Silicon pn junction imaging and characterizations using sensitivity enhanced Kelvin probe force microscopy. Appl. Phys. Lett. 1995, 66, 3510–3512. [Google Scholar] [CrossRef]

- Burke, S.; LeDue, J.; Miyahara, Y.; Topple, J.; Fostner, S.; Grütter, P. Determination of the local contact potential difference of PTCDA on NaCl: A comparison of techniques. Nanotechnology 2009, 20, 264012. [Google Scholar] [CrossRef]

- Kopanski, J.J.; Marchiando, J.F.; Lowney, J.R. Scanning capacitance microscopy measurements and modeling: Progress towards dopant profiling of silicon. J. Vac. Sci. Technol. B 1996, 14, 242–247. [Google Scholar] [CrossRef]

- Lee, D.; Pelz, J.; Bhushan, B. Scanning capacitance microscopy for thin film measurements. Nanotechnology 2006, 17, 1484–1491. [Google Scholar] [CrossRef]

- De Wolf, P.; Clarysse, T.; Vandervorst, W.; Hellemans, L.; Niedermann, P.; Hänni, W. Cross-sectional nano-spreading resistance profiling. J. Vac. Sci. Technol. B 1998, 16, 355–361. [Google Scholar] [CrossRef]

- Eyben, P.; Alvarez, D.; Clarysse, T.; Denis, S.; Vandervorst, W. Recent Progress and Insights in Two-Dimensional Carrier Profiling Using Scanning Spreading Resistance Microscopy; Proceedings of the AIP Conference Proceedings, Austin, TX, USA, 24–28 March 2003; American Institute of Physics: College Park, MA, USA, 2003; pp. 685–692. [Google Scholar]

- Pandey, K.; Paredis, K.; Hantschel, T.; Drijbooms, C.; Vandervorst, W. The impact of focused ion beam induced damage on scanning spreading resistance microscopy measurements. Sci. Rep. 2020, 10, 14893. [Google Scholar] [CrossRef]

- Suh, M.S.; Choi, J.H.; Kuk, Y.; Jung, J. Silicon-based field-effect-transistor cantilever for surface potential mapping. Appl. Phys. Lett. 2003, 83, 386–388. [Google Scholar] [CrossRef]

- Suh, M.; Lee, C.; Kim, S.; Lee, K.; Cho, J.; Kuk, Y.; Shin, J. Surface potential imaging in oxide-nitride-oxide-silicon structure using a field effect transistor cantilever. Sens. Actuators A Phys. 2007, 136, 597–603. [Google Scholar] [CrossRef]

- Park, H.; Jung, J.; Min, D.-K.; Kim, S.; Hong, S.; Shin, H. Scanning resistive probe microscopy: Imaging ferroelectric domains. Appl. Phys. Lett. 2004, 84, 1734–1736. [Google Scholar] [CrossRef]

- Ko, H.; Ryu, K.; Park, H.; Park, C.; Jeon, D.; Kim, Y.K.; Jung, J.; Min, D.-K.; Kim, Y.; Lee, H.N.; et al. High-resolution field effect sensing of ferroelectric charges. Nano Lett. 2011, 11, 1428–1433. [Google Scholar] [CrossRef] [PubMed]

- Trifonov, A.; Presnov, D.; Bozhev, I.; Evplov, D.; Desmaris, V.; Krupenin, V. Non-contact scanning probe technique for electric field measurements based on nanowire field-effect transistor. Ultramicroscopy 2017, 179, 33–40. [Google Scholar] [CrossRef][Green Version]

- Lee, S.H.; Lim, G.; Moon, W.; Shin, H.; Kim, C.W. V-shaped metal-oxide-semiconductor transistor probe with nano tip for surface electric properties. Ultramicroscopy 2008, 108, 1094–1100. [Google Scholar] [CrossRef]

- Shin, K.; Lee, H.; Sung, M.; Lee, S.H.; Shin, H.; Moon, W. A scanning probe mounted on a field-effect transistor: Characterization of ion damage in Si. Micron 2017, 101, 197–205. [Google Scholar] [CrossRef]

- Shin, K.; Kang, D.S.; Lee, S.H.; Moon, W. A scanning microscopy technique based on capacitive coupling with a field-effect transistor integrated with the tip. Ultramicroscopy 2015, 159, 1–10. [Google Scholar] [CrossRef] [PubMed]

- Lee, H.; Shin, K.; Moon, W. Capacitive Measurements of SiO2 Films of Different Thicknesses Using a MOSFET-Based SPM Probe. Sensors 2021, 21, 4073. [Google Scholar]

- Bedner, K.; Guzenko, V.A.; Tarasov, A.; Wipf, M.; Stoop, R.L.; Rigante, S.; Brunner, J.; Fu, W.; David, C.; Calame, M.; et al. Investigation of the dominant 1/f noise source in silicon nanowire sensors. Sens. Actuators B Chem. 2014, 191, 270–275. [Google Scholar] [CrossRef]

- Hung, K.K.; Ko, P.K.; Hu, C.; Cheng, Y.C. A unified model for the flicker noise in metal-oxide-semiconductor field-effect transistors. IEEE Trans. Electron Devices 1990, 37, 654–665. [Google Scholar] [CrossRef]

- Eriguchi, K.; Ono, K. Impacts of plasma process-induced damage on MOSFET parameter variability and reliability. Microelectron. Reliab. 2015, 55, 1464–1470. [Google Scholar] [CrossRef]

- Tseng, A.A. Recent developments in nanofabrication using focused ion beams. Small 2005, 1, 924–939. [Google Scholar] [CrossRef]

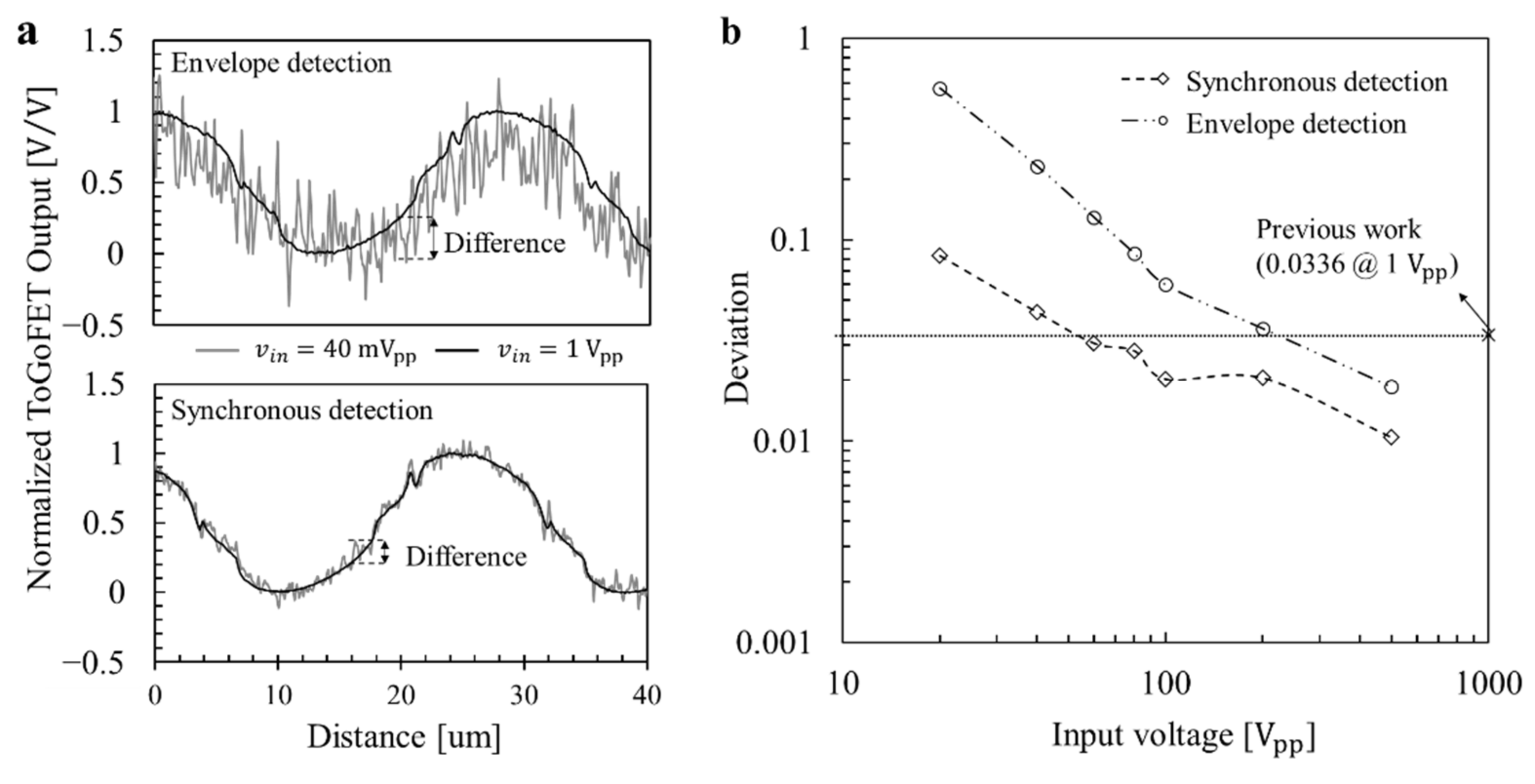

| Methodology | Input Voltage for Same Line Profile Deviation | Note | |

|---|---|---|---|

| Previous study | - | 1000 mVpp (Reference value) | Criterion for quantitative comparison. |

| 1st approach | Modifications of Design and fabrication | 200 mVpp | (@ = 0 V) was increased. (from 177 to 412 A/V) Gate leakage was decreased. (it was confirmed by frequency response) |

| 2nd approach | Adoption of Synchronous detection | 50 mVpp | Noise (deviations along the line profiles) was strongly decreased. |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, H.; Kim, J.; Shin, K.; Moon, W. Improving the Performance of the ToGoFET Probe: Advances in Design, Fabrication, and Signal Processing. Micromachines 2021, 12, 1303. https://doi.org/10.3390/mi12111303

Lee H, Kim J, Shin K, Moon W. Improving the Performance of the ToGoFET Probe: Advances in Design, Fabrication, and Signal Processing. Micromachines. 2021; 12(11):1303. https://doi.org/10.3390/mi12111303

Chicago/Turabian StyleLee, Hoontaek, Junsoo Kim, Kumjae Shin, and Wonkyu Moon. 2021. "Improving the Performance of the ToGoFET Probe: Advances in Design, Fabrication, and Signal Processing" Micromachines 12, no. 11: 1303. https://doi.org/10.3390/mi12111303

APA StyleLee, H., Kim, J., Shin, K., & Moon, W. (2021). Improving the Performance of the ToGoFET Probe: Advances in Design, Fabrication, and Signal Processing. Micromachines, 12(11), 1303. https://doi.org/10.3390/mi12111303