A Tunable-Gain Transimpedance Amplifier for CMOS-MEMS Resonators Characterization

Abstract

1. Introduction

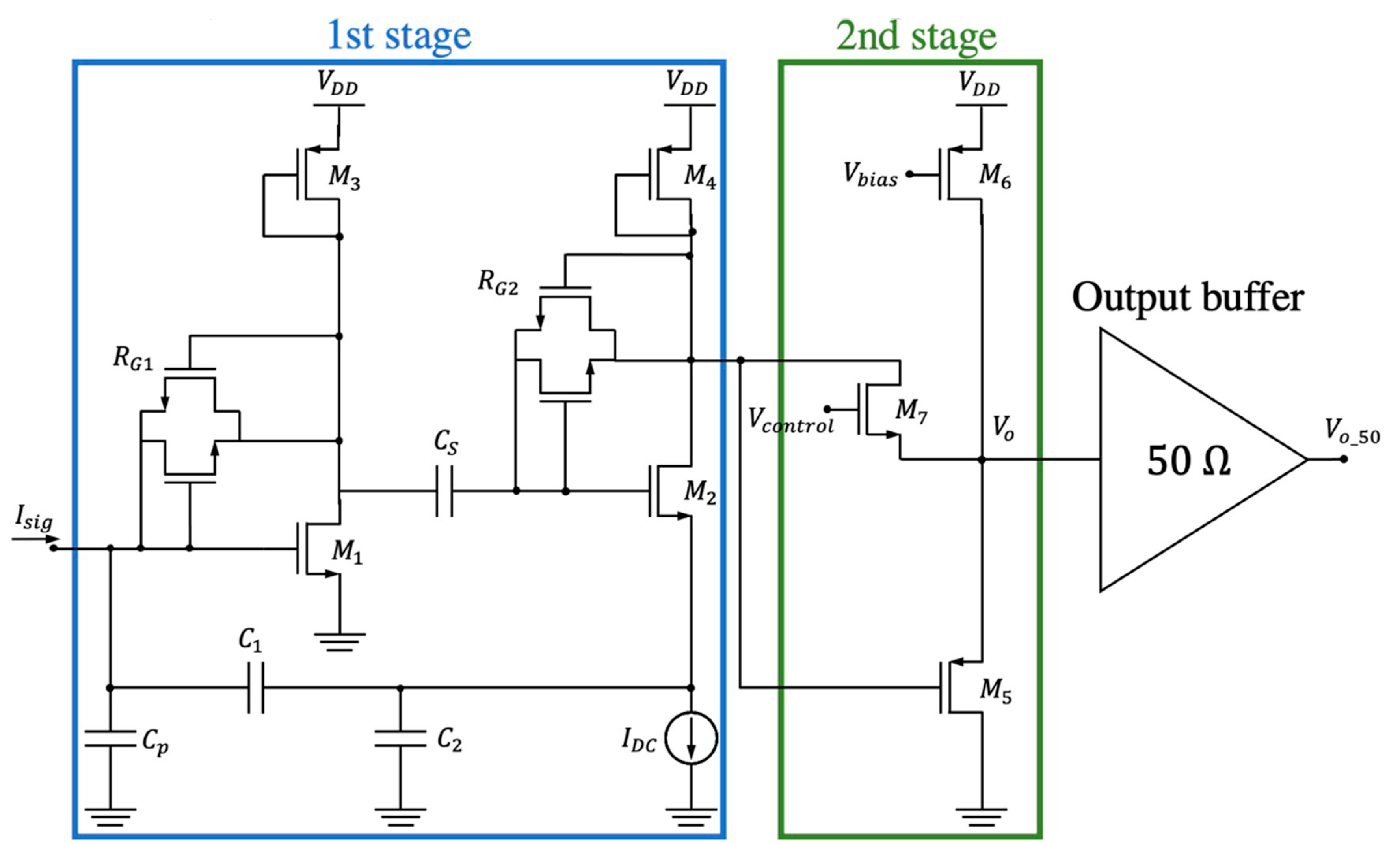

2. Transimpedance Amplifier

3. Oscillator Electromechanical Model

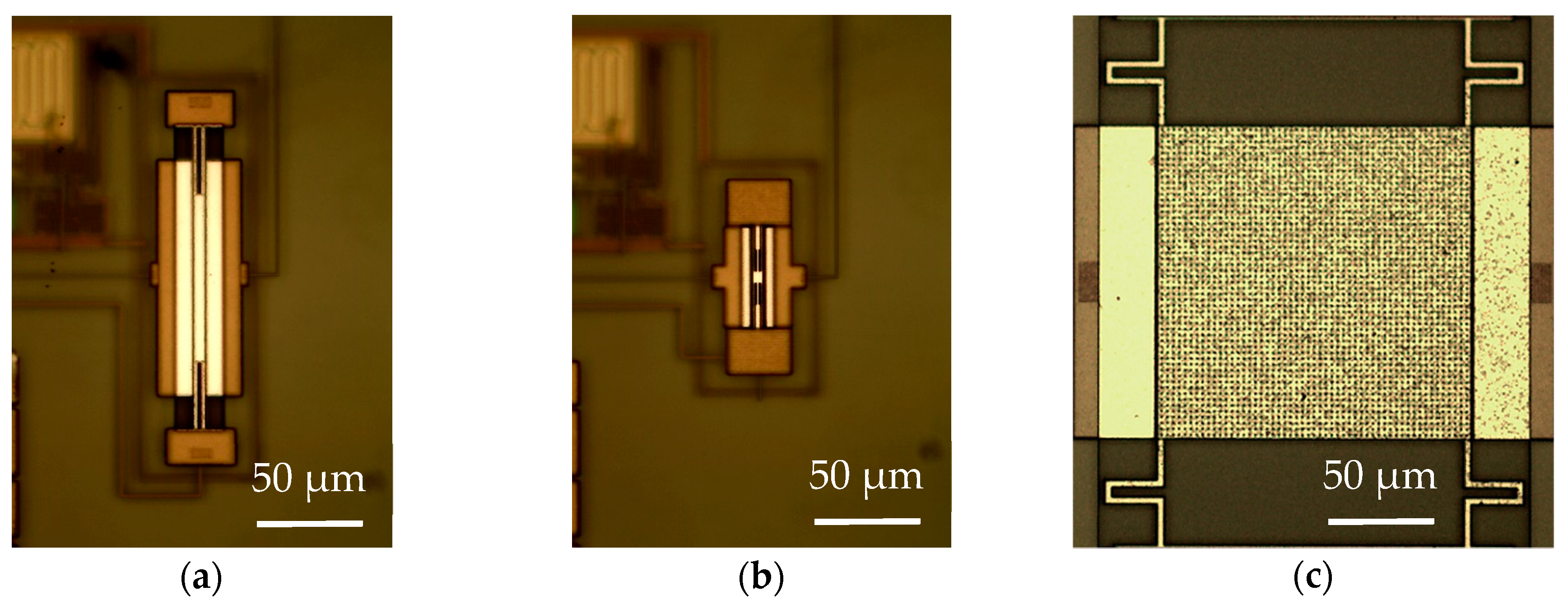

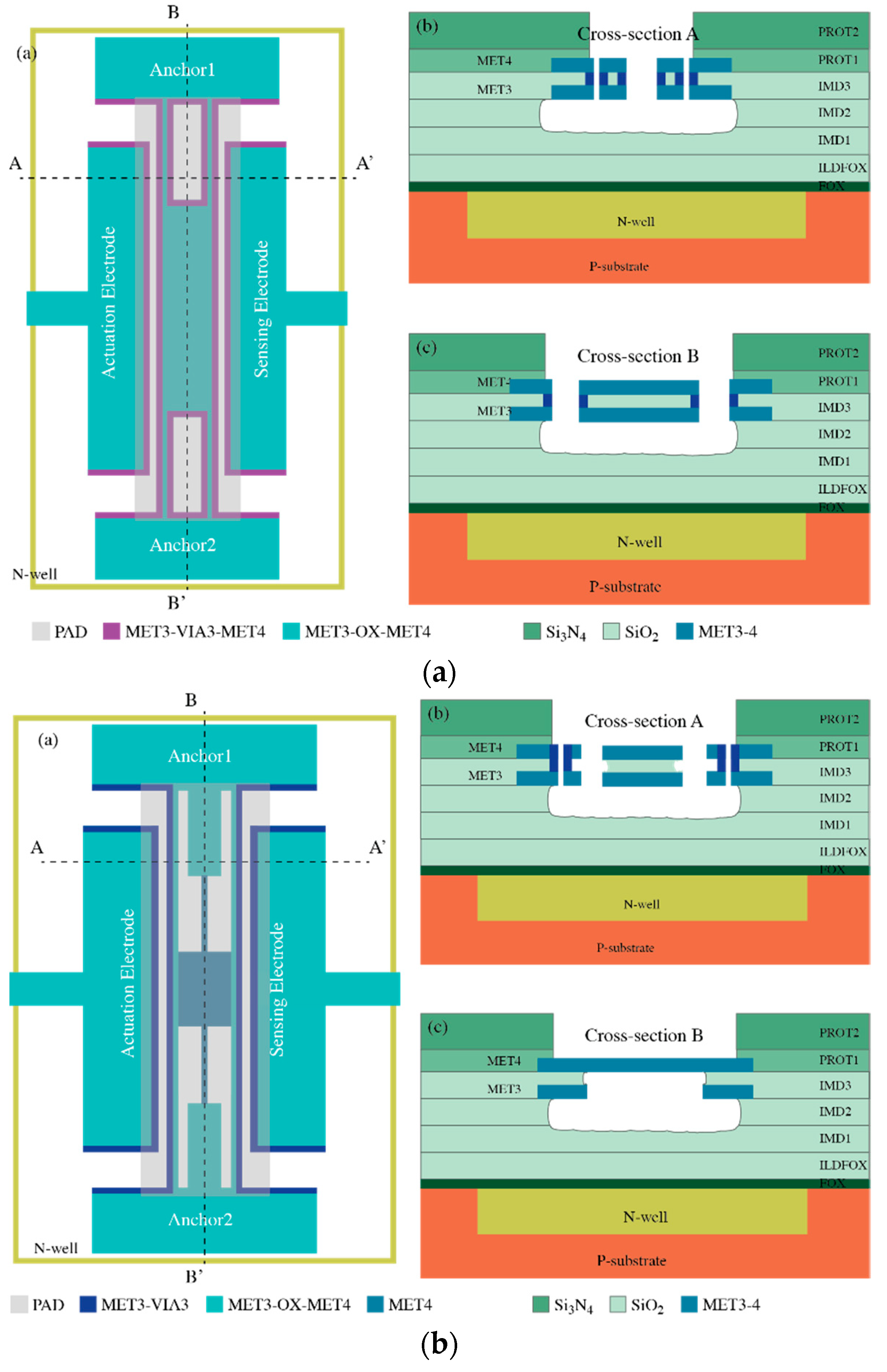

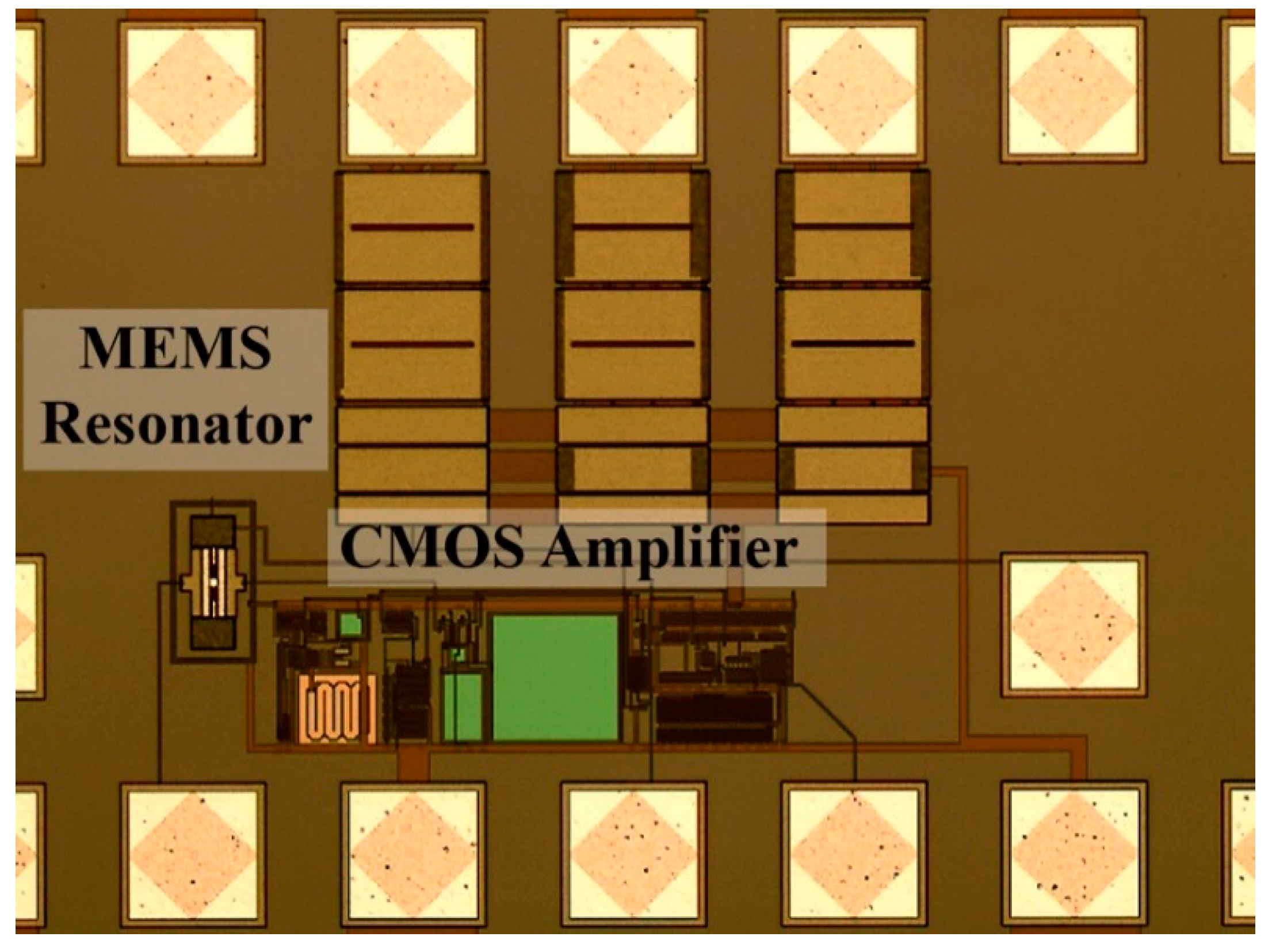

4. MEMS Fabrication and Design

4.1. Plate Resonator 1

4.2. Plate Resonator 2

5. Electrical Characterization

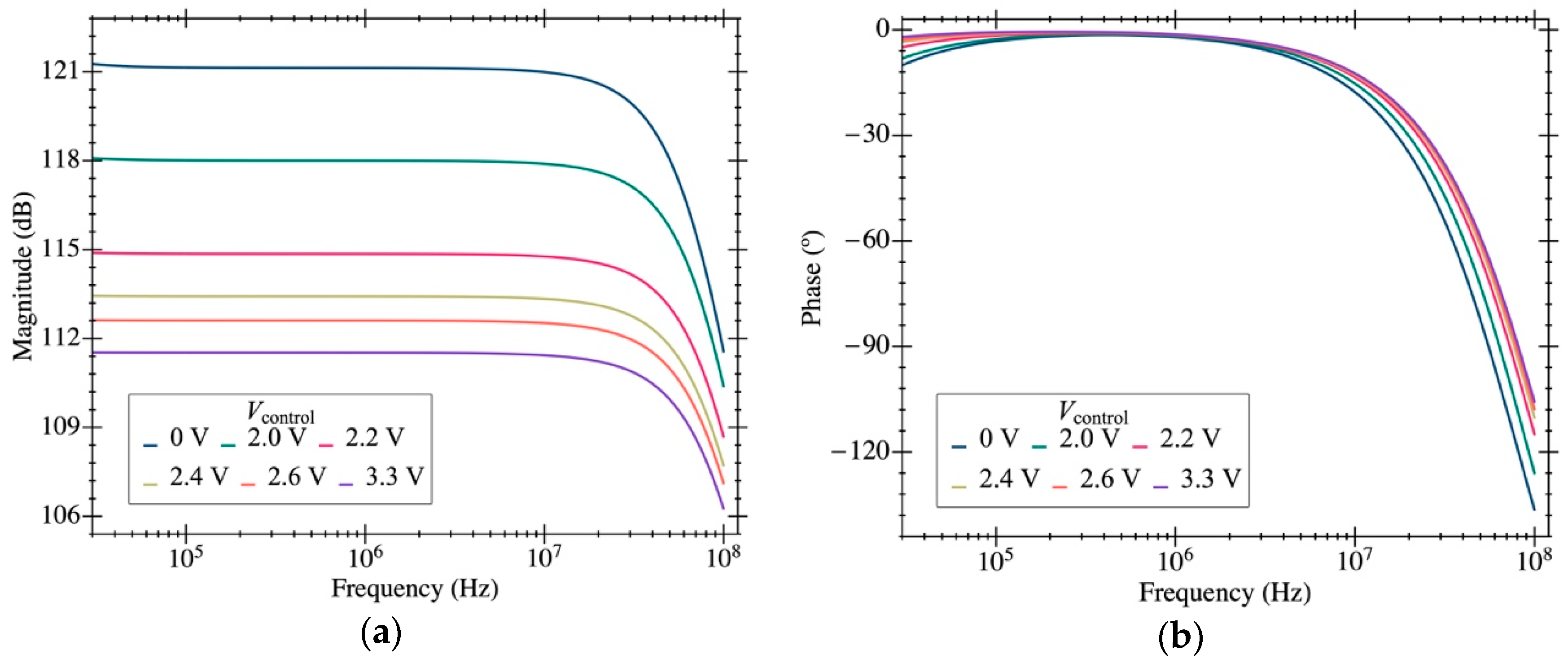

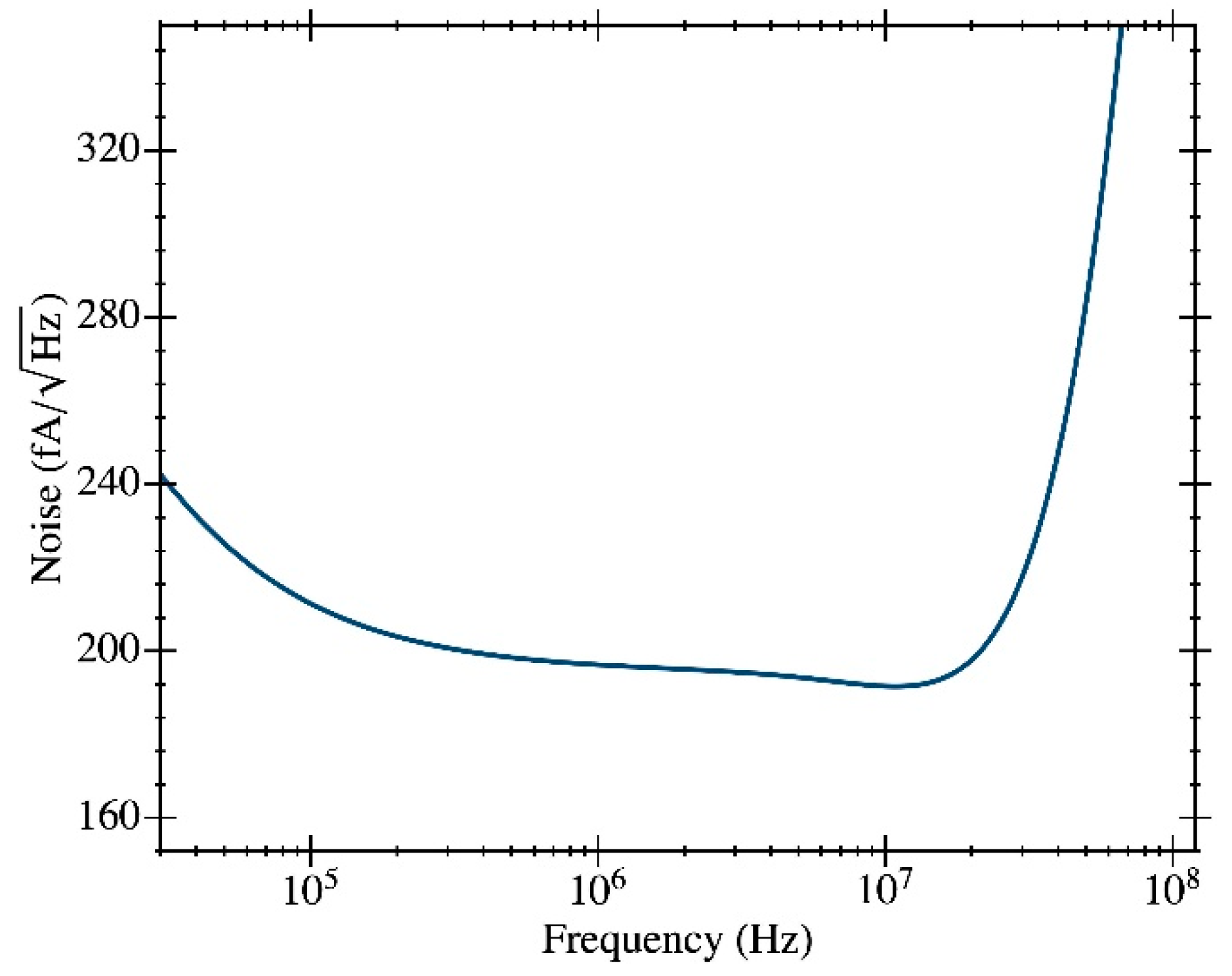

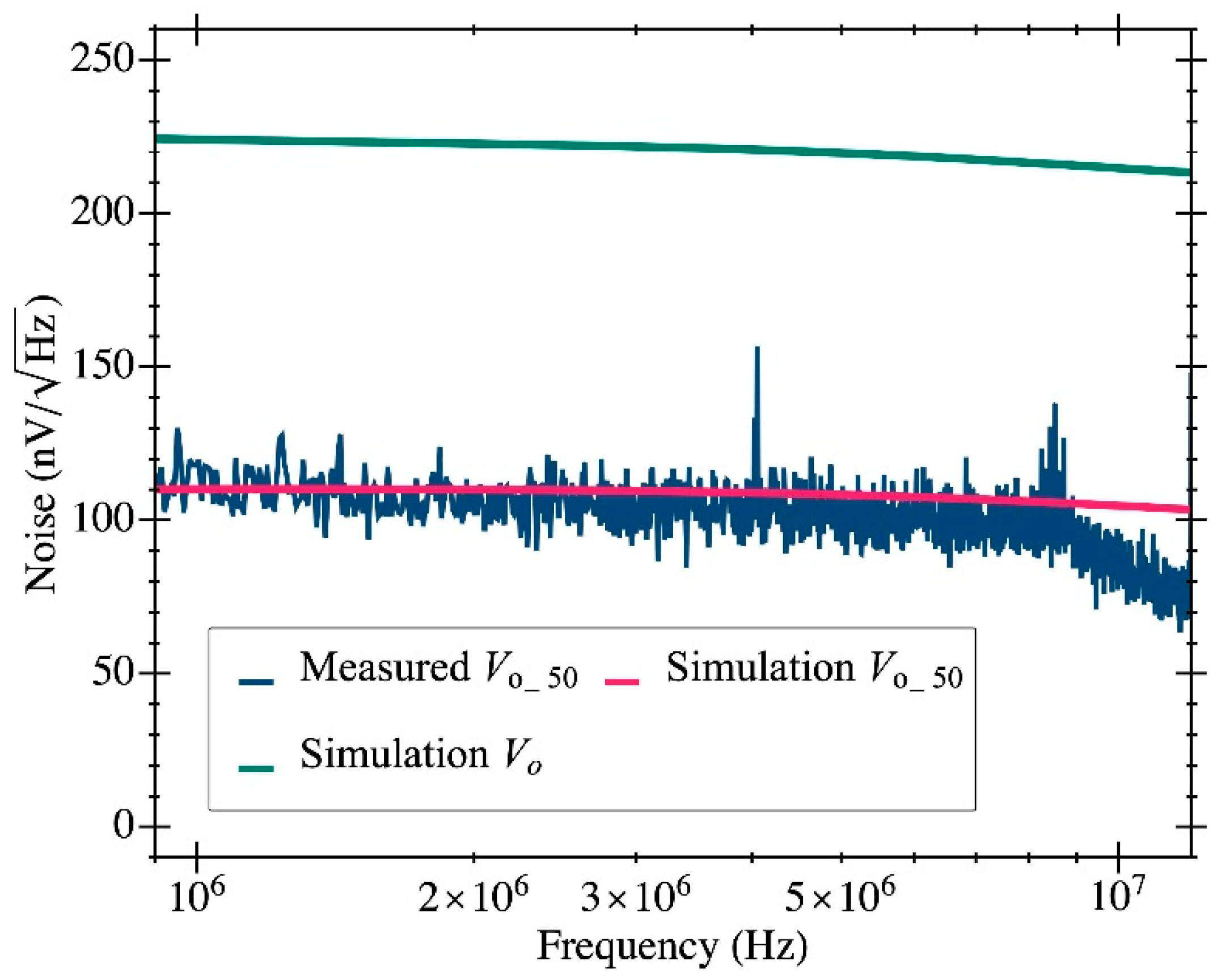

5.1. Transimpedance Amplifier

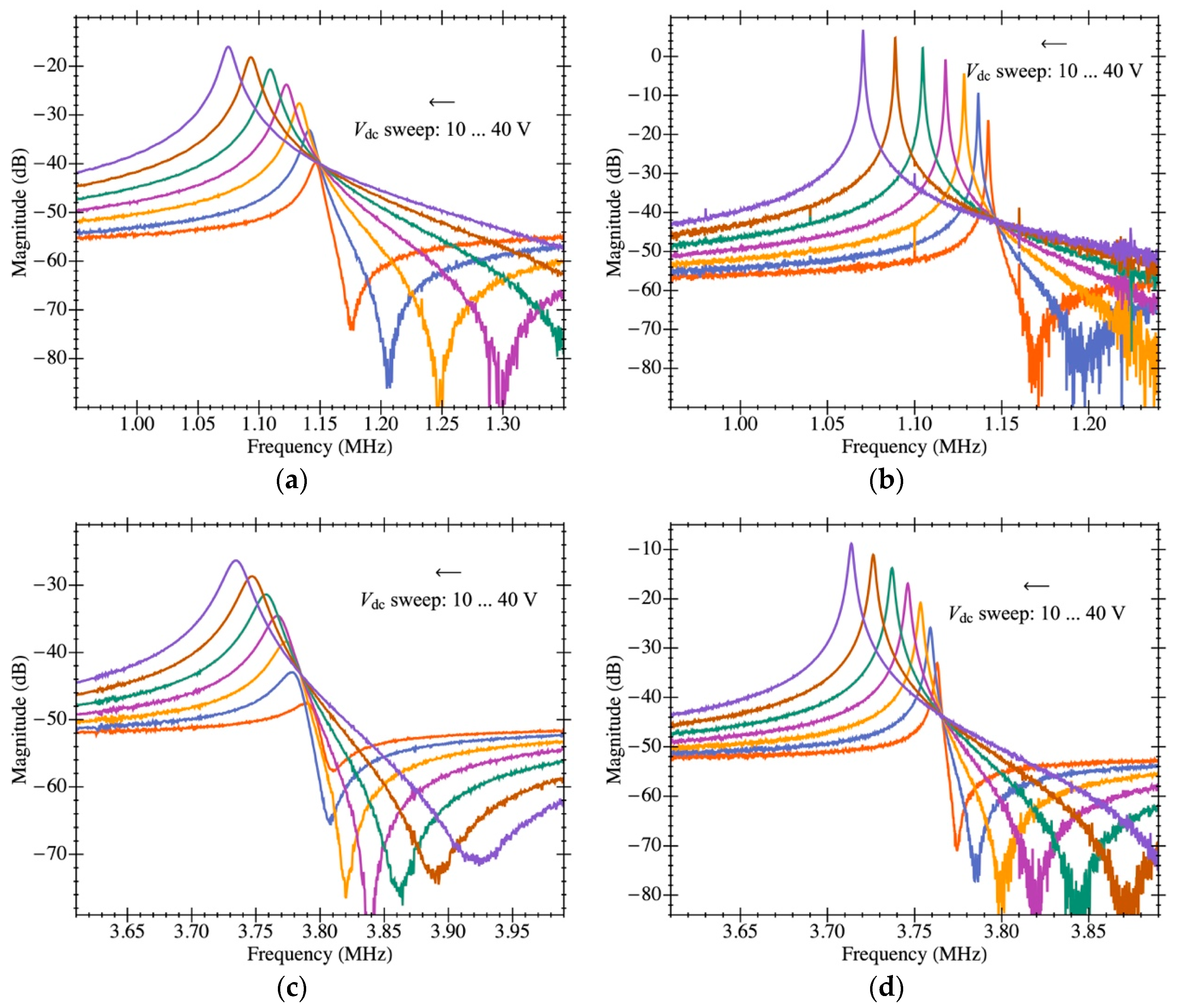

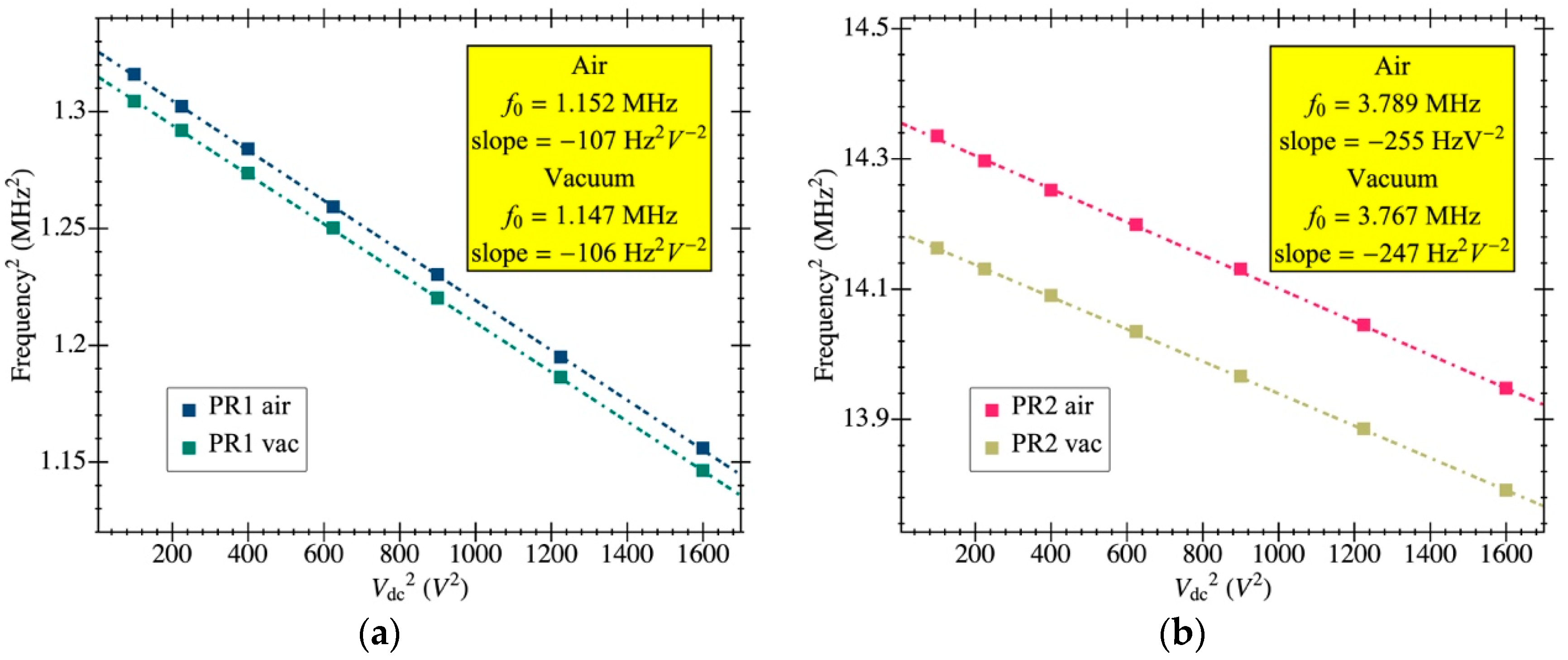

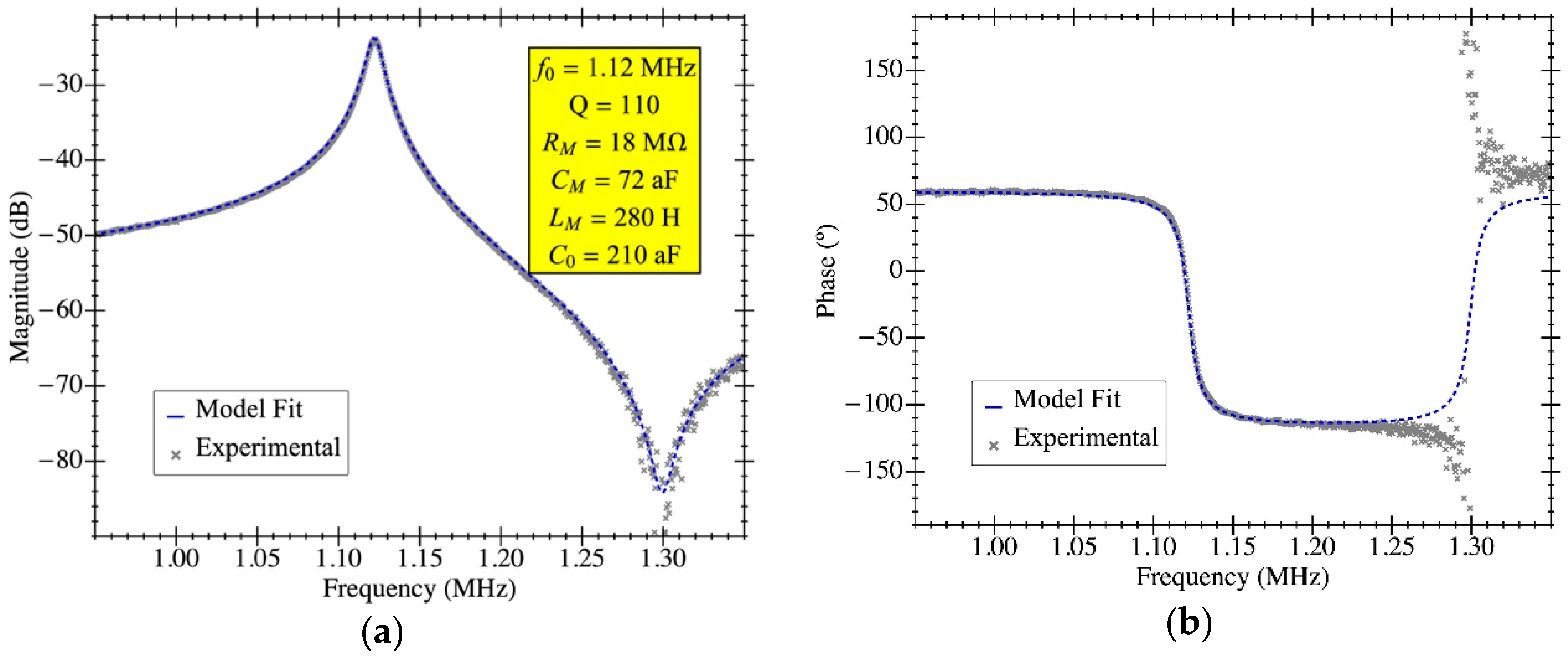

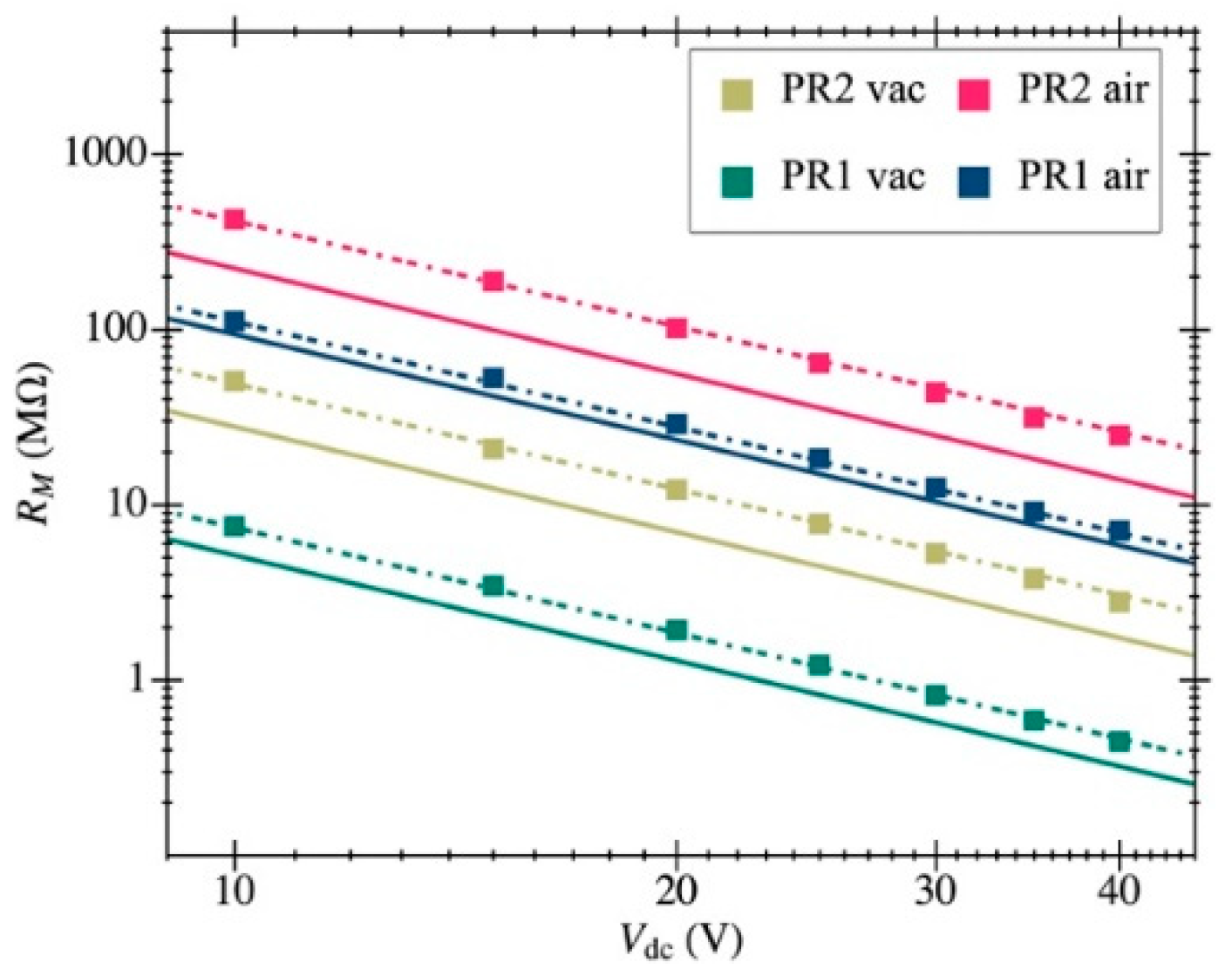

5.2. Plate Resonator 1 and Plate Resonator 2

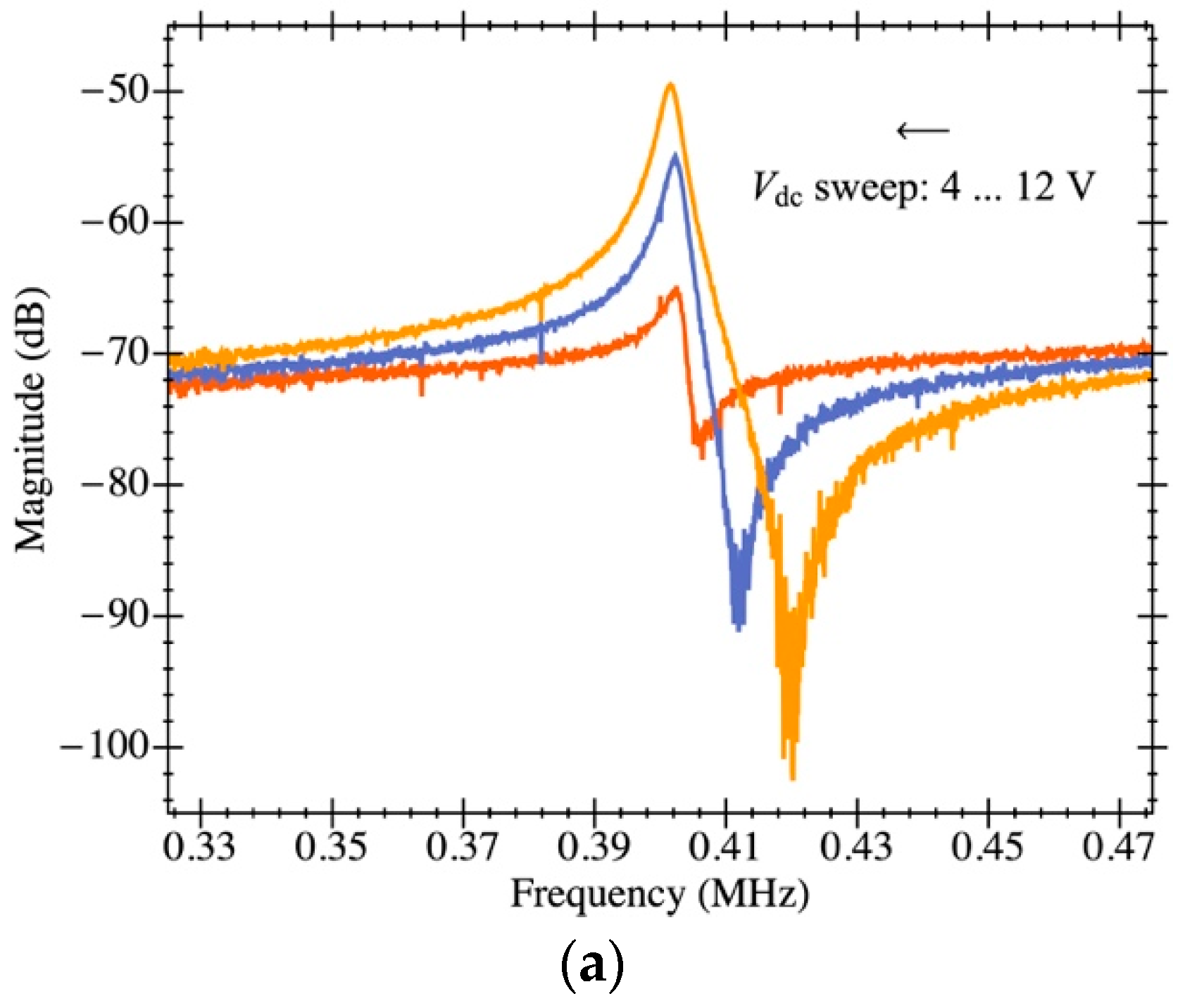

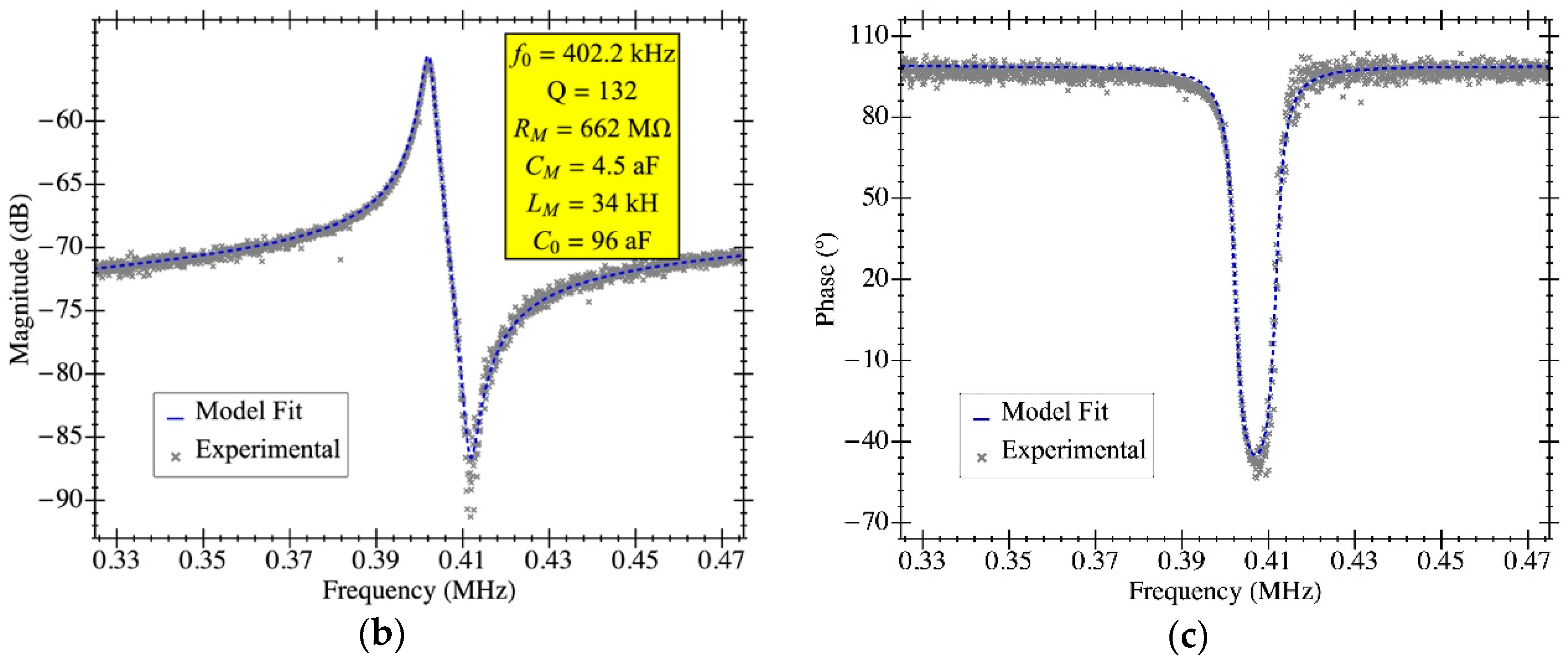

5.3. Plate Resonator 3

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Nguyen, C.T.C. Integrated micromechanical radio front-ends. In Proceedings of the International Symposium on VLSI Technology, Systems, and Applications (VLSA-TSA) 2008, Hsinchu, Taiwan, 21–23 April 2008; pp. 3–4. [Google Scholar]

- Nguyen, C.T.C.; Howe, R.T. CMOS micromechanical resonator oscillator. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 5–8 December 1993; pp. 199–202. [Google Scholar]

- Van Beek, J.T.M.; Puers, R. A review of MEMS oscillators for frequency reference and timing applications. J. Micromech. Microeng. 2012, 22, 013001. [Google Scholar] [CrossRef]

- Pachkawade, V.; Li, M.H.; Li, C.S.; Li, S.S. A CMOS-MEMS resonator integrated system for oscillator application. IEEE Sens. J. 2013, 13, 2882–2889. [Google Scholar] [CrossRef]

- Nguyen, C.T.C. MEMS technology for timing and frequency control. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2007, 54, 251–270. [Google Scholar] [CrossRef] [PubMed]

- Verd, J.; Uranga, A.; Abadal, G.; Teva, J.L.; Torres, F.; López, J.; Pérez-Murano, F.; Esteve, J.; Barniol, N. Monolithic CMOS MEMS oscillator circuit for sensing in the attogram range. IEEE Electron Device Lett. 2008, 29, 146–148. [Google Scholar] [CrossRef]

- Lo, C.C.; Chen, F.; Fedder, G.K. Integrated HF CMOS-MEMS square-frame resonators with on-chip electronics and electrothermal narrow gap mechanism. In Proceedings of the 13th International Conference on Solid-State Sensors, Actuators and Microsystems, 2005 Digest of Technical Papers TRANSDUCERS ’05, Seoul, Korea, 5–9 June 2005; pp. 2074–2077. [Google Scholar]

- Huang, W.L.; Ren, Z.; Lin, Y.W.; Chen, H.Y.; Lahann, J.; Nguyen, C.T.C. Fully monolithic CMOS nickel micromechanical resonator oscillator. In Proceedings of the 2008 IEEE 21st International Conference on Micro Electro Mechanical Systems (MEMS), Wuhan, China, 13–17 January 2008; pp. 10–13. [Google Scholar]

- Brand, O. Microsensor integration into Systems-on-Chip. Proc. IEEE 2006, 94, 1160–1176. [Google Scholar] [CrossRef]

- Uranga, A.; Verd, J.; Barniol, N. CMOS–MEMS resonators: From devices to applications. Microelectron. Eng. 2015, 132, 58–73. [Google Scholar] [CrossRef]

- Chen, W.C.; Fang, W.; Li, S.S. A generalized CMOS-MEMS platform for micromechanical resonators monolithically integrated with circuits. J. Micromech. Microeng. 2011, 21, 065012. [Google Scholar] [CrossRef]

- Fedder, G.K.; Howe, R.T.; Liu, T.J.K.; Quévy, E.P. Technologies for cofabricating MEMS and electronics. Proc. IEEE 2008, 96, 306–322. [Google Scholar] [CrossRef]

- Xie, H.; Erdmann, L.; Zhu, X.; Gabriel, K.J.; Fedder, G.K. Post-CMOS processing for high-aspect-ratio integrated silicon microstructures. J. Microelectromech. Syst. 2002, 11, 93–101. [Google Scholar]

- Seth, S.; Wang, S.; Kenny, T.; Murmann, B. A -131-dBc/Hz, 20-MHz MEMS oscillator with a 6.9-mW, 69-kΩ, gain-tunable CMOS TIA. In Proceedings of the ESSCIRC (ESSCIRC) 2012, Bordeaux, France, 17–21 September 2012; pp. 249–252. [Google Scholar]

- Verd, J.; Uranga, A.; Abadal, G.; Teva, J.; Pérez-Murano, F.; Barniol, N. High-sensitivity capacitive sensing interfacing circuit for monolithic CMOS M/NEMS resonators. Electron. Lett. 2007, 34, 1274. [Google Scholar] [CrossRef]

- Razavi, B. A 622 Mb/s 4.5 pA/√Hz CMOS transimpedance amplifier [for optical receiver front-end]. In Proceedings of the 2000 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 9 February 2000; pp. 162–163. [Google Scholar]

- Salvia, J.; Lajevardi, P.; Hekmat, M.; Murmann, B. A 56 MΩ CMOS TIA for MEMS applications. In Proceedings of the 2009 IEEE Custom Integrated Circuits Conference, Rome, Italy, 13–16 September 2009; pp. 199–202. [Google Scholar]

- Lee, S.; Demirci, M.U.; Nguyen, C.T.C. A 10-MHz Micromechanical Resonator Pierce Reference Oscillator for Communications. In Proceedings of the 11th International Conference on Solid-State Sensors, Actuators and Microsystems (TRANSDUCERS & EUROSENSORS XV) 2001, Berlin, Germany, 10–14 June 2001; pp. 1066–1069. [Google Scholar]

- Sobreviela, G.; Uranga, A.; Barniol, N. Tunable transimpedance sustaining-amplifier for high impedance CMOS-MEMS resonators. In Proceedings of the 10th Conference on PhD Research in Microelectronics and Electronics (PRIME) 2014, Grenoble, France, 30 June–3 July 2014; pp. 1–4. [Google Scholar]

- Verd, J.; Uranga, A.; Segura, J.; Barniol, N. A 3V CMOS-MEMS oscillator in 0.35 μm CMOS technology. In Proceedings of the 17th International Conference on Solid-State Sensors, Actuators and Microsystems (TRANSDUCERS & EUROSENSORS XXVII) 2013, Barcelona, Spain, 16–20 June 2013; pp. 806–809. [Google Scholar]

- Riverola, M.; Sobreviela, G.; Torres, F.; Uranga, A.; Barniol, N. Single-resonator dual-frequency BEOL-embedded CMOS-MEMS oscillator with low-power and ultra-compact TIA core. IEEE Electron Device Lett. 2017, 38, 273–276. [Google Scholar] [CrossRef]

- Roessig, T.A.; Howe, R.T.; Pisano, A.P.; Smith, J.H. Surface-micromachined 1 MHz oscillator with low-noise Pierce configuration. In Proceedings of the 1998 Solid State Sensor and Actuator Workshop, Hilton Head, SC, USA, 1 June 1998. [Google Scholar]

- Naing, T.L.; Rocheleau, T.O.; Alon, E.; Nguyen, C.T.C. Low-power MEMS-based Pierce oscillator using a 61-MHz capacitive-gap disk resonator. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2020, 67, 1377–1391. [Google Scholar] [CrossRef] [PubMed]

- Li, M.H.; Li, C.S.; Hou, L.J.; Liu, Y.C.; Li, S.S. A 1.57 mW 99 dB CMOS transimpedance amplifier for VHF micromechanical reference oscillators. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS) 2012, Seoul, Korea, 20–23 May 2012; pp. 209–212. [Google Scholar]

- Chen, T.T.; Huang, J.C.; Peng, Y.C.; Chu, C.H.; Lin, C.H.; Cheng, C.W.; Li, C.-S.; Li, S.-S. A 17.6-MHz 2.5V ultra-low polarization voltage MEMS oscillator using an innovative high gain-bandwidth fully differential trans-impedance voltage amplifier. In Proceedings of the IEEE 26th International Conference on Micro Electro Mechanical Systems (MEMS) 2013, Taipei, Taiwan, 20–24 January 2013; pp. 741–744. [Google Scholar]

- Li, M.H.; Chen, C.Y.; Liu, C.Y.; Li, S.S. A sub-150-μW BEOL-embedded CMOS-MEMS oscillator with a 138-dB ultra-low-noise TIA. IEEE Electron Device Lett. 2016, 37, 648–651. [Google Scholar] [CrossRef]

- Bouchami, A.; Elsayed, M.Y.; Nabki, F. A Sub-mW 18-MHz MEMS Oscillator Based on a 98-dBΩ Adjustable Bandwidth Transimpedance Amplifier and a Lamé-Mode Resonator. Sensors 2019, 19, 2680. [Google Scholar] [CrossRef] [PubMed]

- Senturia, S.D. Microsystem Design; Springer: New York, NY, USA, 2001. [Google Scholar]

- Verd, J.; Uranga, A.; Teva, J.; López, J.; Torres, F.; Esteve, J.; Abadal, G.; Pérez-Murano, F.; Barniol, N. Integrated CMOS MEMS with on-chip readout electronics for high-frequency applications. IEEE Electron Device Lett. 2006, 27, 495–597. [Google Scholar] [CrossRef]

- Fang, W.; Li, S.S.; Cheng, C.L.; Chang, C.I.; Chen, W.C.; Liu, Y.C.; Tsai, M.-H.; Sun, C. CMOS MEMS: A key technology towards the “More than Moore” era. In Proceedings of the 2013 Transducers & Eurosensors XXVII: The 17th International Conference on Solid-State Sensors, Actuators and Microsystems (TRANSDUCERS & EUROSENSORS XXVII), Barcelona, Spain, 16–20 June 2013; pp. 2513–2518. [Google Scholar]

- Perelló-Roig, R.; Verd, J.; Barceló, J.; Bota, S.; Segura, J. A 0.35-μm CMOS-MEMS oscillator for high-resolution distributed mass detection. Micromachines 2018, 9, 484. [Google Scholar] [CrossRef] [PubMed]

- Vidal-Álvarez, G.; Marigó, E.; Torres, F.; Barniol, N. Fabrication and measurement of a suspended nanochannel microbridge resonator monolithically integrated with CMOS readout circuitry. Micromachines 2016, 7, 40. [Google Scholar] [CrossRef] [PubMed]

- Liu, Y.C.; Tsai, M.H.; Chen, W.C.; Li, M.H.; Li, S.S.; Fang, W. Temperature-compensated CMOS-MEMS oxide resonators. J. Microelectromech. Syst. 2013, 22, 1054–1065. [Google Scholar] [CrossRef]

- Riverola, M.; Vidal-Álvarez, G.; Torres, F.; Barniol, N. CMOS-NEM relay based on tungsten VIA layer. In Proceedings of the IEEE Sensors 2014, Valencia, Spain, 2–5 November 2014; pp. 162–165. [Google Scholar]

- Michalik, P.; Fernández, D.; Wietstruck, M.; Kaynak, M.; Madrenas, J. Experiments on MEMS integration in 0.25 µm CMOS process. Sensors 2018, 18, 2111. [Google Scholar] [CrossRef] [PubMed]

- Perelló-Roig, R.; Verd, J.; Bota, S.; Segura, J. Frequency Fluctuations in CMOS-MEMS Oscillators: Towards the Thermomechanical Limit. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–5. [Google Scholar]

- Melero, A.; Verd, J.; Uranga, A.; Segura, J.; Barniol, N. A 24-MHz differential oscillator circuit for 5-MΩ CMOS-MEMS resonator. In Proceedings of the XXI Conference on Design of Circuits and Integrated Systems (DCIS) 2011, Albufeira, Portugal, 16–18 November 2011. [Google Scholar]

| TIA | [24] | [14] | [25] | [17] | [26] | [27] | This Work |

|---|---|---|---|---|---|---|---|

| Bandwidth | 280 MHz | 20 MHz | 60 MHz | 1.8 MHz | 1.2 MHz | 90 MHz | 50 MHz |

| Gain | 25.0 kΩ–89.0 kΩ | 12.0 kΩ–69.0 kΩ | 316 kΩ | 56.0 MΩ | 7.94 MΩ | 12.5 kΩ–794 kΩ | 330 kΩ–1.17 MΩ |

| Output Voltage noise | - | - | 790 µV/Hz1/2 | 3.64 µV/Hz1/2 | 199 nV/Hz1/2 | 3.18 µV/Hz1/2 | 225 nV/Hz1/2 |

| Input-Referred Current Noise | - | - | 192 fA/Hz1/2 | ||||

| CMOS Technology | 0.18 µm | 0.35 µm | 0.18 µm | 0.18 µm | 0.35 µm | 65 nm | 0.35 µm |

| FoM | - | - | 4.04·1014 | 7.28·1021 | 6.65·1022 | 1.66·1020 | 3.04·1023 |

| Power Consumption | 1.57 mW | 6.90 mW | 5.90 mW | 436 µW | 150 µW | 900 µW | 930 µW |

| Resonator | f0 (MHz) | Q | RM (MΩ) | CM (aF) | LM (H) | C0 (aF) |

|---|---|---|---|---|---|---|

| PR1 (air) | 1.152 | 110 | 18 † | 72 † | 280 † | 210 |

| PR1 (vac) | 1.147 | 2100 | 1.2 † | 56 † | 360 † | 210 |

| PR2 (air) | 3.789 | 210 | 63 † | 3.4 † | 530 † | 890 |

| PR2 (vac) | 3.767 | 1600 | 7.7 † | 3.3 † | 520 † | 890 |

| PR3 (air) | 0.402 | 132 | 662 § | 4.5 § | 34,000 § | 96 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Perelló-Roig, R.; Verd, J.; Bota, S.; Segura, J. A Tunable-Gain Transimpedance Amplifier for CMOS-MEMS Resonators Characterization. Micromachines 2021, 12, 82. https://doi.org/10.3390/mi12010082

Perelló-Roig R, Verd J, Bota S, Segura J. A Tunable-Gain Transimpedance Amplifier for CMOS-MEMS Resonators Characterization. Micromachines. 2021; 12(1):82. https://doi.org/10.3390/mi12010082

Chicago/Turabian StylePerelló-Roig, Rafel, Jaume Verd, Sebastià Bota, and Jaume Segura. 2021. "A Tunable-Gain Transimpedance Amplifier for CMOS-MEMS Resonators Characterization" Micromachines 12, no. 1: 82. https://doi.org/10.3390/mi12010082

APA StylePerelló-Roig, R., Verd, J., Bota, S., & Segura, J. (2021). A Tunable-Gain Transimpedance Amplifier for CMOS-MEMS Resonators Characterization. Micromachines, 12(1), 82. https://doi.org/10.3390/mi12010082