A Simulation Study of a Gate-All-Around Nanowire Transistor with a Core–Insulator

Abstract

1. Introduction

2. Device Structure and Experiment Methodology

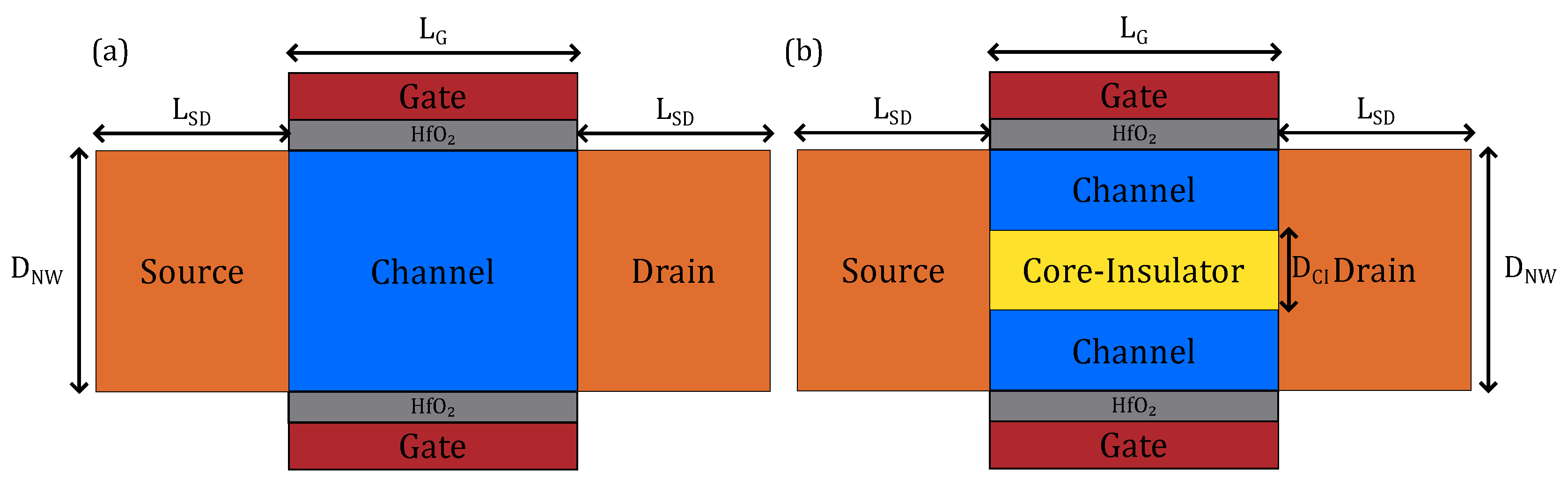

2.1. Descriptions of CIGAA Structure

2.2. Simulation Physical Models

2.3. Structure Parameters Used for Simulation

2.4. Considerations of Workfunction

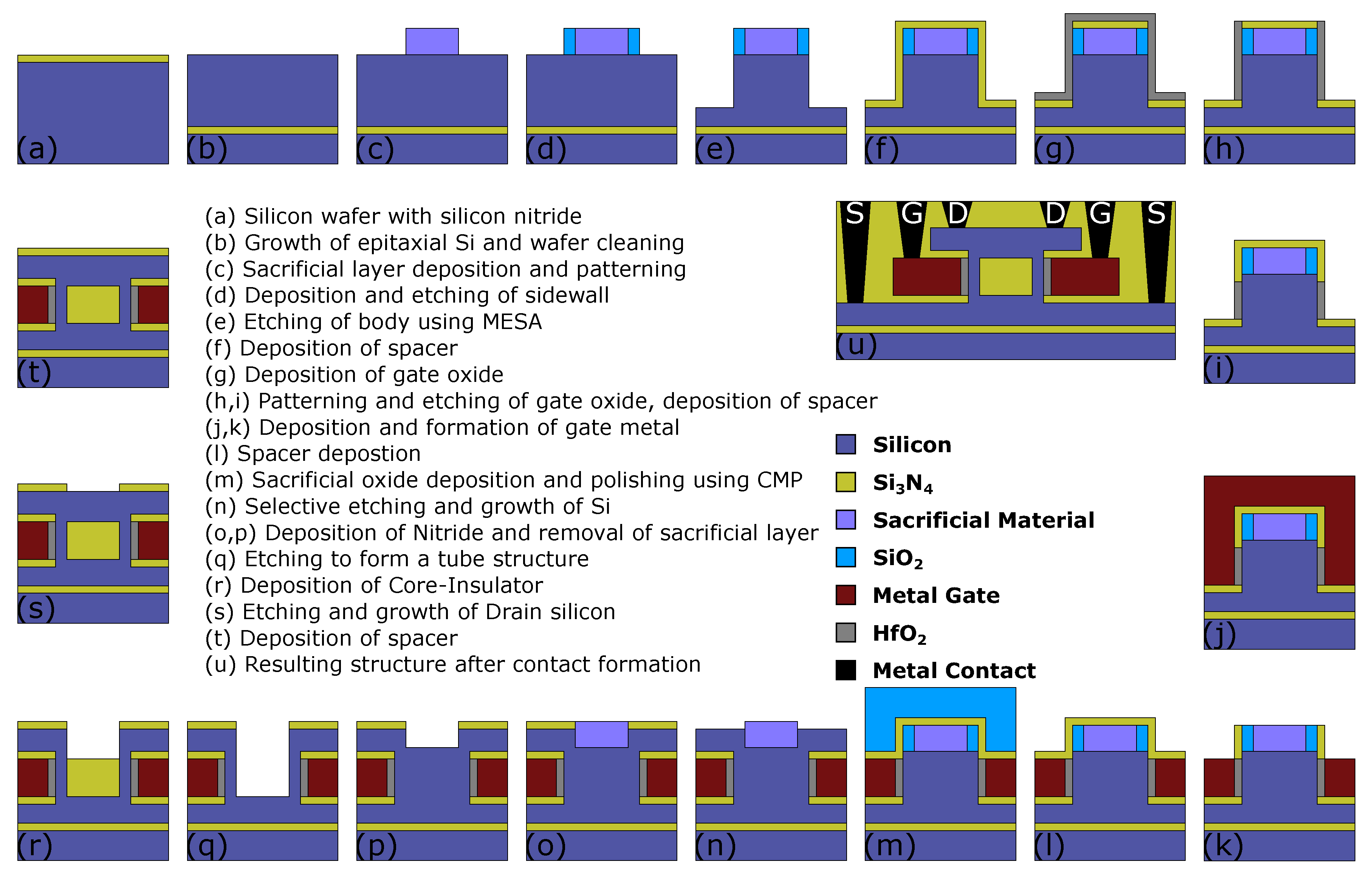

2.5. Suggested Fabrication Process Flow for CIGAA

3. Results and Discussions

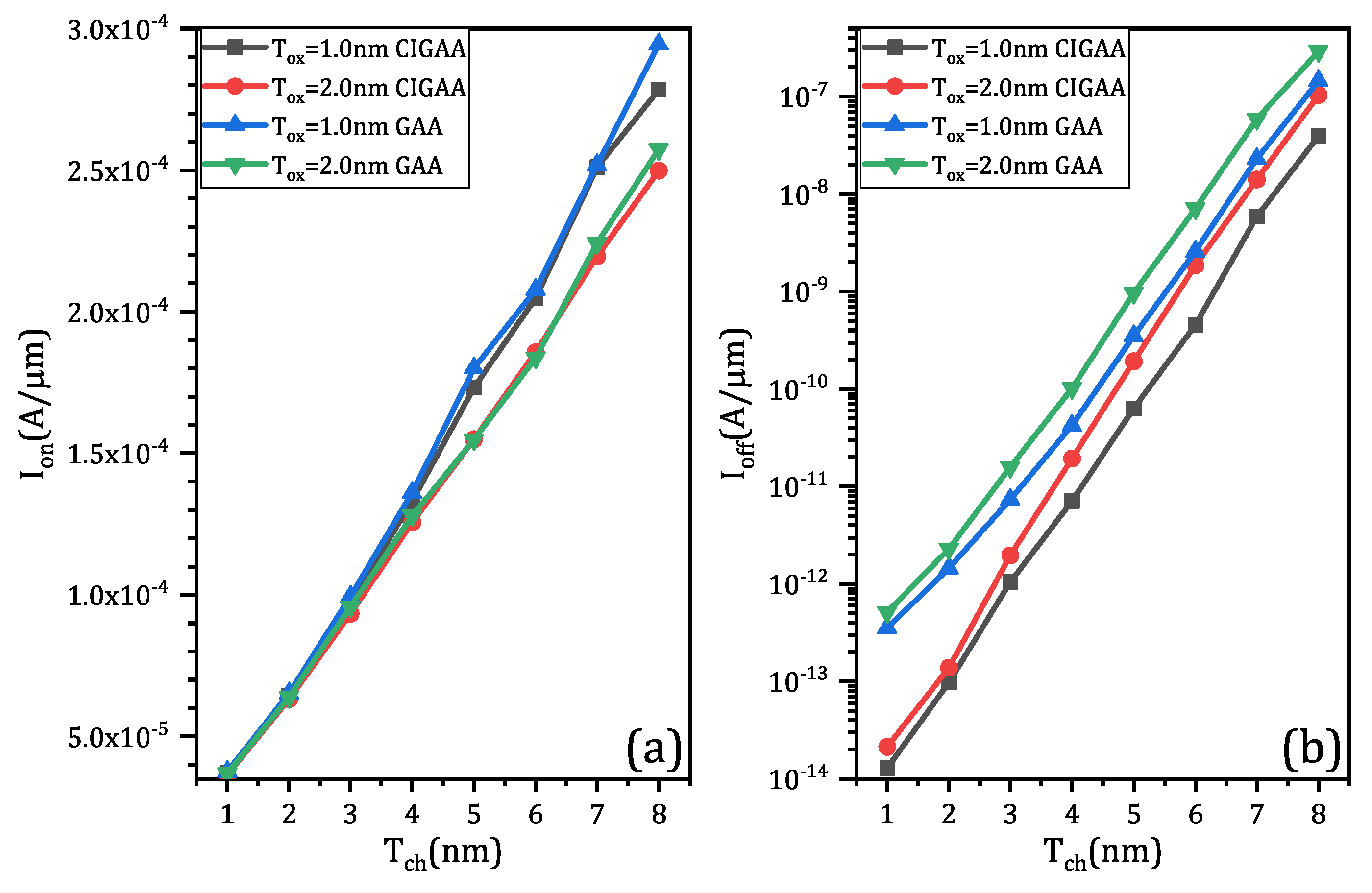

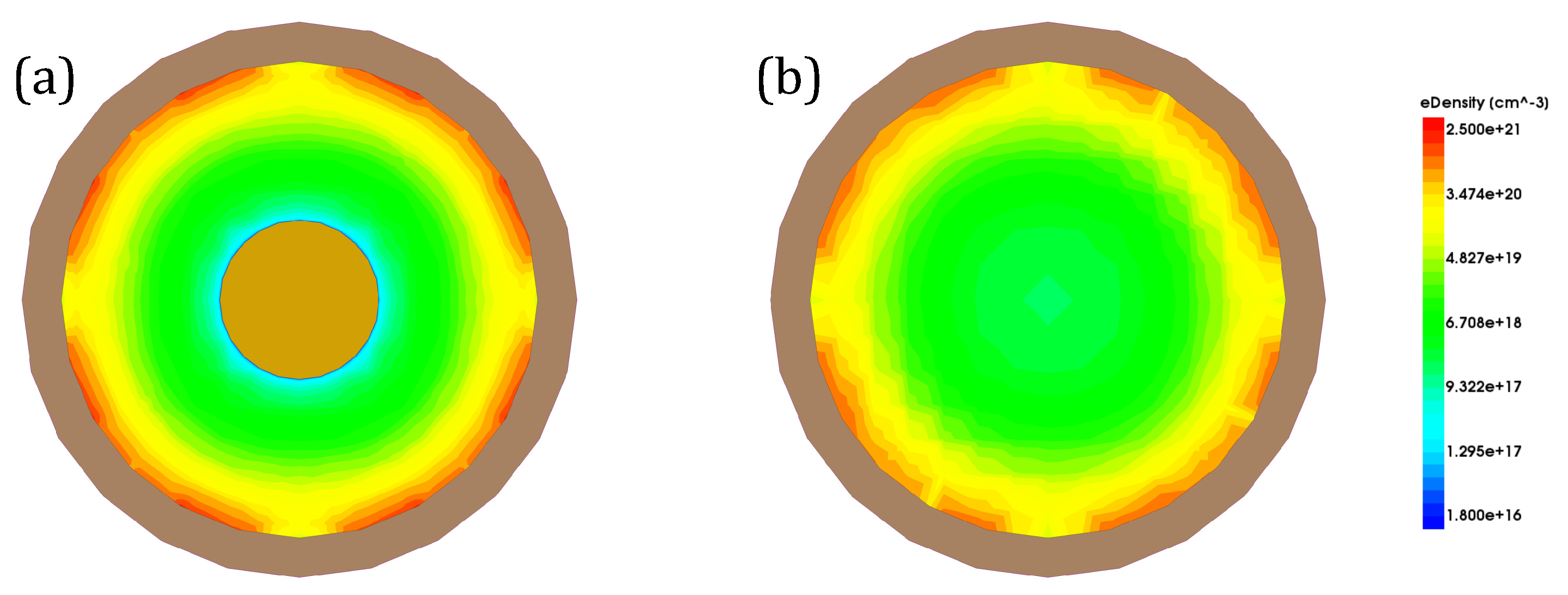

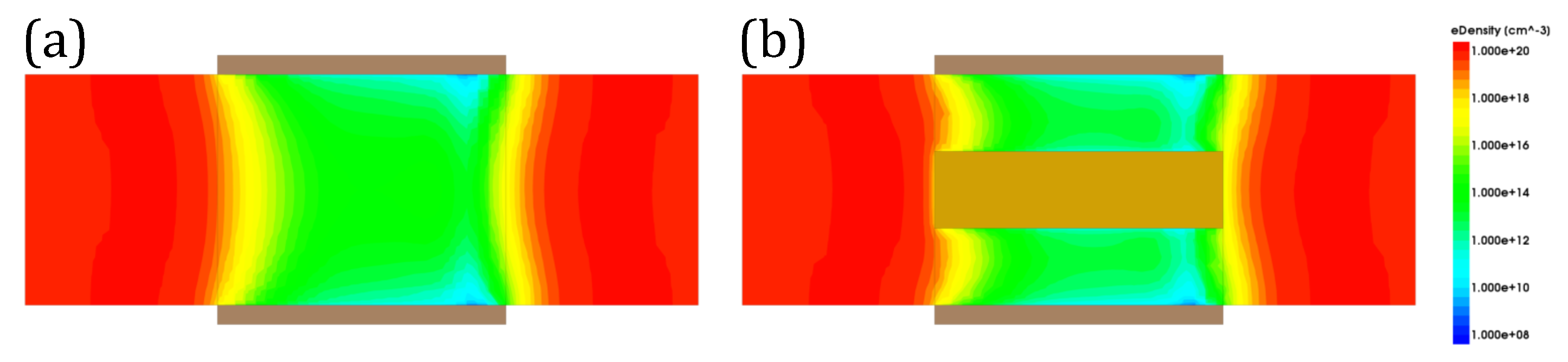

3.1. Basic Characteristics of CIGAA and GAA

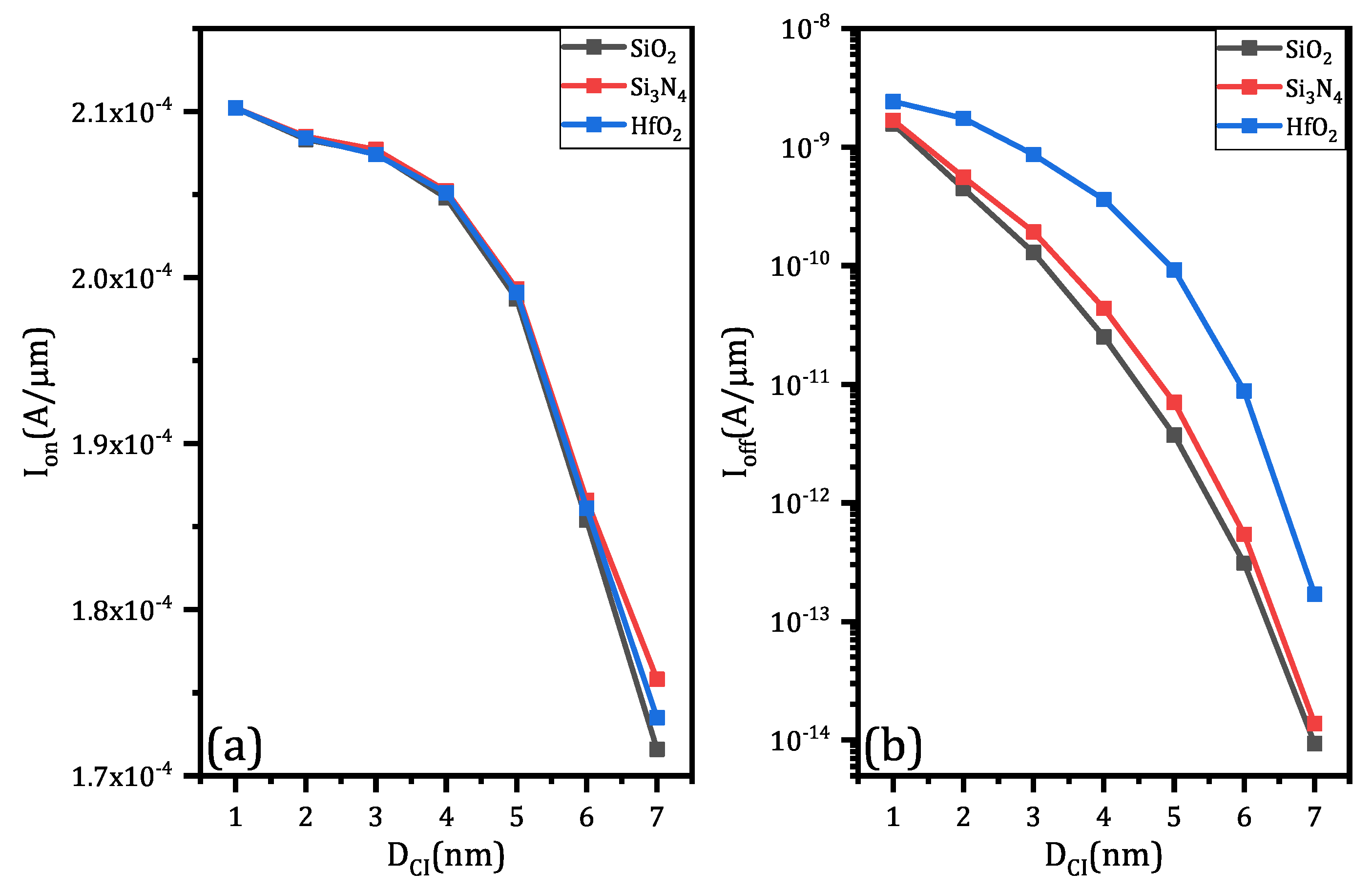

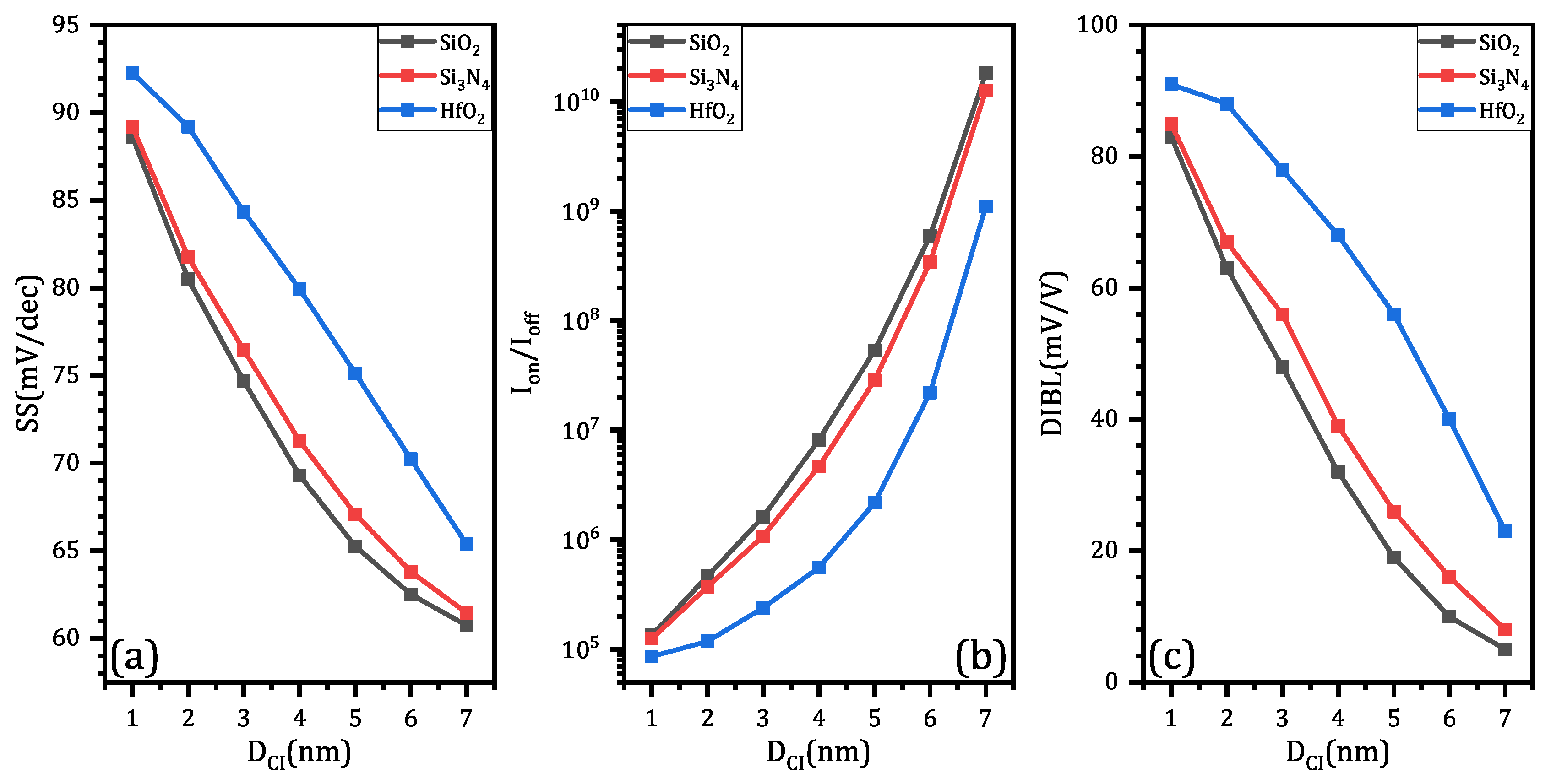

3.2. Impact of Core–Insulator Diameter and Material on Device Performance

3.3. Impact of Core–Insulator Length on Device Performance

3.4. Parasitic Capacitance of CIGAA and GAA

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Abbreviations

| BOX | Buried oxide layer |

| CIGAA | Core-Insulator Gate-All-Around |

| CMOS | Complementary metal oxide semiconductor |

| CMP | Chemical mechanical polishing |

| EBL | Electron beam lithography |

| FET | Field effect transistor |

| IMOS | Impact Ionization MOS |

| ITRS | International Technology Roadmap for Semiconductors |

| GAA | Gate-All-Around |

| LPCVD | Low-pressure chemical vapor deposition |

| MOS | Metal oxide semiconductor |

| MOSFET | Metal oxide semiconductor field effect transistor |

| SOI | Silicon on insulator |

| TCAD | Technology computer aided design |

| TFET | Tunnel field effect transistor |

References

- Carballo, J.A.; Chan, W.T.; Gargini, P.A.; Kahng, A.B.; Nath, S. Itrs 2.0: Toward a re-framing of the semiconductor technology roadmap. In Proceedings of the 2014 IEEE 32nd International Conference on Computer Design (ICCD), Seoul, Korea, 19–22 October 2014; pp. 139–146. [Google Scholar]

- Bruel, M. Silicon on insulator material technology. Electron. Lett. 1995, 31, 1201–1202. [Google Scholar] [CrossRef]

- Orouji, A.A.; Moghadam, H.A.; Dideban, A. Double window partial soi-ldmosfet: A novel device for breakdown voltage improvement. Phys. E Low-Dimens. Syst. Nanostruct. 2010, 43, 498–502. [Google Scholar] [CrossRef]

- Zhang, B.; Li, Z.; Hu, S.; Luo, X. Field enhancement for dielectric layer of high-voltage devices on silicon on insulator. IEEE Trans. Electron Devices 2009, 56, 2327–2334. [Google Scholar] [CrossRef]

- Ramaswamy, S.; Kumar, M.J. Junctionless impact ionization mos: Proposal and investigation. IEEE Trans. Electron Devices 2014, 61, 4295–4298. [Google Scholar] [CrossRef]

- Lu, H.; Seabaugh, A. Tunnel field-effect transistors: State-of-the-art. IEEE J. Electron Devices Soc. 2014, 2, 44–49. [Google Scholar] [CrossRef]

- Gopalakrishnan, K.; Griffin, P.B.; Plummer, J.D. Impact ionization mos (i-mos)—Part I: Device and circuit simulations. IEEE Trans. Electron Devices 2004, 52, 69–76. [Google Scholar] [CrossRef]

- Toh, E.H.; Wang, G.H.; Chan, L.; Lo, G.Q.; Samudra, G.; Yeo, Y.C. Strain and materials engineering for the i-mos transistor with an elevated impact-ionization region. IEEE Trans. Electron Devices 2007, 54, 2778–2785. [Google Scholar] [CrossRef]

- Colinge, J.P.; Lee, C.W.; Afzalian, A.; Akhavan, N.D.; Yan, R.; Ferain, I.; Razavi, P.; O’neill, B.; Blake, A.; White, M.; et al. Nanowire transistors without junctions. Nat. Nanotechnol. 2010, 5, 225. [Google Scholar] [CrossRef] [PubMed]

- Koga, J.; Toriumi, A. Three-terminal silicon surface junction tunneling device for room temperature operation. IEEE Electron Device Lett. 1999, 20, 529–531. [Google Scholar] [CrossRef]

- Settino, F.; Lanuzza, M.; Strangio, S.; Crupi, F.; Palestri, P.; Esseni, D.; Selmi, L. Understanding the potential and limitations of tunnel fets for low-voltage analog/mixed-signal circuits. IEEE Trans. Electron Devices 2017, 64, 2736–2743. [Google Scholar] [CrossRef]

- Boucart, K.; Ionescu, A.M. Double-gate tunnel fet with high-K gate dielectric. IEEE Trans. Electron Devices 2007, 54, 1725–1733. [Google Scholar] [CrossRef]

- TCAD Sentaurus and N Version; Synopsys Inc.: Mountain View, CA, USA, 2017.

- Singh, N.; Agarwal, A.; Bera, L.K.; Liow, T.Y.; Yang, R.; Rustagi, S.C.; Tung, C.H.; Kumar, R.; Lo, G.Q.; Balasubramanian, N.; et al. High-performance fully depleted silicon nanowire (diameter/spl les/5 nm) gate-all-around cmos devices. IEEE Electron Device Lett. 2006, 27, 383–386. [Google Scholar] [CrossRef]

- Pezzimenti, F.; Bencherif, H.; Yousfi, A.; Dehimi, L. Current-voltage analytical model and multiobjective optimization of design of a short channel gate-all-around-junctionless mosfet. Solid-State Electron. 2019, 161, 107642. [Google Scholar] [CrossRef]

- Pezzimenti, F. Modeling of the steady state and switching characteristics of a normally off 4h-sic trench bipolar-mode fet. IEEE Trans. Electron Devices 2013, 60, 1404–1411. [Google Scholar] [CrossRef]

- Zhuge, J.; Tian, Y.; Wang, R.; Huang, R.; Wang, Y.; Chen, B.; Liu, J.; Zhang, X.; Wang, Y. High-performance si nanowire transistors on fully si bulk substrate from top-down approach: Simulation and fabrication. IEEE Trans. Nanotechnol. 2009, 9, 114–122. [Google Scholar] [CrossRef]

- Klaassen, D.B.M. A unified mobility model for device simulation—I. model equations and concentration dependence. Solid-State Electron. 1992, 35, 953–959. [Google Scholar] [CrossRef]

- Jaikumar, M.G.; Karmalkar, S. Calibration of mobility and interface trap parameters for high temperature tcad simulation of 4h-sic vdmosfets. In Materials Science Forum; Trans Tech Publication: Zürich, Switzerland, 2012; Volume 717, pp. 1101–1104. [Google Scholar]

- Singh, J.; Kumar, M.J. A planar junctionless fet using sic with reduced impact of interface traps: Proposal and analysis. IEEE Trans. Electron Devices 2017, 64, 4430–4434. [Google Scholar] [CrossRef]

- Lombardi, C.; Manzini, S.; Saporito, A.; Vanzi, M. A physically based mobility model for numerical simulation of nonplanar devices. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 1988, 7, 1164–1171. [Google Scholar] [CrossRef]

- Marchi, M.D.; Sacchetto, D.; Frache, S.; Zhang, J.; Gaillardon, P.; Leblebici, Y.; Micheli, G.D. Polarity control in double-gate, gate-all-around vertically stacked silicon nanowire fets. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012; pp. 4–8. [Google Scholar]

- Marchi, M.D.; Zhang, J.; Frache, S.; Sacchetto, D.; Gaillardon, P.; Leblebici, Y.; Micheli, G.D. Configurable logic gates using polarity-controlled silicon nanowire gate-all-around fets. IEEE Electron Device Lett. 2014, 35, 880–882. [Google Scholar] [CrossRef]

- Yang, J.; He, J.; Liu, F.; Zhang, L.; Liu, F.; Zhang, X.; Chan, M. A compact model of silicon-based nanowire mosfets for circuit simulation and design. IEEE Trans. Electron Devices 2008, 55, 2898–2906. [Google Scholar] [CrossRef]

- Brown, A.R.; Watling, J.R.; Roy, G.; Riddet, C.; Alexander, C.L.; Kovac, U.; Martinez, A.; Asenov, A. Use of density gradient quantum corrections in the simulation of statistical variability in mosfets. J. Comput. Electron. 2010, 9, 187–196. [Google Scholar] [CrossRef]

- Palankovski, V.; Kaiblinger-Grujin, G.; Selberherr, S. Study of dopant-dependent band gap narrowing in compound semiconductor devices. Mater. Sci. Eng. B 1999, 66, 46–49. [Google Scholar] [CrossRef]

- Fahad, H.M.; Hussain, M.M. High-performance silicon nanotube tunneling fet for ultralow-power logic applications. IEEE Trans. Electron Devices 2013, 60, 1034–1039. [Google Scholar] [CrossRef]

- Musalgaonkar, G.; Sahay, S.; Saxena, R.S.; Kumar, M.J. Nanotube tunneling fet with a core source for ultrasteep subthreshold swing: A simulation study. IEEE Trans. Electron Devices 2019, 66, 4425–4432. [Google Scholar] [CrossRef]

- Tekleab, D.; Tran, H.H.; Sleight, J.W.; Chidambarrao, D. Silicon Nanotube Mosfet. U.S. Patent 8,871,576, 28 October 2014. [Google Scholar]

- Ionescu, A.M.; Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 2011, 479, 329. [Google Scholar] [CrossRef]

| Variables | Values |

|---|---|

| Gate Length (L) | 15 nm |

| HfO2 Thickness | 1.0 nm/2.0 nm |

| Channel Thickness (D/2D/2) | 1.0 to 8.0 nm |

| Source/Drain Length (L) | 10 nm |

| Core–Insulator Diameter (D) | 2 nm to 14 nm |

| Source/Drain Doping | |

| Channel Doping | |

| Core–Insulator | Si3N4, SiO2, HfO2 |

| Channel Thickness (nm) | Core–Insulator Diameter (nm) |

|---|---|

| 1 | 7 |

| 2 | 6 |

| 3 | 5 |

| 4 | 4 |

| 5 | 3 |

| 6 | 2 |

| 7 | 1 |

| Lext (nm) | ΔIon (%) | ΔIoff (%) | ΔIon/Ioff (%) | ΔSS (%) | ΔDIBL (mV) |

|---|---|---|---|---|---|

| −2 | 0.3 | 0.5 | −0.5 | 0.7 | 1 |

| −1 | 0 | 0.8 | −0.8 | 0.4 | 1 |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | −0.5 | −0.7 | 0.6 | −0.5 | 0 |

| 2 | −1.1 | −0.4 | 0.9 | −0.7 | −1 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, Y.; Han, K.; Li, a.J. A Simulation Study of a Gate-All-Around Nanowire Transistor with a Core–Insulator. Micromachines 2020, 11, 223. https://doi.org/10.3390/mi11020223

Zhang Y, Han K, Li aJ. A Simulation Study of a Gate-All-Around Nanowire Transistor with a Core–Insulator. Micromachines. 2020; 11(2):223. https://doi.org/10.3390/mi11020223

Chicago/Turabian StyleZhang, Yannan, Ke Han, and and Jiawei Li. 2020. "A Simulation Study of a Gate-All-Around Nanowire Transistor with a Core–Insulator" Micromachines 11, no. 2: 223. https://doi.org/10.3390/mi11020223

APA StyleZhang, Y., Han, K., & Li, a. J. (2020). A Simulation Study of a Gate-All-Around Nanowire Transistor with a Core–Insulator. Micromachines, 11(2), 223. https://doi.org/10.3390/mi11020223