Research on the Protrusions Near Silicon-Glass Interface during Cavity Fabrication

Abstract

:1. Introduction

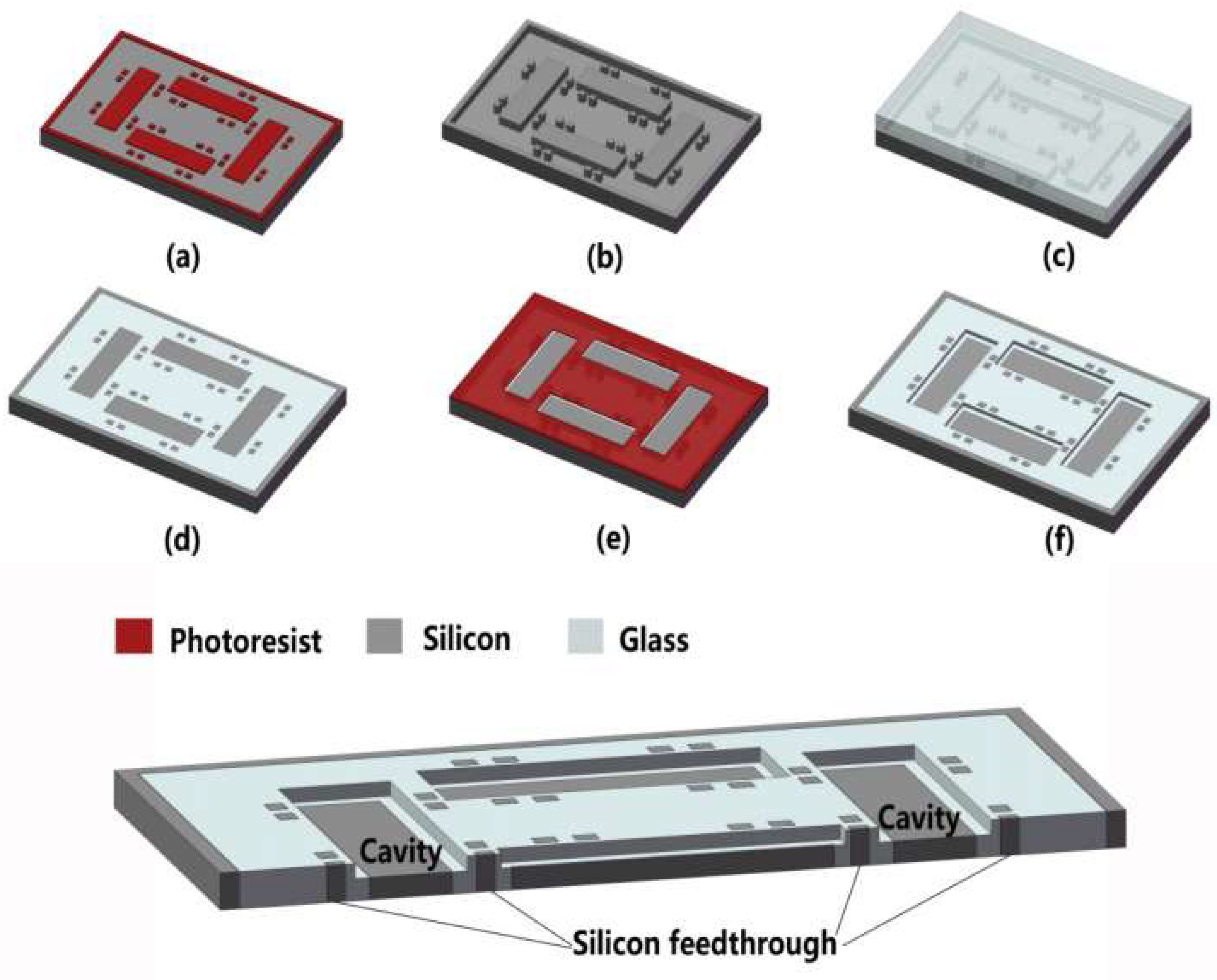

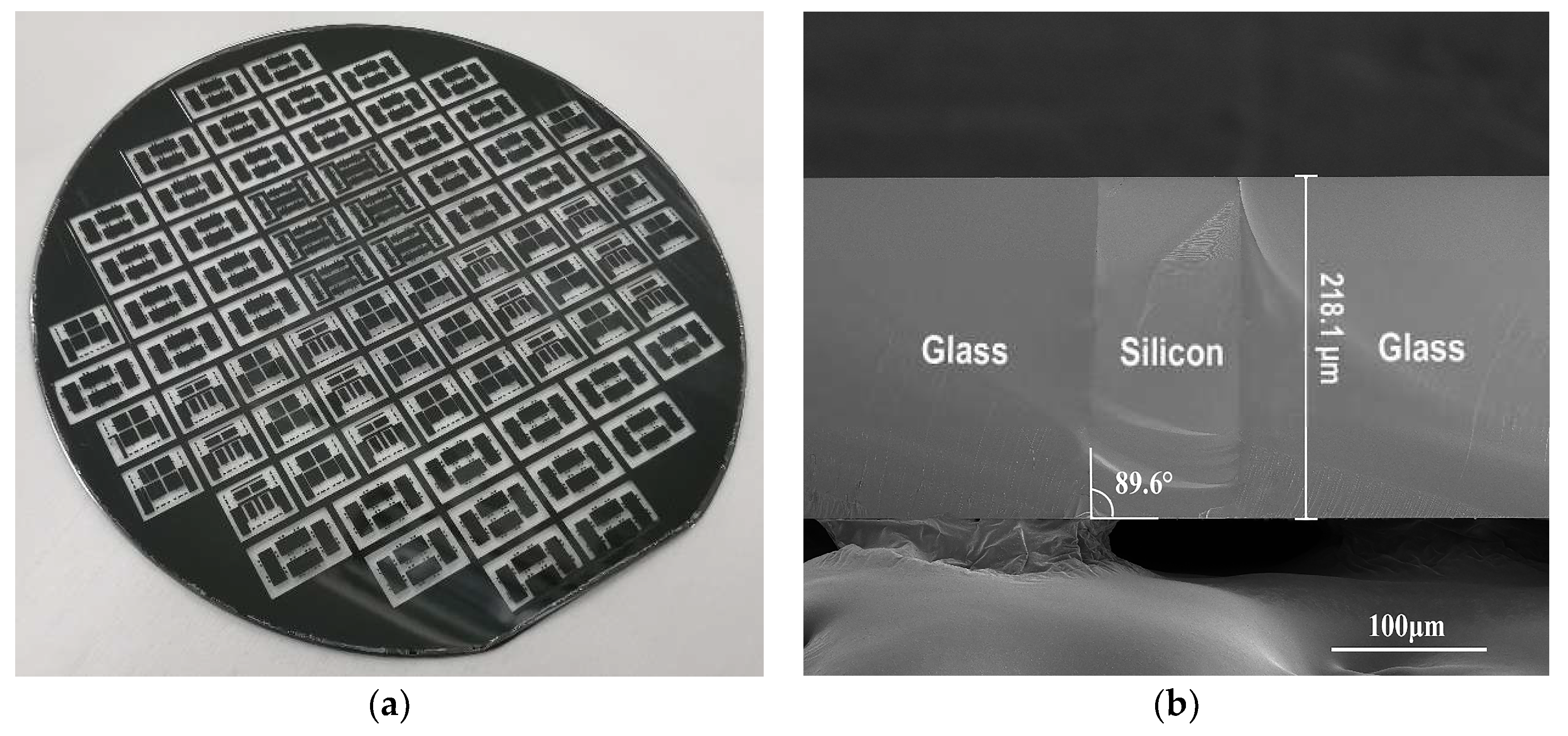

2. Experiment Details

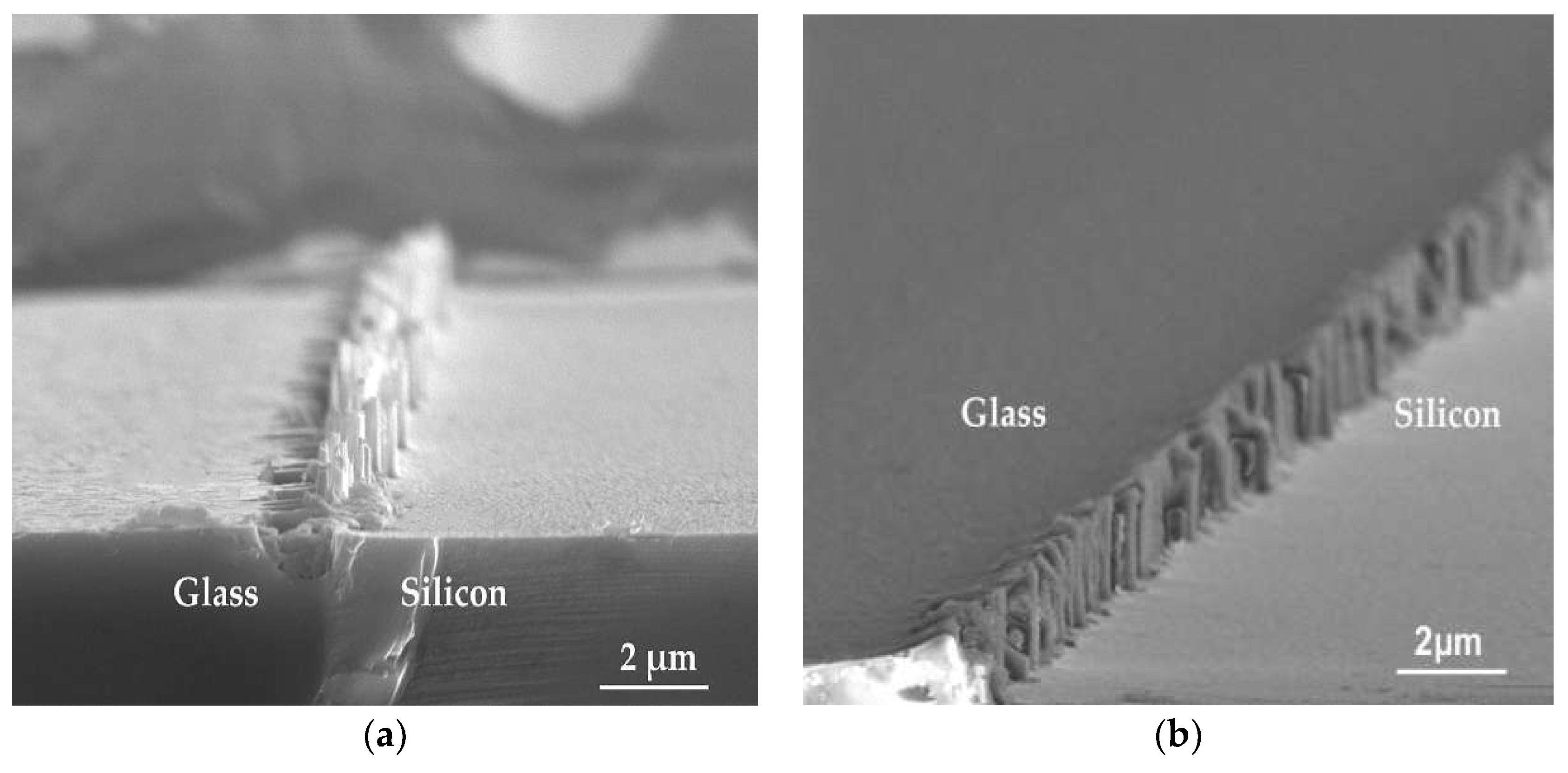

3. Results and Discussion

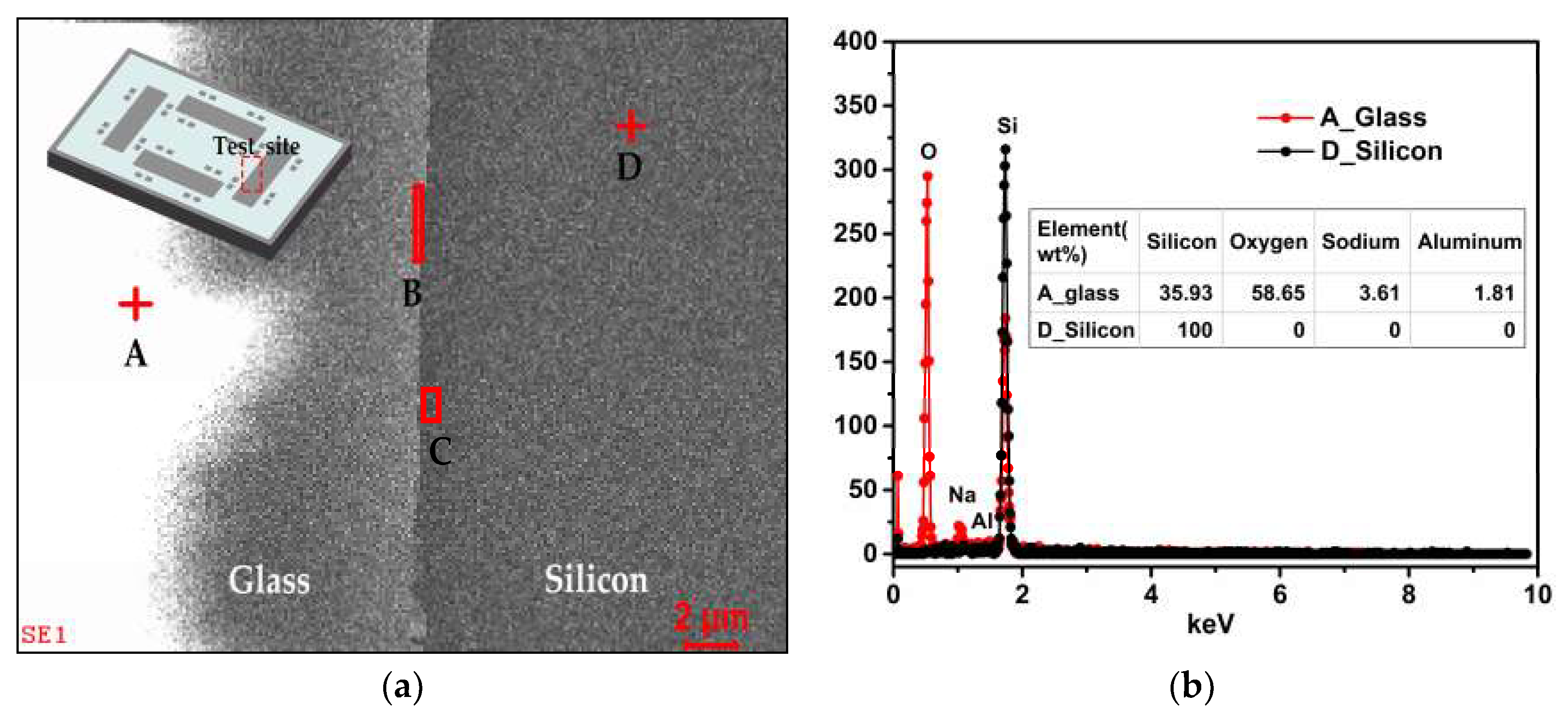

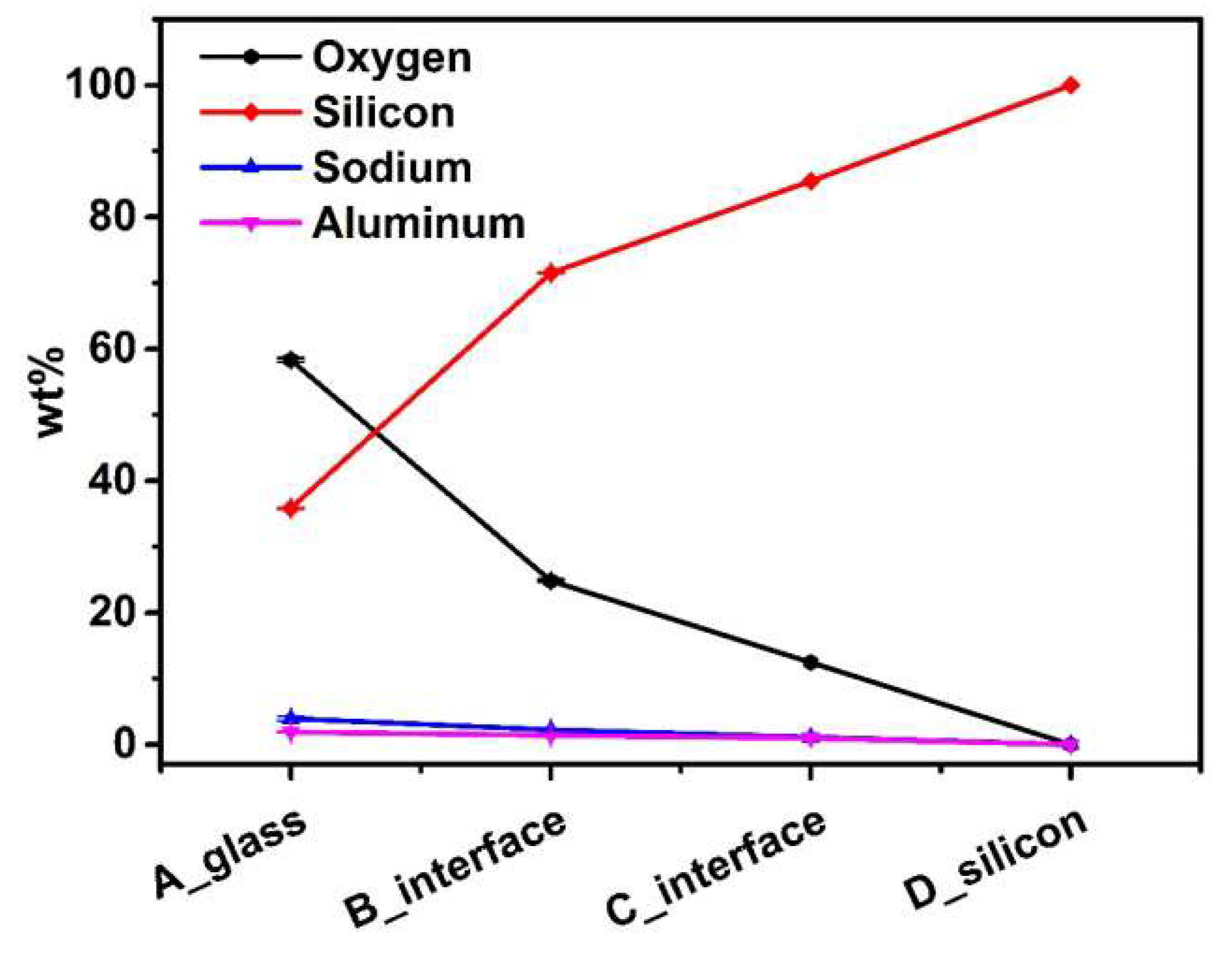

3.1. Chemical Composition

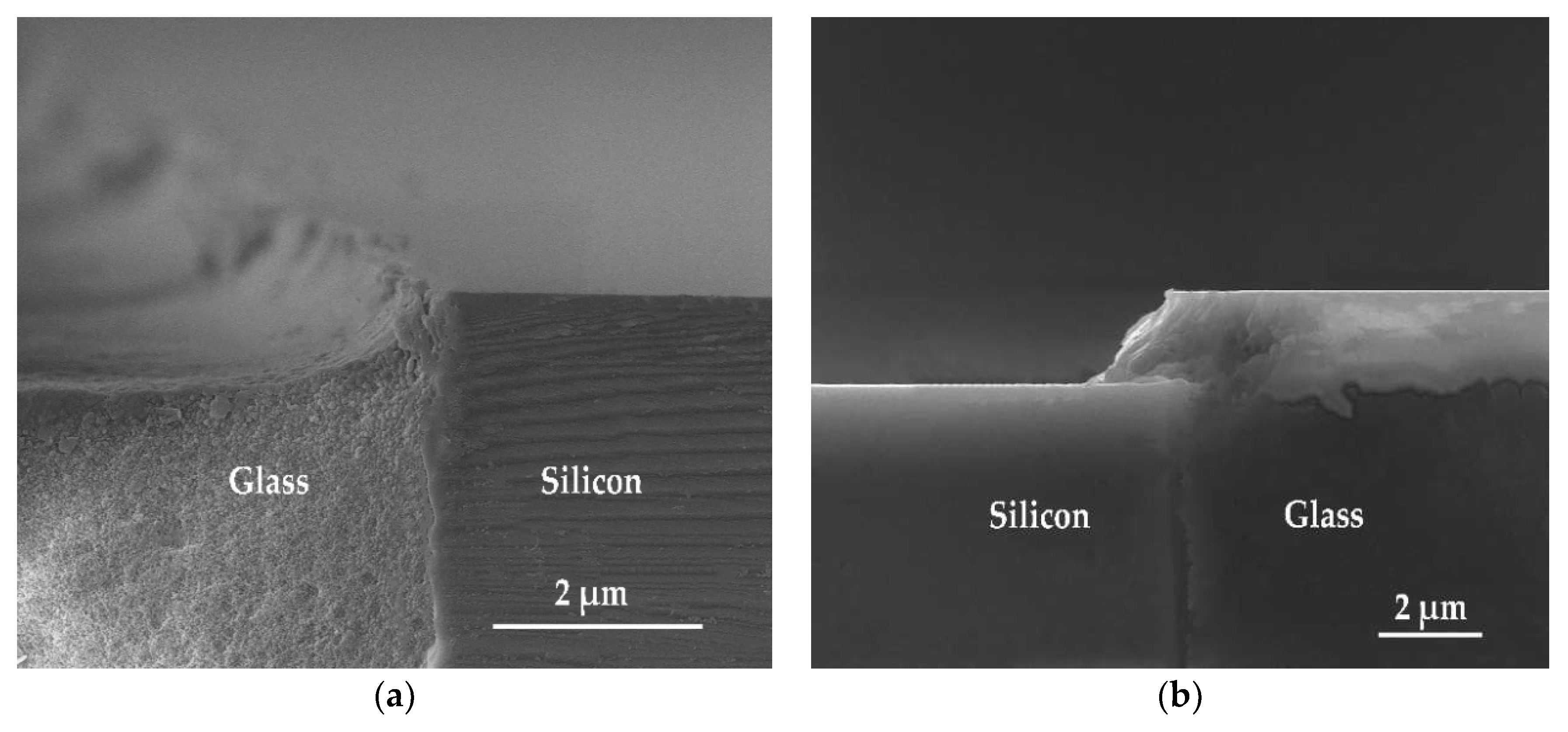

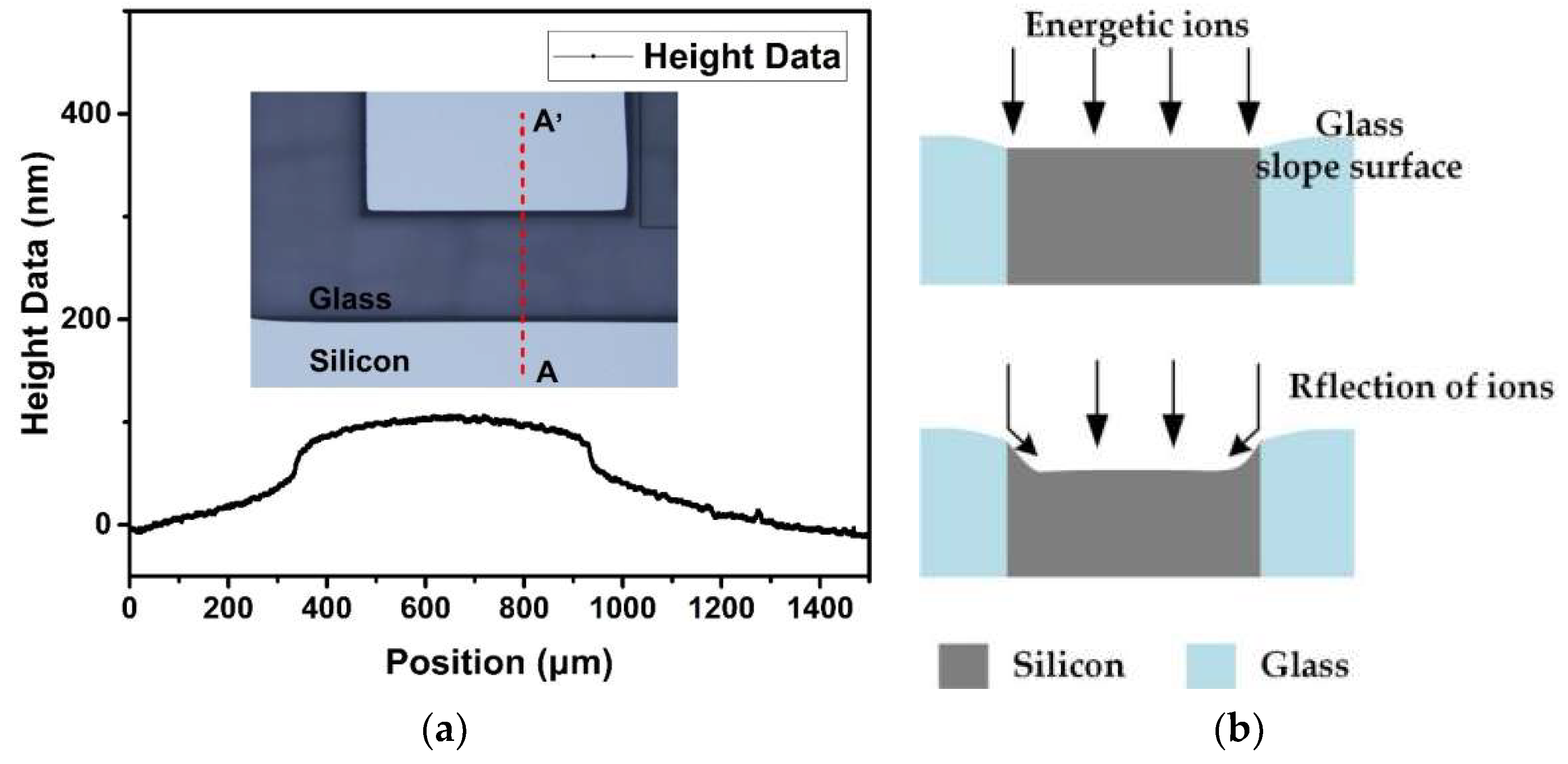

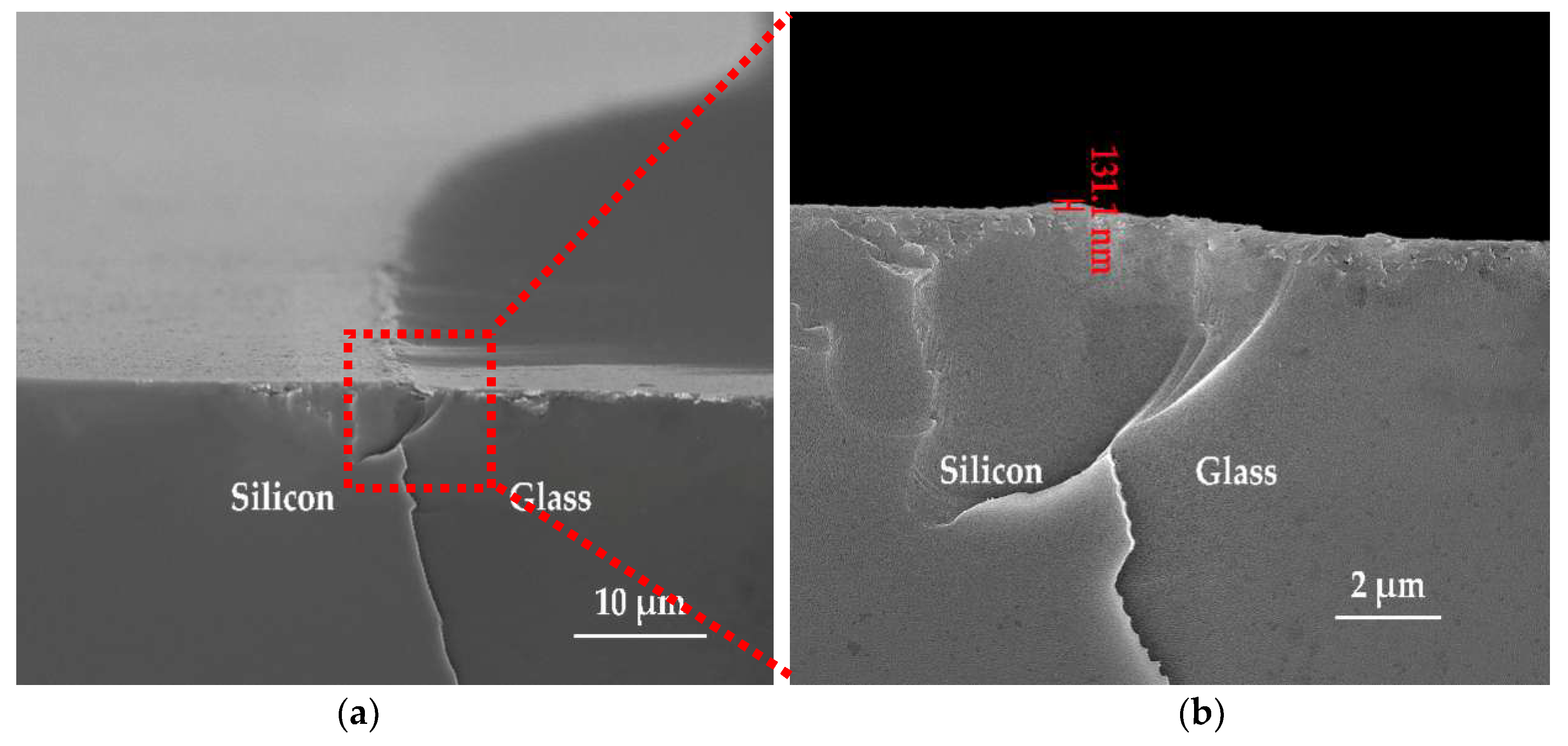

3.2. Etching Mechanisms

4. Optimized Fabrication Scheme

- (a)

- At first, the sample was immersed in the HF-based solution with added HCl for 5 s to remove the part of glass about 80 nm higher than silicon to avoid the effect of ion reflection on the glass slope. The oxide layer thermally grown on the silicon sidewalls was simultaneously exposed.

- (b)

- Then, the silicon was etched for 24 s to the depth of 1 μm by ICP dry etching technology. During etching, the plasma groups consisting of energetic ions accumulated at the interface to accelerate the etching of the oxide layer. Since plasma accumulation accelerated etching and the ion reflection at glass edges attenuated, much less material remained near the interface to form the protrusions.

- (c)

- Afterwards, without the shield effect of silicon at the interface, 1 μm glass was etched completely, which exposed the protrusions near the interface completely.

- (d)

- One micrometer of silicon was etched away again, as in step (b). During the silicon etching process, the protrusions that were completely exposed were etched more quickly than before in order to be minimized further.

- (e)

- Finally, the glass was also etched to same depth as silicon, as in step (c). By this time, a 2 μm-deep cavity with tiny protrusions was prepared. It should be mentioned that 2-min BHF wet etching could be adopted to further make the step between glass and silicon become smoother. Cavity with other depths could be fabricated by adjusting the number of the etching steps and the etching depth in each step in the optimized process flow in Figure 8.

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Najafi, K. Micropackaging technologies for integrated microsystems: Applications to MEMS and MOEMS. In Micromachining and Microfabrication Process Technology Viii; Yasaitis, J.A., PerezMaher, M.A., Karam, J.M., Eds.; International Society for Optics and Photonics: San Jose, CA, USA, 2003; Volume 4979, pp. 1–19. [Google Scholar]

- Esashi, M. Wafer level packaging of MEMS. J. Micromech. Microeng. 2008, 18, 073001. [Google Scholar] [CrossRef]

- Wang, Z.Y. 3-D Integration and Through-Silicon Vias in MEMS and Microsensors. J. Microelectromech. Syst. 2015, 24, 1211–1244. [Google Scholar] [CrossRef]

- Lee, S.W.; Lee, S.K.; Park, J.H. High-density through-wafer copper via array in insulating glass mold using reflow process. Jpn. J. Appl. Phys. 2015, 54, 047202. [Google Scholar] [CrossRef]

- Jin, J.Y.; Yoo, S.; Yoo, B.W.; Kim, Y.K. Characterisation of silicon through-vias for wafer-level interconnection with glass reflows. Electron. Lett. 2012, 48, 1354–1355. [Google Scholar] [CrossRef]

- Yoon, S.W.; Na, D.J.; Choi, W.K.; Kang, K.T.; Yong, C.B.; Kim, Y.C.; Marimuthu, P.C. 2.5 D/3D TSV processes development and assembly/packaging technology. In Proceedings of the 2011 IEEE 13th Electronics Packaging Technology Conference (EPTC), Singapore, 7–9 December 2011; pp. 336–340. [Google Scholar]

- Lee, J.-Y.; Lee, S.-W.; Lee, S.-K.; Park, J.-H. Through-glass copper via using the glass reflow and seedless electroplating processes for wafer-level RF MEMS packaging. J. Micromech. Microeng. 2013, 23, 085012. [Google Scholar] [CrossRef]

- Fernández-Bolaños, M.; Vitale, W.A.; López, M.M.; Ionescu, A.M.; Klumpp, A.; Merkel, R.; Weber, J.; Ramm, P. 3D TSV based high frequency components for RF IC and RF MEMS applications. In Proceedings of the 2016 IEEE International 3D Systems Integration Conference (3DIC), San Francisco, CA, USA, 8–11 November 2016; pp. 1–4. [Google Scholar]

- Benali, A.; Bouya, M.; Faqir, M.; El Amrani, A.; Ghogho, M.; Benabdellah, A. Through Glass Via Thermomechanical Analysis: Geometrical parameters effect on thermal stress. In Proceedings of the 2013 8th International Design and Test Symposium, Marrakesh, Morocco, 16–18 December 2013. [Google Scholar]

- Baum, M.; Hofmann, L.; Wiemer, M.; Schulz, S.; Gessner, T. Development and characterisation of 3D integration technologies for MEMS based on copper filled TSV’s and copper-to-copper metal thermo compression bonding. In Proceedings of the 2013 International Semiconductor Conference Dresden-Grenoble (ISCDG), Dresden, Germany, 26–27 September 2013; pp. 1–4. [Google Scholar]

- Töpper, M.; Ndip, I.; Erxleben, R.; Brusberg, L.; Nissen, N.; Schröder, H.; Yamamoto, H.; Todt, G.; Reichl, H. 3-D Thin film interposer based on TGV (Through Glass Vias): An alternative to Si-interposer. In Proceedings of the 2010 Proceedings 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 66–73. [Google Scholar]

- Haque, R.; Wise, K. An intraocular pressure sensor based on a glass reflow process. In Proceedings of the Solid-State Sensors, Actuators, and Microsystems Workshop, Hilton Head Island, South Carolina, 6–10 June 2010; pp. 49–52. [Google Scholar]

- Haque, R.U.; Wise, K.D. A Glass-in-Silicon Reflow Process for Three-Dimensional Microsystems. J. Microelectromech. Syst. 2013, 22, 1470–1477. [Google Scholar] [CrossRef]

- Lin, C.W.; Hsu, C.P.; Yang, H.A.; Wang, W.C.; Fang, W. Implementation of silicon-on-glass MEMS devices with embedded through-wafer silicon vias using the glass reflow process for wafer-level packaging and 3D chip integration. J. Micromech. Microeng. 2008, 18, 025018. [Google Scholar] [CrossRef]

- Haque, R.M.; Serrano, D.E.; Gao, X.; Keesara, V.; Ayazi, F.; Wise, K.D. Hermetic packaging of resonators with vertical feedthroughs using a glass-in-silicon reflow process. In Proceedings of the Solid-State Sensors, Actuators and Microsystems Conference, Beijing, China, 5–9 June 2011; pp. 2303–2306. [Google Scholar]

- Wenyin, L.; Xuezhong, W.; Dingbang, X.; Zhanqiang, H.; Zhihua, C.; Xinghua, W.; Jian, Z. Characterization of signal transfer performance of a through glass via (TGV) substrate with silicon vertical feedthroughs. Microelectron. Eng. 2016, 165, 52–56. [Google Scholar] [CrossRef]

- Zhao, J.C.; Yuan, Q.; Wang, F.X.; Kan, X.; Han, G.W.; Sun, L.; Yang, J.-L. Design and characterization of a 3D encapsulation with silicon vias for radio frequency micro-electromechanical system resonator. Chin. Phys. B 2017, 26, 060705. [Google Scholar] [CrossRef]

- Kuang, Y.; Xiao, D.; Zhou, J.; Li, W.; Hou, Z.; Cui, H.; Wu, X. Theoretical model and experiments of glass reflow process in TGV for 3D wafer-level packaging. In Proceedings of the 2018 IEEE International Symposium on Inertial Sensors and Systems (INERTIAL), Lake Como, Italy, 26–29 March 2018; pp. 1–4. [Google Scholar]

- Zhang, M.; Yang, J.; He, Y.; Yang, F.; Yang, F.; Han, G.; Si, C.; Ning, J. Research on a 3D Encapsulation Technique for Capacitive MEMS Sensors Based on Through Silicon Via. Sensors 2018, 19, 93. [Google Scholar] [CrossRef]

- Lee, S.H.; Cho, J.; Lee, S.W.; Zaman, M.F.; Ayazi, F.; Najafi, K. A low-power oven-controlled vacuum package technology for high-performance mems. In Proceedings of the IEEE 22nd International Conference on Micro Electro Mechanical Systems, Sorrento, Italy, 25–29 January 2009; pp. 753–756. [Google Scholar]

- Jin, J.Y.; Yoo, S.H.; Yoo, B.W.; Kim, Y.K. A Wafer-Level Vacuum Package Using Glass-Reflowed Silicon Through-Wafer Interconnection for Nano/Micro Devices. J. Nanosci. Nanotechnol. 2012, 12, 5252–5262. [Google Scholar] [CrossRef] [PubMed]

- Albaugh, K. Irreversibility of anodic bonding. Mater. Lett. 1986, 4, 465–469. [Google Scholar] [CrossRef]

- Bu, M.; Melvin, T.; Ensell, G.J.; Wilkinson, J.S.; Evans, A.G.R. A new masking technology for deep glass etching and its microfluidic application. Sens. Actuators A Phys. 2004, 115, 476–482. [Google Scholar] [CrossRef]

- Iliescu, C.; Miao, J.; Tay, F.E. Stress control in masking layers for deep wet micromachining of Pyrex glass. Sens. Actuators A Phys. 2005, 117, 286–292. [Google Scholar] [CrossRef]

- Iliescu, C.; Jing, J.; Tay, F.E.; Miao, J.; Sun, T. Characterization of masking layers for deep wet etching of glass in an improved HF/HCl solution. Surf. Coat. Technol. 2005, 198, 314–318. [Google Scholar] [CrossRef]

- Iliescu, C.; Chen, B.; Miao, J. On the wet etching of Pyrex glass. Sens. Actuators A Phys. 2008, 143, 154–161. [Google Scholar] [CrossRef]

- Zhu, H.; Holl, M.; Ray, T.; Bhushan, S.; Meldrum, D.R. Characterization of deep wet etching of fused silica glass for single cell and optical sensor deposition. J. Micromech. Microeng. 2009, 19, 065013. [Google Scholar] [CrossRef]

- Wei, J.; Nai, S.M.L.; Wong, C.K.S.; Sun, Z.; Lee, L.C. Low temperature glass-to-glass wafer bonding. IEEE Trans. Adv. Packag. 2003, 26, 289–294. [Google Scholar]

- Aljancic, U.; Resnik, D.; Vrtacnik, D.; Mozek, M.; Amon, S. Silicon-glass anodic bonding. Inf. Midem-J. Microelectron. Electron. Compon. Mater. 2004, 34, 168–173. [Google Scholar]

- Henmi, H.; Shoji, S.; Shoji, Y.; Yoshimi, K.; Esashi, M. Vacuum packaging for microsensors by glass-silicon anodic bonding. Sens. Actuators A Phys. 1994, 584, 243–248. [Google Scholar] [CrossRef]

- Rogers, T.; Kowal, J. Selection of glass, anodic bonding conditions and material compatibility for silicon-glass capacitive sensors. Sens. Actuators A Phys. 1995, 46, 113–120. [Google Scholar] [CrossRef]

- Tanaka, S. Wafer-level hermetic MEMS packaging by anodic bonding and its reliability issues. Microelectron. Reliab. 2014, 54, 875–881. [Google Scholar] [CrossRef]

- Corman, T.; Enoksson, P.; Stemme, G. Deep wet etching of borosilicate glass using an anodically bonded silicon substrate as mask. JMM 1998, 8, 84. [Google Scholar] [CrossRef]

- Li, X.; Abe, T.; Esashi, M. Deep reactive ion etching of Pyrex glass. In Proceedings of the IEEE Thirteenth Annual International Conference on Micro Electro Mechanical Systems, Miyazaki, Japan, 23–27 January 2000; pp. 271–276. [Google Scholar]

| Element | Oxygen | Silicon | Sodium | Aluminum | ||

|---|---|---|---|---|---|---|

| wt% | ||||||

| Location | ||||||

| A_glass | 58.335 | 35.83 | 3.94 | 1.895 | ||

| B_interface | 19.48 | 77.027 | 2.01 | 1.483 | ||

| C_interface | 12.45 | 85.45 | 1.12 | 0.98 | ||

| D_silicon | 0 | 100 | 0 | 0 | ||

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, M.; Yang, J.; He, Y.; Yang, F.; Zhao, Y.; Xue, F.; Han, G.; Si, C.; Ning, J. Research on the Protrusions Near Silicon-Glass Interface during Cavity Fabrication. Micromachines 2019, 10, 420. https://doi.org/10.3390/mi10060420

Zhang M, Yang J, He Y, Yang F, Zhao Y, Xue F, Han G, Si C, Ning J. Research on the Protrusions Near Silicon-Glass Interface during Cavity Fabrication. Micromachines. 2019; 10(6):420. https://doi.org/10.3390/mi10060420

Chicago/Turabian StyleZhang, Meng, Jian Yang, Yurong He, Fan Yang, Yongmei Zhao, Fen Xue, Guowei Han, Chaowei Si, and Jin Ning. 2019. "Research on the Protrusions Near Silicon-Glass Interface during Cavity Fabrication" Micromachines 10, no. 6: 420. https://doi.org/10.3390/mi10060420

APA StyleZhang, M., Yang, J., He, Y., Yang, F., Zhao, Y., Xue, F., Han, G., Si, C., & Ning, J. (2019). Research on the Protrusions Near Silicon-Glass Interface during Cavity Fabrication. Micromachines, 10(6), 420. https://doi.org/10.3390/mi10060420