In this section, we present the transfer function of the DCS noise model and analyze the noise in each component of the model. The results of the analysis revealed that the most significant factor affecting the phase adjustment accuracy was the quantization noise resulting from the low resolution of the DAC. To address this issue, we proposed a DCS method based on discrete - modulation. Furthermore, a method based on augmented Lagrangian optimization was designed to ensure the best performance of the - modulator. Finally, we designed a loop filter to ensure clock steering speed while maintaining steer accuracy.

2.1. Noise Analysis

Noise analysis is a crucial step for understanding the precision of DCS. The noise model of DCS can be treated as a linear system, with each component introducing independent and uncorrelated random noise. The total phase noise was calculated, and the power spectral density of the output phase noise was analyzed.

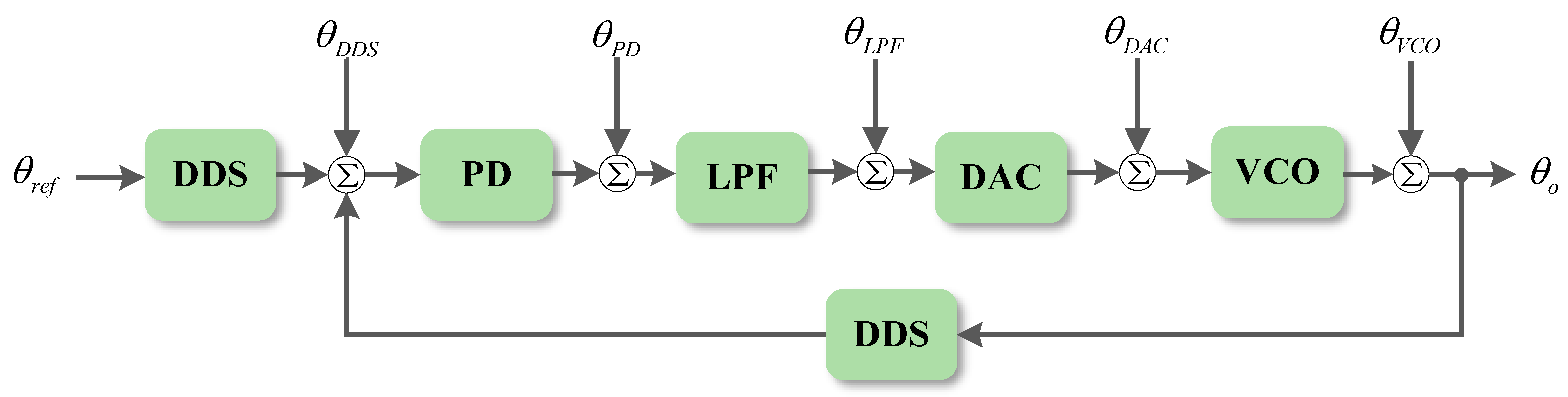

Figure 1 illustrates the noise transfer model of the DCS model, comprising the DDS, PD, LPF, DAC, and voltage-controlled oscillator (VCO), each of which contributes to the introduced noise.

The noise transfer function of the output signal is expressed as follows:

where

z is a complex variable,

is the PD gain,

is the LPF gain,

N is the allocation coefficient of the frequency divider,

is the transfer function of the LPF, and

is the transfer function of the VCO.

The phase noise power spectrum of the output signal can be generated by employing the superposition theorem. The obtained phase noise power spectral density of the output signal is expressed as follows:

where

f is the frequency.

Based on noise theory analysis, the main sources of noise are the DDS, DAC, frequency source, and PD. The level of noise introduced by a DDS depends on its frequency control word (FCW) and phase control word (PCW). The quantization noise can be reduced by increasing the number of bits in the FCW and PCW. Similarly, it can be minimized in a purely digital PD by increasing the number of bits. Thus, the quantization noise can be characterized as independent and uniformly distributed white noise, with the quantizer power spectral density given by

where

is the sampling rate and

is the quantization noise range.

Frequency source noise is inevitable and is often represented as a linear combination of five independent noises [

19]. To mitigate this noise, selecting a clock with a higher accuracy can be beneficial. The power spectral density of the frequency source noise is given by

where

f is the Fourier frequency,

is the amplitude, and

is the power-law spectral index.

The quantization noise introduced by the DAC can be mitigated by increasing its resolution. However, it is currently challenging to fulfill the requirements of a time–frequency reference system. Moreover, a higher-resolution DAC is often associated with a higher cost. Consequently, upgrading the hardware to address the issue of a low-resolution DAC and the resulting quantization noise may not be the most effective solution.

2.2. Discrete - Modulator Design

We designed a discrete

-

modulator to shape the quantization noise caused by insufficient resolution of the DAC.

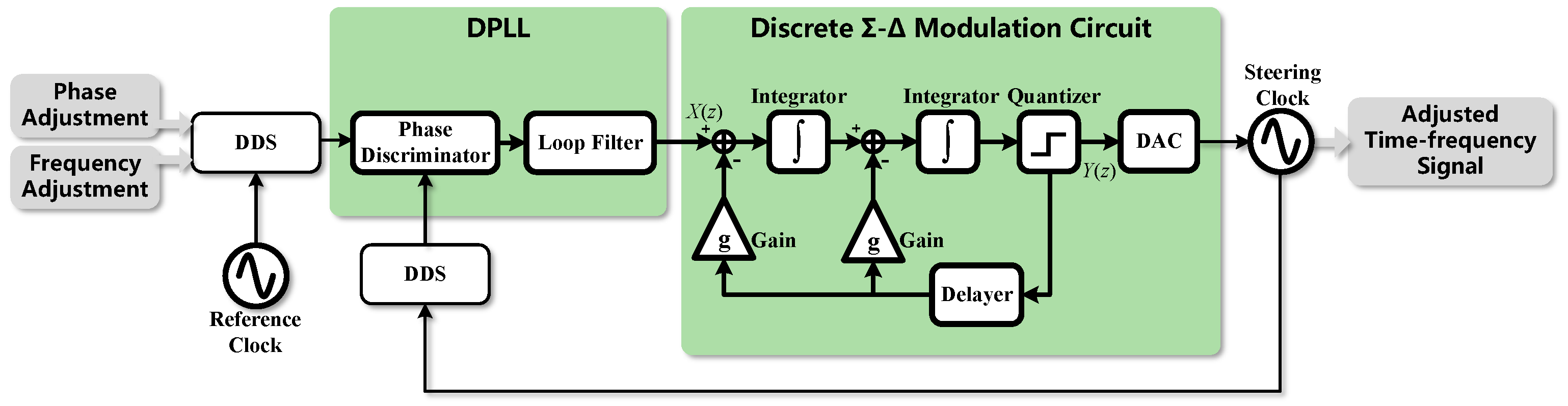

Figure 2 depicts the DCS model based on discrete

-

modulation. In this model, the reference and steering clocks function as sampling clocks for the two DDSs. Frequency and phase adjustments of the DDSs were achieved by varying the FCW and PCW. The phase discrimination of the output time–frequency signals from the two DDSs were carried out by the DPLL. The resulting phase difference is converted into digital frequency adjustment signals via loop filtering; it is then converted into an analog voltage-controlled voltage by the discrete

-

modulator. Ultimately, this voltage regulates the steering clock, thereby enabling the accurate output of the time–frequency signal after frequency and phase adjustments. The system transfer function of the DCS based on discrete

-

modulation can be represented as follows:

where

is the transfer function of the DCS system and

is the transfer function of the discrete

-

modulator.

In the DCS model, the phase adjustment is accomplished by integrating the frequency adjustment. After the phase difference signal passes through a high-order loop filter, the output includes not only the filtered result of the phase difference but also high-order information such as the speed and acceleration of phase difference changes [

20]. In a discrete

-

modulator, the input

is a frequency-adjusted signal, which is the integral of the phase signal. Therefore,

can be represented as:

where

is frequency step amplitude,

is frequency increment magnitude, and

is unit step sequence. Its z-transform is:

According to the final value theorem, we need to design a second-order

-

modulator to ensure that the steady-state error of the system is 0.

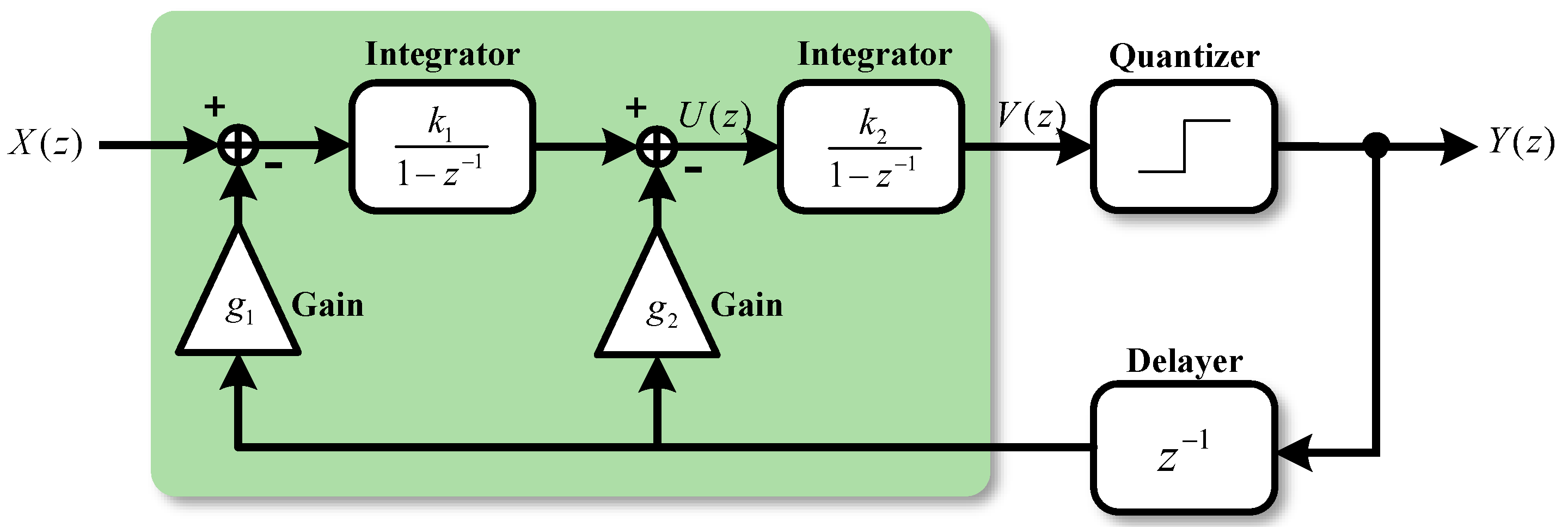

Figure 3 shows the transfer function model of a second-order discrete

-

modulator.

Based on the system block diagram of the second-order discrete

-

modulator, the noise transfer function can be defined as follows:

where

is the noise transfer function of the discrete

-

modulator,

and

are the gain of the integrator,

and

are the loop gain, and

is the noise transfer function introduced by the quantizer, which can be seen as a type of uniformly distributed noise. The noise transfer function of

can be defined as follows:

where

is the resolution of the DAC.

To achieve system convergence, with all zeros and poles of the system transfer function inside the unit circle, we provide constrains as follows:

where

,

,

, and

are functions for finding zeros and poles.

The frequency adjustment resolution is primarily influenced by the DAC reference voltage and DAC resolution. Equation (

11) represents the calculation formula for the frequency-adjustment resolution.

where

is the frequency-adjustment resolution,

is the DAC reference voltage, and

N is the DAC bit.

The minimum resolution of the voltage-controlled voltage output of the DAC is directly proportional to the frequency-adjustment resolution, which differs from the frequency adjustment accuracy. The frequency adjustment resolution refers to the minimum resolution of the actual tuning frequency of the VCO output, which is determined by the hardware parameters.

To enhance the accuracy of frequency and phase adjustments, it is important to analyze the relationship between the DCS frequency and phase and the loop update period, while also designing the gains for the - modulator. Additionally, increasing the value of g provides a loop with sufficient gain, improves the tracking capabilities, and reduces the steady-state error in the DCS model. Moreover, decreasing the value of k helps to control the range of .

The objective function can be represented as follows:

where

is the frequency adjustment deviation between the actual value and the ideal value, with minimax values reducing quantization errors.

Combining Equations (10) and (12), the

-

modulator design problem can be posed as follows:

Equation (

13) represents a minimax optimization problem with constraints. We solve it using the augmented Lagrangian method [

21]. The augmented Lagrangian function is as follows:

where

is the penalty parameter,

,

,

, and

are Lagrangian multipliers, and

,

,

, and

are slack variables.

The algorithm is implemented as follows:

- (1)

Update

,

,

, and

, by solving Equation (

14), we find the optimal value of

,

,

, and

.

Variables

,

,

, and

appear only in the two terms of Equation (

14), which is actually a convex quadratic function of each relaxation variable. We take the partial derivative of

. The unconstrained minimum of Equation (

14) with respect to

occurs when the partial derivative equals 0. If this is an unconstrained minimum, which has a lower bound less than 0, then it is convex in Equation (

14). The optimal solution for

in Equation (

13) is 0. Therefore, the solution to Equation (

13) is:

- (2)

Update

,

,

, and

by:

Then, continuously repeat steps 1 and 2. Upon meeting the termination conditions, the optimal

-

modulation gain is obtained.

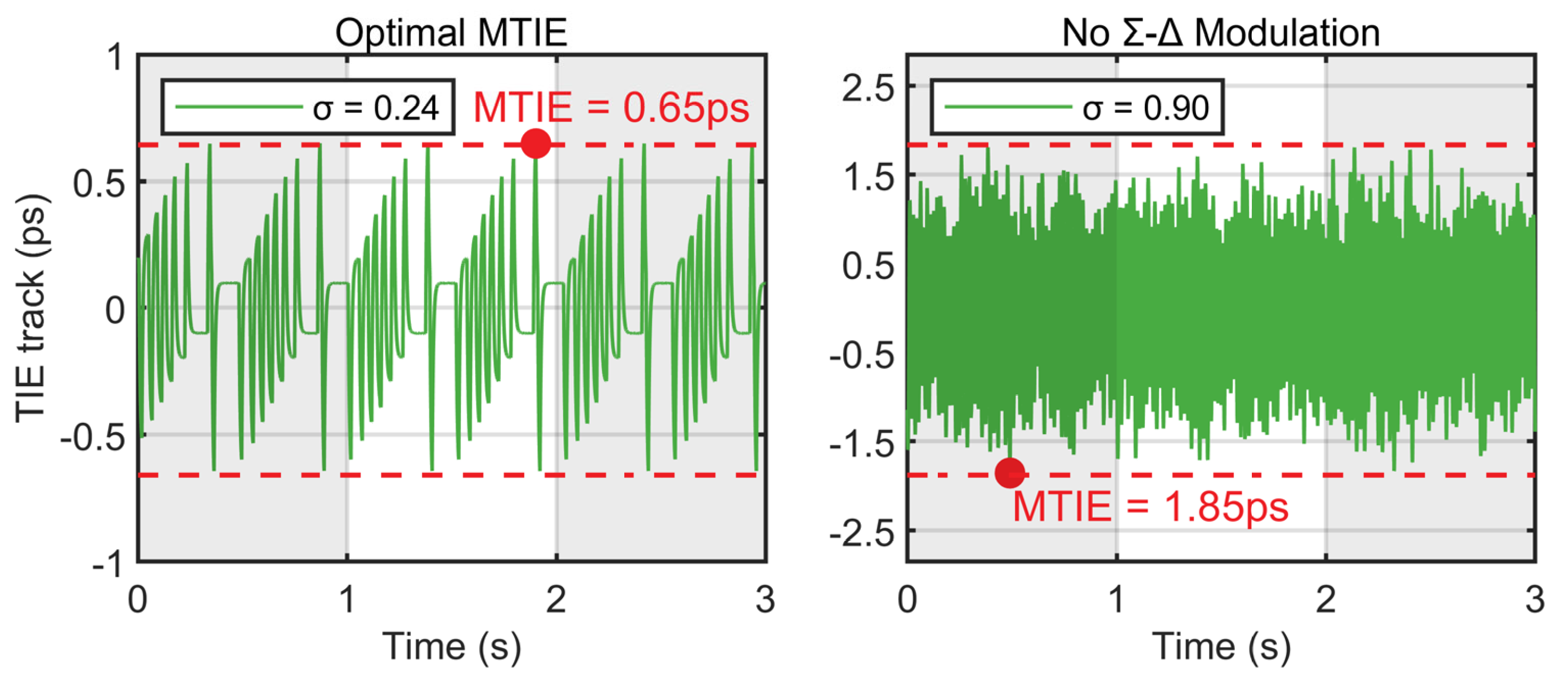

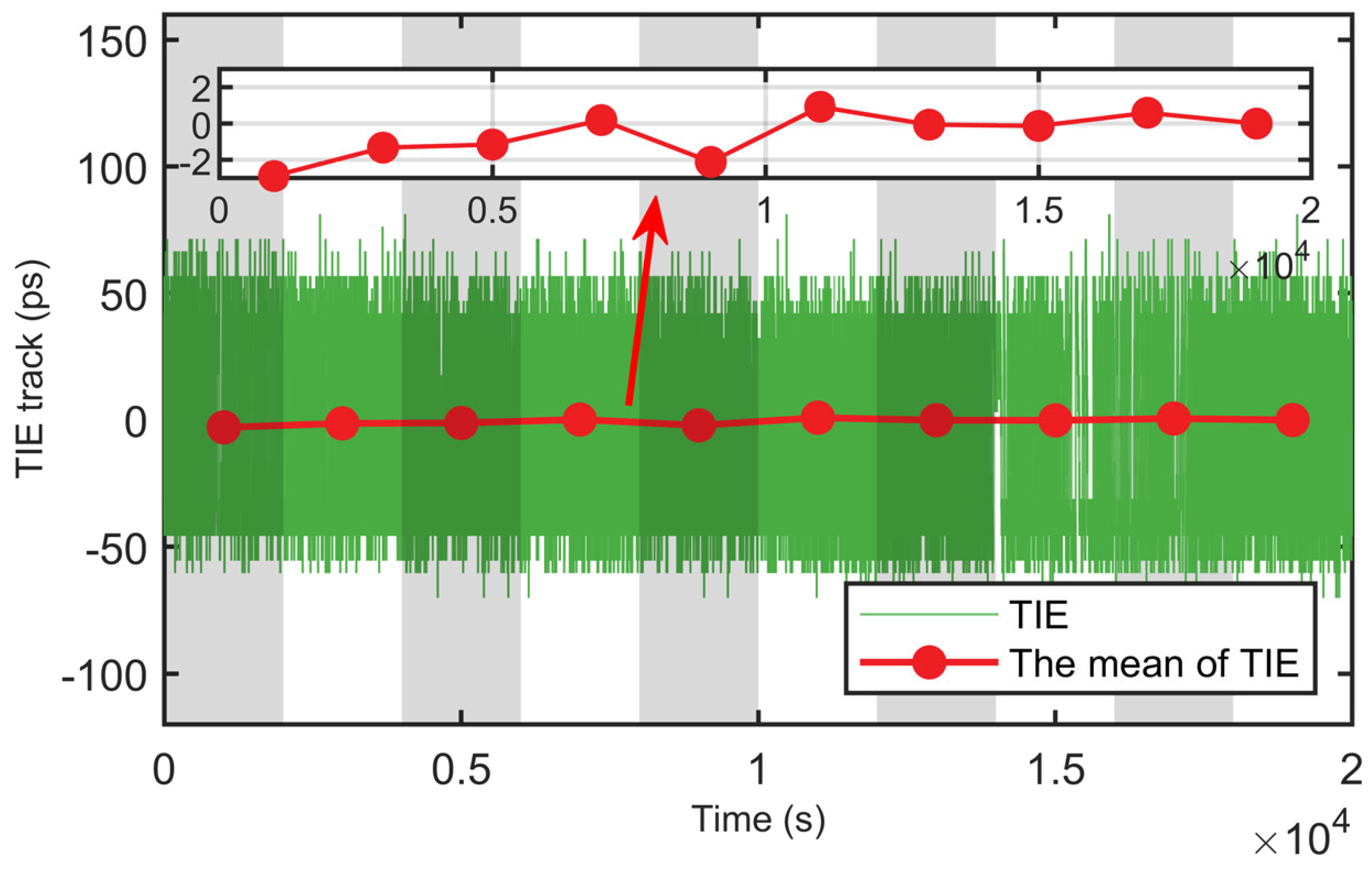

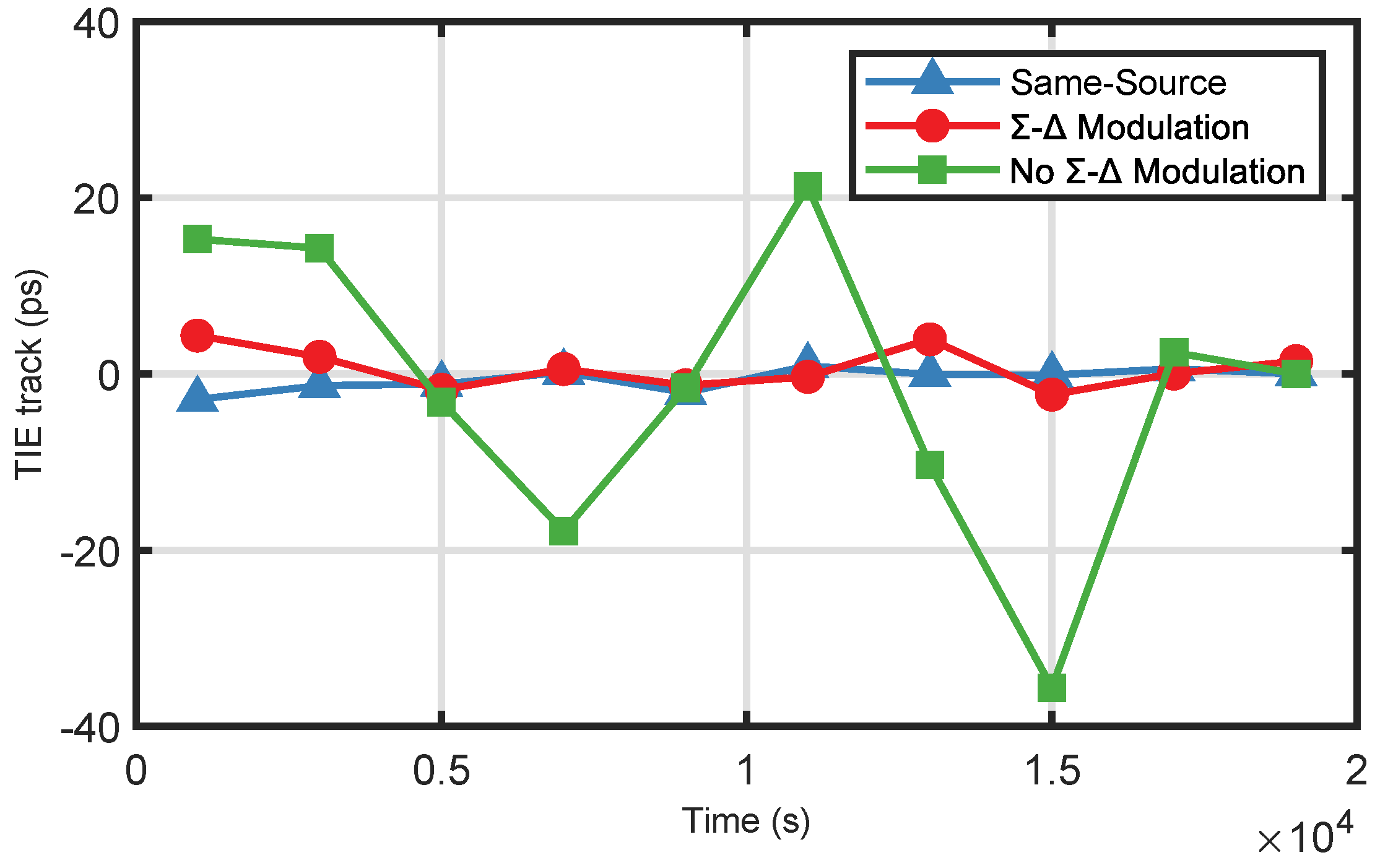

Figure 4 shows the TIE trace of the optimal MTIE and without the use of

-

modulation.

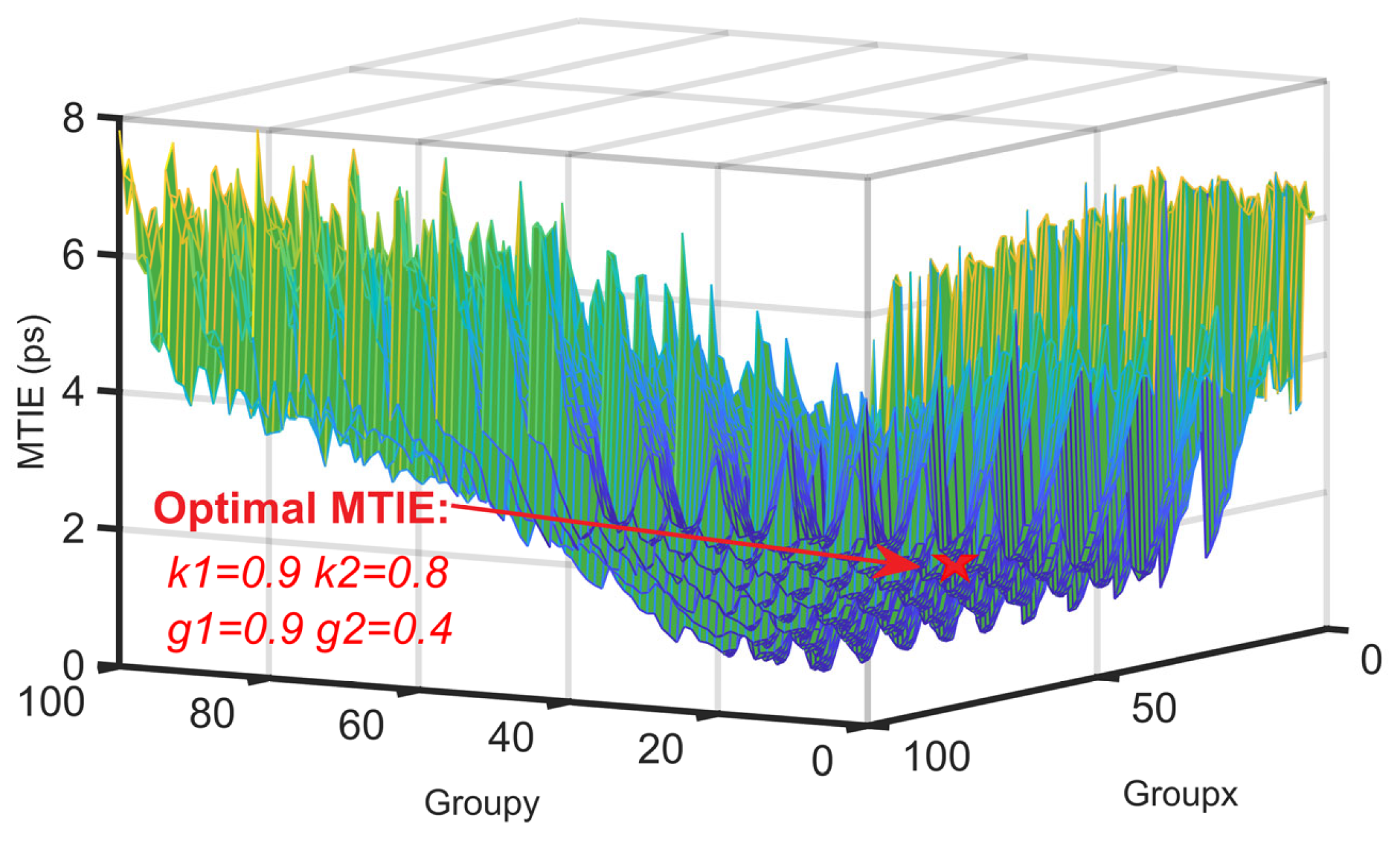

To validate the correctness of the optimization algorithm results, we conducted Monte Carlo simulations using the values of

k1,

k2,

g1, and

g2. During the simulations, we used a performance metric: the maximum time interval error (MTIE). The goal was to determine the optimal parameter values corresponding to this metric.

Figure 5 shows the Monte Carlo simulations for finding the optimal MTIE result. The optimal MTIE result of the Monte Carlo simulations is consistent with the derived results of the augmented Lagrangian method. Simulation conditions are as follows.

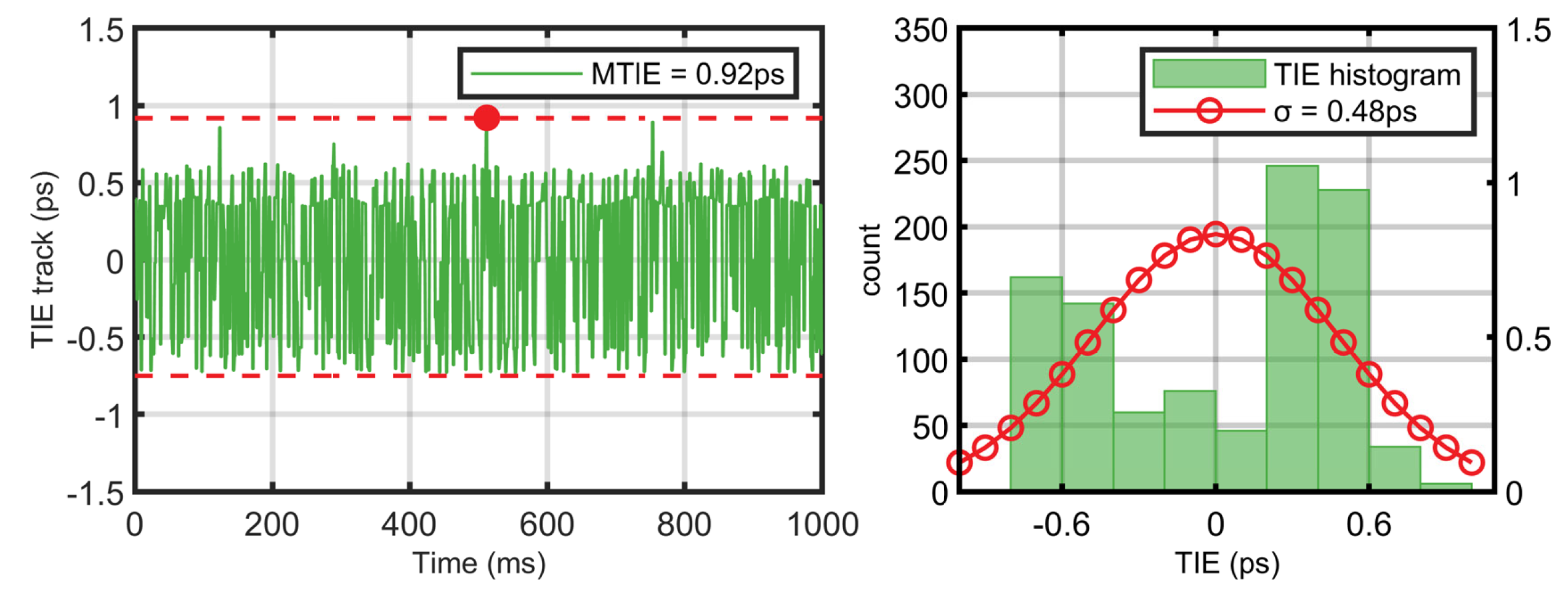

In

Figure 6, we compare the TIE histograms with different

-

modulator gain values and without the use of

-

modulation. A TIE histogram provides a direct analysis of the various characteristics of the TIE. When the number of measurements, N, in the TIE was sufficiently large (N > 100), the TIE histogram effectively reflected its statistical characteristics. By comparing the TIE histograms, we can more directly observe and analyze the distribution and statistical properties of the TIE, which thereby enables us to evaluate the performance improvements achieved by the proposed method.

In this study, the TIE was transformed into a frequency-tracking error. Notably, the frequency-tracking error differs from the frequency-adjustment resolution. The frequency-adjustment resolution refers to the minimum resolution of the actual tuning frequency of the output from the VCO. In contrast, the frequency-tracking error is the result of the phase-value determination. According to Equation (

17), under the optimal MTIE conditions, the frequency-tracking error was calculated to be 0.24 pHz.

where

is the time interval used to calculate the frequency. The time–frequency signal is often used for counting to generate a one pulse per second (1PPS) signal. Here, we take

as 1 s.

2.3. Optimal LPF Design

The performance of a

-

modulator is directly affected by the phase difference filtering results of the LPF, as it serves as the input to the

-

modulator. At the same time, the LPF design is crucial for determining the dynamic and steady-state characteristics of the PLL. We empirically designed the loop bandwidth and loop update period to achieve a PLL that meets the requirements of a steady-state error, locking time, overshoot, and other factors. Equation (

18) provides a formula for the loop bandwidth of a third-order PLL:

where

and

are the classical parameters of the third-order LPF and

is the characteristic frequency of the phase-locked loop.

The equivalent noise bandwidth of a DPLL can be approximated as a function of the closed-loop system frequency response

.

Rewrite Equation (

19) as follows:

where the integral of the circumference

, its integral path, is a unit circle.

Derive the relationship between the loop bandwidth of a third-order DPLL and the loop bandwidth of an analog PLL by combining Equations (18), (20), and (21).

where

,

, and

are the classical parameters of the third-order LPF;

is the analog third-order PLL loop bandwidth; and

is the loop update period.

The simulation results of the optimal loop bandwidth in

Figure 7 show that, when

is 20, the locking time of the PLL is 1 s, when

is 30, the locking time of the PLL is 1 s, and, when

is 10, the lock time of the PLL is 1.5 s. The steady-state errors of the DPLL were equal for different loop bandwidths. Reducing the loop bandwidth of the DPLL increased the locking time; however, the phase-tracking accuracy did not improve after the PLL stabilized.

Therefore, the design concept behind the DPLL loop bandwidth and loop update period aims to maximize the loop tracking accuracy by appropriately increasing the loop bandwidth and accelerating the loop update period. This approach achieves a high level of precision and fast loop locking.