An Asymmetrical Step-Up Multilevel Inverter Based on Switched-Capacitor Network

Abstract

:1. Introduction

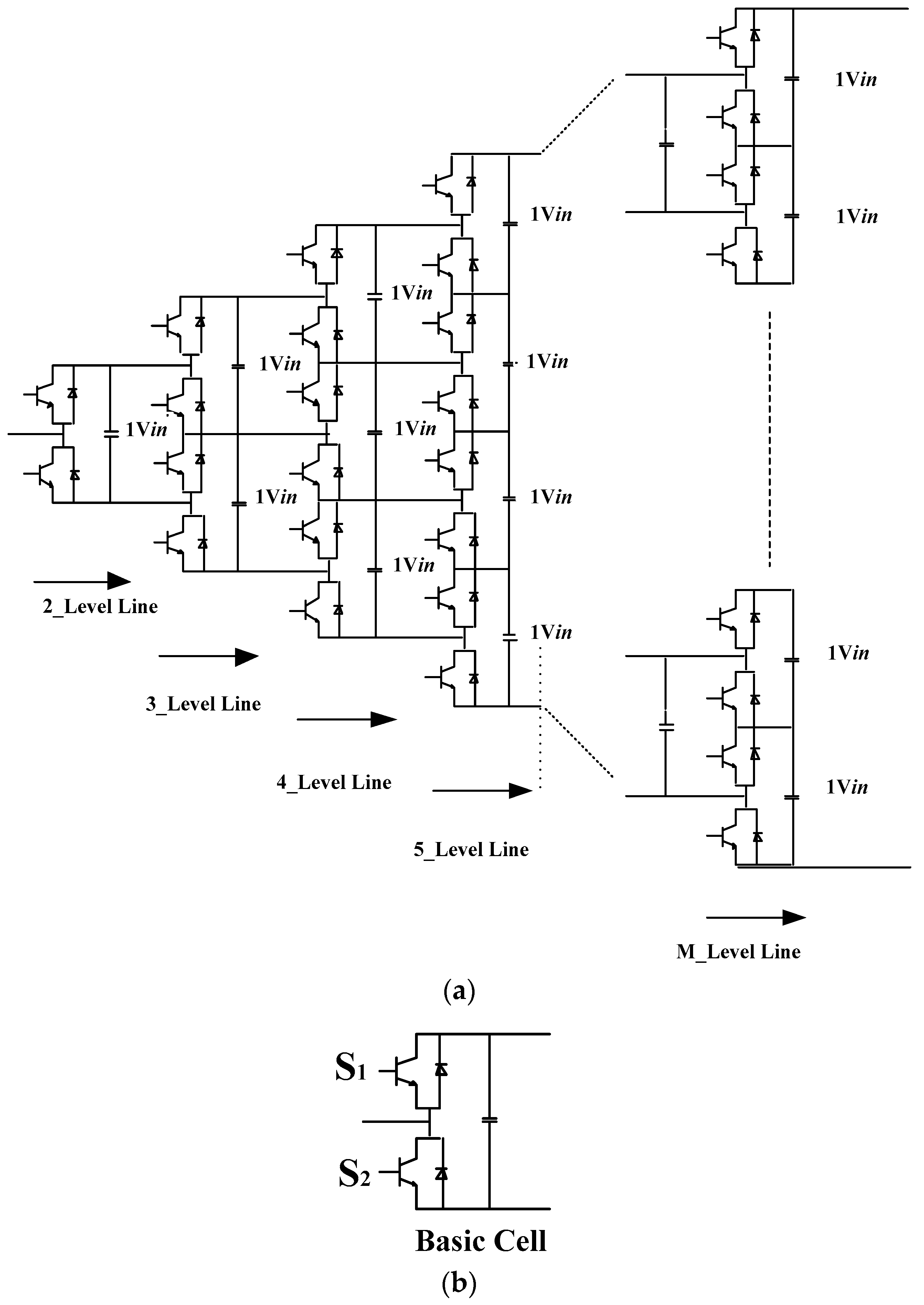

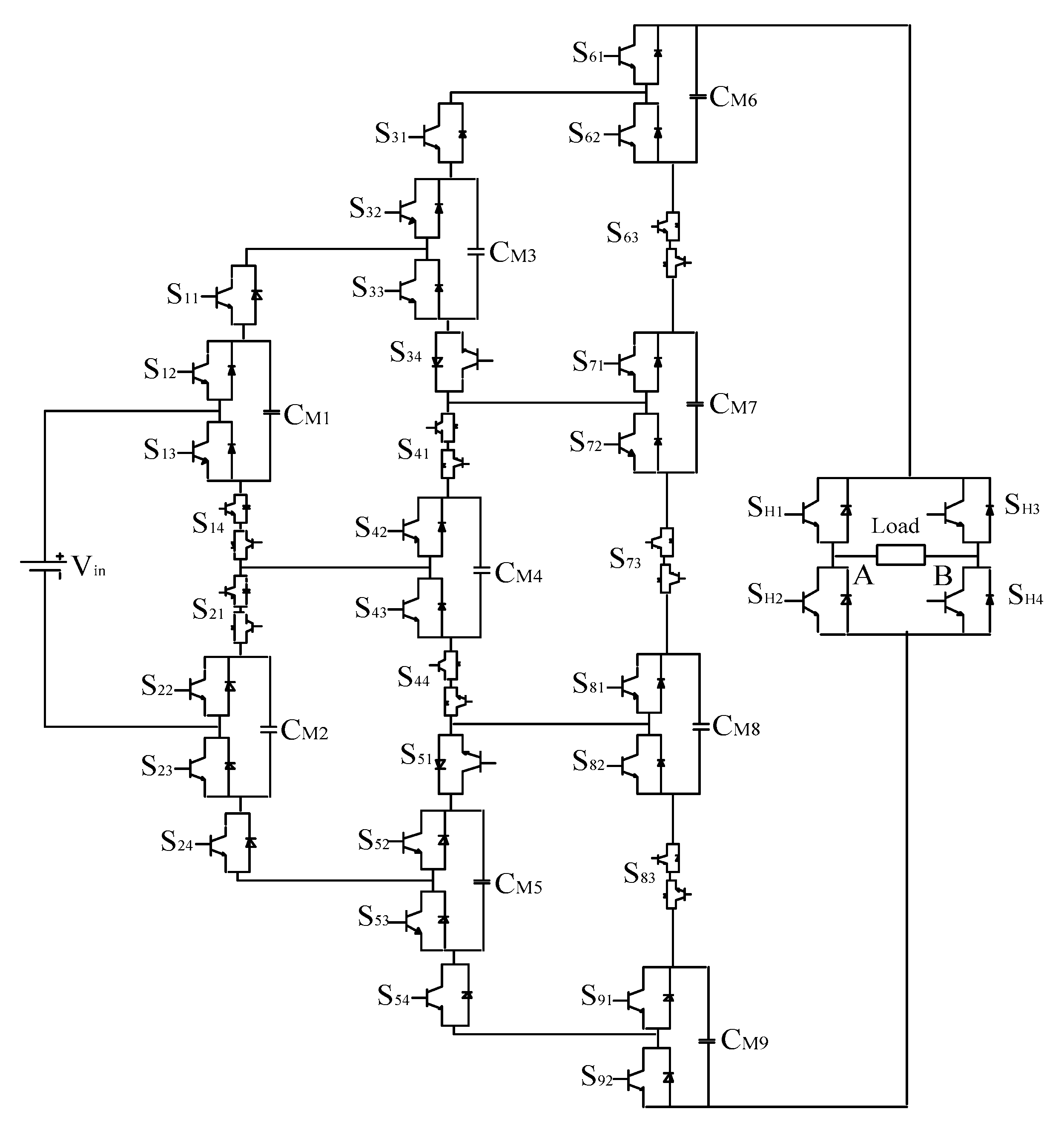

2. Proposed Topology

3. Operating Principle of the Proposed Topology

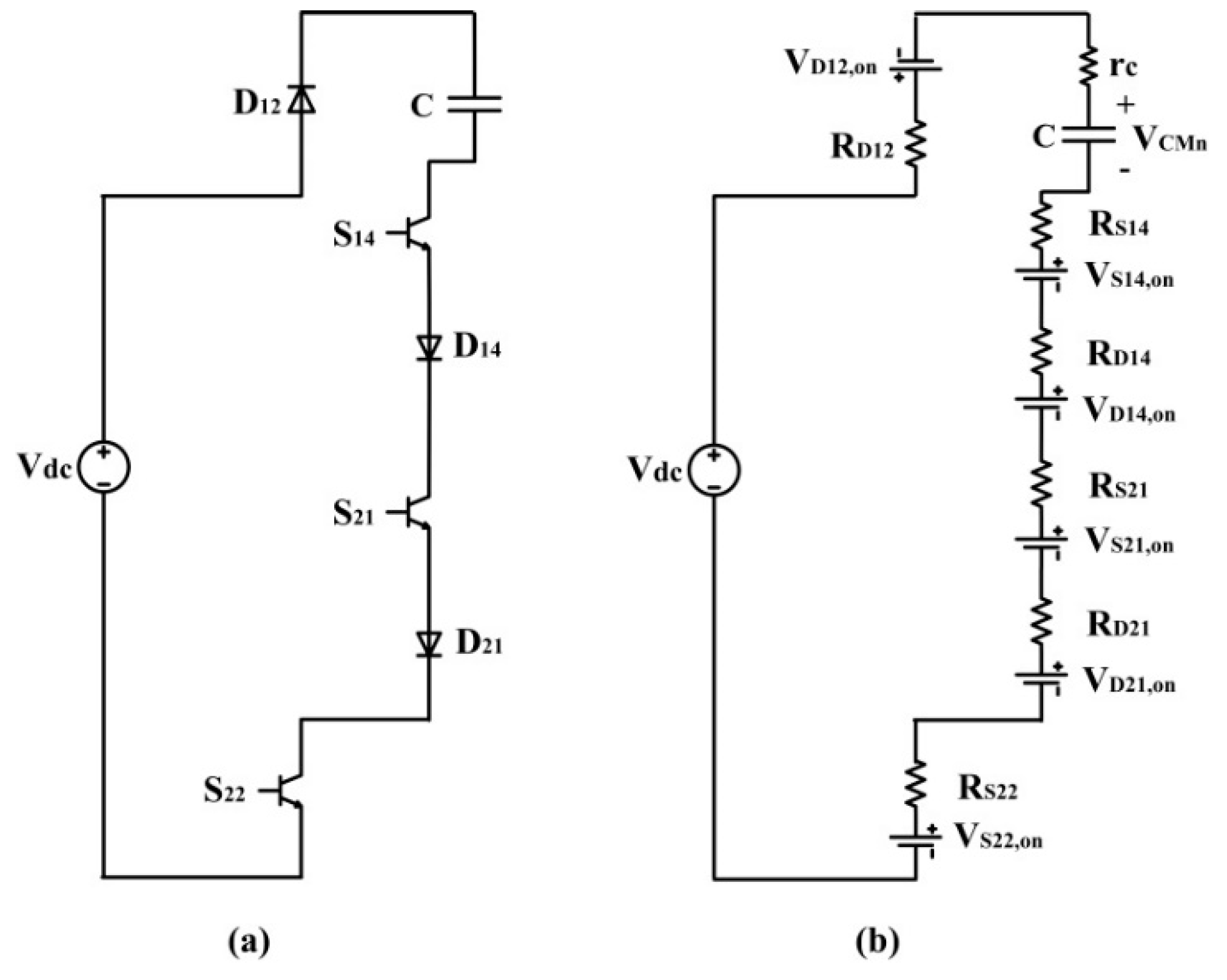

4. Asymmetrical Charging of the Capacitors

- VDij: Diode on-state voltage of ith module and jth diode

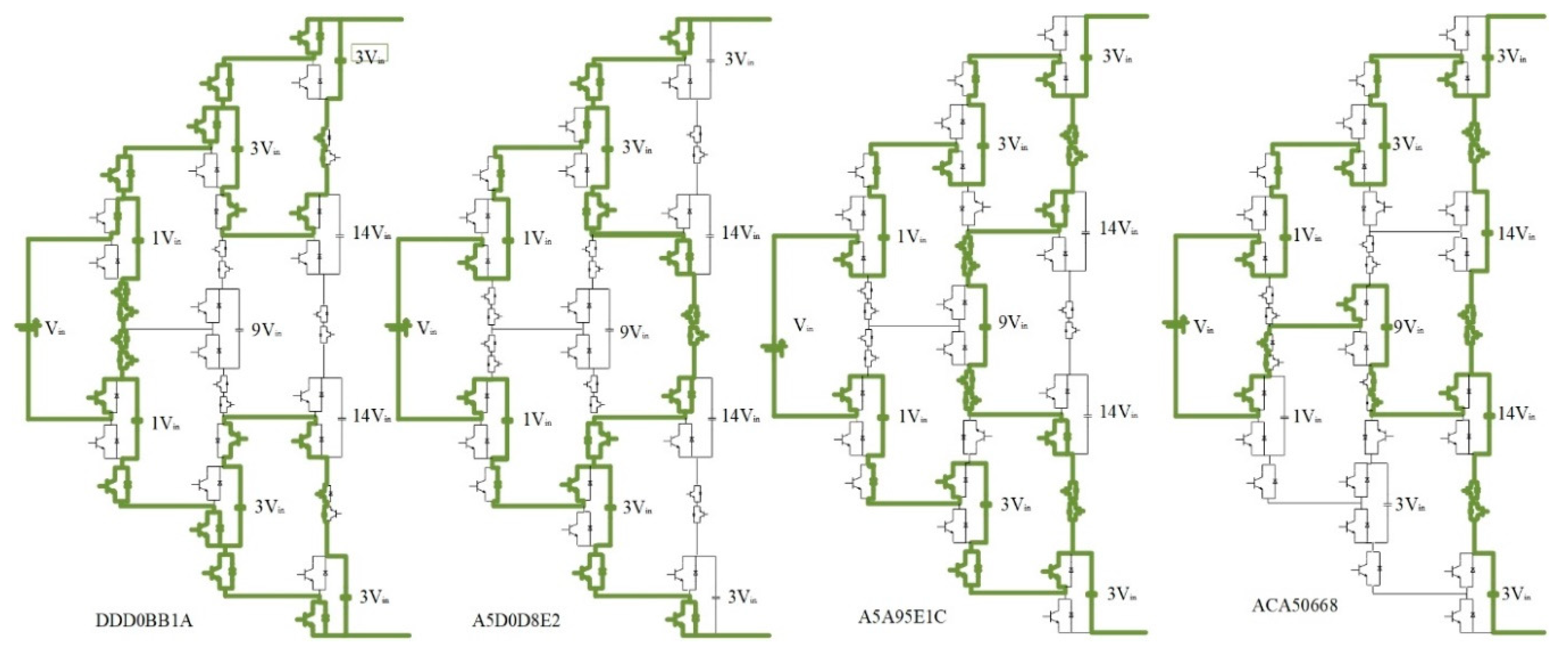

- RDij: Diode on-state resistant of ith module and jth diode

- rcn: ESR of nth capacitor

- VSij: Switch on-state voltage of ith module and jth switch

- RSij: RDij: Switch on-state resistant of ith module and jth switch

5. Multilevel Output Voltage Generation

6. Capacitor Calculation for Self-Balancing Purpose

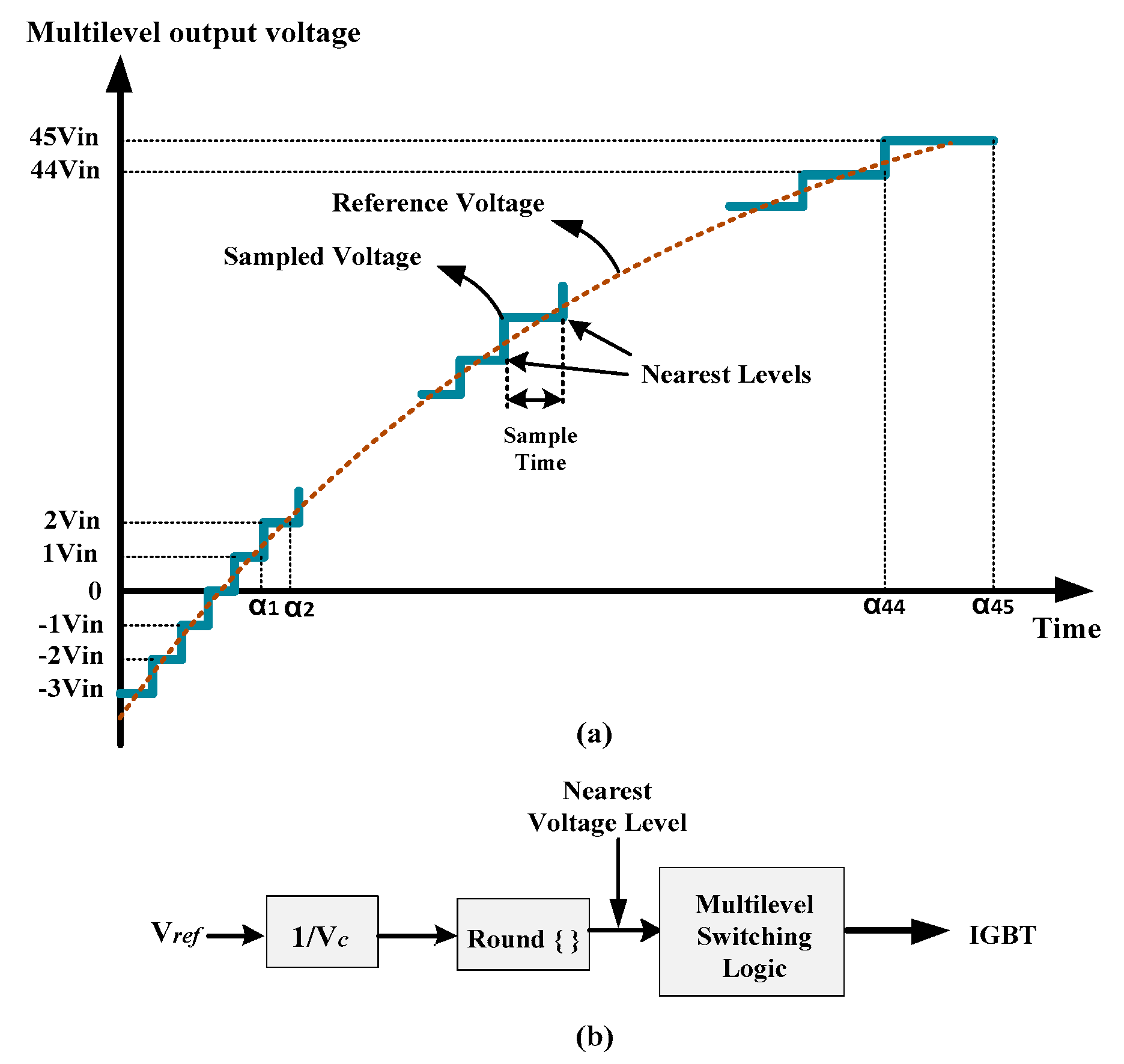

7. Modulation Strategy and Switching States Selection

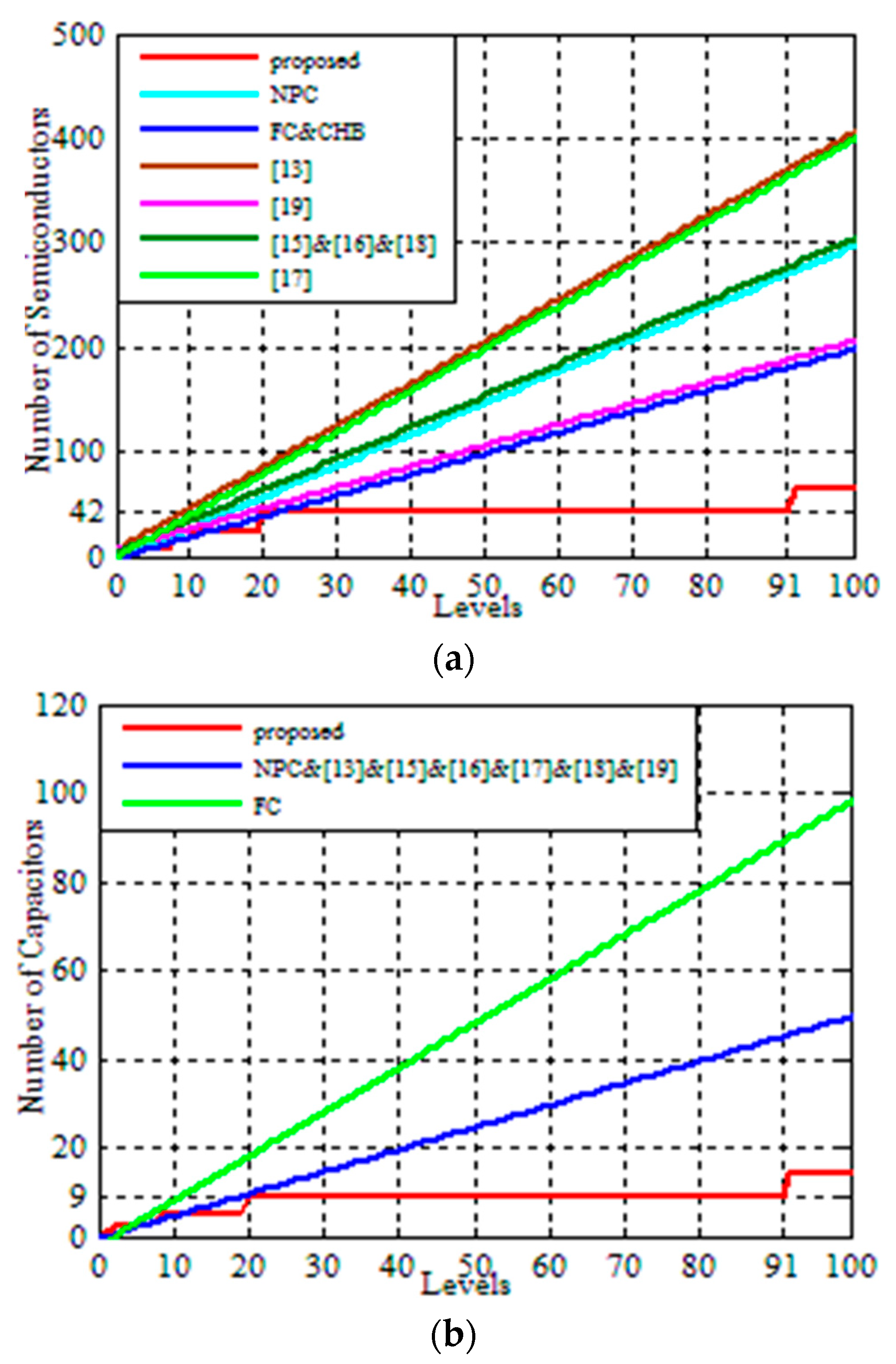

8. Comparison with Other Topologies

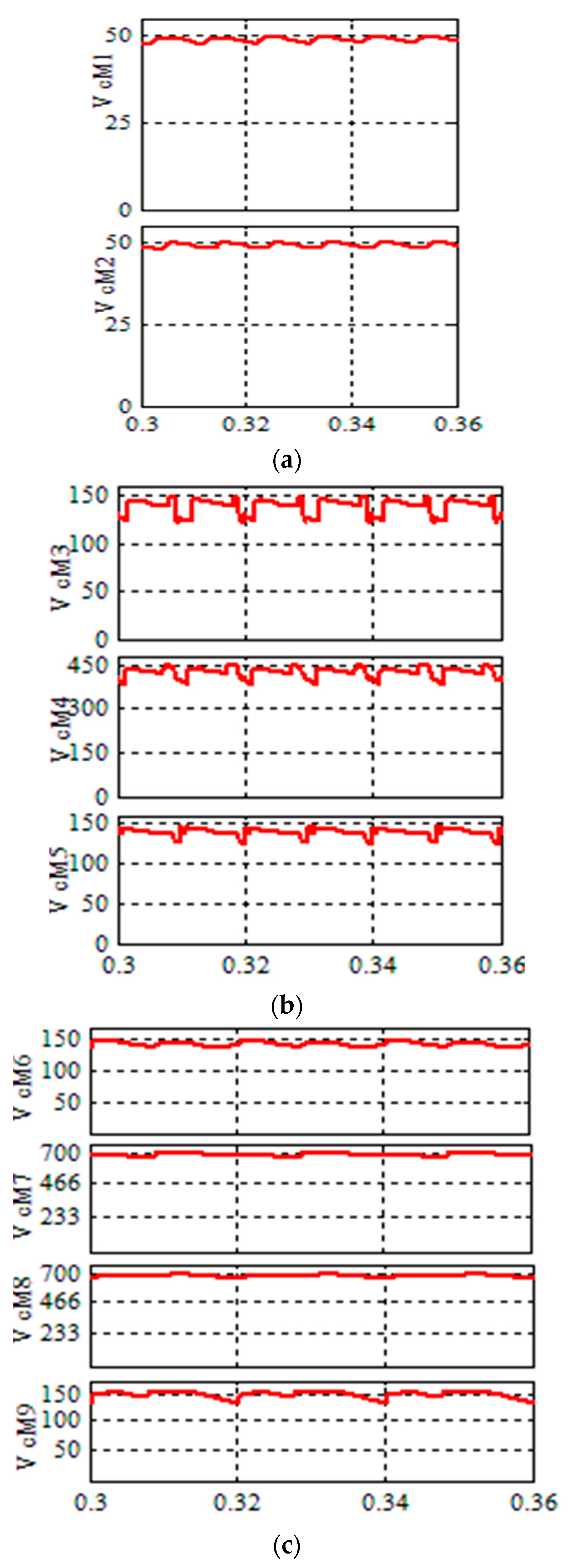

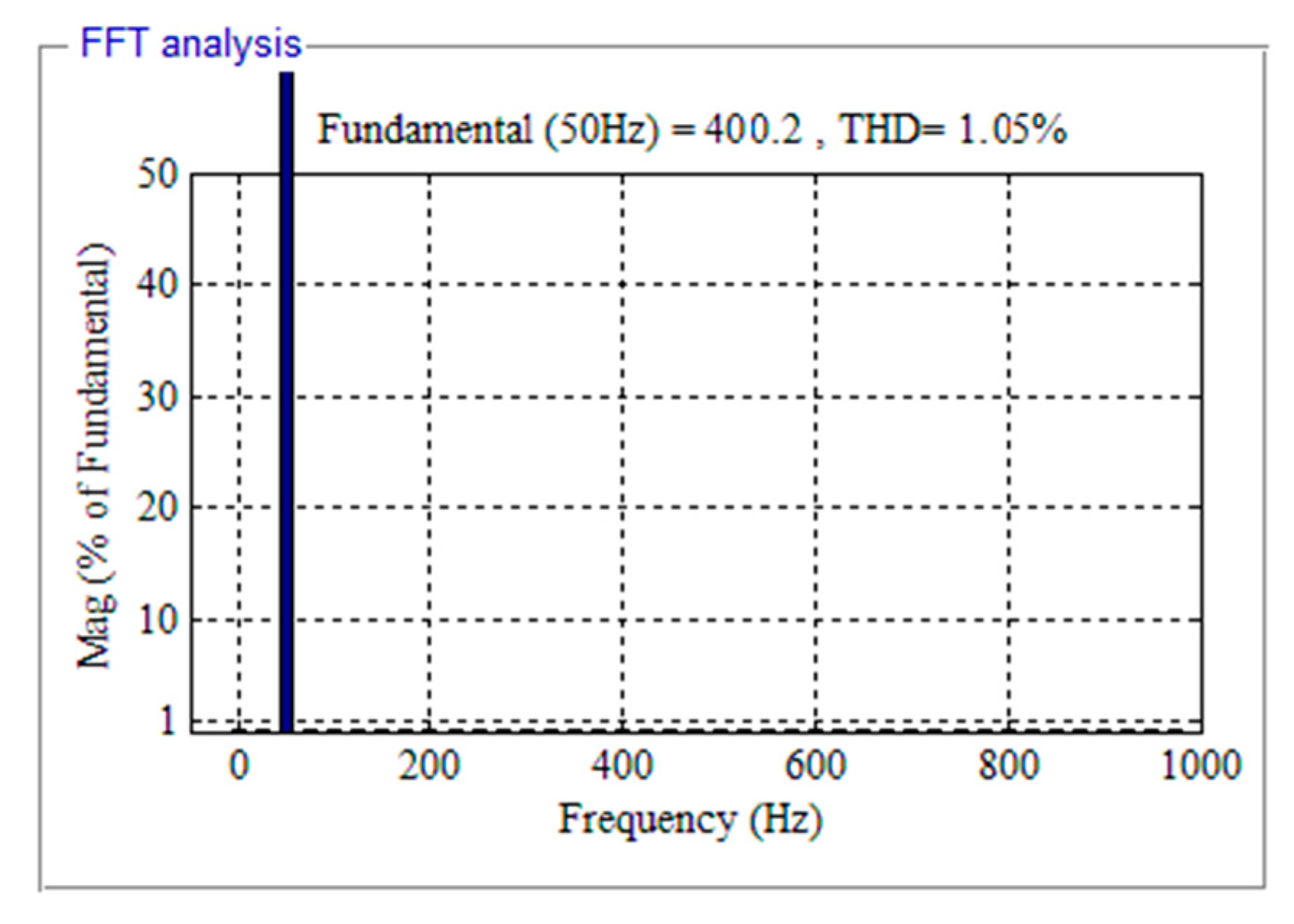

9. The Simulation Results

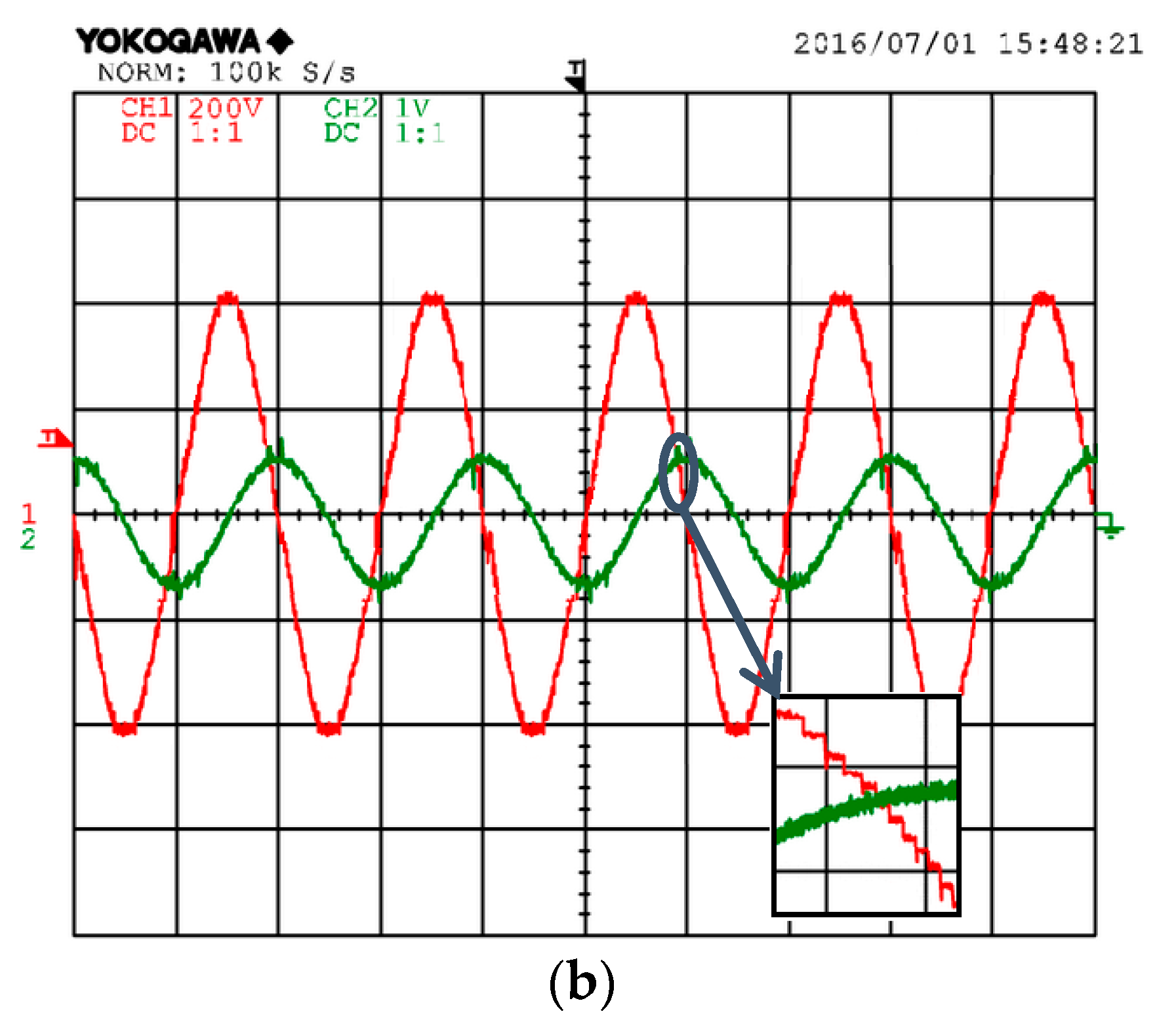

10. Experimental Results

11. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Mohan, N.; Undeland, T.M.; Robbins, W.P. Power Electronics: Converters, Applications and Design, 3rd ed.; John Wiley & Sons: Hoboken, NJ, USA, 2003. [Google Scholar]

- Nabae, N.; Takahashi, I.; Akagi, H. A new neutral point clamped PWM inverter. IEEE Trans. Ind. Appl. 1981, 17, 518–523. [Google Scholar] [CrossRef]

- Zare, F. Power Electronics Education Electronic-Book, 1st ed.; School of Engineering Systems, Queensland University of Technology: Brisbane, Australia, 2008. [Google Scholar]

- Khenar, M.; Taghvaie, A.; Adabi, J.; Rezanejad, M. Multi-level inverter with combined T-type and cross-connected modules. IET Power Electron. 2018, 11, 1407–1415. [Google Scholar] [CrossRef]

- Vahedi, H.; Labbe, P.A.; Haddad, K.A. Sensor-Less Five-Level Packed U-Cell (PUC5) Inverter Operating in Stand-Alone and Grid-Connected Modes. IEEE Trans. Ind. Inform. 2016, 12, 361–370. [Google Scholar] [CrossRef]

- Taghvaie, A.; Adabi, J.; Rezanejad, M. A Multilevel Inverter Structure Based on a Combination of Switched-Capacitors and DC Sources. IEEE Trans. Ind. Inform. 2017, 13, 2162–2171. [Google Scholar] [CrossRef]

- Taghvaie, A.; Adabi, J.; Rezanejad, M. Circuit Topology and Operation of a Step-Up Multilevel Inverter with a Single DC Source. IEEE Trans. Ind. Electron. 2016, 63, 6643–6652. [Google Scholar] [CrossRef]

- Samsami, H.; Taheri, A.; Samanbakhsh, R. New bidirectional Multilevel inverter topology with staircase cascading for symmetric and asymmetric structures. IET Power Electron. 2017, 10, 1315–1323. [Google Scholar] [CrossRef]

- Ali, J.S.M.; Alishah, R.S.; Sandeep, N.; Hosseini, S.H.; Babaei, E.; Vijayakumar, K.; Yaragatti, U.R. A new generalized multilevel converter topology based on cascaded connection of basic units. IEEE J. Emerg. Sel. Top. 2018. [Google Scholar] [CrossRef]

- Pereda, J.; Dixon, J. High-frequency link: A solution for using only one DC source in asymmetric cascaded multilevel invrter. IEEE Trans. Ind. Electron. 2011, 58, 3884–3893. [Google Scholar] [CrossRef]

- Vijeh, M.; Rezanejad, M.; Samadaei, E.; Bertilson, K. A general review on multilevel inverters based on main submodule: Structural point of view. IEEE Trans. Power Electron. 2019. [Google Scholar] [CrossRef]

- Gautam, S.P.; Sahu, L.K.; Gupta, S. Reduction in number of devices for symmetrical and asymmetrical multilevel inverters. IET Power Electron. 2016, 9, 698–709. [Google Scholar] [CrossRef]

- Chattopadhyay, S.K.; Chakraborty, C. A New Multilevel Inverter Topology with Self-Balancing Level Doubling Network. IEEE Trans. Ind. Electron. 2014, 61, 4622–4631. [Google Scholar] [CrossRef]

- Tseng, K.C.; Huang, C.C.; Shih, W.Y. A High Step-Up Converter with a Voltage Multiplier Module for a Photovoltaic System. IEEE Trans. Power Electron. 2013, 28, 3047–3057. [Google Scholar] [CrossRef]

- Du, Z.; Ozpineci, B.; Tolbert, L.M.; Chiasson, J.N. DC-AC cascaded H-bridge multilevel boost inverter with no inductors for electric/hybrid electric vehicle applications. IEEE Trans. Ind. Appl. 2009, 45, 963–970. [Google Scholar] [CrossRef]

- Lee, S.S.; Chu, B.; Rumzi, N.; Idris, N.; Goh, H.H.; Heng, Y.E. Switched-Battery Boost-Multilevel Inverter with GA Optimized SHEPWM for Standalone Application. IEEE Trans. Ind. Electron. 2016, 63, 2133–2142. [Google Scholar] [CrossRef]

- Mak, O.C.; Ioinovici, A. Switched-capacitor inverter with high power density and enhanced regulation capability. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 1998, 45, 336–347. [Google Scholar]

- Liu, Y.; Luo, F.L. Multilevel inverter with the ability of self-voltage balancing. IEE Proc. Electr. Power Appl. 2006, 153, 105–115. [Google Scholar] [CrossRef]

- Hinago, Y.; Koizumi, H. A Switched-Capacitor Inverter Using Series/Parallel Conversion with Inductive Load. IEEE Trans. Ind. Electron. 2012, 59, 878–887. [Google Scholar] [CrossRef]

- Babaei, E.; Gowgani, S.S. Hybrid multilevel inverter using switched-capacitor units. IEEE Trans. Ind. Electron. 2014, 61, 4614–4621. [Google Scholar] [CrossRef]

- Barzegarkhoo, R.; Kojabadi1, H.M.; Zamiry, E.; Vosooghi, N.; Chang, L. Generalized Structure for a Single Phase Switched-Capacitor Multilevel Inverter Using a New Multiple DC Link Producer with Reduced Number of Switches. IEEE Trans. Power Electron. 2016, 31, 5604–5617. [Google Scholar] [CrossRef]

- Ye, Y.; Cheng, K.W.E.; Liu, J.; Ding, K. A Step-Up Switched-Capacitor Multilevel Inverter with Self Voltage Balancing. IEEE Trans. Ind. Electron. 2014, 61, 6672–6680. [Google Scholar] [CrossRef]

- Ebrahimi, J.; Babaei, E.; Gharehpetian, G.B. A New Multilevel Converter Topology with Reduced Number of Power Electronic Components. IEEE Trans. Ind. Electron. 2012, 59, 655–667. [Google Scholar] [CrossRef]

- Peng, F.Z. A Generalized Multilevel Inverter Topology with Self Voltage Balancing. IEEE Trans. Ind. Appl. 2001, 37, 611–618. [Google Scholar] [CrossRef]

- Taghvaie, A.; Adabi, J.; Rezanejad, M. A Self-Balanced Step-up Multilevel Inverter based on Switched-Capacitors Structure. IEEE Trans. Power Electron. 2018, 33, 199–209. [Google Scholar] [CrossRef]

- Meshram, P.M.; Borghate, V.B. A Simplified Nearest Level Control (NLC) Voltage Balancing Method for Modular Multilevel Converter (MMC). IEEE Trans. Power Electron. 2015, 30, 450–462. [Google Scholar] [CrossRef]

| n | k | m | |

|---|---|---|---|

| 2 | 3 | 3 | |

| 3 | 6 | 6 | |

| 4 | 12 | 8 | |

| 5 | 6 | 6 | |

| 6 | 3 | 3 | |

| 7 | 10 | 6 | |

| 8 | 10 | 6 | |

| 9 | 3 | 3 |

| VCM1 | VCM2 | VCM3 | VCM4 | VCM5 | VCM6 | VCM7 | VCM8 | VCM9 | |

|---|---|---|---|---|---|---|---|---|---|

| 0(0000) | 0 (-) | 0 (-) | 0 (-) | 0 (-) | 0 (-) | 0 (-) | 0 (-) | 0 (-) | 3Vin (▼) |

| 2(0010) | ⨯ | ⨯ | ⨯ | ⨯ | ⨯ | 3Vin (▼) | 14Vin(▼,▲) | 14Vin (▼,▲) | ⨯ |

| 3 (0011) | 0 (-) | 0 (-) | 0 (-) | 0 (-) | 0 (-) | ⨯ | ⨯ | ⨯ | ⨯ |

| 4(0100) | ⨯ | ⨯ | ⨯ | ⨯ | ⨯ | 3Vin (▼) | 14Vin (▼) | 14Vin (▼) | 0 (-, ▲) |

| 5(0101) | −1Vin (▲) | 1Vin (▼) | −3Vin (▲) | 9Vin (▼) −9Vin (▼) | 3Vin (▼) | ⨯ | ⨯ | ⨯ | ⨯ |

| 6(0110) | ⨯ | ⨯ | ⨯ | ⨯ | ⨯ | 0 (-) | 0 (-) | 0 (-) | _ |

| 8(1000) | ⨯ | ⨯ | ⨯ | ⨯ | ⨯ | 0 (-) | 0 (-) | 0 (-) | 3Vin(▼) |

| 9(1001) | 1Vin(▼) | 1Vin(▼) | 3Vin(▼) | 9Vin (▲▼) −9Vin(▼) | 3Vin(▼) | ⨯ | ⨯ | ⨯ | ⨯ |

| A(1010) | 1Vin(▼) | −1Vin(▲) | 3Vin(▼) | 9Vin (▼) −9Vin (▼) | −3Vin (▲) | 3Vin (▲) | 14Vin (▼) | 14Vin (▼) | ⨯ |

| B(1011) | 1Vin (▼) | 1Vin (▲) | 3Vin (▼) | ⨯ | 3Vin (▲) | ⨯ | ⨯ | ⨯ | ⨯ |

| C(1100) | 0 (-) | 0 (-) | 0 (-) | ⨯ | 0 (-) | ⨯ | ⨯ | ⨯ | ⨯ |

| D(1101) | 1Vin (▲) | 1Vin (▼) | 3Vin (▲) | ⨯ | 3Vin (▼) | ⨯ | ⨯ | ⨯ |

| Level | Switching States (CM1, CM2, CM3, CM4, CM5, CM6, CM7, CM8, CM9) |

|---|---|

| 0VIN | 5C0000000(↑− − − − − − − −) 3A0000000(−↑− − − − − − −) A550C0680(↓↓↑− − − − − −) A530A0680(↓↓− −↑− − − −) A5A956868 (↓↓↓↑↓− − − −) 00909A864(− −↓−↓↑− −↑) ACA506280(↓−↓↓− −↑− −) 350A50628(−↓−↓↓− −↑ −) |

| 1VIN | C3D0BA864(− −↓−↓↑− −↑) |

| 2VIN | BBD0BA864(↓↑↓−↓↑− −↑) DDD0BA864(↑↓↓−↓↑− −↑) |

| 3VIN | A5D0BA864(↓↓↓−↓↑− −↑) |

| 4VIN | 5D9CBA864(↑↓↓−↓↑− −↑) 3B9CBA864(↓↑↓−↓↑− −↑) BAD39A864(↓↑↓−↓↑− −↑) DCD39A864(↑↓↓−↓↑− −↑) |

| 5VIN | BBB0BA864(↓↑↓−↓↑− −↑) DDB0BA864(↑↓↓−↓↑− −↑) BBD0DA864(↓↑↓−↓↑− −↑ DDD0DA864(↑↓↓−↓↑− −↑) |

| 6VIN | A5D0D8684(↓↓↑−↓− − − −) A5B0B8684(↓↓↓−↑− − − −) 5C9098684(↑−↓−↓− − − −) 3A9098684(−↑↓−↓− − − −) A5B0BA864(↓↓↓−↓↑− −↑) A5D0DA864(↓↓↓−↓↑− −↑) |

| 7VIN | BAD39A804(↓↑↓−↓↑− −↑) DCD39A804(↑↓↓−↓↑− −↑) 5D9CDA864(↑↓↓−↓↑− −↑) 3B9CDA864(↓↑↓−↓↑− −↑) |

| 8VIN | DDB0DA864(↑↓↓−↓↑− −↑) BBB0DA864(↓↑↓−↓↑− −↑) |

| 9VIN | A5B0DA864(↓↓↓−↓↑− −↑) A5B0B8688(↓↓↓−↑− − −↓) A5D0D8688(↓↓↑−↓− − −↓) 5C9094684(↑−↓−↓↓− − −)3A9094684(−↑↓−↓↓− − −) |

| 10VIN | BAB39A808(↓↑↓−↓↑− −) DCB39A808(↑↓↓−↓↑− −↓) 5D9CD4064(↑↓↓−↓↓− −↑) 3B9CD4064(↓↑↓−↓↓− −↑) |

| 11VIN | DDA0D4064(↑↓↓−↓↓− −↑) BBA0D4064(↓↑↓−↓↓− −↑) DDB05A808(↑↓↓−↓↑− −↓) BBB05A808(↓↑↓−↓↑− −↓) |

| 12VIN | 5C9094688(↑−↓−↓↓− −↓) 3A9094688(−↑↓−↓↓− −↓) A5D0D4688(↓↓↑−↓↓− −↓) A5B0B4688(↓↓↓−↑↓− −↓) A5B05A808(↓↓↓−↓↑− −↓) A5A0D4064(↓↓↓−↓↓− −↑) |

| 13VIN | 5D9ABA864(↑↓↓↓↓↑− −↑) 3B9ABAA864(↓↑↓↓↓↑− −↑) BAD59A864(↓↑↓↓↓↑− −↑) DCD59A864(↑↓↓↓↓↑− −↑) |

| 14VIN | 359ABA864(−↓↓↓↓↑− −↑) ACD59A864(↓−↓↓↓↑− −↑) |

| 15VIN | A5A956868(↓↓↓↑↓↓− −↓) 5C999A864(↑−↓↓↓↑− −↑) 3A999A864(−↑↓↓↓↑− −↑) |

| 16VIN | 5D9ADA864(↑↓↓↓↓↑− −↑) BAB59A864(↓↑↓↓↓↑− −↑) |

| 17VIN | 359ADA864(−↓↓↓↓↑− −↑) |

| 18VIN | 5C999A808(↑−↓↓↓↑− −↓) 5C9994064(↑−↓↓↓↓− −↑) 3A999A808(−↑↓↓↓↑− −↓) 3A9994064(−↑↓↓↓↓− −↑) |

| 19VIN | DD30B2464(↑↓− −↓↓↓−↑) DDD0CA8A0(↑↓↓− −↑−↓↓) BB30B2464(↓↑− −↓↓↓−↑) BBD0CA8A0(↓↑↓− −↑−↓↓) |

| 20VIN | ACA596284(↓−↓↓↓↓↑− −) A550D2684(↓↓↑−↓↓↓− −) 359A58628(−↓↓↓↓− −↑↓) A530B2684(↓↓− −↑↓↓− −) 5C9008620(↑−↓− − − −↓↓) 3A9008620(−↑↓− − − −↓↓) |

| 21VIN | 5C9994008(↑−↓↓↓↓− −↓) 3A9994008(−↑↓↓↓↓− −↓) |

| 22VIN | DD30D2464(↑↓− −↓↓↓−↑) BB30D2464(↓↑− −↓↓↓−↑) DDD0CA8A0(↑↓↓− −↑−↓↓) BBD0CA8A0(↓↑↓− −↑−↓↓) |

| 23VIN | ACA596288(↓−↓↓↓↓↑−↓) 359A54628(−↓↓↓↓↓−↑↓) A5D0C46A0(↓↓↑− −↓−↓↓) A550D2688(↓↓↑−↓↓↓−↓) A5B0A46A0(↓↓↓−↑↓−↓↓) A530B2688(↓↓− −↑↓↓−↓) |

| 24VIN | 5D0C52408(↑↓− −↓↓↓−↓) 3B0C52408(↓↑− −↓↓↓−↓) BAA3040A0(↓↑↓− −↓−↓↓) DCA3040A0(↑↓↓− −↓−↓↓) |

| 25VIN | DD3052408(↑↓− −↓↓↓−↓) BB3052408(↓↑− −↓↓↓−↓) DDA0C40A0(↑↓↓− −↓−↓↓) BBA0C40A0(↓↑↓− −↓−↓↓) |

| 26VIN | 5C9094A88(↑−↓−↓↓↓−↓) 3A9094A88(−↑↓−↓↓↓−↓) 5C9094648(↑−↓−↓↓−↓↓) 3A9094648(−↑↓−↓↓−↓↓) |

| 27VIN | 5D0AB2464(↑↓−↓↓↓↓−↑) BAD50A8A0(↓↑↓↓−↑−↓↓) |

| 28VIN | ACD50A8A0(↓−↓↓−↑−↓↓) 350AB2464(−↓−↓↓↓↓−↑) |

| 29VIN | 5C0992404(↑− −↓↓↓↓− −) 3A0992404(−↑−↓↓↓↓− −) 5C99080A0(↑−↓↓− − −↓↓) 3A99080A0(−↑↓↓− − −↓↓) |

| 30VIN | 5D0AD2464(↑↓−↓↓↓↓−↑) 3B0AD2464(−↑−↓↓↓↓−↑) |

| 31VIN | 350AD2464(−↓−↓↓↓↓−↑) ACD50A8A0(↓−↓↓−↑−↓↓) |

| 32VIN | 5C0992408(↑−−↓↓↓↓−↓) 3A0992408(−↑−↓↓↓↓−↓) 5C99040A0(↑−↓↓−↓−↓↓) 3A99040A0(−↑↓↓−↓−↓↓) |

| 33VIN | 35933AA44(−↓↓− −↑↓↓−) ACCC98A64(↓− − −↓−↓↓↑) 5D0A52408(↑↓−↓↓↓↓−↓) BAA5040A0(↓↑↓↓−↓−↓↓) |

| 34VIN | ACA5062A0(↓−↓↓−↓↑↓↓) 350A52628(−↓−↓↓↓↓↑↓) A550C26A0(↓↓↑− −↓↓↓↓) A530A26A0(↓↓− −↑↓↓↓↓) 5C0002220(↑− − − −↓↓↓↓) 3A0002220(−↑ − − −↓↓↓↓) |

| 35VIN | 5D933AA48(↑↓↓− −↑↓↓↓) BACC94A64(↓↑− −↓↓↓↓↑) |

| 36VIN | 35933AA48(−↓↓− −↑↓↓↓) ACCC94A64(↓− − −↓↓↓↓↑) DD30C24A0(↑↓− − −↓↓↓↓) BB30C24A0(↓↑− − −↓↓↓↓) |

| 37VIN | 5C9094A64(↑−↓−↓↓↓↓↑) 3A9094A64(−↑↓−↓↓↓↓↑) |

| 38VIN | BBCC94A48(↓↑− −↓↓↓↓↓) 5D9334A48(↑↓↓− −↓↓↓↓) |

| 39VIN | ACCC94A48(↓− − −↓↓↓↓↓) |

| 40VIN | 5C9094A48(↑−↓−↓↓↓↓↓) 3A9094A48(−↑↓−↓↓↓↓↓) |

| 41VIN | 099352248(−↓↓−↓↓↓↓↓) |

| 42VIN | 359352248(−↓↓−↓↓↓↓↓) |

| 43VIN | 5C09024A0(↑− −↓−↓↓↓↓) 3A09024A0(−↑−↓−↓↓↓↓) |

| 44VIN | 5D0AC24A0(↑↓−↓−↓↓↓↓) BA35024A0(↓↑−↓−↓↓↓↓) |

| 45VIN | AC35024A0(↓− −↓−↓↓↓↓) |

| Topology | Number of Active Switches | Number of Series Diodes | Number of Drivers | Number of Capacitors | Balance Circuit |

|---|---|---|---|---|---|

| Proposed | 0 | No Need | |||

| NPC | Need | ||||

| FC | 0 | Need | |||

| CHB | 0 | Need | |||

| [13] | No Need | ||||

| [15] | 0 | No Need | |||

| [16] | No Need | ||||

| [17] | No Need | ||||

| [18] | No Need | ||||

| [19] | 0 | Need |

| Parameter | Value |

|---|---|

| Input Voltage | 50 Volts |

| Number of Output Voltage levels | 91 |

| Output Frequency | 50 Hz |

| CM1, CM2 | 20,000 μF |

| CM3, CM5 | 1000 μF |

| CM4, CM6, CM7, CM8, CM9 | 100 μF |

| Resistive Load (R) | 100 Ω |

| Inductive-Resistive Load (R-L) | 100 Ω, 318.4 mH |

| Input Voltage | 10 v |

|---|---|

| Number of Output Voltage levels | 91 |

| Output Frequency | 50 HZ |

| CM1, CM2 | 20,000 μF |

| CM3, CM5 | 1000 μF |

| CM4, CM6, CM7, CM8, CM9 | 100 μF |

| Load | 570 Ω |

| Diode | MUR860 |

| IGBT | 12n60a4 |

| Driver | HCPL 3120 |

| Processor | DSP TMS320F28335 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Taghvaie, A.; Alijani, A.; Adabi, M.E.; Rezanejad, M.; Adabi, J.; Rouzbehi, K.; Pouresmaeil, E. An Asymmetrical Step-Up Multilevel Inverter Based on Switched-Capacitor Network. Sustainability 2019, 11, 3453. https://doi.org/10.3390/su11123453

Taghvaie A, Alijani A, Adabi ME, Rezanejad M, Adabi J, Rouzbehi K, Pouresmaeil E. An Asymmetrical Step-Up Multilevel Inverter Based on Switched-Capacitor Network. Sustainability. 2019; 11(12):3453. https://doi.org/10.3390/su11123453

Chicago/Turabian StyleTaghvaie, Amir, Ahmad Alijani, M. Ebrahim Adabi, Mohammad Rezanejad, Jafar Adabi, Kumars Rouzbehi, and Edris Pouresmaeil. 2019. "An Asymmetrical Step-Up Multilevel Inverter Based on Switched-Capacitor Network" Sustainability 11, no. 12: 3453. https://doi.org/10.3390/su11123453

APA StyleTaghvaie, A., Alijani, A., Adabi, M. E., Rezanejad, M., Adabi, J., Rouzbehi, K., & Pouresmaeil, E. (2019). An Asymmetrical Step-Up Multilevel Inverter Based on Switched-Capacitor Network. Sustainability, 11(12), 3453. https://doi.org/10.3390/su11123453