Quantum Circuit-Width Reduction through Parameterisation and Specialisation

Abstract

1. Introduction

1.1. Brief Review of Quantum Computing Essentials

1.1.1. Qubit Representation and Manipulation

1.1.2. Quantum Circuit Model

1.2. Context of Present Work

1.3. Exemplar Circuit: Integer Divider

1.4. Contributions of This Work

- Demonstration of quantum circuit width reduction transformations based on Circuit Parameterisation and Qubit Specialisation for quantum algorithms performing arithmetic operations as part of the computational work;

- Demonstration of the derivation steps used in creating parameterised quantum circuits for quantum arithmetic. The formulation in parameterised form for a quantum comparator and a quantum subtractor are detailed. To the best of the authors’ knowledge, these parameterised circuits have not been considered in the literature before. The derivations detailed here also show how similar parameterisation can be applied to a wider range of arithmetic circuits;

- Analysis of the quantum circuit design of integer dividers in terms of suitability for the proposed quantum circuit width transformations;

- Demonstration how for the quantum divider exemplar the pre-computed and verified comparator and subtractor circuits in parameterised form can be imported into the complete quantum circuit implementation, followed by the automated selection of qubits suitable for specialisation and the automated specialisation for different user-defined inputs;

- Analysis in terms of circuit complexity of specialised quantum integer divider circuits as obtained from the transformation techniques introduced. The correctness of the circuits is verified using a quantum circuit simulator.

2. Data Encoding in Quantum Information

- The motivation for this type of encoding is typically performing quantum arithmetic operations;

- To maintain the property that only a single computational basis state has a non-zero amplitude throughout the computation, the gates in the Quantum Circuit model are limited to quantum equivalents of logic gates (e.g., X as equivalent of and Toffoli as doubly-controlled ). By doing so, the quantum circuit can efficiently be simulated on a classical computer using a logic-based simulator. In such a simulator, n classical bits suffice to represent the state of n qubits. Then, the controlled logic gate operations conditionally flip states between 0 and 1;

- If quantum arithmetic operations are implemented in the quantum circuit model based on the Quantum Fourier Transform [43,44], then efficient simulation using classical logic-based simulation is not possible, since the QFT in the case of quantum arithmetic circuits temporarily moves the encoding approach to amplitude-based encoding, before finally returning an output in computational basis encoding.

- The quantum arithmetic operations in circuit using computational basis encoding considered here can be efficiently simulated on a classical computer using a logic based simulator—these circuits act as classical reversible circuits when not used as part of a larger quantum algorithm;

- As arithmetic blocks which operate in the computational basis are often parts of larger quantum algorithms, quantum circuit simulations often require a full-state vector simulation approach;

- For quantum circuit simulations where the effect of (modeled) quantum errors are included, the full-state vector simulation approach is generally required even for algorithms operating entirely (through computation) with computational basis encoding.

3. Quantum Circuit Simulation

4. Discussion of Key Concepts

- Step 1: For the three most-significant qubits at the top of the circuit, the gate operations in the neighbouring and blocks partially cancel out. Specifically, only two s remain. The with as control and target can then be reduced to a on since in the specialisation shown .

- Step 2: is accounted for by removing the three s where acts as control.

- Step 3: The actions on can be removed by replacing the two Toffoli gates that conditionally change into state and the gate with as target, by a single Toffoli gate with as target and with the same control qubits as the replaced Toffoli gates.

- Step 4: is accounted for first by replacing three s by three s.

- Step 5: The three s resulting from the previous step are then accounted for by modifying the control in two Toffoli gates with as target.

- Step 6: is accounted for by removing as control from the two Toffoli gates with as target and removing the with as target.

- Step 7: The actions on are removed by removing the remaining two s with acting as target. The resulting circuit has no gate operations on the qubits used for specialisation and so this is the final reduced form of the circuit for these values of the specialisation qubits ().

4.1. Issue with Reduction-by-Specialisation

4.2. Our Approach: Reduction by Parameterisation

- First, the original quantum circuit implementation shown in the top half of Figure 6 is replaced with a parameterised subtractor circuit; this causes one of the inputs to the subtractor to be only used as controls and the states of its qubits will remain static throughout the entire subtractor.

- Then a choice is made for the input values of the static qubits and a smaller specialised circuit can be constructed for this choice of input during the static analysis step.

4.3. Reducing Memory Requirement in Full-State Vector Simulation

5. Derivation of Parameterised Comparator Circuits

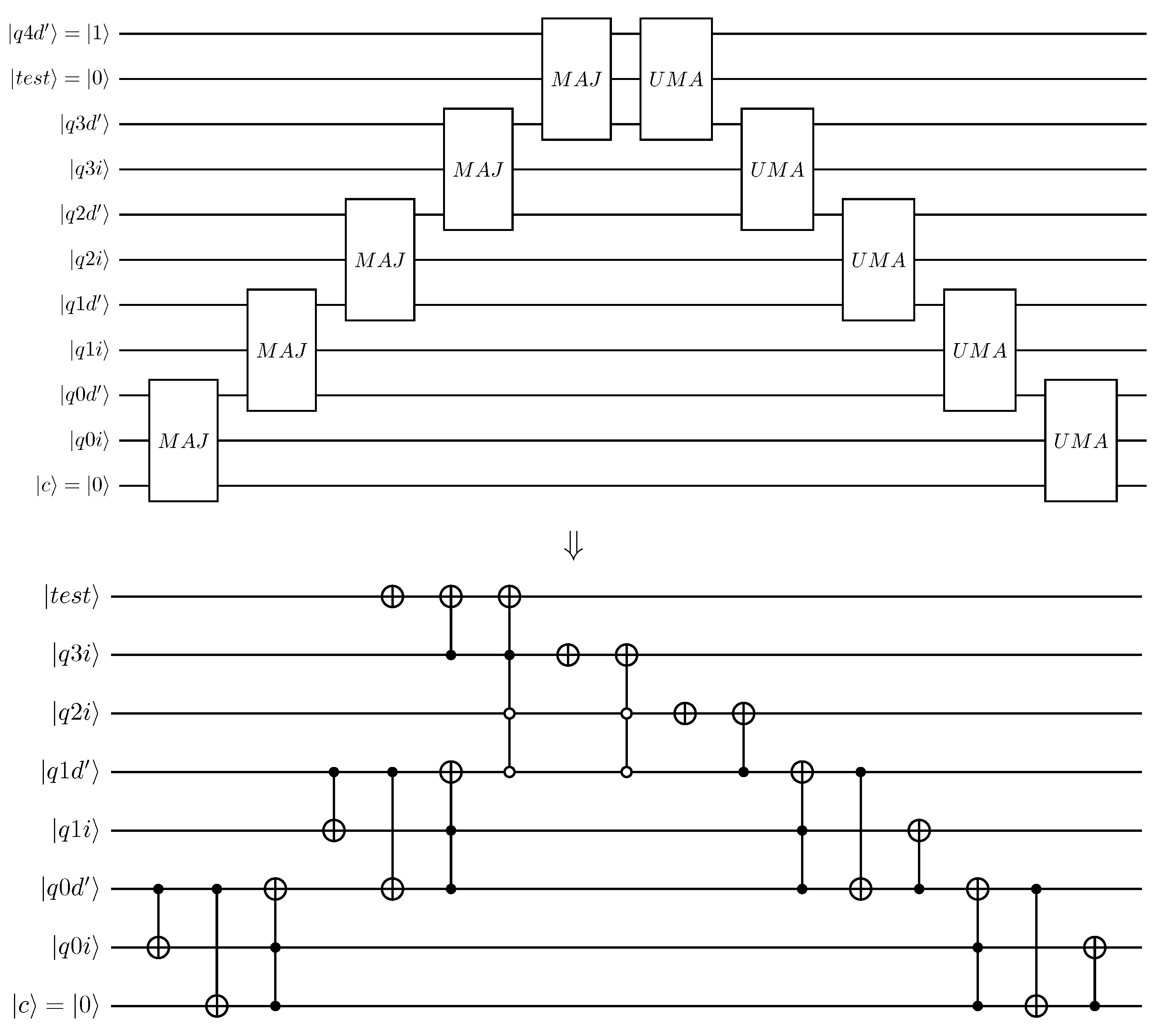

- An -qubit ripple-carry modulo adder of the type introduced by Cuccaro acts as starting point where subtraction of two positive numbers can be achieved by having one of the -qubit inputs represent an n-qubit number in 2’s complement, while the second input will have its leading qubit in state ;

- For a specific choice of the qubits defining the divisor in 2’s complements representation, qubit specialisation steps of the type previously illustrated in Figure 5 for a 3-qubit modulo adder are applied;

- The reduced circuits that result from this process represent a subtraction operation by the integer value represented in negative form by the 2’s complement representation;

- Next, the gate operations in the reduced circuits are sorted in groups, where each group represents gate operations affecting the state of each of the qubits from the second (remaining) input string;

- To create the comparator circuit, the group acting on the most-significant qubit of the input qubit register is selected, while the rest of the gate operations can be ignored;

- The subtractor circuits discussed in Section 6 are similarly created by using the gate operations from each of the groups identified.

5.1. Comparator Circuits for 3-Qubit Divisor

5.2. Comparator Circuits for 4-Qubit Divisor

5.3. Comparator Circuits for 5-Qubit Divisor

6. Derivation of Parameterised Subtractor Circuits

7. Applying Circuit Transformations to a Quantum Integer Divider

7.1. Design 1: Baseline Divider

- In the comparator C and its uncomputation , the state of the divisor qubits can temporarily become changed before returning the their original state;

- The subtractor involves a transformation to 2’s complement formulation for divisor qubits at start and completes with a transformation from 2’s complement to original representation. Along with the further temporary changes to divisor qubit states in the ripple-carry based modulo adder, this greatly complicates static analysis, as outlined previously in Section 4;

- The ‘downward’ movement of subtractor circuit toward less significant qubits of the dividend in successive long-division steps requires re-arrangement of qubits so that the modular addition on which the subtractor is based can be performed. This further complicates qubit-reduction steps.

7.2. Design 2: Dividend Register-Shifting Divider

- The ‘downward’ movement of the comparator (and its uncomputations) and subtraction steps for successive long-division steps have been removed by introducing shift operation that moves the dividend register one step toward more significant qubits. The quantum circuit implementation of this operation, as well as the reverse operation (used in the uncomputation steps), was previously discussed in previous work by the authors [30] and follows the work of Jayashree et al. [38];

- With the changes introduced, the divisor qubits (states) remain in the same position in the qubit register throughout the computation.

7.3. Design 3: Parameterised Divider

- For the comparator C and , the original implementation is replaced by an alternative, parameterised quantum circuit implementation where divisor qubits acts as specialisation parameters;

- For the subtractor , the original implementation is replaced by an alternative, parameterised quantum circuit implementation where divisor qubits acts as specialisation parameters;

- Design 3 also stores divisor qubits directly in 2’s complement representation. The current analysis shows that using this form of the divisor state makes the parameterisation of the comparator and subtractor more compact than with the original form of divisor.

8. Quantum Circuit Toolchain

8.1. Circuit Specification and eDSL

8.2. Static Analysis to Reduce Qubit Count

8.3. Testing and Verification

9. Demonstration of Reduction of Integer Divider

9.1. Parameterised Integer Divider Implementation in Toolchain—Before Circuit Transformation

9.2. Specialised Integer Divider

9.3. Results

9.4. Discussion of Results—Implication for Wider Range of Circuits

10. Conclusions and Future Work

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| QC | Quantum Computing |

| FQT | Functional Quantum Toolchain |

| DSL | Domain Specific Language |

| eDSL | Embedded Domain Specific Language |

References

- Nielsen, M.; Chuang, I. Quantum Computation and Quantum Information: 10th Anniversary Edition; Cambridge University Press: Cambridge, UK, 2010. [Google Scholar]

- Preskill, J. Quantum Computing in the NISQ era and beyond. Quantum 2018, 2, 79. [Google Scholar] [CrossRef]

- IBM unveils 127-qubit computer. Phys. World 2021, 34, 13ii. [CrossRef]

- Gambetta, J. IBM Quantum Roadmap to Build Quantum-Centric Supercomputers. 2022. Available online: https://research.ibm.com/blog/ibm-quantum-roadmap-2025 (accessed on 28 April 2023).

- Guerreschi, G.G.; Hogaboam, J.; Baruffa, F.; Sawaya, N.P.D. Intel Quantum Simulator: A cloud-ready high-performance simulator of quantum circuits. Quantum Sci. Technol. 2020, 5, 34007. [Google Scholar] [CrossRef]

- Childs, A.M.; Schoute, E.; Unsal, C.M. Circuit Transformations for Quantum Architectures. In Proceedings of the TQC 2019, College Park, MD, USA, 3–7 June 2019; Volume 135, pp. 1–24. [Google Scholar] [CrossRef]

- Boixo, S.; Isakov, S.V.; Smelyanskiy, V.N.; Neven, H. Simulation of low-depth quantum circuits as complex undirected graphical models. arXiv 2017, arXiv:1712.05384. [Google Scholar] [CrossRef]

- Chen, J.; Zhang, F.; Huang, C.; Newman, M.; Shi, Y. Classical Simulation of Intermediate-Size Quantum Circuits. arXiv 2018, arXiv:1805.01450. [Google Scholar] [CrossRef]

- Schutski, R.; Lykov, D.; Oseledets, I. Adaptive algorithm for quantum circuit simulation. Phys. Rev. A 2020, 101, 42335. [Google Scholar] [CrossRef]

- Pednault, E.; Gunnels, J.A.; Nannicini, G.; Horesh, L.; Magerlein, T.; Solomonik, E.; Draeger, E.W.; Holland, E.T.; Wisnieff, R. Pareto-Efficient Quantum Circuit Simulation Using Tensor Contraction Deferral. arXiv 2017, arXiv:1710.05867. [Google Scholar] [CrossRef]

- Chen, Z.Y.; Zhou, Q.; Xue, C.; Yang, X.; Guo, G.C.; Guo, G.P. 64-qubit quantum circuit simulation. Sci. Bull. 2018, 63, 964–971. [Google Scholar] [CrossRef]

- Li, R.; Wu, B.; Ying, M.; Sun, X.; Yang, G. Quantum Supremacy Circuit Simulation on Sunway TaihuLight. IEEE Trans. Parallel Distrib. Syst. 2018, 31, 805–816. [Google Scholar] [CrossRef]

- Qiskit Contributors. Qiskit: An Open-source Framework for Quantum Computing; Zenodo: Geneva, Switzerland, 2023. [Google Scholar] [CrossRef]

- Green, A.S.; LeFanu, P.; Ross, N.J.; Selinger, P.; Valiron, B. Quipper: A Scalable Quantum Programming Language. ACM SIGPLAN Not. 2013, 48, 333–342. [Google Scholar]

- Cross, A.W.; Bishop, L.S.; Smolin, J.A.; Gambetta, J.M. Open Quantum Assembly Language. arXiv 2017, arXiv:1707.03429. [Google Scholar]

- Cross, A.W.; Javadi-Abhari, A.; Alexander, T.; de Beaudrap, N.; Bishop, L.S.; Heidel, S.; Ryan, C.A.; Smolin, J.; Gambetta, J.M.; Johnson, B.R. OpenQASM 3: A broader and deeper quantum assembly language. ACM Trans. Quantum Comput. 2021, 3, 12. [Google Scholar] [CrossRef]

- Killoran, N.; Izaac, J.; Quesada, N.; Bergholm, V.; Amy, M.; Weedbrook, C. Strawberry Fields: A Software Platform for Photonic Quantum Computing. Quantum 2019, 3, 129. [Google Scholar] [CrossRef]

- Bergholm, V.; Izaac, J.; Schuld, M.; Gogolin, C.; Ahmed, S.; Ajith, V.; Alam, M.S.; Alonso-Linaje, G.; AkashNarayanan, B.; Asadi, A.; et al. PennyLane: Automatic differentiation of hybrid quantum-classical computations. arXiv 2018, arXiv:quant-ph/1811.04968. [Google Scholar]

- Hooyberghs, J. Q# Language Overview and the Quantum Simulator. In Introducing Microsoft Quantum Computing for Developers; Apress: Berkeley, CA, USA, 2022; pp. 121–167. [Google Scholar] [CrossRef]

- Shor, P. Algorithms for quantum computation: Discrete logarithms and factoring. In Proceedings of the 35th Annual Symposium on Foundations of Computer Science, Santa Fe, NM, USA, 20–22 November 1994; pp. 124–134. [Google Scholar] [CrossRef]

- Partsch, H.; Steinbrüggen, R. Program transformation systems. ACM Comput. Surv. 1983, 15, 199–236. [Google Scholar] [CrossRef]

- Lattner, C.; Amini, M.; Bondhugula, U.; Cohen, A.; Davis, A.; Pienaar, J.; Riddle, R.; Shpeisman, T.; Vasilache, N.; Zinenko, O. MLIR: Scaling compiler infrastructure for domain specific computation. In Proceedings of the 2021 IEEE/ACM International Symposium on Code Generation and Optimization (CGO), Seoul, Republic of Korea, 27 February–3 March 2021; IEEE: Piscataway, NJ, USA, 2021; pp. 2–14. [Google Scholar]

- Bastoul, C.; Cohen, A.; Girbal, S.; Sharma, S.; Temam, O. Putting polyhedral loop transformations to work. In Proceedings of the Languages and Compilers for Parallel Computing: 16th International Workshop (LCPC 2003), College Station, TX, USA, 2–4 October 2003; Springer: Berlin/Heidelberg, Germany, 2004; pp. 209–225. [Google Scholar]

- Vanderbauwhede, W. Making legacy Fortran code type safe through automated program transformation. J. Supercomput. 2022, 78, 2988–3028. [Google Scholar] [CrossRef]

- Todorova, B.; Steijl, R. Quantum Algorithm for the collisionless Boltzmann equation. J. Comp. Phys. 2020, 409, 109347. [Google Scholar] [CrossRef]

- Steijl, R. Quantum Algorithms for Fluid Simulations. In Advances in Quantum Communication and Information Bulnes; Bulnes, F., Ed.; IntechOpen: London, UK, 2020; ISBN 978-1-78-985268-4. [Google Scholar] [CrossRef]

- Budinski, L. Quantum algorithm for the advection–diffusion equation simulated with the lattice Boltzmann method. Quantum Inf. Process. 2021, 20, 57. [Google Scholar] [CrossRef]

- Itani, W.; Succi, S. Analysis of Carleman Linearization of Lattice Boltzmann. Fluids 2022, 7, 24. [Google Scholar] [CrossRef]

- Steijl, R. Quantum algorithms for nonlinear equations in fluid mechanics. In Quantum Computing and Communications; Zhao, Y., Ed.; IntechOpen: London, UK, 2022; ISBN 978-1-83-968133-2. [Google Scholar] [CrossRef]

- Moawad, Y.; Vanderbauwhede, W.; Steijl, R. Investigating hardware acceleration for simulation of CFD quantum circuits. Front. Mech. Eng. 2022, 8. [Google Scholar] [CrossRef]

- Steijl, R. Quantum Circuit Implementation of Multi-Dimensional Non-Linear Lattice Models. Appl. Sci. 2023, 13, 529. [Google Scholar] [CrossRef]

- Overton, M. Numerical Computing with IEEE Floating Point Arithmetic, 1st ed.; SIAM: Philadelphia, PA, USA, 2001. [Google Scholar]

- Xia, H.; Li, H.; Zhang, H.; Liang, Y.; Xin, J. Novel multi-bit quantum comparators and their application in image binarization. Quantum Inf. Process. 2019, 18, 229. [Google Scholar] [CrossRef]

- Shan-zhi, L. Design of Quantum Comparator Based on Extended General Toffoli Gates with Multiple Targets. Comput. Sci. 2012, 39, 302–306. [Google Scholar]

- Vudadha, C.; Phaneendra, P.S.; Sreehari, V.; Ahmed, S.E.; Muthukrishnan, N.M.; Srinivas, M. Design of Prefix-Based Optimal Reversible Comparator. In Proceedings of the 2012 IEEE Computer Society Annual Symposium on VLSI, Amherst, MA, USA, 19–21 August 2012; pp. 201–206. [Google Scholar] [CrossRef]

- Orts, F.; Ortega, G.; Cucura, A.C.; Filatovas, E.; Garzón, E.M. Optimal fault-tolerant quantum comparators for image binarization. J. Supercomput. 2021, 77, 8433–8444. [Google Scholar] [CrossRef]

- Yuan, S.; Gao, S.; Wen, C.; Wang, Y.; Qu, H.; Wang, Y. A novel fault-tolerant quantum divider and its simulation. Quantum Inf. Process. 2022, 21, 182. [Google Scholar] [CrossRef]

- Jayashree, H.; Thapliyal, H.; Arabnia, H.; Agrawal, V. Ancilla-input and garbage-output optimized design of a reversible quantum integer multiplier. J. Supercomput. 2016, 72, 1477–1493. [Google Scholar] [CrossRef]

- Dutta, S.; Bhattacharjee, D.; Chattopadhyay, A. Quantum circuits for Toom-Cook multiplication. Phys. Rev. A 2018, 98, 012311. [Google Scholar] [CrossRef]

- Munoz-Coreas, E.; Thapliyal, H. Quantum Circuit Design of a T-count Optimized Integer Multiplier. IEEE Trans. Comput. 2019, 68, 729–739. [Google Scholar] [CrossRef]

- Orts, F.; Ortega, G.; Filatovas, E.; Garzón, E.M. Implementation of three efficient 4-digit fault-tolerant quantum carry lookahead adders. J. Supercomput. 2022, 78, 13323–13341. [Google Scholar] [CrossRef]

- Gayathri, S.; Kumar, R.; Dhanalakshmi, S.; Dooly, G.; Duraibabu, D.B. T-Count Optimized Quantum Circuit Designs for Single-Precision Floating-Point Division. Electronics 2021, 10, 703. [Google Scholar] [CrossRef]

- Draper, T.G. Addition on a Quantum Computer. arXiv 2000, arXiv:quant-ph/0008033. [Google Scholar] [CrossRef]

- Ruiz-Perez, L.; Garcia-Escartin, J. Quantum arithmetic with the quantum Fourier transform. Quantum Inf. Process. 2017, 16, 152. [Google Scholar] [CrossRef]

- Cuccaro, S.A.; Draper, T.G.; Kutin, S.A.; Moulton, D.P. A new quantum ripple-carry addition circuit. arXiv 2004, arXiv:quant-ph/0410184. [Google Scholar] [CrossRef]

- Moawad, Y.; Vanderbauwhede, W.; Steijl, R. Transformations for accelerator-based quantum circuit simulation in Haskell. arXiv 2022, arXiv:2210.12703. [Google Scholar] [CrossRef]

- Marlow, S. Haskell 2010 Language Report. 2010. Available online: http://www.haskell.org/ (accessed on 28 April 2023).

| Operation | Input | Output | Unpacked |

| (7) | |||

| (7) | |||

| (8) | |||

| (8) | |||

| (8) | |||

| (5) | |||

| (6) | |||

| Operation | Input | Output | Unpacked |

| (7) | |||

| (7) | |||

| (8) | |||

| (8) | |||

| (8) | |||

| (5) | |||

| (6) | |||

| Divider | Comparator | Subtractor | |

|---|---|---|---|

| Baseline Circuit Qubit Count | 17 | 9 | 8 |

| Reduced Circuit Qubit Count | 12 | 5 | 4 |

| Baseline Circuit Gate Count | 674 | 49 | 24 |

| Reduced Gate Count (for divisor (9)) | 252 | 3 | 14 |

| Reduced Gate Count (for divisor (11)) | 296 | 5 | 19 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Moawad, Y.; Vanderbauwhede, W.; Steijl, R. Quantum Circuit-Width Reduction through Parameterisation and Specialisation. Algorithms 2023, 16, 241. https://doi.org/10.3390/a16050241

Moawad Y, Vanderbauwhede W, Steijl R. Quantum Circuit-Width Reduction through Parameterisation and Specialisation. Algorithms. 2023; 16(5):241. https://doi.org/10.3390/a16050241

Chicago/Turabian StyleMoawad, Youssef, Wim Vanderbauwhede, and René Steijl. 2023. "Quantum Circuit-Width Reduction through Parameterisation and Specialisation" Algorithms 16, no. 5: 241. https://doi.org/10.3390/a16050241

APA StyleMoawad, Y., Vanderbauwhede, W., & Steijl, R. (2023). Quantum Circuit-Width Reduction through Parameterisation and Specialisation. Algorithms, 16(5), 241. https://doi.org/10.3390/a16050241