Dual-Step Selective Homoepitaxy of Ge with Low Defect Density and Modulated Strain Based on Optimized Ge/Si Virtual Substrate

Abstract

:1. Introduction

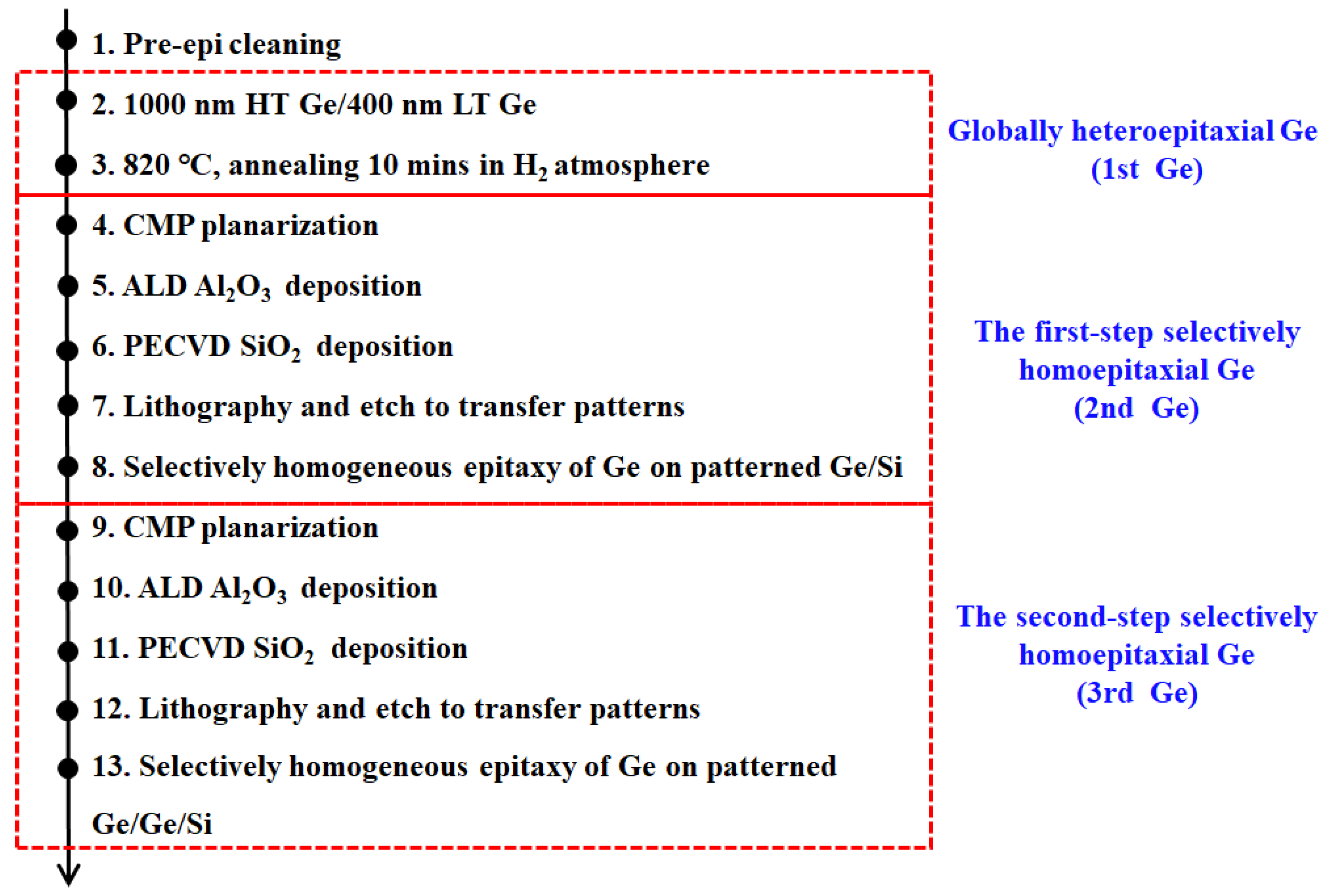

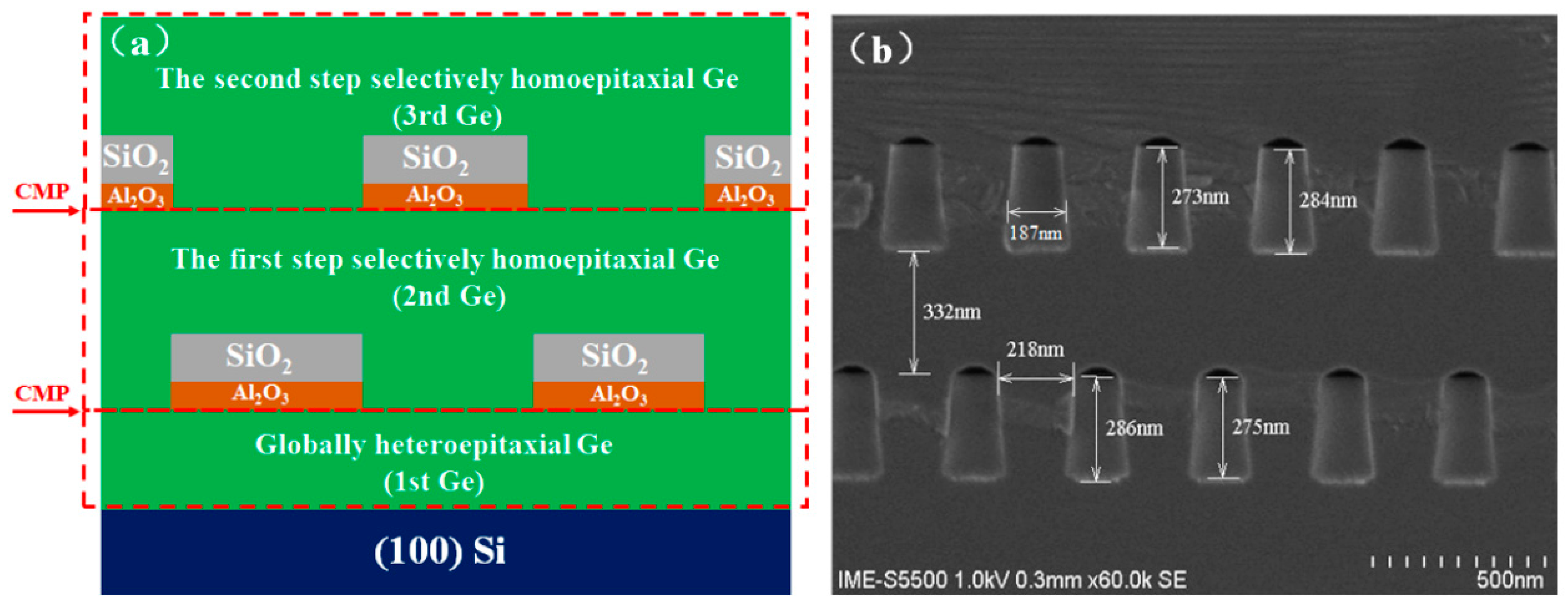

2. Experimental Details

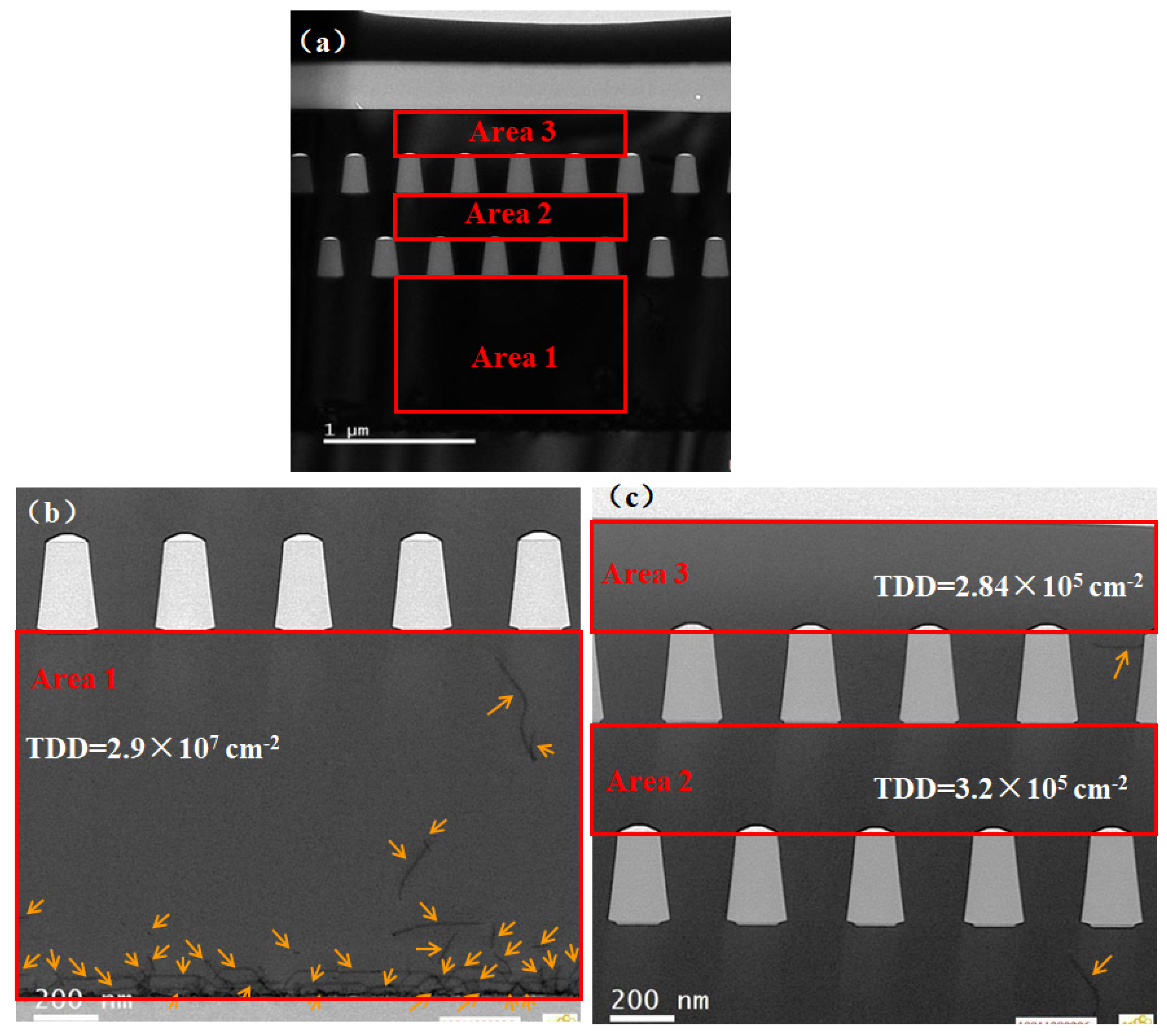

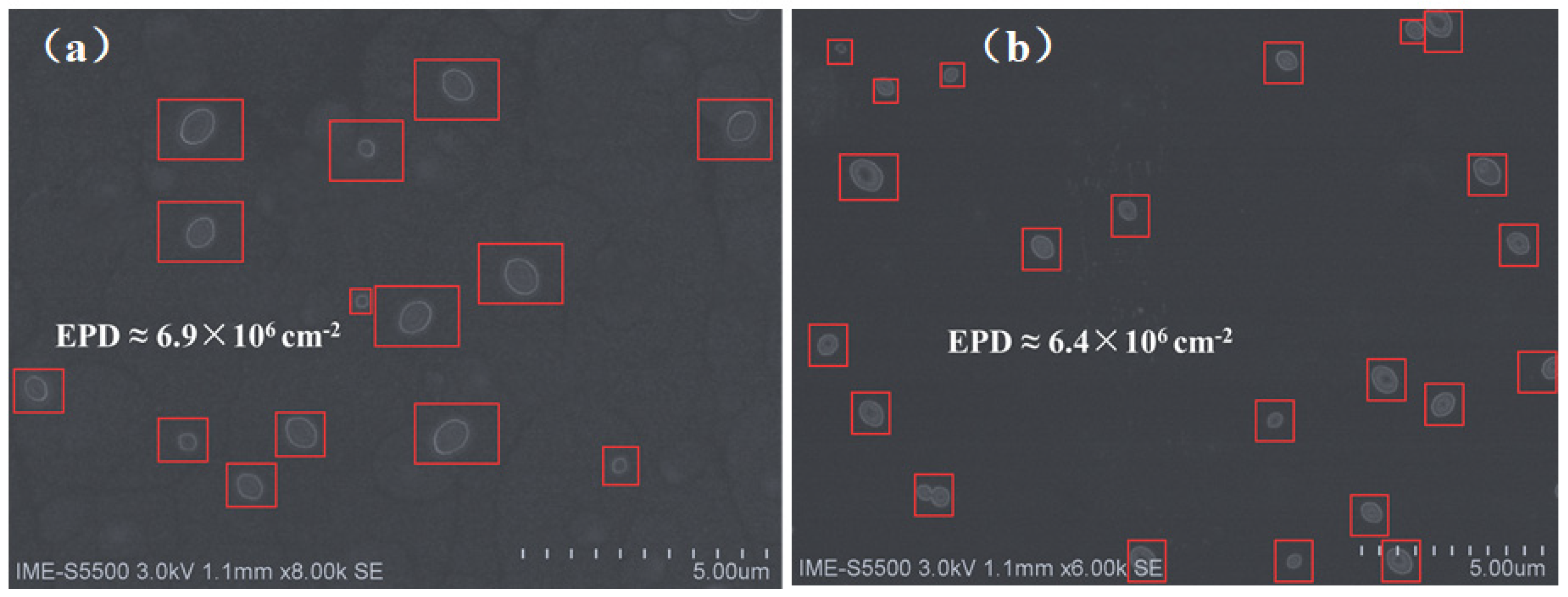

3. Results and Discussion

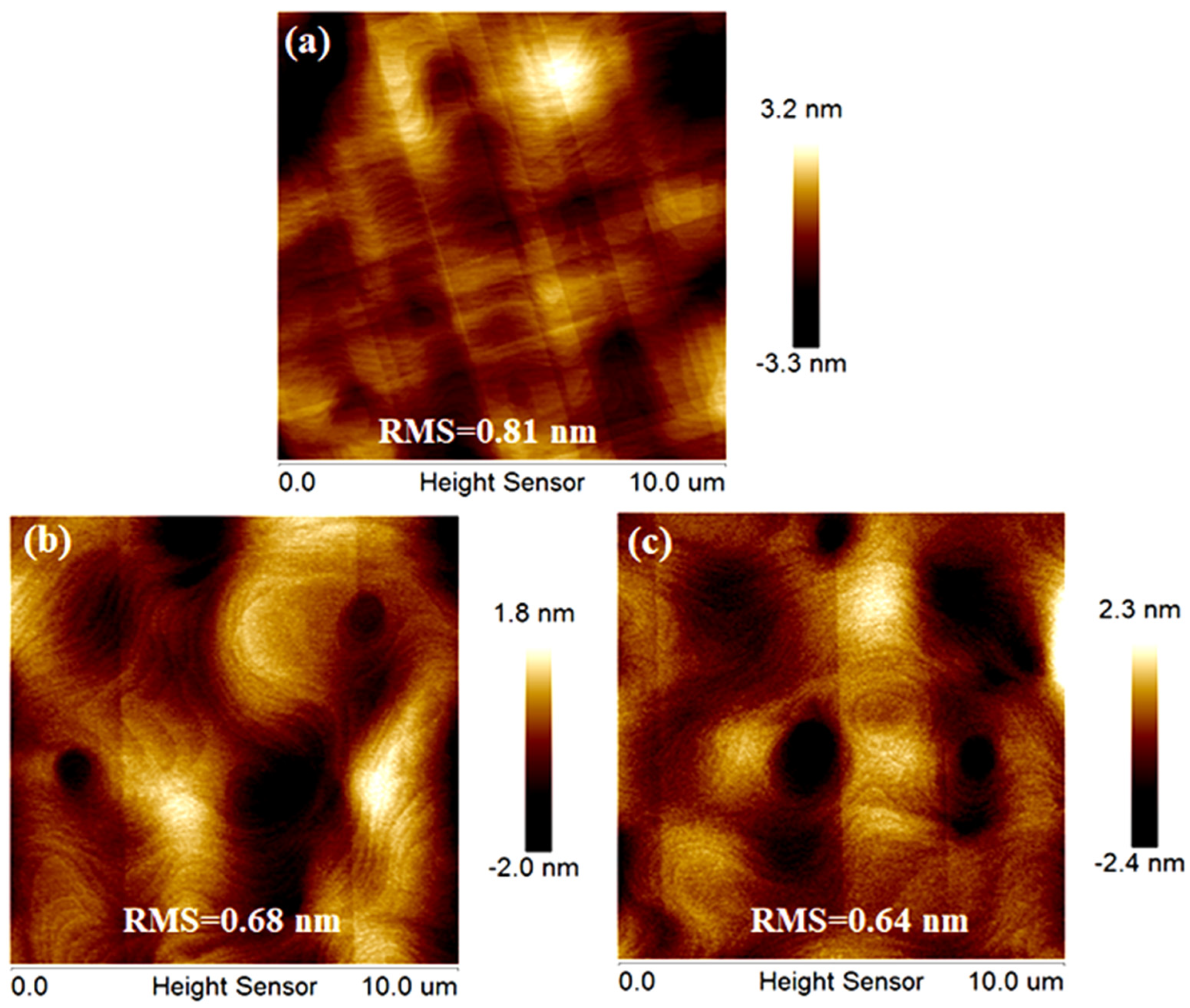

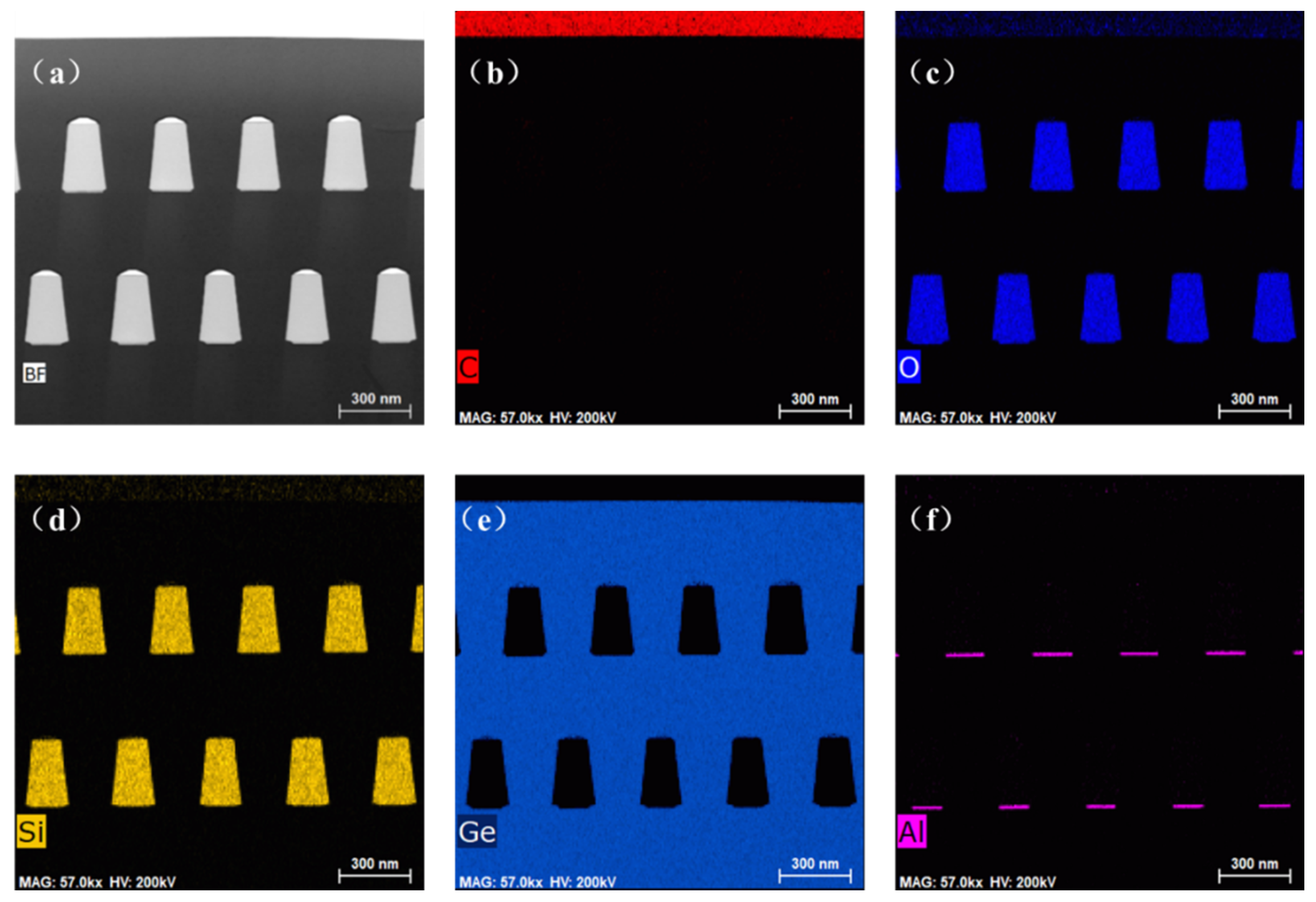

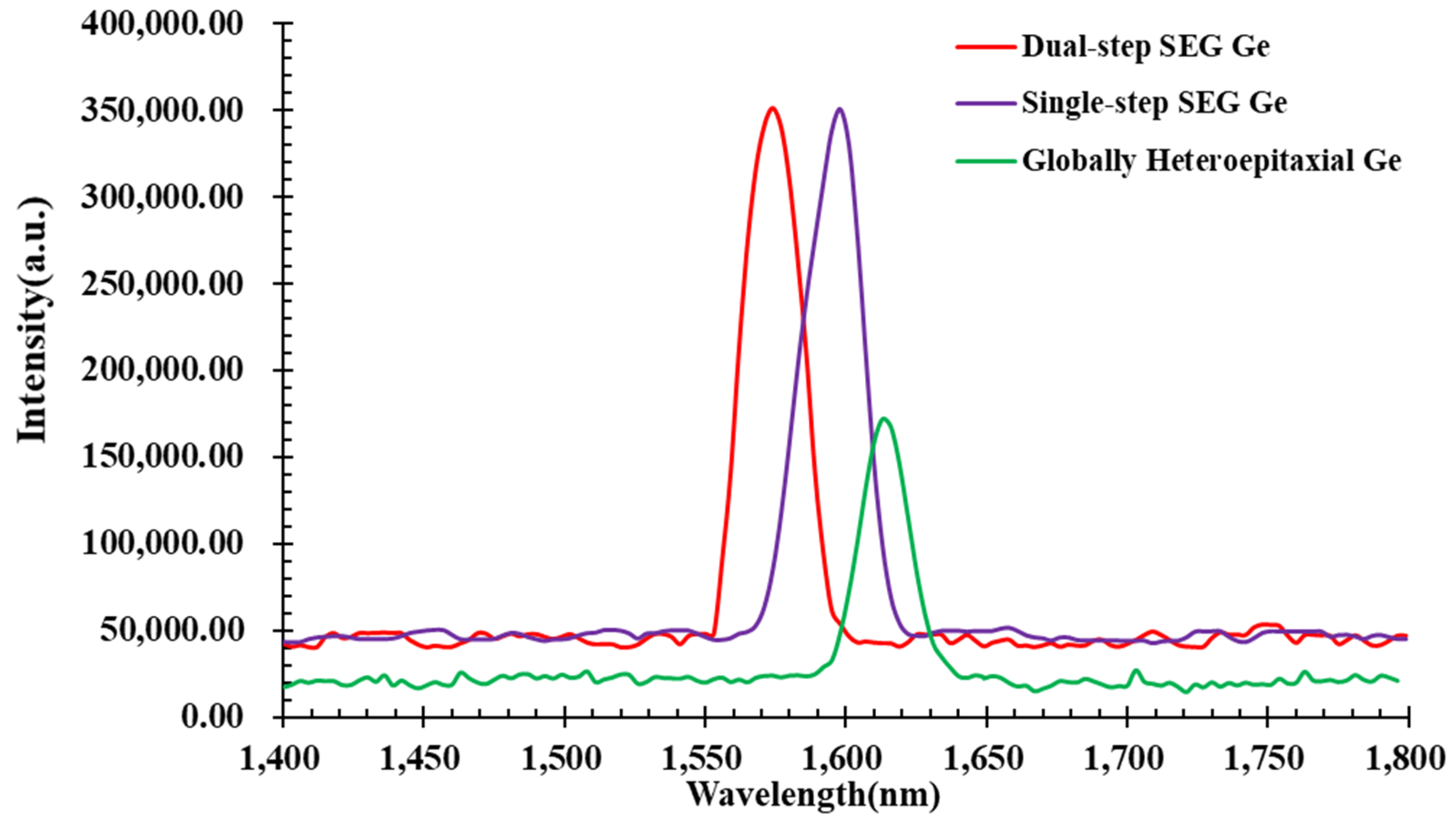

3.1. Film Structure and Morphology

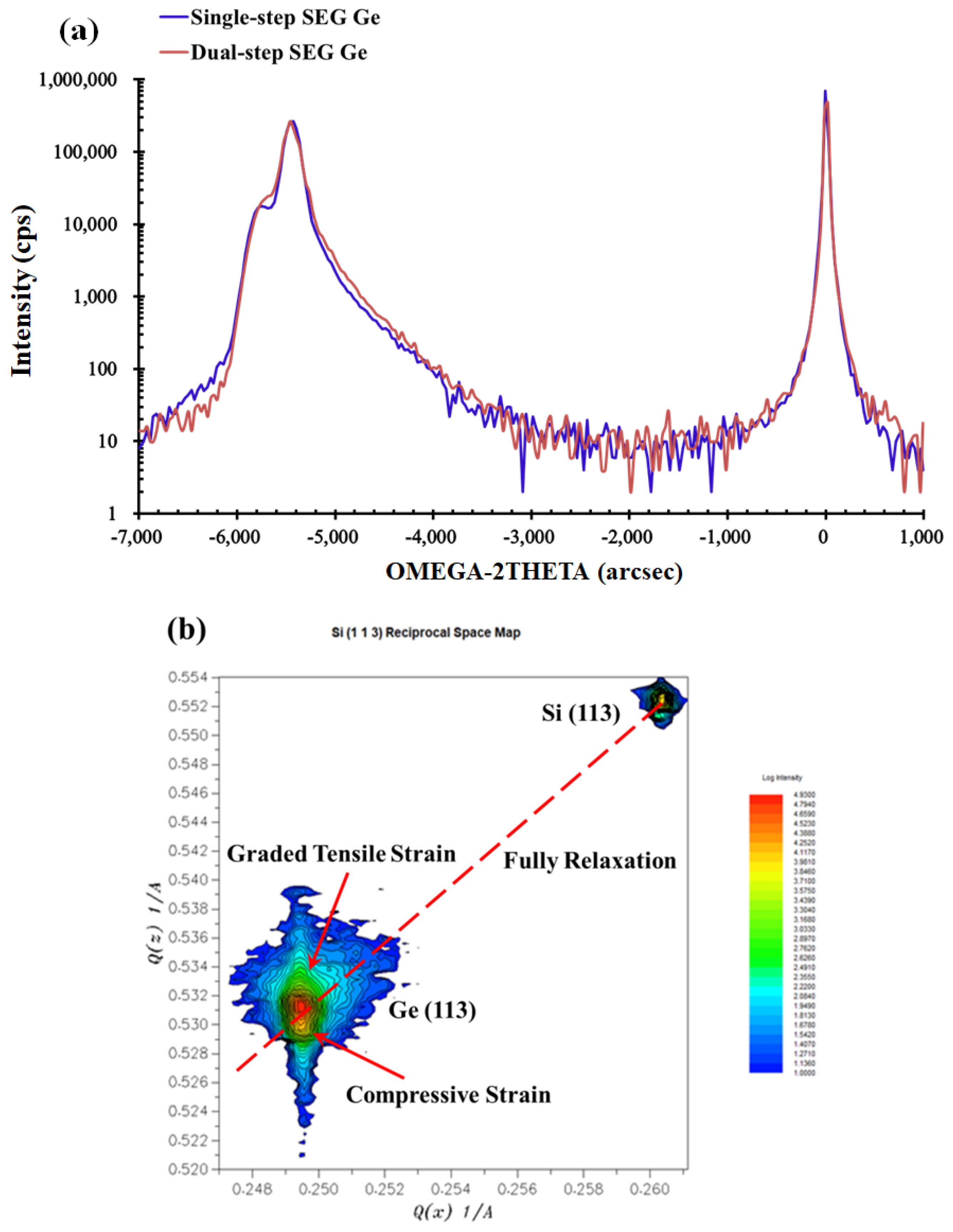

3.2. Strain Characterization

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Sze, S.M.; Ng, K.K. Physics of Semiconductor Devices, 3rd ed.; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2007; ISBN 978-0-471-14323-9. [Google Scholar]

- Yonenaga, I. Single Crystals of Electronic Materials; Woodhead Publishing: Cambridge, UK, 2019; ISBN 978-0-08-102096-8. [Google Scholar]

- Radamson, H.H.; Zhu, H.; Wu, Z.; He, X.; Lin, H.; Liu, J.; Xiang, J.; Kong, Z.; Xiong, W.; Li, J.; et al. State of the Art and Future Perspectives in Advanced CMOS Technology. Nanomaterials 2020, 10, 1555. [Google Scholar] [CrossRef] [PubMed]

- Wang, G.; Kolahdouz, M.; Luo, J.; Qin, C.; Gu, S.; Kong, Z.; Yin, X.; Xiong, W.; Zhao, X.; Liu, J.; et al. Growth of SiGe layers in source and drain regions for 10 nm node complementary metal-oxide semiconductor (CMOS). J. Mater. Sci. Mater. Electron. 2019, 1, 26–33. [Google Scholar] [CrossRef]

- Radamson, H.H.; Kolahdouz, M. Selective epitaxy growth of Si1xGex layers for MOSFETs and FinFETs. J. Mater. Sci. Mater. Electron. 2015, 26, 4584–4603. [Google Scholar] [CrossRef]

- Saraswat, K.; Chui, C.O.; Krishnamohan, T.; Kim, D.; Nayfeh, A.; Pethe, A. High performance germanium MOSFETs. Mater. Sci. Eng. B 2006, 135, 242–249. [Google Scholar] [CrossRef]

- Radamson, H.H.; Luo, J.; Simoen, E.; Zhao, C. CMOS Past, Present and Future; Woodhead Publishing: Cambridge, UK, 2018; ISBN 9780081021392. [Google Scholar]

- Du, Y.; Xu, B.; Wang, G.; Gu, S.; Li, B.; Kong, Z.; Yu, J.; Bai, G.; Li, J.; Wang, W.; et al. Growth of high-quality epitaxy of GaAs on Si with engineered Ge buffer using MOCVD. J. Mater. Sci. Mater. Electron. 2021, 32, 6425–6437. [Google Scholar] [CrossRef]

- Hsieh, Y.D.; Lin, J.H.; Soref, R.; Sun, G.; Cheng, H.H.; Chang, G.E. Electro-absorption modulation in GeSn alloys for wide-spectrum mid-infrared applications. Commun. Mater. 2021, 2, 40. [Google Scholar] [CrossRef]

- Kong, Z.; Wang, G.; Liang, R.; Su, J.; Xun, M.; Miao, Y.; Gu, S.; Li, J.; Cao, K.; Lin, H.; et al. Growth and Strain Modulation of GeSn Alloys for Photonic and Electronic Applications. Nanomaterials 2022, 12, 981. [Google Scholar] [CrossRef]

- Radamson, H.H.; Noroozi, M.; Jamshidi, A.; Thompson, P.E.; Östling, M. Strain engineering in GeSnSi materials. ECS Trans. 2013, 50, 527–531. [Google Scholar] [CrossRef]

- Zhou, H.; Xu, S.; Lin, Y.; Huang, Y.C.; Son, B.; Chen, Q.; Guo, X.; Lee, K.H.; Chun, K.G.; Gong, X.; et al. High-efficiency GeSn/Ge multiple-quantum-well photodetectors with photon-trapping microstructures operating at 2 μm. Opt. Express 2020, 28, 10280–10293. [Google Scholar] [CrossRef]

- Miao, Y.; Wang, G.; Kong, Z.; Xu, B.; Zhao, X.; Luo, X.; Lin, H.; Dong, Y.; Lu, B.; Dong, L.P.; et al. Review of Si-Based GeSn CVD Growth and Optoelectronic Applications. Nanomaterials 2021, 11, 2556. [Google Scholar] [CrossRef]

- Yin, X.; Zhang, Y.; Zhu, H.; Wang, G.; Li, J.; Du, A.; Li, C.; Zhao, L.; Huang, W.; Yang, H.; et al. Vertical Sandwich Gate-All-Around Field-Effect Transistors with Self-Aligned High-k Metal Gates and Small Effective-Gate-Length Variation. IEEE Electron. Device Letters 2019, 41, 8–11. [Google Scholar] [CrossRef]

- Harada, K.; Suzuki, T.; Kusano, T.; Takeshita, K.; Oniki, Y.; Sanchez, E.A.; Struyf, H.; Holsteyns, F. Si1-XGeX Selective Etchant for Gate-All-Around Transistors. Solid State Phenomena 2021, 314, 71–76. [Google Scholar] [CrossRef]

- Li, C.; Zhu, H.; Zhang, Y.; Yin, X.; Jia, K.; Li, J.; Wang, G.; Kong, Z.; Du, A.; Yang, T.; et al. Selective Digital Etching of Silicon-Germanium Using Nitric and Hydrofluoric Acids. ACS Appl. Mater. Interfaces 2020, 12, 48170–48178. [Google Scholar] [CrossRef] [PubMed]

- Zhang, Y.; Ai, X.; Yin, X.; Zhu, H.; Yang, H.; Wang, G.; Li, J.; Du, A.; Li, C.; Huang, W.; et al. Vertical Sandwich GAA FETs with Self-Aligned High-k Metal Gate Made by Quasi Atomic Layer Etching Process. IEEE Trans. Electron. Devices 2021, 68, 2604–2610. [Google Scholar] [CrossRef]

- Zhao, X.W.; Moeen, M.; Toprak, M.S.; Wang, G.; Luo, J.; Ke, X.; Li, Z.; Liu, D.; Wang, W.; Zhao, C.; et al. Design impact on the performance of Ge PIN photodetectors. J. Mater. Sci. Mater. Electron. 2019, 31, 18–25. [Google Scholar] [CrossRef]

- Menon, C.; Lindgren, A.C.; Persson, P.; Hultman, L.; Radamson, H.H. Selective epitaxy of Si1-xGex layers for complementary metal oxide semiconductor applications. J. Electrochem. Soc. 2009, 150, G253–G257. [Google Scholar] [CrossRef]

- Wang, G.; Luo, J.; Qin, C.; Liang, R.; Xu, Y.; Liu, J.; Li, J.; Yin, H.; Yan, J.; Zhu, H.; et al. Integration of Highly Strained SiGe in Source and Drain with HK and MG for 22 nm Bulk PMOS Transistors. Nanoscale Res. Lett. 2017, 12, 123. [Google Scholar] [CrossRef] [Green Version]

- Hallstedt, J.; Kolahdouz, M.; Ghandi, R.; Radamson, H.H.; Wise, R. Pattern dependency in selective epitaxy of B-doped SiGe layers for advanced metal oxide semiconductor field effect transistors. J. Appl. Phys. 2008, 103, 2716. [Google Scholar] [CrossRef]

- Vincent, B.; Witters, L.; Richard, O.; Hikavyy, A.; Bender, H.; Loo, R.; Caymax, M.; Thean, A. Selective growth of strained Ge channel on relaxed SiGe buffer in shallow trench isolation for high mobility Ge planar and Fin p-FET. ECS Trans. 2012, 50, 39–45. [Google Scholar] [CrossRef]

- Hartmann, J.; Clavelier, L.; Jahan, C.; Holliger, P.; Rolland, G.; Billon, T.; Defranoux, C. Selective epitaxial growth of boron- and phosphorus-doped Si and SiGe for raised sources and drains. J. Cryst. Growth 2004, 264, 36–47. [Google Scholar] [CrossRef]

- Kolahdouz, M.; Hallstedt, J.; Khatibi, A.; Östling, M.; Wise, R.; Riley, D.J.; Radamson, H.H. Comprehensive Evaluation and Study of Pattern Dependency Behavior in Selective Epitaxial Growth of B-Doped SiGe Layers. IEEE Trans. Nanotechnol. 2009, 8, 291–297. [Google Scholar] [CrossRef]

- Radamson, H.H.; Hallstedt, J.; Suvar, E.; Menon, C.; Östling, M. Improvement in epitaxial quality of selectively grown Si1-XGeX layers with low pattern sensitivity for CMOS applications. Mater. Sci. Semicond. Process. 2005, 8, 25–30. [Google Scholar] [CrossRef]

- Hartmann, J.M.; Bertin, F.; Rolland, G.; Laugier, F.; Séméria, M. Selective epitaxial growth of Si and SiGe for metal oxide semiconductor transistors. J. Crystal Growth 2003, 259, 419–427. [Google Scholar] [CrossRef]

- Kolahdouz, M.; Hallstedt, J.; Ostling, M.; Wise, R.; Radamson, H.H. Selective Epitaxial Growth with Full Control of Pattern Dependency Behavior for pMOSFET Structures. J. Electrochem. Soc. 2009, 156, H169–H171. [Google Scholar] [CrossRef]

- Ye, H.; Yu, J. Germanium epitaxy on silicon. Sci. Technol. Adv. Mater. 2014, 15, 024601. [Google Scholar] [CrossRef] [Green Version]

- Berbezier, I.; Gallas, B.; Ronda, A.; Derrien, J. Dependence of SiGe growth instability on Si substrate orientation. Surf. Sci. 1998, 412–413, 415–429. [Google Scholar] [CrossRef]

- Bioud, Y.A.; Boucherif, A.; Patriarche, G.; Drouin, D.; Arès, R. Capturing the Effects of Free Surfaces on Threading Dislocation Density Reduction. ECS Trans. 2020, 98, 527–532. [Google Scholar] [CrossRef]

- Kasper, E.; Herzog, H.J.; Kibbel, H. A one-dimensional SiGe superlattice grown by UHV epitaxy. Appl. Phys. 1975, 8, 199–205. [Google Scholar] [CrossRef]

- Yoon, T.S.; Liu, J.; Noori, A.M.; Goorsky, M.S.; Xie, Y.H. Surface roughness and dislocation distribution in compositionally graded relaxed SiGe buffer layer with inserted-strained Si layers. Appl. Phys. Lett. 2005, 87, 12104. [Google Scholar] [CrossRef]

- Wang, G.; Abedin, A.; Moeen, M.; Kolahdouz, M.; Luo, J.; Guo, Y.; Chen, T.; Yin, H.X.; Zhu, H.; Li, J.; et al. Integration of highly-strained SiGe materials in 14nm and beyond nodes FinFET technology. Solid-State Electron. 2015, 103, 222–228. [Google Scholar] [CrossRef]

- Yamamoto, Y.; Corley, C.; Schubert, M.A.; Zoellner, M.; Tillack, B. Threading Dislocation Reduction of Ge by Introducing a SiGe/Ge Superlattice. ECS J. Solid State Sci. Technol. 2021, 10, 034005. [Google Scholar] [CrossRef]

- Bogumilowicz, Y.; Hartmann, J.M.; Di Nardo, C.; Holiiger, P.; Papon, A.M.; Rolland, G.; Billon, T. High-temperature growth of very high germanium content SiGe virtual substrates. J. Cryst. Growth 2006, 290, 523–531. [Google Scholar] [CrossRef]

- Hartmann, J.; Aubin, J. Assessment of the growth/etch back technique for the production of Ge strain-relaxed buffers on Si. J. Cryst. Growth 2018, 488, 43–50. [Google Scholar] [CrossRef]

- Yamamoto, Y.; Zaumseil, P.; Schubert, M.A.; Tillack, B. Influence of annealing conditions on threading dislocation density in Ge deposited on Si by reduced pressure chemical vapor deposition. Semicond. Sci. Technol. 2018, 33, 124007. [Google Scholar] [CrossRef]

- Lee, S.; Son, Y.H.; Park, Y.; Hwang, K.; Shin, Y.G.; Yoon, E. Ge surface-energy-driven secondary grain growth via two-step annealing. Thin Solid Film 2014, 571, 108–113. [Google Scholar] [CrossRef]

- Singha, R.K.; Das, S.; Majumdar, S.; Das, K.; Ray, S.K. Evolution of strain and composition of Ge islands on Si (001) grown by molecular beam epitaxy during postgrowth annealing. J. Appl. Phys. 2008, 103, 114301. [Google Scholar] [CrossRef]

- Lee, K.H.; Bao, S.; Wang, B.; Wang, C.; Yoon, S.F.; Michel, J.; Fitzgerald, E.A.; Tan, C.S. Reduction of threading dislocation density in Ge/Si using a heavily As-doped Ge seed layer. AIP Adv. 2016, 6, 025028. [Google Scholar] [CrossRef]

- Yu, H.-Y.; Park, J.-H.; Okyay, A.K.; Saraswat, K.C. Selective-Area High-Quality Germanium Growth for Monolithic Integrated Optoelectronics. IEEE Electron. Device Lett. 2012, 33, 579–581. [Google Scholar] [CrossRef] [Green Version]

- Loo, R.; Wang, G.; Souriau, L.; Lin, J.C.; Takeuchi, S.; Brammertz, G.; Caymax, M. Epitaxial Ge on standard STI patterned Si wafers: High quality virtual substrates for Ge pMOS and III/V nMOS. ECS Trans. 2009, 25, 335–350. [Google Scholar] [CrossRef]

- Du, Y.; Kong, Z.; Toprak, M.S.; Wang, G.; Miao, Y.; Xu, B.; Yu, J.; Li, B.; Lin, H.; Han, J.; et al. Investigation of the Heteroepitaxial Process Optimization of Ge Layers on Si (001) by RPCVD. Nanomaterials 2021, 11, 928. [Google Scholar] [CrossRef]

- Du, Y.; Wang, G.; Miao, Y.; Xu, B.; Li, B.; Kong, Z.; Yu, J.; Zhao, X.; Lin, H.; Su, J.; et al. Strain Modulation of Selectively and/or Globally Grown Ge Layers. Nanomaterials 2021, 11, 1421. [Google Scholar] [CrossRef] [PubMed]

- Radamson, H.H.; Joelsson, K.B.; Ni, W.X.; Hultman, L.; Hansson, G.V. Characterization of highly boron-doped Si, Si1-xGex and Ge layers by high-resolution transmission electron microscopy. J. Cryst. Growth 1995, 157, 80–84. [Google Scholar] [CrossRef]

- McMahon, W.E.; Vaisman, M.; Zimmerman, J.D.; Tamboli, A.C.; Warren, E.L. Perspective: Fundamentals of coalescence-related dislocations, applied to selective-area growth and other epitaxial films. APL Mater. 2018, 6, 120903. [Google Scholar] [CrossRef]

- Yako, M.; Ishikawa, Y.; Abe, E.; Wada, K. Defects and their reduction in Ge selective epitaxy and coalescence layer on Si with semicylindrical voids on SiO2 masks. IEEE J. Sel. Top. Quantum Electron. 2018, 24, 1. [Google Scholar] [CrossRef]

- Vanamu, G.; Datye, A.K.; Zaidi, S.H. Ge growth on nanostructured silicon surfaces. MRS Proc. 2005, 862, A2.6. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xu, B.; Du, Y.; Wang, G.; Xiong, W.; Kong, Z.; Zhao, X.; Miao, Y.; Wang, Y.; Lin, H.; Su, J.; et al. Dual-Step Selective Homoepitaxy of Ge with Low Defect Density and Modulated Strain Based on Optimized Ge/Si Virtual Substrate. Materials 2022, 15, 3594. https://doi.org/10.3390/ma15103594

Xu B, Du Y, Wang G, Xiong W, Kong Z, Zhao X, Miao Y, Wang Y, Lin H, Su J, et al. Dual-Step Selective Homoepitaxy of Ge with Low Defect Density and Modulated Strain Based on Optimized Ge/Si Virtual Substrate. Materials. 2022; 15(10):3594. https://doi.org/10.3390/ma15103594

Chicago/Turabian StyleXu, Buqing, Yong Du, Guilei Wang, Wenjuan Xiong, Zhenzhen Kong, Xuewei Zhao, Yuanhao Miao, Yijie Wang, Hongxiao Lin, Jiale Su, and et al. 2022. "Dual-Step Selective Homoepitaxy of Ge with Low Defect Density and Modulated Strain Based on Optimized Ge/Si Virtual Substrate" Materials 15, no. 10: 3594. https://doi.org/10.3390/ma15103594

APA StyleXu, B., Du, Y., Wang, G., Xiong, W., Kong, Z., Zhao, X., Miao, Y., Wang, Y., Lin, H., Su, J., Li, B., Wu, Y., & Radamson, H. H. (2022). Dual-Step Selective Homoepitaxy of Ge with Low Defect Density and Modulated Strain Based on Optimized Ge/Si Virtual Substrate. Materials, 15(10), 3594. https://doi.org/10.3390/ma15103594