4H-SiC Double Trench MOSFET with Split Heterojunction Gate for Improving Switching Characteristics

Abstract

:1. Introduction

2. Proposed Device Structures

3. Results and Discussion

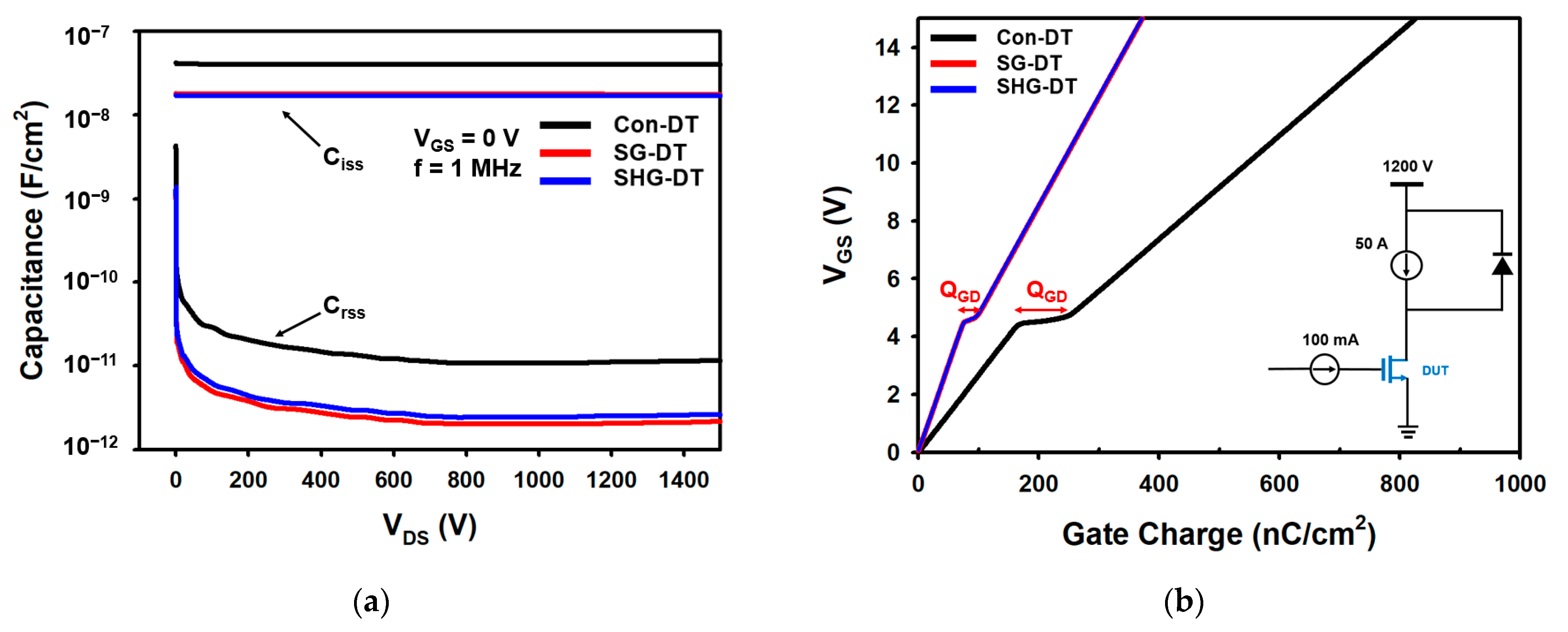

3.1. Static and Dynamic Characteristics

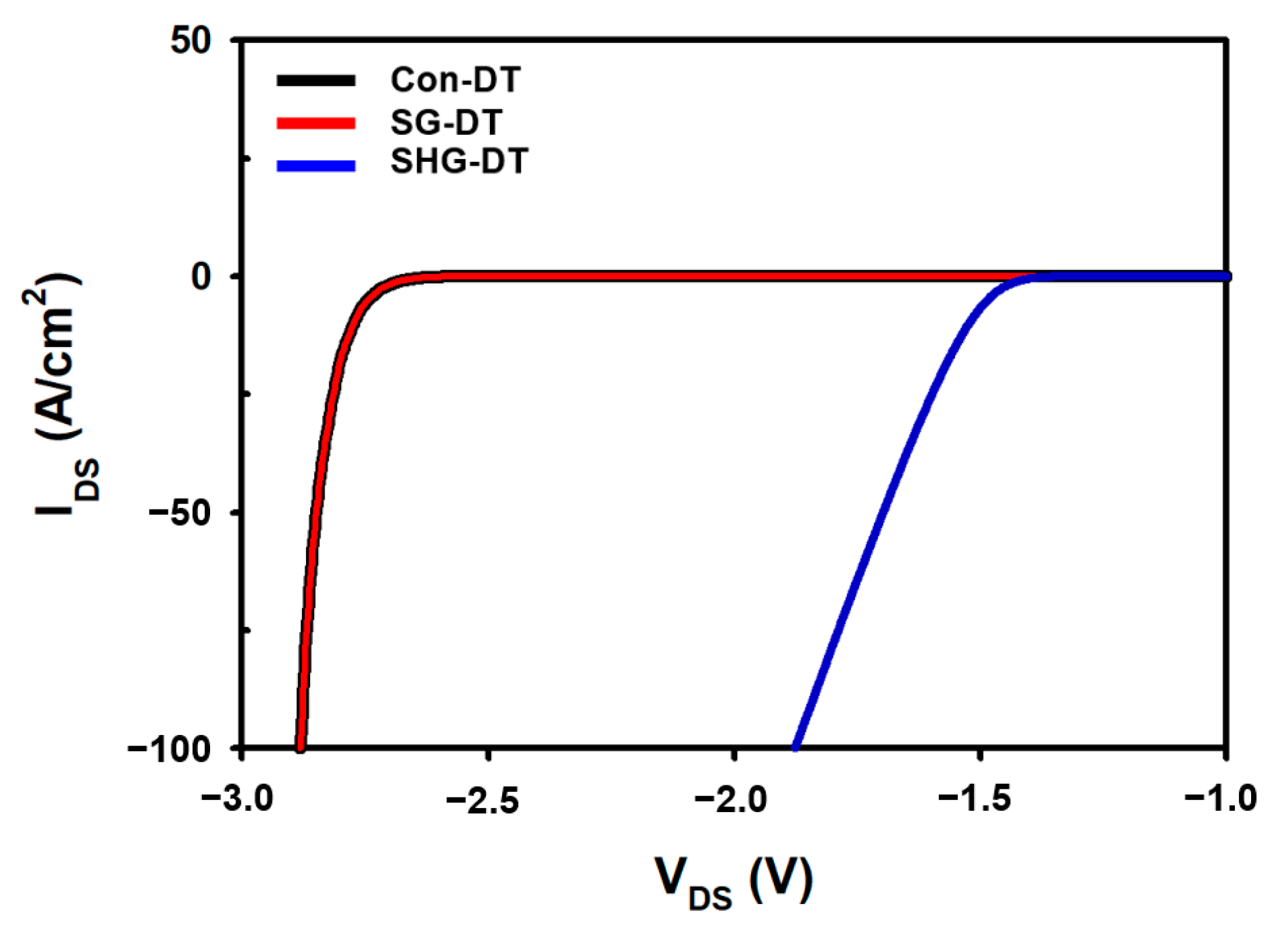

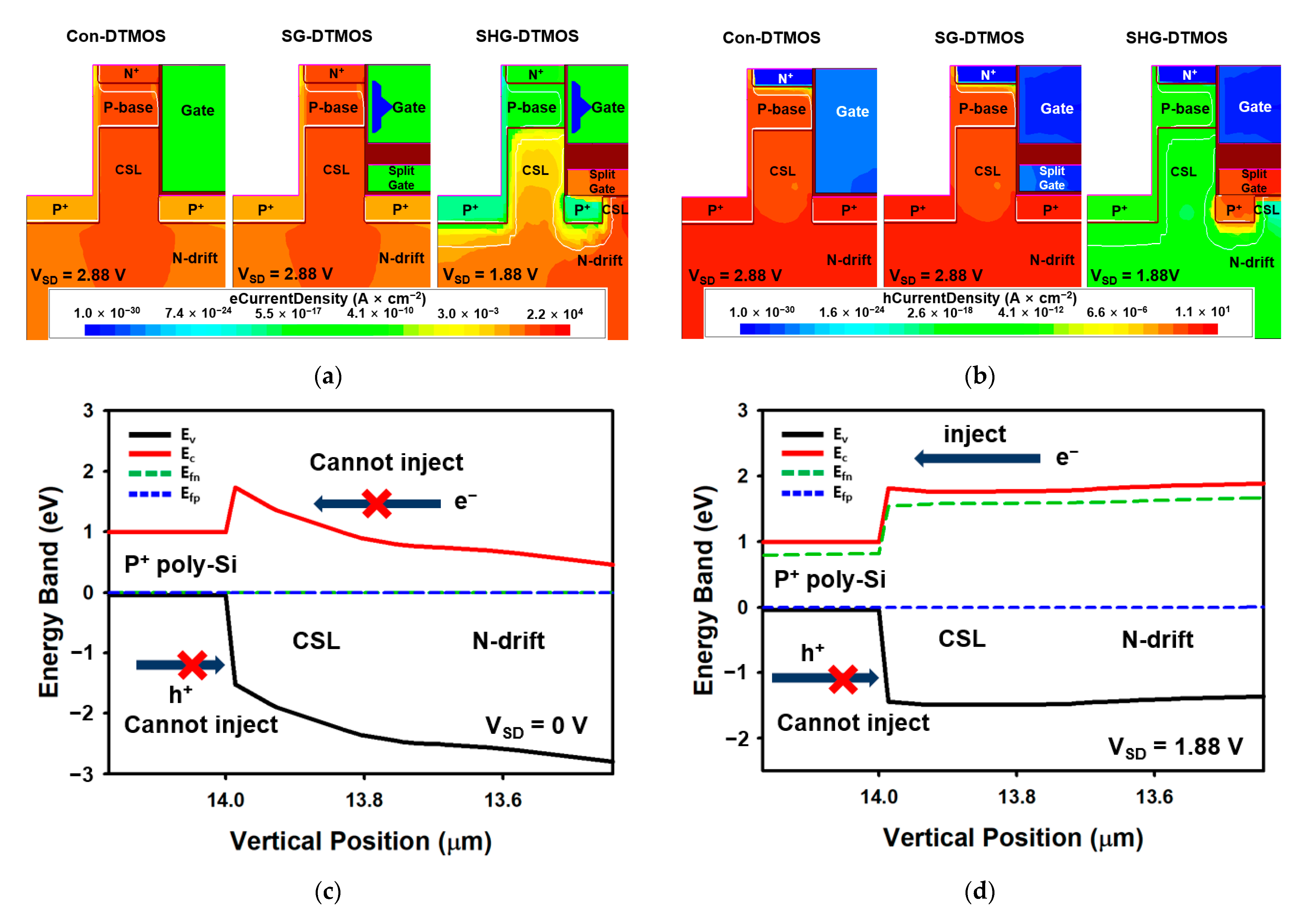

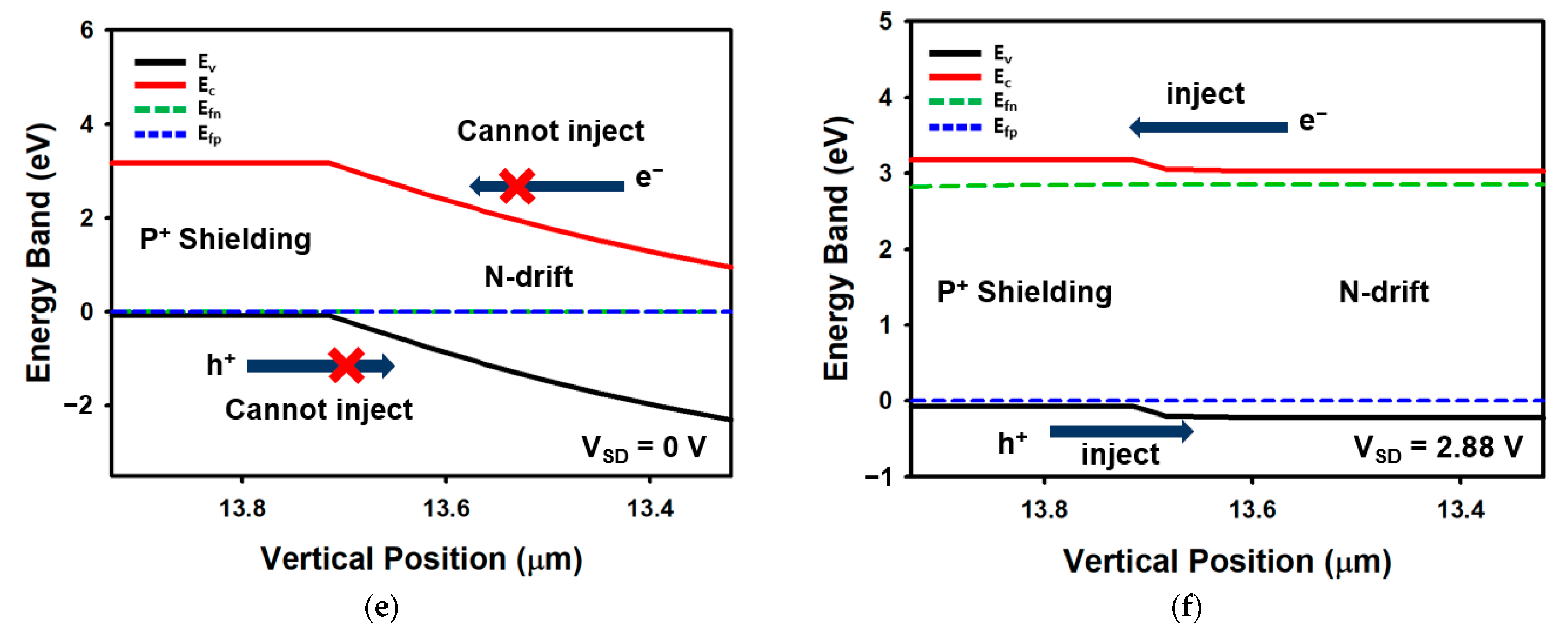

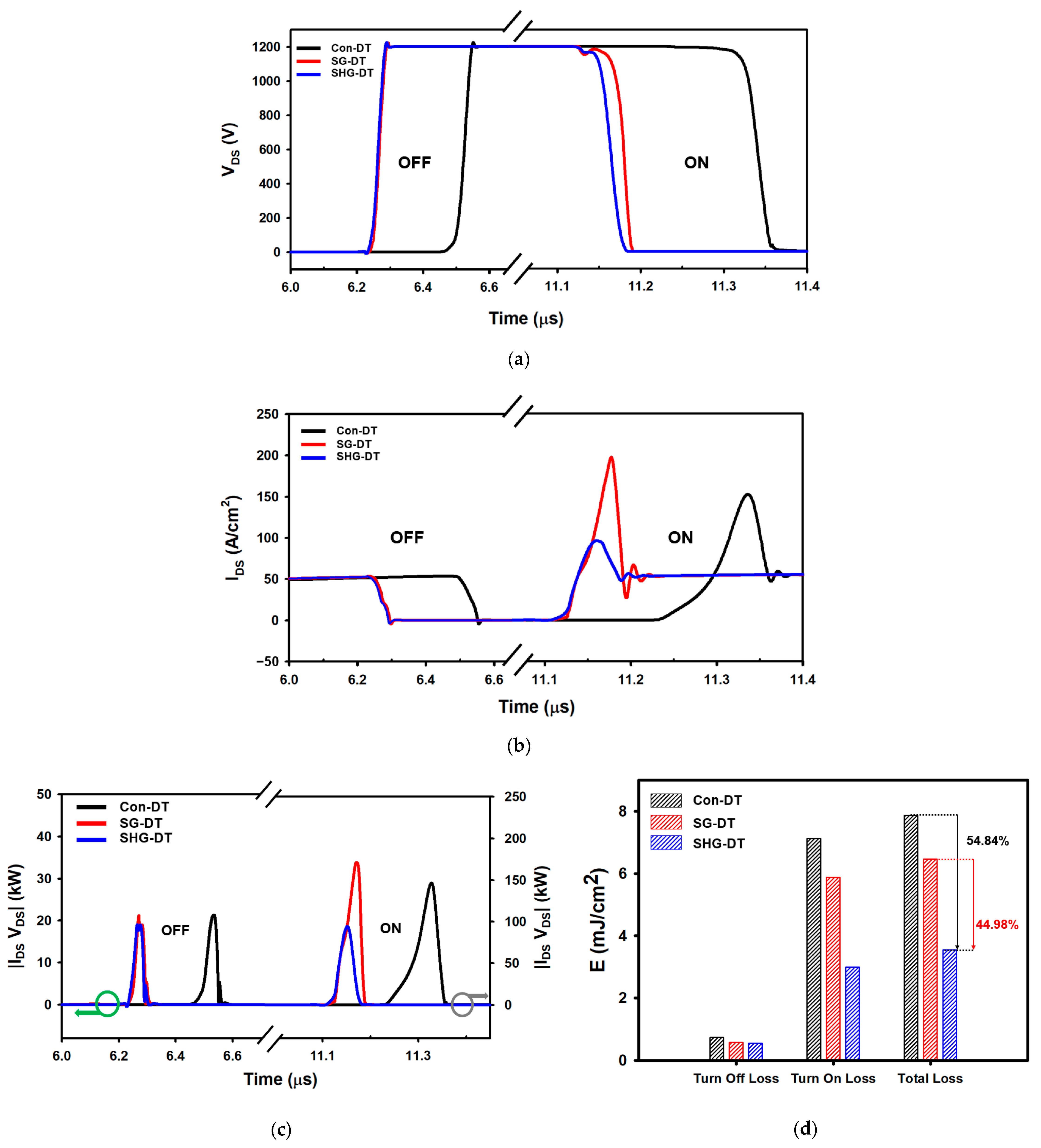

3.2. Body Diode and Switching Characteristics

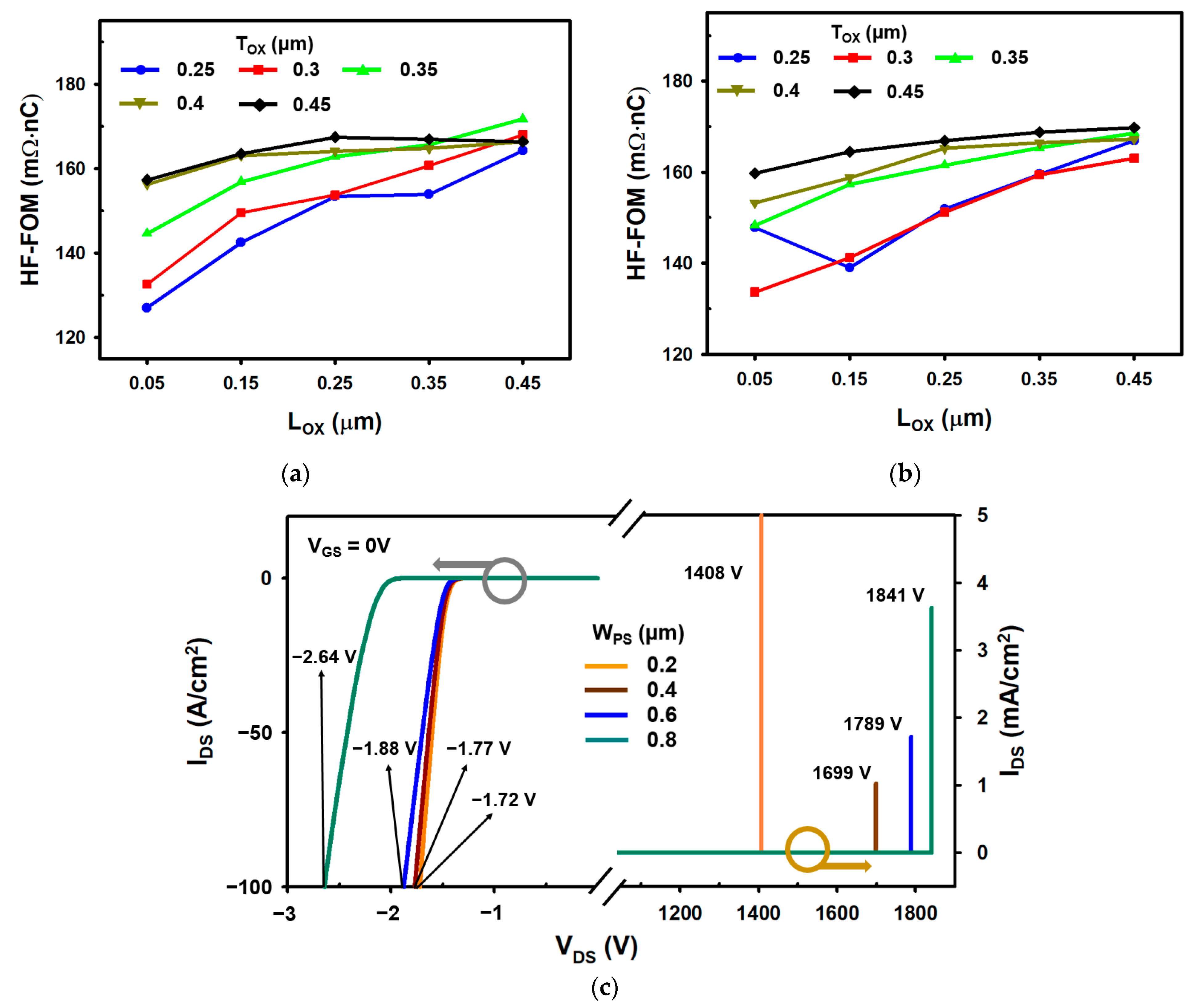

3.3. Optimization and Proposed Fabrication Process

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Paul, T. Wide bandgap semiconductor power devices for energy efficient systems. In Proceedings of the 2015 IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Blacksburg, VA, USA, 2–4 November 2015; pp. 402–405. [Google Scholar] [CrossRef]

- Cooper, J.-A.; Agarwal, A. SiC power-switching devices-the second electronics revolution? Proc. IEEE 2002, 90, 956–968. [Google Scholar] [CrossRef]

- Wiliams, R.-K.; Darwidh, M.-N.; Blanchard, R.-A.; Siemieniec, R.; Rutter, P.; Kawaguchi, Y. The Trench Power MOSFET: Part 1-History, technology, and Prospects. IEEE Trans. Electron Devices 2017, 64, 674–691. [Google Scholar] [CrossRef]

- Goh, J.; Kim, K. Low on-resistance 4H-SiC UMOSFET with local floating superjunction. J. Comput. Electron. 2020, 19, 234–241. [Google Scholar] [CrossRef]

- Cheon, J.; Kim, K. Numerical Simulation Analysis of Switching Characteristics in the Source-Trench MOSFET’s. Electronics 2020, 9, 1895. [Google Scholar] [CrossRef]

- Harada, S.; Kato, M.; Okumura, H. Determination of optimum structure of 4H-SiC Trench MOSFET. In Proceedings of the 2012 24th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Bruges, Belgium, 4–7 June 2012; pp. 253–256. [Google Scholar] [CrossRef]

- Jiang, J.; Huang, C.; Wu, T.; Zhao, F. Simulation Study of 4H-SiC Trench MOSFETs with Various Gate Structures. In Proceedings of the 2019 Electron Devices Technology and Manufacturing Conference (EDTM), Singapore, 12–15 March 2019; pp. 401–403. [Google Scholar] [CrossRef]

- Luo, X.; Liao, T.; Wei, J.; Fang, J.; Yang, F.; Zhang, B. A novel 4H-SiC trench MOSFET with double shielding structures and ultralow gate-drain charge. J. Semicond. 2019, 40, 052803. [Google Scholar] [CrossRef]

- Li, X.; Tong, X.; Huang, A.; Qiu, S.; She, X.; Deng, X.; Zhang, B. Shielded Gate SiC Trench Power MOSFET with Ultra-Low Switching Loss. Mater. Sci. Forum 2018, 924, 765–769. [Google Scholar] [CrossRef]

- Yin, S.; Liu, Y.; Tseng, K.; Pou, J.; Simanjorang, R. Comparison of SiC Voltage Source Inverters Using Synchronous Rectification and Freewheeling Diode. IEEE Trans. Ind. Electron. 2018, 65, 1051–1061. [Google Scholar] [CrossRef]

- Horff, R.; März, A.; Lechler, M.; Bakran, M. Optimised switching of a SiC MOSFET in a VSI using the body diode and additional Schottky barrier diode. In Proceedings of the 2015 17th European Conference on Power Electronics and Applications (EPE’15 ECCE-Europe), Geneva, Switzerlans, 8–10 September 2015; pp. 1–11. [Google Scholar] [CrossRef]

- Jiang, X.; Wang, J.; Li, Z.; Zhai, D.; Yang, X.; Ji, B.; Shen, Z. Investigation on Degradation of SiC MOSFET Under Surge Current Stress of Body Diode. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 77–89. [Google Scholar] [CrossRef]

- Li, X.; Tong, X.; Huang, A.; Tao, H.; Zhou, K.; Jiang, Y.; Jiang, J.; She, X.; Zhang, B.; Zhang, Y.; et al. SiC Trench MOSFET With Integrated Self-Assembled Three-Level Protection Schottky Barrier Diode. IEEE Trans. Electron. Devices 2018, 65, 347–351. [Google Scholar] [CrossRef]

- Kim, J.; Kim, K. 4H-SiC Double-Trench MOSFET with Side Wall Heterojunction Diode for Enhanced Reverse Recovery Performance. Energies 2020, 13, 4602. [Google Scholar] [CrossRef]

- An, J.; Hu, S. Heterojunction Diode Shielded SiC Split-Gate Trench MOSFET with Optimized Reverse Recovery Characteristic and Low Switching Loss. IEEE Access 2019, 7, 28592–28596. [Google Scholar] [CrossRef]

- Wang, Y.; Ma, Y.; Hao, Y.; Hu, Y.; Wang, G.; Cao, F. Simulation Study of 4H-SiC UMOSFET Structure With p+-polySi/SiC Shielded Region. IEEE Trans. Electron Devices 2017, 64, 3719–3724. [Google Scholar] [CrossRef]

- Okuto, Y.; Crowell, C.-R. Threshold energy effect on avalanche breakdown voltage in semiconductor junctions. Solid State Electron 1975, 18, 161–168. [Google Scholar] [CrossRef]

- Lombardi, C.; Manzini, S.; Saporito, A.; Vanzi, M. A physically based mobility model for numerical simulation of nonplanar devices. IEEE Trans. Comput -Aided Des. Integr. Circuits Syst. 1988, 7, 1164–1171. [Google Scholar] [CrossRef]

- Lu, C.-Y.; Cooper, J.A.; Tsuji, T.; Cung, G.; Williams, J.R.; McDonald, K.; Feldman, L.C. Effect of process variations and ambient temperature on electron mobility at the SiO2/4H-SiC interface. IEEE Trans. Electron. Devices 2003, 50, 1582–1588. [Google Scholar] [CrossRef]

- Yang, H.; Hu, S.; Ran, S.; Wang, J.; Liu, T. Simulative Researching of a 1200V SiC Trench MOSFET with an Enhanced Vertical RESURF Effect. IEEE J. Electron Devices Soc. 2020, 8, 1335–1338. [Google Scholar] [CrossRef]

- Nakamura, T.; Nakano, Y.; Yokotsuji, Y. High performance SiC trench devices with ultra-low ron. In Proceedings of the 2011 Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 26.5.1–26.5.3. [Google Scholar] [CrossRef]

- Baliga, B.J. Trench-Gate Power MOSFETs. In Silicon Carbide Power Devices; World Scientific: Singapore, 2006; pp. 323–360. [Google Scholar]

- Henning, J.; Schoen, K.; Melloch, M.; Woodall, J.; Cooper, J. Electrical characteristics of rectifying polycrystalline silicon/silicon carbide heterojunctions. J. Electron. Mater. 1998, 27, 296–299. [Google Scholar] [CrossRef]

- Baliga, B.J. Breakdown Voltage. In Silicon Carbide Power Devices; World Scientific: Singapore, 2006; pp. 37–43. [Google Scholar]

- Baliga, B.J. Semiconductor Power Devices; Woodhead Publishing: Sawston, UK, 2019; pp. 21–42. [Google Scholar] [CrossRef]

- Dahlquist, F. Junction Barrier Schottky Rectifiers in Silicon Carbide. Ph.D. Thesis, KTH Royal Institute of Technology, Stockholm, Sweden, 2002. [Google Scholar]

- Salvadó, O.; Morel, H.; Buttay, C.; Labrousse, D.; Lefebvre, S. Threshold Voltage instability in SiC MOSFET as a consequence of current conduction in their body diode. Microelectron. Reliab. 2018, 88–90, 636–640. [Google Scholar] [CrossRef] [Green Version]

- Dyer, J.; Zhang, Z.; Costinett, D.; Tolbert, L.; Blalock, B. Dead-time optimization for SiC based voltage source converters using online condition monitoring. In Proceedings of the 2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Albuquerque, NM, USA, 30 October–1 November 2017; pp. 15–19. [Google Scholar] [CrossRef]

- Shammas, N.; Chamund, D.; Taylor, P. Forward and reverse recovery behavior of diodes in power converter applications. In Proceedings of the 2004 24th International Conference on Microelectronics (IEEE Cat.No.04TH8716), Nis, Serbia, 16–19 May 2004; pp. 3–10. [Google Scholar] [CrossRef]

- Yue, K.; Pang, L.; You, H.; Li, S.; Kong, D.; Li, Y.; Zhang, Q.; Liu, L. Reverse recovery characteristics of high power thyristors in HVDC converter valve. IEEE Trans. Dielectr. Electr. Insul. 2017, 24, 2132–2140. [Google Scholar] [CrossRef]

- Graovac, D.; Purschel, M.; Kiep, A. MOSFET power losses calculation using the data-sheet parameters. Infineon Appl. Note 2006, 1, 1–23. [Google Scholar]

- Shen, H.-J.; Tang, Y.-C.; Peng, Z.-Y.; Deng, X.-C.; Bai, Y.; Wang, Y.-Y.; Li, C.-Z.; Liu, K.-A.; Liu, X.-Y. Fabrication and Characterization of 1700 V 4H-SiC Vertical Double-Implanted Metal-Oxide-Semiconductor Field-Effect Transistors. Chinese Phys. 2015, 32, 127101. [Google Scholar] [CrossRef]

- Kobayashi, Y.; Harada, S.; Ishimori, H.; Takasu, S.; Kojima, T.; Ariyoshi, K.; Sometani, M.; Senzaki, J.; Takei, M.; Tanaka, Y.; et al. 3.3kV-Class 4H-SiC UMOSFET by Double Trench with Tilt Angle Ion implantation. Mater. Sci. Forum 2016, 858, 974–977. [Google Scholar] [CrossRef]

- Sung, H.K.; Qiang, T.; Yao, Z.; Li, Y.; Wu, Q.; Lee, H.-K.; Park, B.-D.; Lim, W.-S.; Park, K.-H.; Wang, C. Vertical and bevel-structured SiC etching techniques incorporating different gas mixture plasmas for various microelectronic applications. Sci. Rep. 2017, 7. [Google Scholar] [CrossRef]

- Yano, H.; Hatayama, T.; Yraoka, Y.; Fuyuki, T. Characterization of 4H-SiC MOSFETs with NO-annealed CVD oxide. Mater. Sci. Forum 2006, 527–529, 971–974. [Google Scholar] [CrossRef]

- Jiang, J.-Y.; Wu, T.-L.; Zhao, F.; Huang, C.-F. Numerical Study of 4H-SiC UMOSFETs with Split-Gate and P+ Shielding. Energies 2020, 13, 1122. [Google Scholar] [CrossRef] [Green Version]

| Parameter | Con-DTMOS | SG-DTMOS | SHG-DTMOS | Unit |

|---|---|---|---|---|

| Cell pitch | 6 | 6 | 6 | µm |

| Epi-layer thickness | 13 | 13 | 13 | µm |

| Gate trench width | 2 | 2 | 2 | µm |

| Source trench depth | 1.5 | 1.5 | 1.5 | µm |

| Channel length | 0.7 | 0.7 | 0.7 | µm |

| Channel gate length | 1.45 | 0.9 | 0.9 | µm |

| Gate oxide thickness | 0.05 | 0.05 | 0.05 | µm |

| Lox | 0.05 | 0.05 | 0.05 | µm |

| Tox | - | 0.25 | 0.3 | µm |

| WPS | - | - | 0.6 | µm |

| Doping concentration of N-drift (N type) | 5 × 1015 | 5 × 1015 | 5 × 1015 | cm−3 |

| Doping concentration of CSL (N type) | 2 × 1016 | 2 × 1016 | 2 × 1016 | cm−3 |

| Doping concentration of P+ region (P type) | 5 × 1018 | 5 × 1018 | 5 × 1018 | cm−3 |

| Doping concentration of N+ polysilicon (N type) | 1 × 1021 | 1 × 1021 | 1 × 1021 | cm−3 |

| Doping concentration of P+ polysilicon (P type) | - | - | 5 × 1018 | cm−3 |

| Doping concentration of N+ substrate (N type) | 5 × 1019 | 5 × 1019 | 5 × 1019 | cm−3 |

| Parameter | Con-DTMOS | SG-DTMOS | SHG-DTMOS | Unit |

|---|---|---|---|---|

| Breakdown voltage (BV) | 1853 | 1852 | 1789 | V |

| Ron-sp (@VDS = 1 V) | 4.74 | 5.55 | 5.45 | mΩ∙cm2 |

| Emox (@VDS = 1200 V) | 2.09 | 2.09 | 1.33 | MV∙cm−1 |

| Ciss (@VDS = 1200 V) | 40.6 | 17.7 | 17.0 | nF∙cm−2 |

| Crss (@VDS = 1200 V) | 11.06 | 2.05 | 2.5 | pF∙cm−2 |

| Coss (@VDS = 1200 V) | 670 | 670 | 669 | pF∙cm−2 |

| QGD | 84.84 | 22.89 | 24.52 | nC∙cm−2 |

| QG | 826.1 | 372.8 | 362.5 | nC∙cm−2 |

| HF-FOM (Ron-sp × QGD) | 402.1 | 127.0 | 133.6 | mΩ∙nC |

| Parameter | Con-DTMOS | SG-DTMOS | SHG-DTMOS | Unit |

|---|---|---|---|---|

| VF | 2.88 | 2.88 | 1.88 | V |

| trr | 63.7 | 52.7 | 46.9 | ns |

| Qrr | 2996 | 3804 | 1010 | nC∙cm−2 |

| Toff | 456 | 229 | 226 | ns |

| Ton | 282 | 139 | 129 | ns |

| TSW | 738 | 368 | 355 | ns |

| Eoff | 0.737 | 0.572 | 0.552 | mJ∙cm−2 |

| Eon | 7.131 | 5.885 | 3.001 | mJ∙cm−2 |

| ESW | 7.868 | 6.457 | 3.553 | mJ∙cm−2 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Na, J.; Cheon, J.; Kim, K. 4H-SiC Double Trench MOSFET with Split Heterojunction Gate for Improving Switching Characteristics. Materials 2021, 14, 3554. https://doi.org/10.3390/ma14133554

Na J, Cheon J, Kim K. 4H-SiC Double Trench MOSFET with Split Heterojunction Gate for Improving Switching Characteristics. Materials. 2021; 14(13):3554. https://doi.org/10.3390/ma14133554

Chicago/Turabian StyleNa, Jaeyeop, Jinhee Cheon, and Kwangsoo Kim. 2021. "4H-SiC Double Trench MOSFET with Split Heterojunction Gate for Improving Switching Characteristics" Materials 14, no. 13: 3554. https://doi.org/10.3390/ma14133554

APA StyleNa, J., Cheon, J., & Kim, K. (2021). 4H-SiC Double Trench MOSFET with Split Heterojunction Gate for Improving Switching Characteristics. Materials, 14(13), 3554. https://doi.org/10.3390/ma14133554