Drain Current Stress-Induced Instability in Amorphous InGaZnO Thin-Film Transistors with Different Active Layer Thicknesses

Abstract

1. Introduction

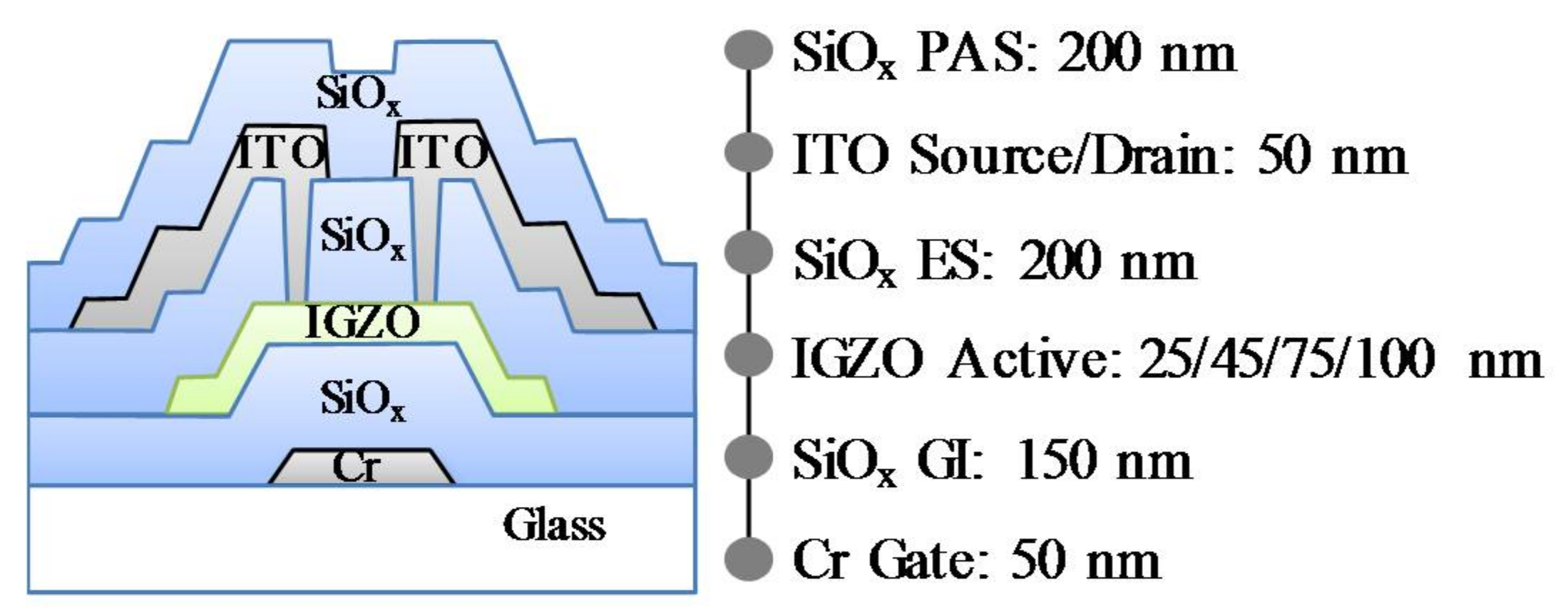

2. Experimental

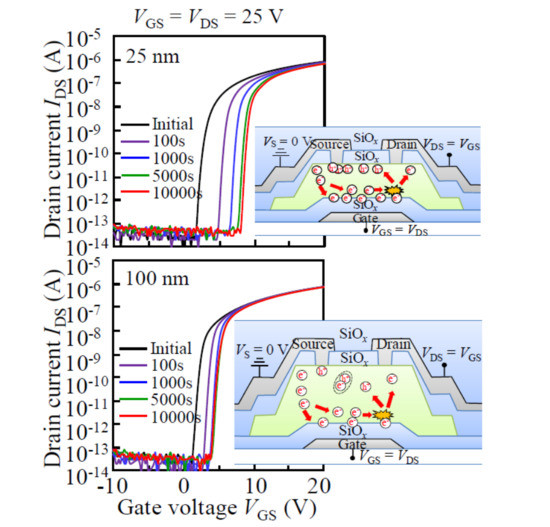

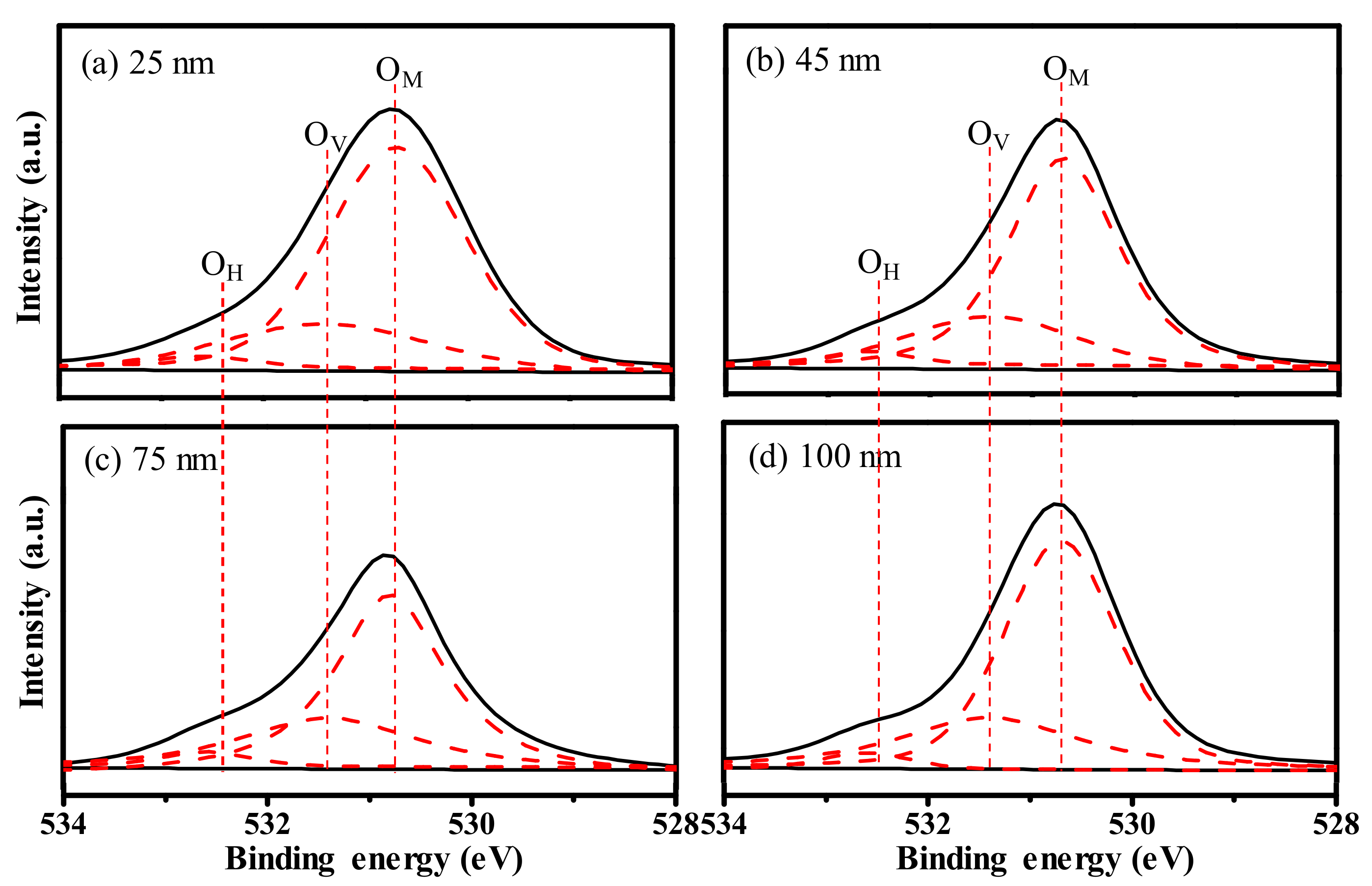

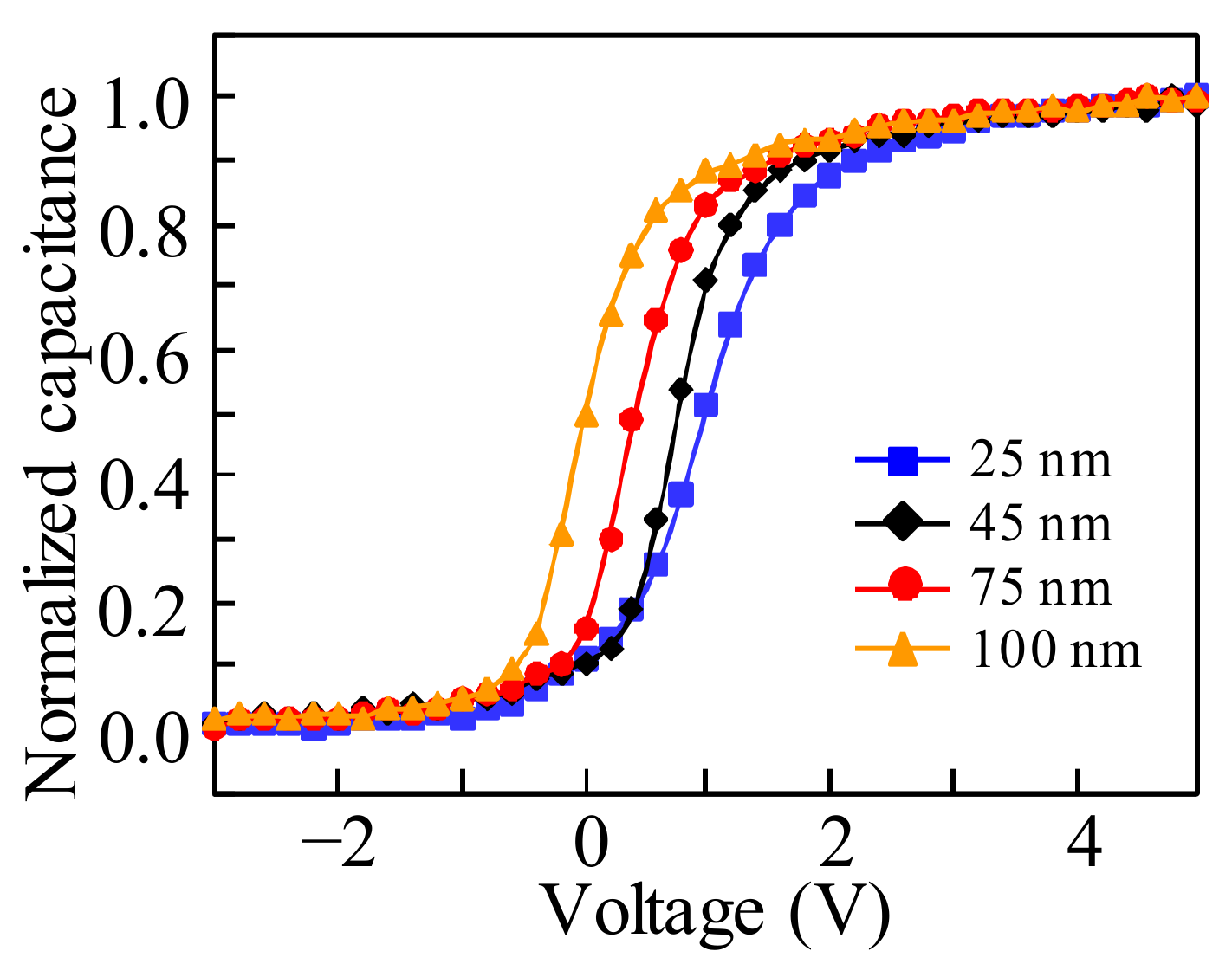

3. Results and Discussion

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 2004, 432, 488–492. [Google Scholar] [CrossRef] [PubMed]

- Lee, S.-H.; Kim, T.; Lee, J.; Avis, C.; Jang, J. Solution-processed gadolinium doped indium-oxide thin-film transistors with oxide passivation. Appl. Phys. Lett. 2017, 110, 122102. [Google Scholar] [CrossRef]

- Martins, J.; Bahubalindruni, P.; Rovisco, A.; Kiazadeh, A.; Martins, R.; Fortunato, E.; Barquinha, P. Bias stress and temperature impact on InGaZnO TFTs and circuits. Materials 2017, 10, 680. [Google Scholar] [CrossRef] [PubMed]

- Wang, W.-H.; Lyu, S.-R.; Hredia, E.; Liu, S.-H.; Jiang, P.-H.; Liao, P.-Y.; Chang, T.-C.; Chen, H.-M. Competing weak localization and weak antilocalization in amorphous indium–gallium–zinc-oxide thin-film transistors. Appl. Phys. Lett. 2017, 110, 022106. [Google Scholar] [CrossRef]

- Zhang, J.; Yang, J.; Li, Y.; Wilson, J.; Ma, X.; Xin, Q.; Song, A. High performance complementary circuits based on p-SnO and n-IGZO thin-film transistors. Materials 2017, 10, 319. [Google Scholar] [CrossRef] [PubMed]

- Hung, M.P.; Wang, D.; Jiang, J.; Furuta, M. Negative bias and illumination stress induced electron trapping at back-channel interface of InGaZnO thin-film transistor. ECS Solid State Lett. 2014, 3, Q13–Q16. [Google Scholar] [CrossRef]

- Hirao, T.; Furuta, M.; Hiramatsu, T.; Matsuda, T.; Li, C.; Furuta, H.; Hokari, H.; Yoshida, M.; Ishii, H.; Kakegawa, M. Bottom-gate zinc oxide thin-film transistors (ZnO TFTs) for AM-LCDs. IEEE Trans. Electron Dev. 2008, 55, 3136–3142. [Google Scholar] [CrossRef]

- Kim, K.S.; Ahn, C.H.; Kang, W.J.; Cho, S.W.; Jung, S.H.; Yoon, D.H.; Cho, H.K. An all oxide-based imperceptible thin-film transistor with humidity sensing properties. Materials 2017, 10, 530. [Google Scholar] [CrossRef] [PubMed]

- Wang, D.; Hung, M.P.; Jiang, J.; Toda, T.; Furuta, M. Suppression of degradation induced by negative gate bias and illumination stress in amorphous InGaZnO thin-film transistors by applying negative drain bias. ACS Appl. Mater. Interfaces 2014, 6, 5713–5718. [Google Scholar] [CrossRef] [PubMed]

- Billah, M.M.; Jang, J. Millisecond positive bias recovery of negative bias illumination stressed amorphous InGaZnO thin-film transistors. IEEE Electron Device Lett. 2017, 38, 477–480. [Google Scholar] [CrossRef]

- Fujii, M.; Yano, H.; Hatayama, T.; Uraoka, Y.; Fuyuki, T.; Jung, J.S.; Kwon, J.Y. Thermal analysis of degradation in Ga2O3–In2O3–ZnO thin-film transistors. Jpn. J. Appl. Phys. 2008, 47, 6236–6240. [Google Scholar] [CrossRef]

- Choi, S.-H.; Han, M.-K. Effect of channel widths on negative shift of threshold voltage, including stress induced hump phenomenon in InGaZnO thin-film transistors under high-gate and drain bias stress. Appl. Phys. Lett. 2012, 100, 043503. [Google Scholar] [CrossRef]

- Valdinoci, M.; Colalongo, L.; Baccarani, G.; Fortunato, G.; Pecora, A.; Policicchio, I. Floating body effects in polysilicon thin-film transistors. IEEE Trans. Electron Dev. 1997, 44, 2234–2241. [Google Scholar] [CrossRef]

- Park, H.-W.; Park, K.; Kwon, J.-Y.; Choi, D.; Chung, K.-B. Effect of active layer thickness on device performance of tungsten-doped InZnO thin-film transistor. IEEE Trans. Electron Dev. 2016, 64, 159–163. [Google Scholar] [CrossRef]

- Park, J.; Kim, Y.S.; Kim, J.H.; Park, K.; Park, Y.C.; Kim, H.-S. The effects of active layer thickness and annealing conditions on the electrical performance of ZnON thin-film transistors. J. Alloy. Compd. 2016, 688, 666–671. [Google Scholar] [CrossRef]

- Yang, Z.; Yang, J.; Meng, T.; Qu, M.; Zhang, Q. Influence of channel layer thickness on the stability of amorphous indium zinc oxide thin film transistors. Mater. Lett. 2016, 166, 46–50. [Google Scholar] [CrossRef]

- Avis, C.; Hwang, H.R.; Jang, J. Effect of channel layer thickness on the performance of Indium–Zinc–Tin oxide thin film transistors manufactured by inkjet printing. ACS Appl. Mater. Interfaces 2014, 6, 10941–10945. [Google Scholar] [CrossRef] [PubMed]

- Jeong, J.; Hong, Y. Debye length and active layer thickness-dependent performance variations of amorphous oxide-based TFTs. IEEE Trans. Electron Dev. 2012, 59, 710–714. [Google Scholar] [CrossRef]

- Li, Y.; Pei, Y.L.; Hu, R.Q.; Chen, Z.M.; Zhao, Y.; Shen, Z.; Fan, B.F.; Liang, J.; Wang, G. Effect of channel thickness on electrical performance of amorphous IGZO thin-film transistor with atomic layer deposited alumina oxide dielectric. Curr. Appl. Phys. 2014, 14, 941–945. [Google Scholar] [CrossRef]

- Singh, T.; Lehnen, T.; Leuning, T.; Sahu, D.; Mathur, S. Thickness dependence of optoelectronic properties in ALD grown ZnO thin films. Appl. Surf. Sci. 2014, 289, 27–32. [Google Scholar] [CrossRef]

- Wang, D.; Jiang, J.; Furuta, M. Investigation of carrier generation mechanism in fluorine-doped n+ In–Ga–Zn-O for self-aligned thin-film transistors. J. Disp. Technol. 2016, 12, 258–262. [Google Scholar] [CrossRef]

- Yue, L.; Pu, H.-F.; Li, H.-L.; Pang, S.-J.; Zhang, Q. Effect of active layer thickness on device performance of a-LZTO thin-film transistors. Superlattices Microstruct. 2013, 57, 123–128. [Google Scholar] [CrossRef]

- Chen, A.H.; Cao, H.T.; Zhang, H.Z.; Liang, L.Y.; Liu, Z.M.; Yu, Z.; Wan, Q. Influence of the channel layer thickness on electrical properties of indium zinc oxide thin-film transistor. Microelectron. Eng. 2010, 87, 2019–2023. [Google Scholar] [CrossRef]

- Woo, C.H.; Kim, Y.Y.; Kong, B.H.; Cho, H.K. Effects of the thickness of the channel layer on the device performance of InGaZnO thin-film-transistors. Surf. Coat. Technol. 2010, 205, S168–S171. [Google Scholar] [CrossRef]

- Wang, Y.; Sun, X.W.; Goh, G.K.L.; Demir, H.V.; Yu, H.Y. Influence of channel layer thickness on the electrical performances of inkjet-printed In-Ga-Zn oxide thin-film transistors. IEEE Trans. Electron Dev. 2011, 58, 480–485. [Google Scholar] [CrossRef]

- Urakawa, S.; Tomai, S.; Ueoka, Y.; Yamazaki, H.; Kasami, M.; Yano, K.; Wang, D.; Furuta, M.; Horita, M.; Ishikawa, Y.; et al. Thermal distribution in amorphous InSnZnO thin-film transistor. Phys. Status Solidi C 2013, 10, 1561–1564. [Google Scholar] [CrossRef]

| O 1s | IGZO Thickness (nm) | ||||

|---|---|---|---|---|---|

| 25 | 45 | 75 | 100 | ||

| OM | Position (eV) | 530.7 | 530.7 | 530.7 | 530.7 |

| Area | 177500 | 159500 | 158000 | 156000 | |

| OV | Position (eV) | 531.4 | 531.4 | 531.4 | 531.4 |

| Area | 53500 | 55500 | 61000 | 67000 | |

| OH | Position (eV) | 532.6 | 532.6 | 532.6 | 532.6 |

| Area | 7500 | 7000 | 7000 | 7500 | |

| OM/(OM + OV + OH) area ratio (%) | 74.4 | 71.8 | 69.9 | 67.7 | |

| OV/(OM + OV + OH) area ratio (%) | 22.4 | 25.0 | 27.0 | 29.1 | |

| OH/(OM + OV + OH) area ratio (%) | 3.2 | 3.2 | 3.1 | 3.2 | |

| Thickness (nm) | 25 | 45 | 75 | 100 |

|---|---|---|---|---|

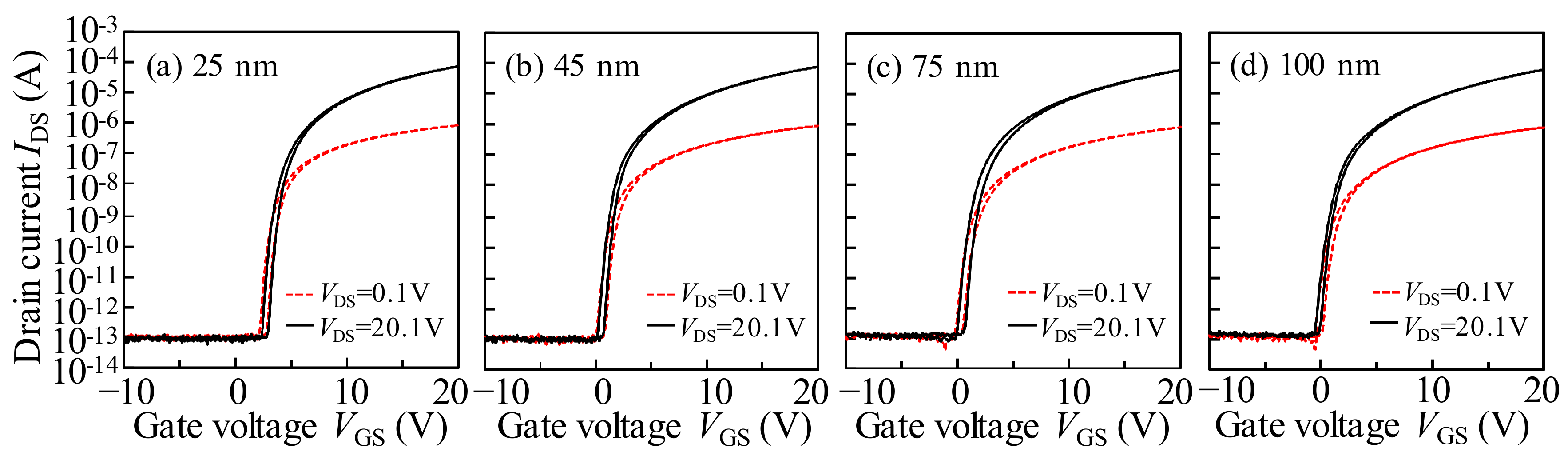

| μsat (cm2∙V−1∙s−1) | 14.17 | 14.01 | 13.62 | 13.04 |

| Von at IDS = 1 nA (V) | 2.32 | 0.27 | 0.04 | −0.33 |

| Hysteresis ΔVH (V) | 0.52 | 0.54 | 0.55 | 0.43 |

| Subthreshold swing (mV/dec.) | 323 | 367 | 416 | 475 |

| Thickness (nm) | 25 | 45 | 75 | 100 |

|---|---|---|---|---|

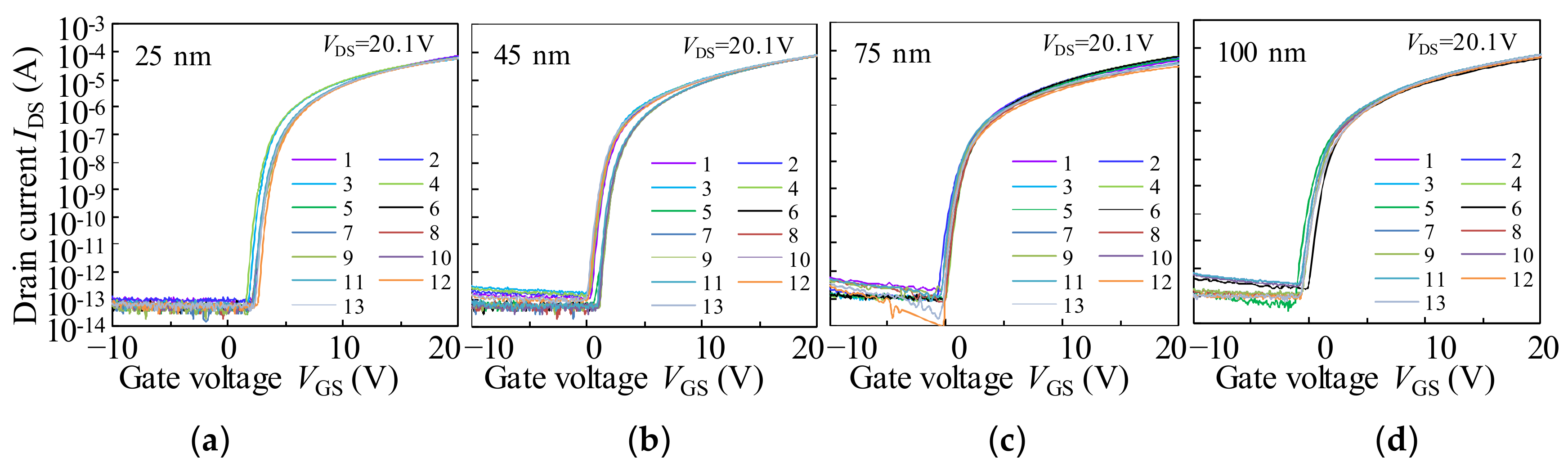

| μsat (cm2∙V−1∙s−1) | 13.91 ± 0.92 | 13.70 ± 0.39 | 12.50 ± 1.01 | 11.88 ± 0.34 |

| Von at IDS = 1 nA (V) | 2.29 ± 0.28 | 1.60 ± 0.46 | 1.31 ± 0.44 | 0.88 ± 0.46 |

| Hysteresis ΔVH (V) | 0.37 ± 0.18 | 0.33 ± 0.07 | 0.38 ± 0.27 | 0.28 ± 0.12 |

| SS (mV/dec.) | 279 ± 24 | 287 ± 19 | 314 ± 23 | 351 ± 26 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, D.; Zhao, W.; Li, H.; Furuta, M. Drain Current Stress-Induced Instability in Amorphous InGaZnO Thin-Film Transistors with Different Active Layer Thicknesses. Materials 2018, 11, 559. https://doi.org/10.3390/ma11040559

Wang D, Zhao W, Li H, Furuta M. Drain Current Stress-Induced Instability in Amorphous InGaZnO Thin-Film Transistors with Different Active Layer Thicknesses. Materials. 2018; 11(4):559. https://doi.org/10.3390/ma11040559

Chicago/Turabian StyleWang, Dapeng, Wenjing Zhao, Hua Li, and Mamoru Furuta. 2018. "Drain Current Stress-Induced Instability in Amorphous InGaZnO Thin-Film Transistors with Different Active Layer Thicknesses" Materials 11, no. 4: 559. https://doi.org/10.3390/ma11040559

APA StyleWang, D., Zhao, W., Li, H., & Furuta, M. (2018). Drain Current Stress-Induced Instability in Amorphous InGaZnO Thin-Film Transistors with Different Active Layer Thicknesses. Materials, 11(4), 559. https://doi.org/10.3390/ma11040559