Effect of Wafer Level Underfill on the Microbump Reliability of Ultrathin-Chip Stacking Type 3D-IC Assembly during Thermal Cycling Tests

Abstract

:1. Introduction

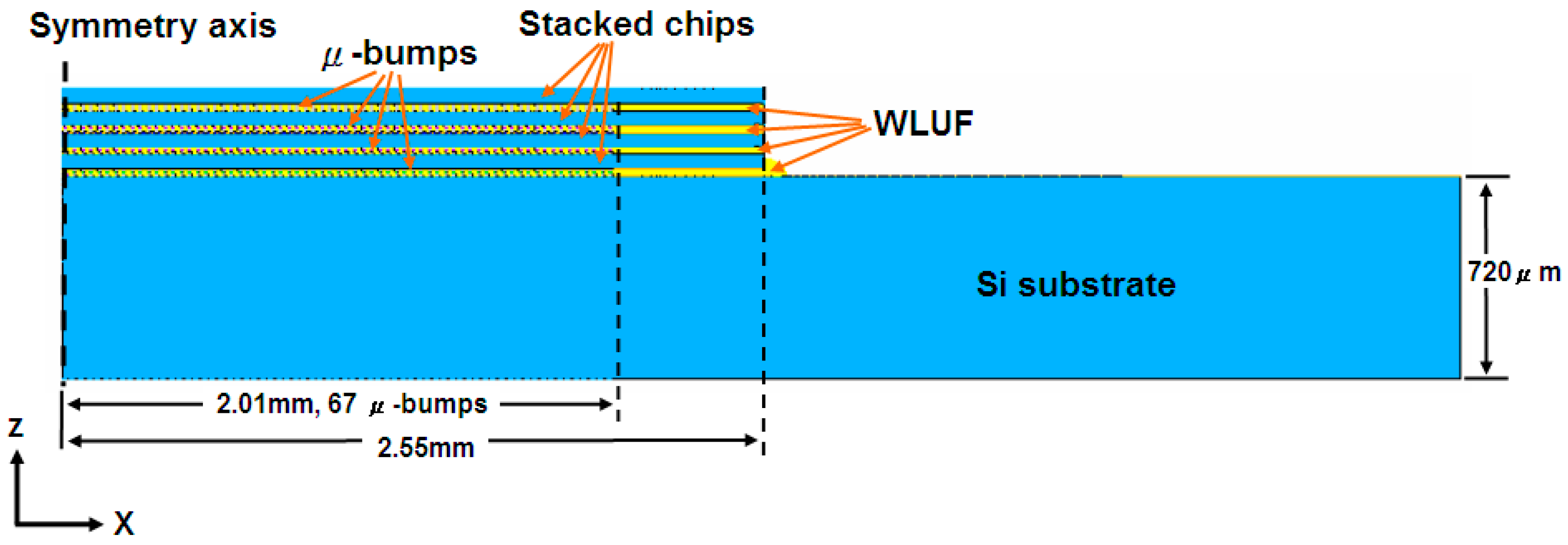

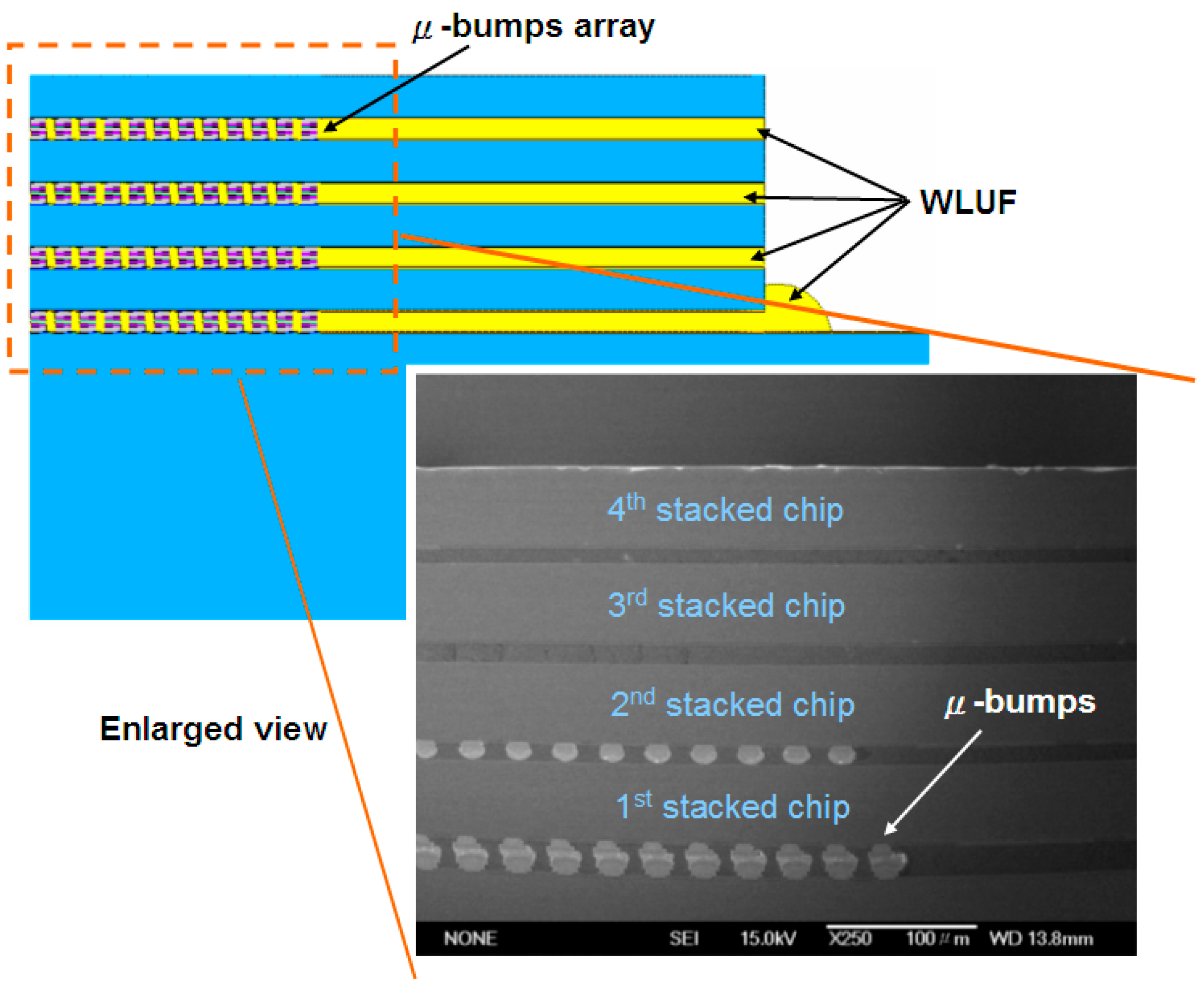

2. Temperature Cycling Test of 3D-IC Packaging

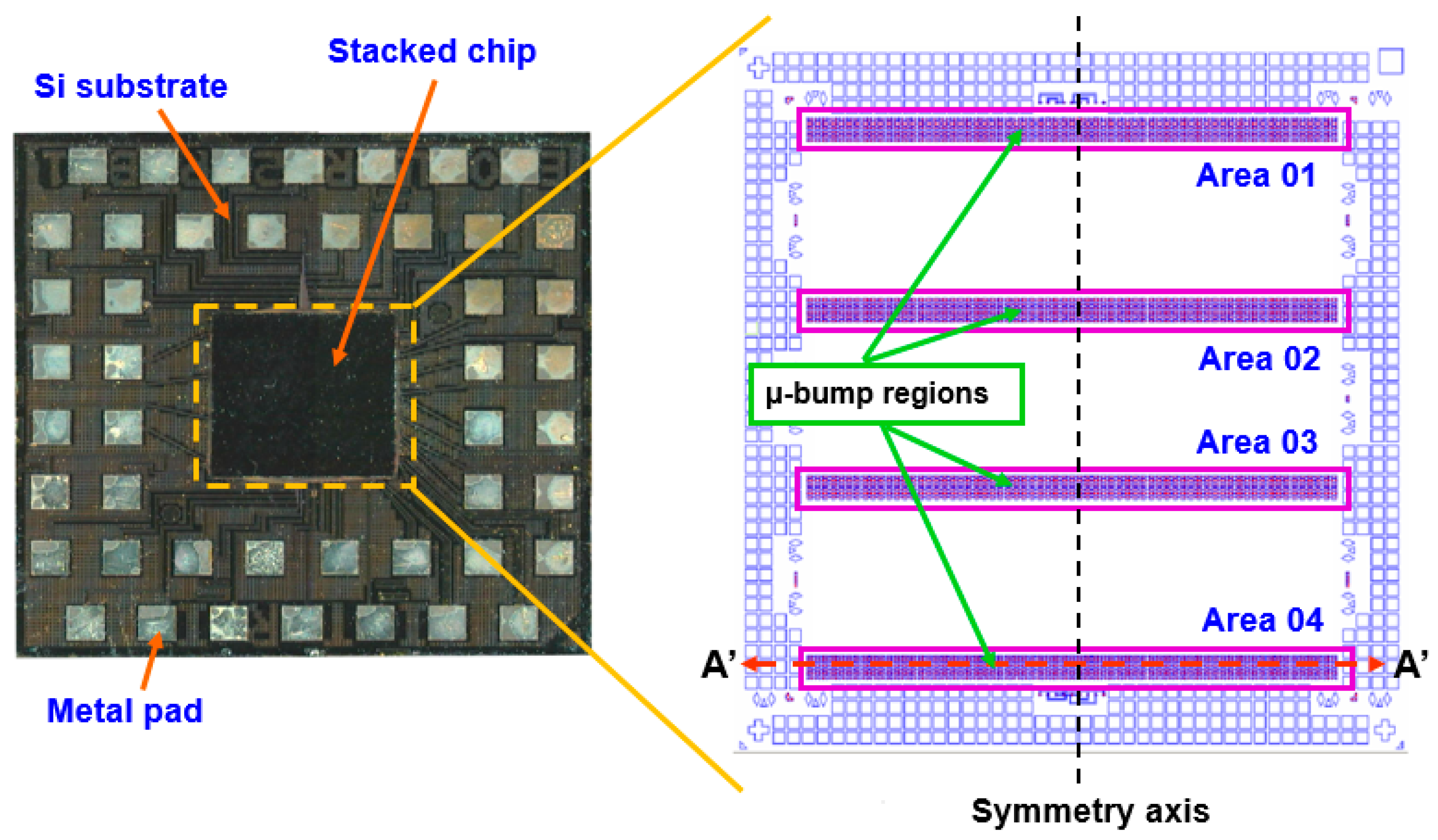

2.1. Assembly of Stacked Chips with WLUF

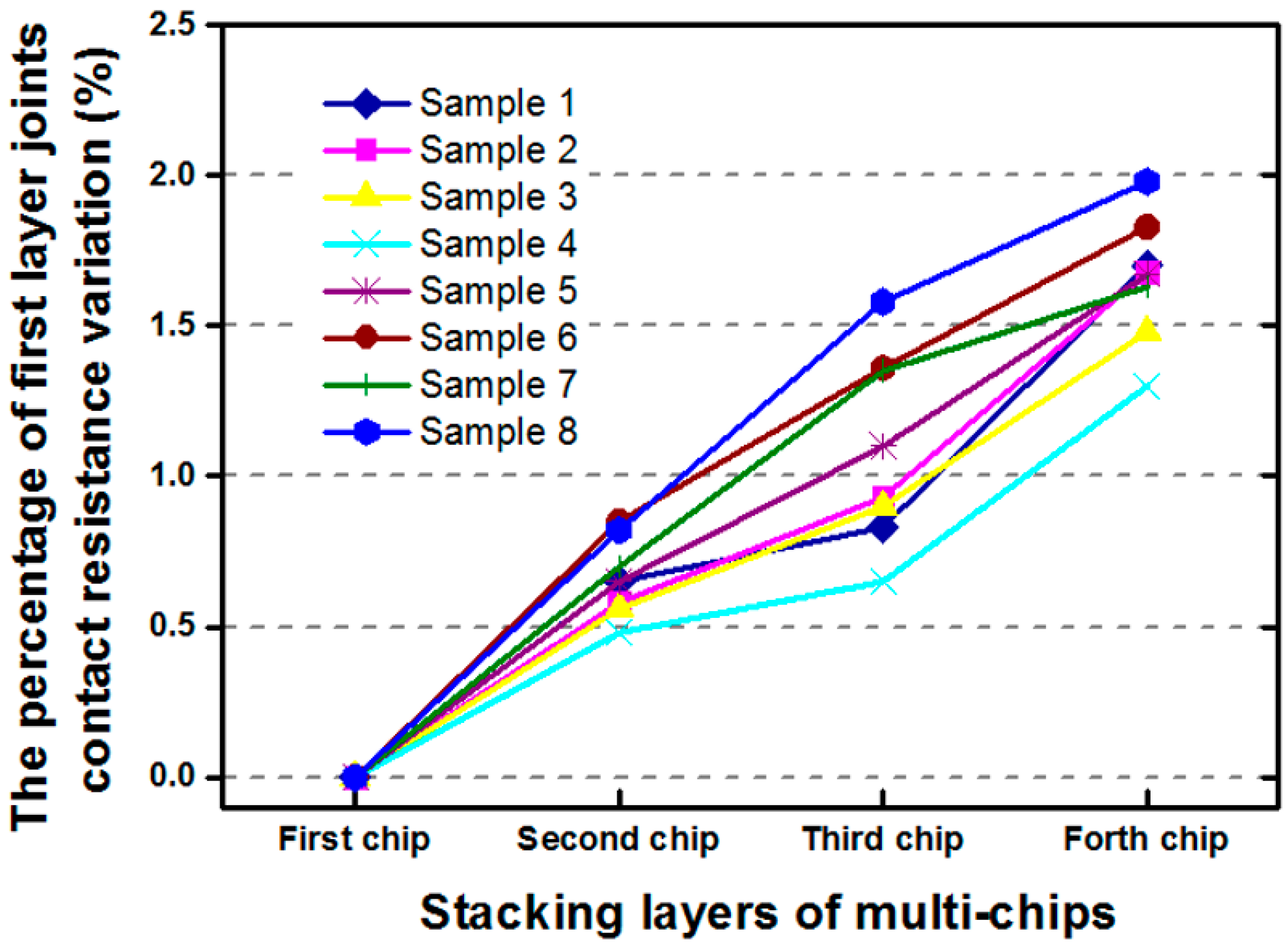

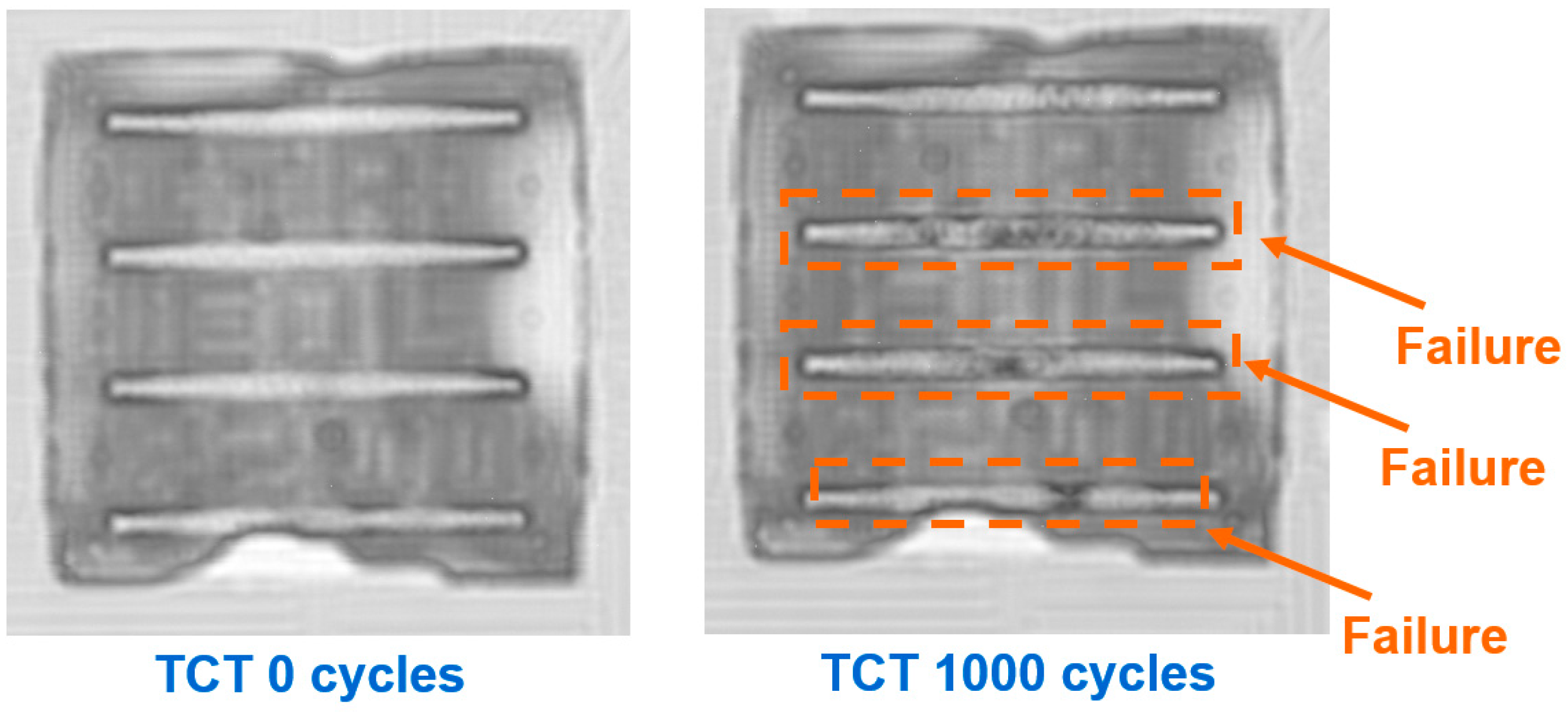

2.2. Reliability Experiment Results

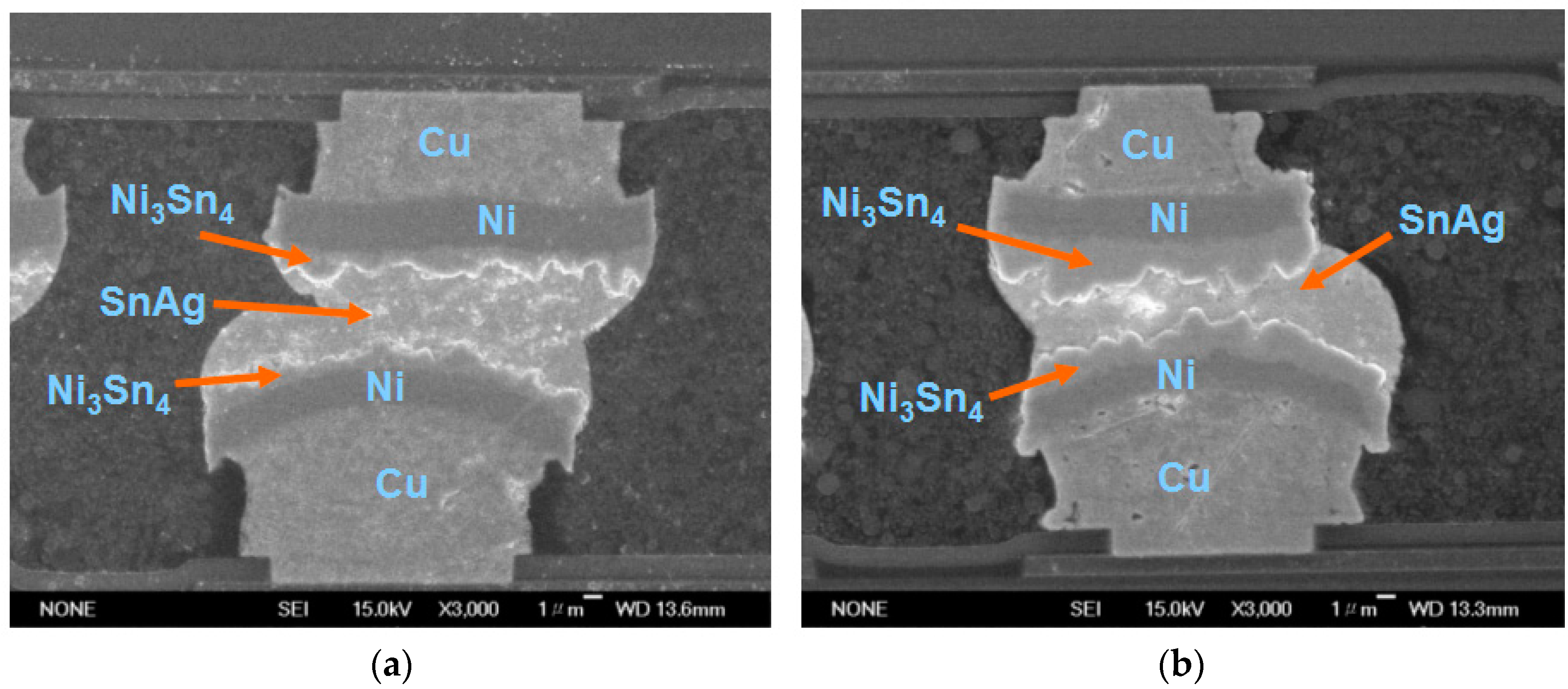

3. Failure Analysis and the Estimation of Fatigue Lifetime in μ-Bumps

3.1. Coffin-Manson Relationship in Lead-Free Bumps

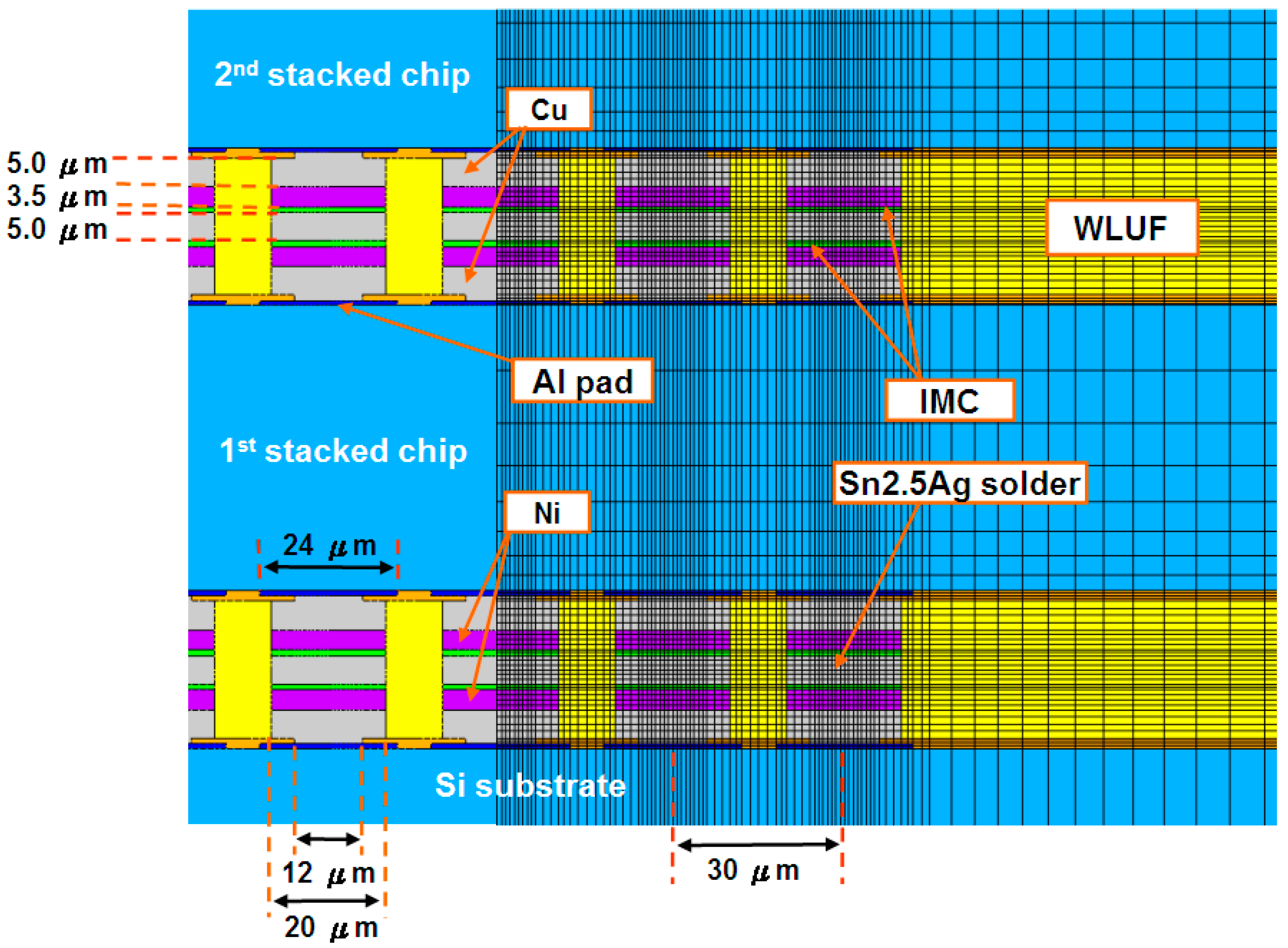

3.2. Finite Modeling Assembly of Stacked Chips Using WLUF

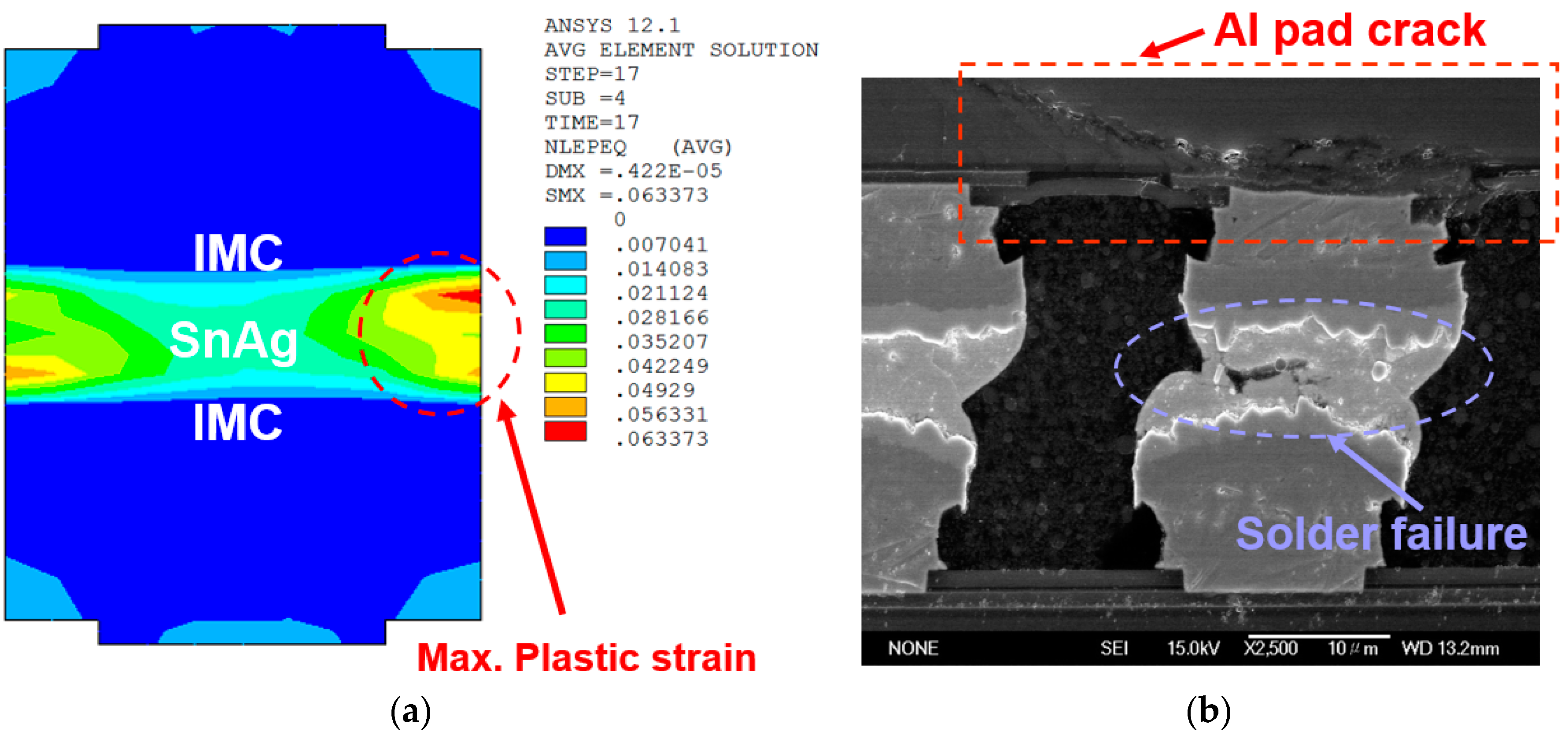

3.3. Failure Mode and Comparison of the Simulated Predictions and the Experimental Results in Terms of the Fatigue Lifetimes of 3D-IC Packaging

4. Geometric and Material Influences of 3D-IC Packages on μ-Bump Reliability

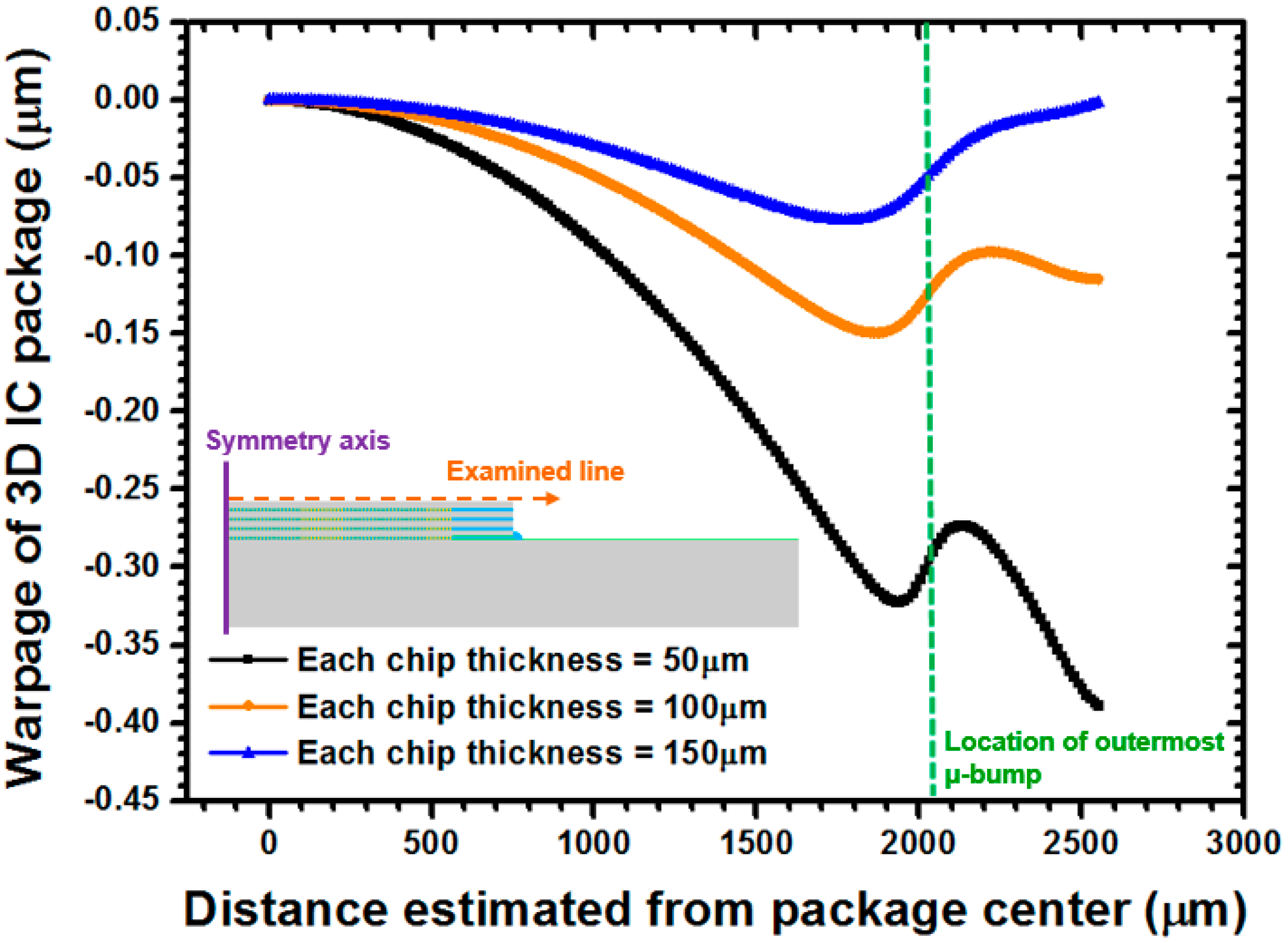

4.1. Warpage Induced during Temperature Cycling Loads

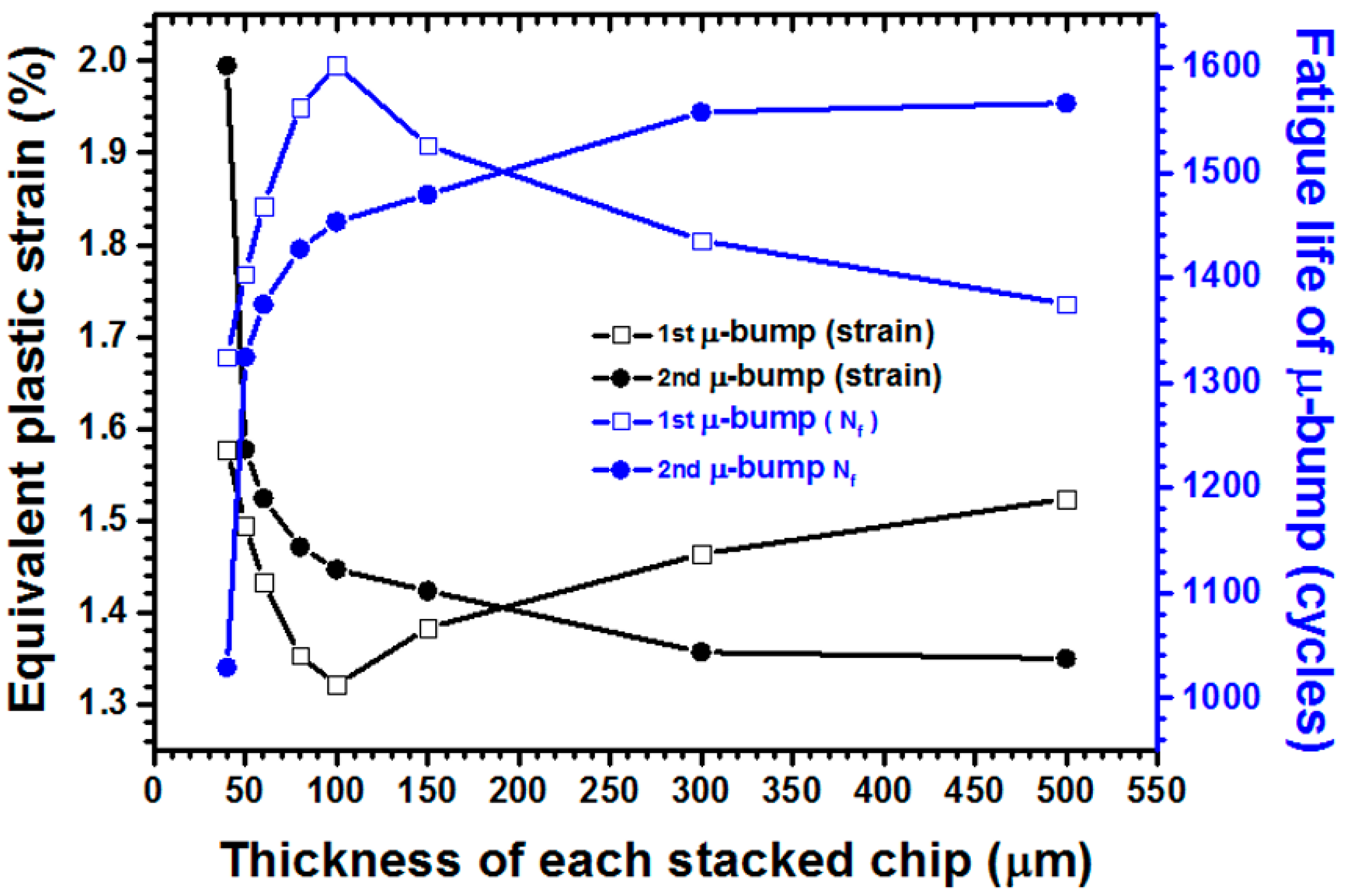

4.2. Effect of Stacked Chip Thickness

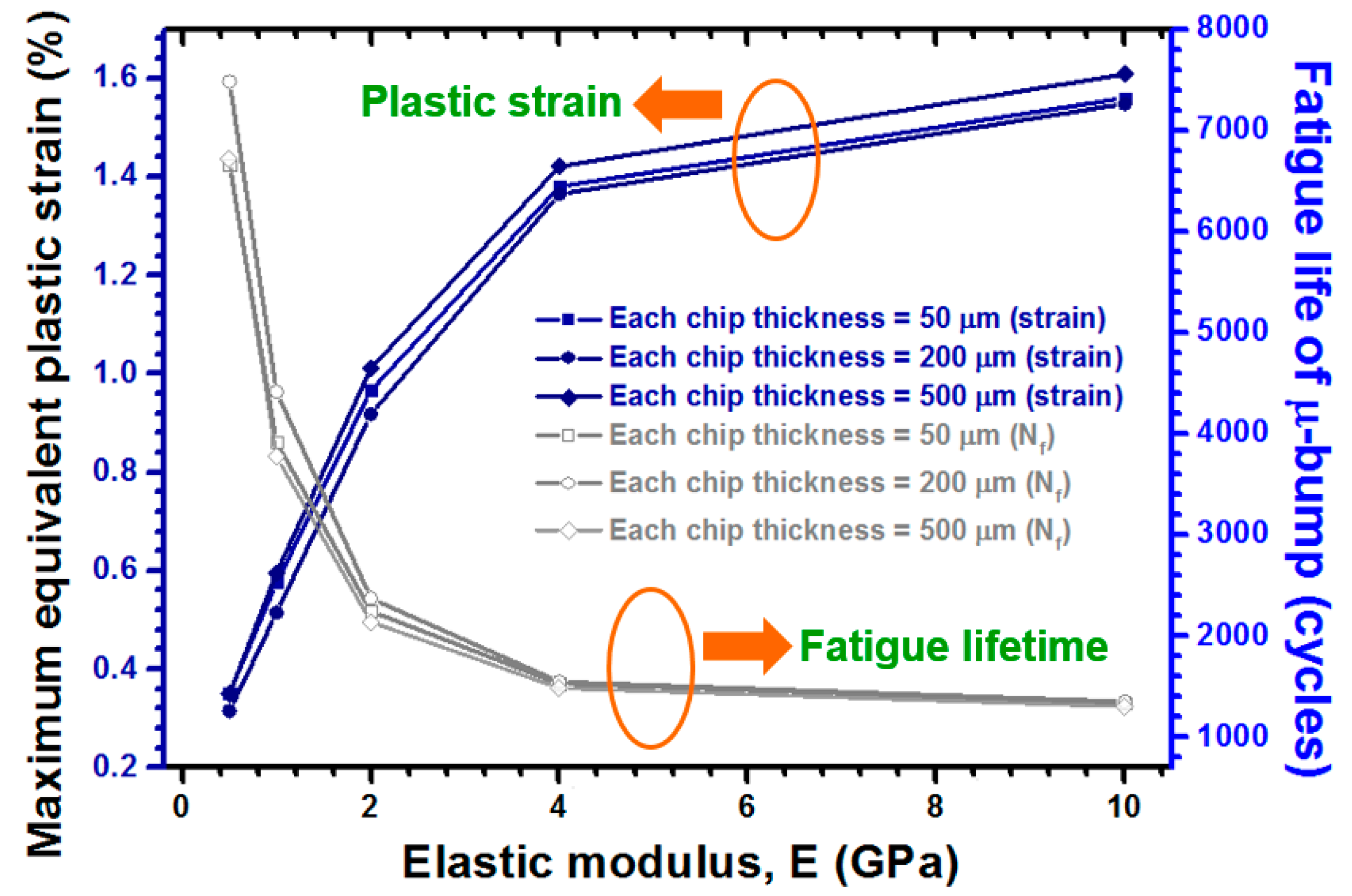

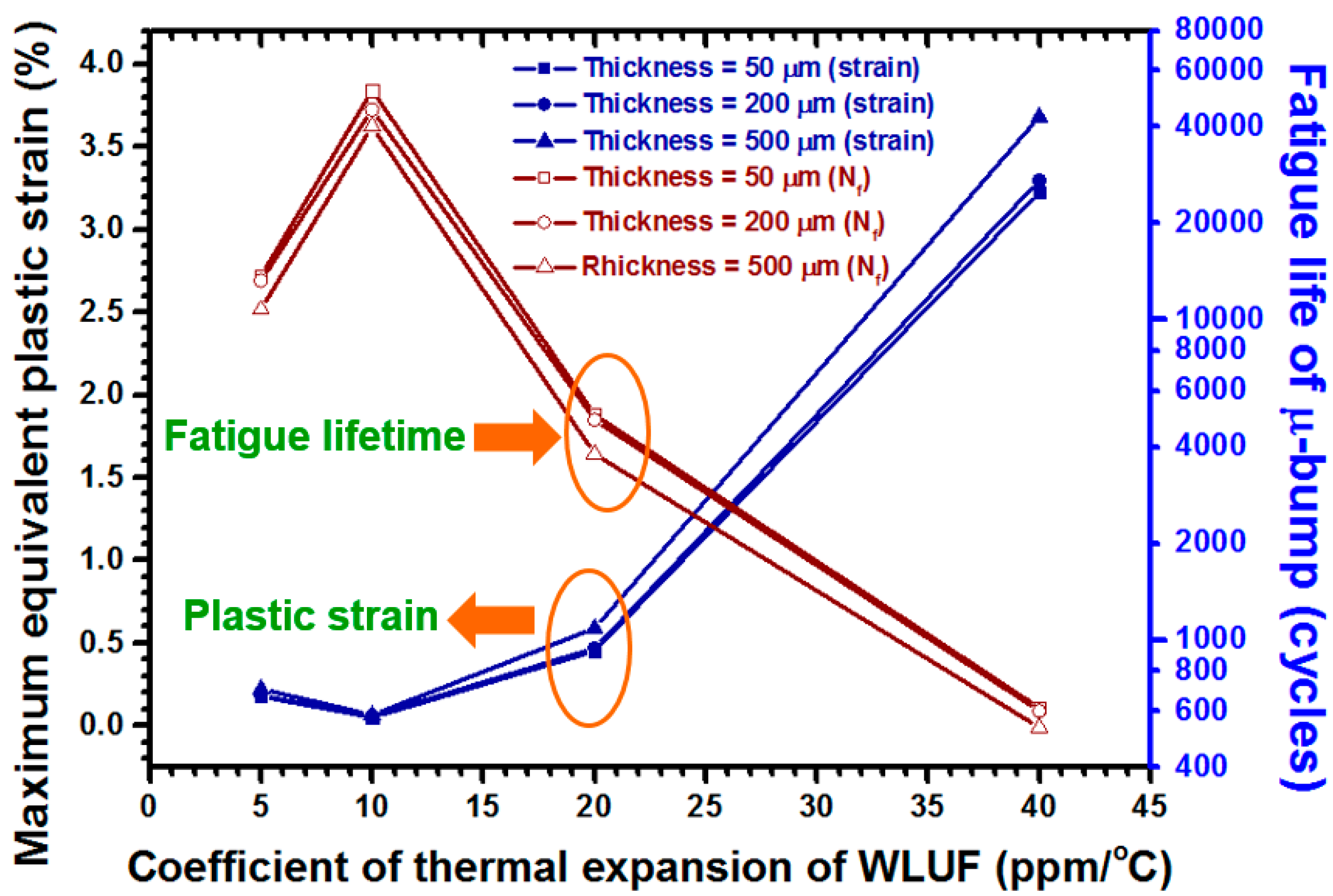

4.3. Effect of WLUF Elastic Modulus

5. Conclusions

Acknowledgments

Conflicts of Interest

References

- Sukumaran, V.; Kumar, G.; Ramachandran, K.; Suzuki, Y.; Demir, K.; Sato, Y.; Seki, T.; Sundaram, V.; Tummala, R. Design, fabrication, and characterization of ultrathin 3-D glass interposers with through-package-vias at same pitch as TSVs in silicon. IEEE Trans. Compon. Packag. Manuf. Technol. 2014, 4, 786–795. [Google Scholar] [CrossRef]

- Qin, X.; Kumbhat, N.; Raj, P.M.; Sundaram, V.; Tummala, R. Finite element analysis and experiment validation of highly reliable silicon and glass interposers-to-printed wiring board SMT interconnections. IEEE Trans. Compon. Packag. Manuf. Technol. 2014, 4, 796–806. [Google Scholar] [CrossRef]

- Guiller, O.; Joblot, S.; Lamy, Y.; Farcy, A.; Carpentier, J.F.; Defay, E. Through silicon capacitor co-integrated with TSVs on silicon interposer. Microelectron. Eng. 2014, 120, 121–126. [Google Scholar] [CrossRef]

- Auersperg, J.; Dudek, R.; Jordan, R.; Bochow, N.O.; Rzepka, S.; Michel, B. On the crack and delamination risk optimization of a Si-interposer for LED packaging. Microelectron. Reliab. 2014, 54, 1223–1227. [Google Scholar] [CrossRef]

- Kumar, G.; Sitaraman, S.; Cho, J.H.; Sundaram, V.; Kim, J.H.; Tummala, R. Design and demonstration of power delivery networks with effective resonance suppression in double-sided 3-D glass interposer packages. IEEE Trans. Compon. Packag. Manuf. Technol. 2016, 6, 87–99. [Google Scholar] [CrossRef]

- Su, Y.F.; Chang, K.N.; Liang, S.Y. Design and reliability assessment of novel 3D-IC packaging. J. Mech. 2017, 33, 193–203. [Google Scholar] [CrossRef]

- Cheng, H.C.; Huang, T.C.; Hwang, P.W.; Chen, W.H. Heat dissipation assessment of through silicon via (TSV)-based 3D IC packaging for CMOS image sensing. Microelectron. Reliab. 2016, 59, 84–94. [Google Scholar] [CrossRef]

- Chen, W.Y.; Duh, J.G. Suppression of Cu3Sn layer and formation of multi-orientation IMCs during thermal aging in Cu/Sn-3.5Ag/Cu-15Zn transient liquid-phase bonding in novel 3D-IC technologie. Mater. Lett. 2017, 186, 279–282. [Google Scholar] [CrossRef]

- Lee, C.C.; Yang, T.F.; Kao, K.S.; Cheng, R.C.; Zhan, C.J.; Chen, T.H. Development of Cu/Ni/SnAg microbump bonding processes for thin chip-on-chip packages via wafer-level underfill film. IEEE Trans. Compon. Packag. Manuf. Technol. 2012, 2, 1412–1419. [Google Scholar] [CrossRef]

- Lee, C.C.; Kao, K.S.; Cheng, R.C.; Zhan, C.J.; Chang, T.C. Reliability enhancements of chip-on-chip package with layout designs of microbumps. Microelectron. Eng. 2014, 120, 138–145. [Google Scholar] [CrossRef]

- Lee, C.C.; Lin, P.T. Reliability-based design guidance of three-dimensional integrated circuits packaging using thermal compression bonding and dummy Cu/Ni/SnAg microbumps. J. Electron. Packag. 2014, 136, 031006. [Google Scholar] [CrossRef]

- Kao, K.S.; Cheng, R.S.; Zhan, C.J.; Chang, J.Y.; Yang, T.F.; Huang, S.Y.; Fan, C.W.; Chen, S.M.; Chung, S.C.; Lu, Y.L.; et al. Assembly and reliability assessment of 50 µm-thick chip stacking by wafer-level underfill film. In Proceedings of the IEEE 7th International Microsystems, Packaging, Assembly and Circuits Technology Conference (IMPACT 2012), Taipei, Taiwan, 24–26 October 2012; pp. 307–310. [Google Scholar]

- Ling, X.; Wickramanayaka, S.; Boo, Y.J.; Li, J.A.J.; Lim, J.K.; Ismael, D. Wafer level underfill study for high density ultra-fine pitch Cu-Cu bonding for 3D IC stacking. In Proceedings of the IEEE 16th Electronics Packaging Technology Conference (EPTC 2014), Singapore, 3–5 December 2014; pp. 400–404. [Google Scholar]

- Wang, T.; Bex, P.; Capuz, G.; Duval, F.; Inoue, F.; Gerets, C.; Bertheau, J.; Rebibis, K.J.; Miller, A.; Beyer, G.; et al. 3D IC assembly using thermal compression bonding and wafer-level underfill–Strategies for quality improvement and throughput enhancement. In Proceedings of the IEEE 18th Electronics Packaging Technology Conference (EPTC 2016), Singapore, 30 November–3 December 2016; pp. 791–796. [Google Scholar]

- Cadacio, F., Jr.; Rebibis, K.J.; Capuz, G.; Daily, R.; Gerets, C.; Sleeckx, E.; Duval, F.; Wang, T.; Miller, R.A.; Beyer, G.; et al. Reliability of 3D package using wafer level underfill and low CTE epoxy mold compound materials. In Proceedings of the IEEE 16th Electronics Packaging Technology Conference (EPTC 2014), Singapore, 3–5 December 2014; pp. 444–448. [Google Scholar]

- Rao, V.S.; Ser, C.C.; Chen, Z.; Jie, L.A.; Ching, E.W.L.; Hwang, G.; Fernandez, D.M. Development of bonding process for high density fine pitch micro bump interconnections with wafer level underfill for 3D applications. In Proceedings of the IEEE 15th Electronics Packaging Technology Conference (EPTC 2013), Singapore, 11–13 December 2013; pp. 543–548. [Google Scholar]

- Shen, Y.L.; Flores, G.C.; Guthrie, J. Numerical study of microbump failure in 3D microelectronic structures. Microelectron. Reliab. 2016, 61, 48–55. [Google Scholar] [CrossRef]

- Che, F.X.; Zhang, X.W.; Lin, J.K. Reliability study of 3D IC packaging based on through-silicon interposer (TSI) and silicon-less interconnection technology (SLIT) using finite element analysis. Microelectron. Reliab. 2016, 61, 64–70. [Google Scholar] [CrossRef]

- Zhen, Q.H.; Guan, Y.; Su, F.; Chen, J.; Jin, Y.F. Influence of viscoelastic underfill on thermal mechanical reliability of a 3-D-TSV stack by simulation. IEEE Trans. Device Mater. Reliab. 2017, 17, 340–348. [Google Scholar]

- Coffin, L.F., Jr. A study of the effects of cyclic thermal stresses on a ductile metal. ASME Trans. 1954, 76, 931–950. [Google Scholar]

- Manson, S.S. Fatigue: A complex subject—Some simple approximations. Exp. Mech. 1965, 5, 193–226. [Google Scholar] [CrossRef]

- Kanchanomai, C.; Mutoh, Y. Low-cycle fatigue prediction model for pb-free solder 96.5Sn-3.5Ag. J. Electron. Mater. 2004, 33, 329–333. [Google Scholar] [CrossRef]

- Clech, J.P. BGA, flip-chip and CSP solder joint reliability of the importance of model validation. In Proceedings of the International Electronic Packaging Technical Conference and Exhibition, Maui, HI, USA, 13 June 1999; pp. 211–217. [Google Scholar]

- Tsai, K.H.; Hwan, C.L.; Lin, M.J.; Huang, Y.S. Finite element based point stress criterion for predicting the notched strengths of composite plates. J. Mech. 2012, 28, 401–406. [Google Scholar] [CrossRef]

- Liu, D.S.; Cheng, K.L.; Zhuang, Z.W. Development of plate infinite element method for stress analysis of elastic bodies with singularities. J. Mech. 2013, 29, 481–492. [Google Scholar] [CrossRef]

- He, M.; Chen, Z.; Qi, G.J. Mechanical strength of thermally aged Sn-3.5Ag/N-P solder joints. Metall. Mater. Trans. A 2005, 36, 65–75. [Google Scholar] [CrossRef]

| Materials | Young’s Modulus (E) | Coefficient of Thermal Expansion (CTE) (ppm/°C) | Poisson’s Ratio |

|---|---|---|---|

| Si | 169.5 GPa | 3 | 0.28 |

| Cu | E = 122 GPa | 17 | 0.35 |

| Reference temperature (T) = 25 °C | |||

| Yield stress = 173 MPa | |||

| Tensile strength = 1.2 GPa | |||

| Passivation (Si3N4) | 155 GPa | 5 | 0.28 |

| Wafer-level underfill | 5.6 GPa@25C | 29.2 | 0.33 |

| SnAg solder | Temperature dependence | 22.5 | 0.4 |

| IMC (Ni3Sn4) | 85.6 GPa | −40 °C:16.3 | 0.31 |

| 25 °C:17.6 | |||

| 50 °C:18.1 | |||

| 125 °C:19.3 | |||

| Ni | 186 | 12.5 | 0.342 |

| Al | 72 GPa | 24 | 0.36 |

© 2017 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, C.-C. Effect of Wafer Level Underfill on the Microbump Reliability of Ultrathin-Chip Stacking Type 3D-IC Assembly during Thermal Cycling Tests. Materials 2017, 10, 1220. https://doi.org/10.3390/ma10101220

Lee C-C. Effect of Wafer Level Underfill on the Microbump Reliability of Ultrathin-Chip Stacking Type 3D-IC Assembly during Thermal Cycling Tests. Materials. 2017; 10(10):1220. https://doi.org/10.3390/ma10101220

Chicago/Turabian StyleLee, Chang-Chun. 2017. "Effect of Wafer Level Underfill on the Microbump Reliability of Ultrathin-Chip Stacking Type 3D-IC Assembly during Thermal Cycling Tests" Materials 10, no. 10: 1220. https://doi.org/10.3390/ma10101220

APA StyleLee, C.-C. (2017). Effect of Wafer Level Underfill on the Microbump Reliability of Ultrathin-Chip Stacking Type 3D-IC Assembly during Thermal Cycling Tests. Materials, 10(10), 1220. https://doi.org/10.3390/ma10101220