GaN Electric Vehicle Systems—A Comparative Review

Abstract

1. Introduction

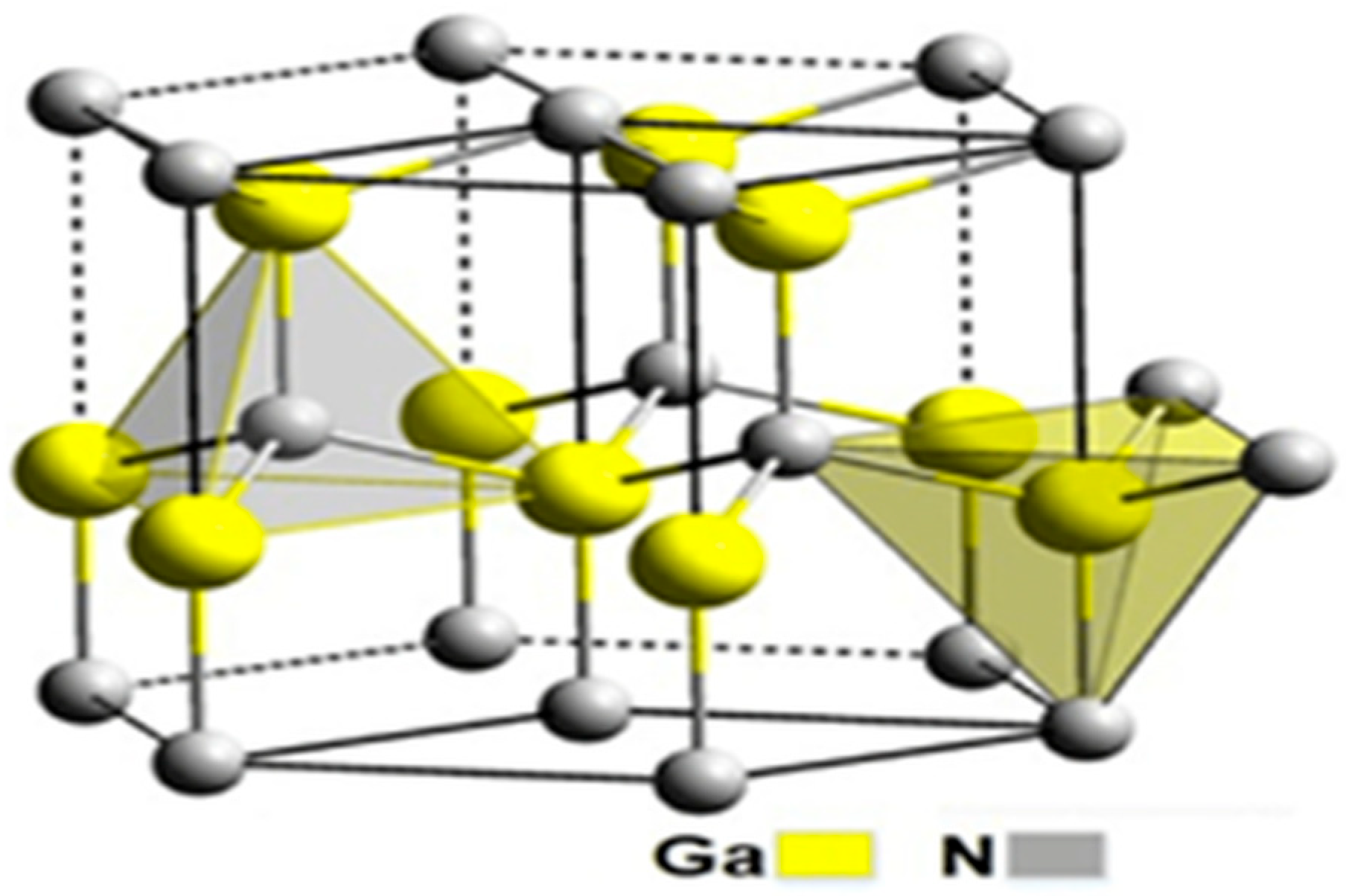

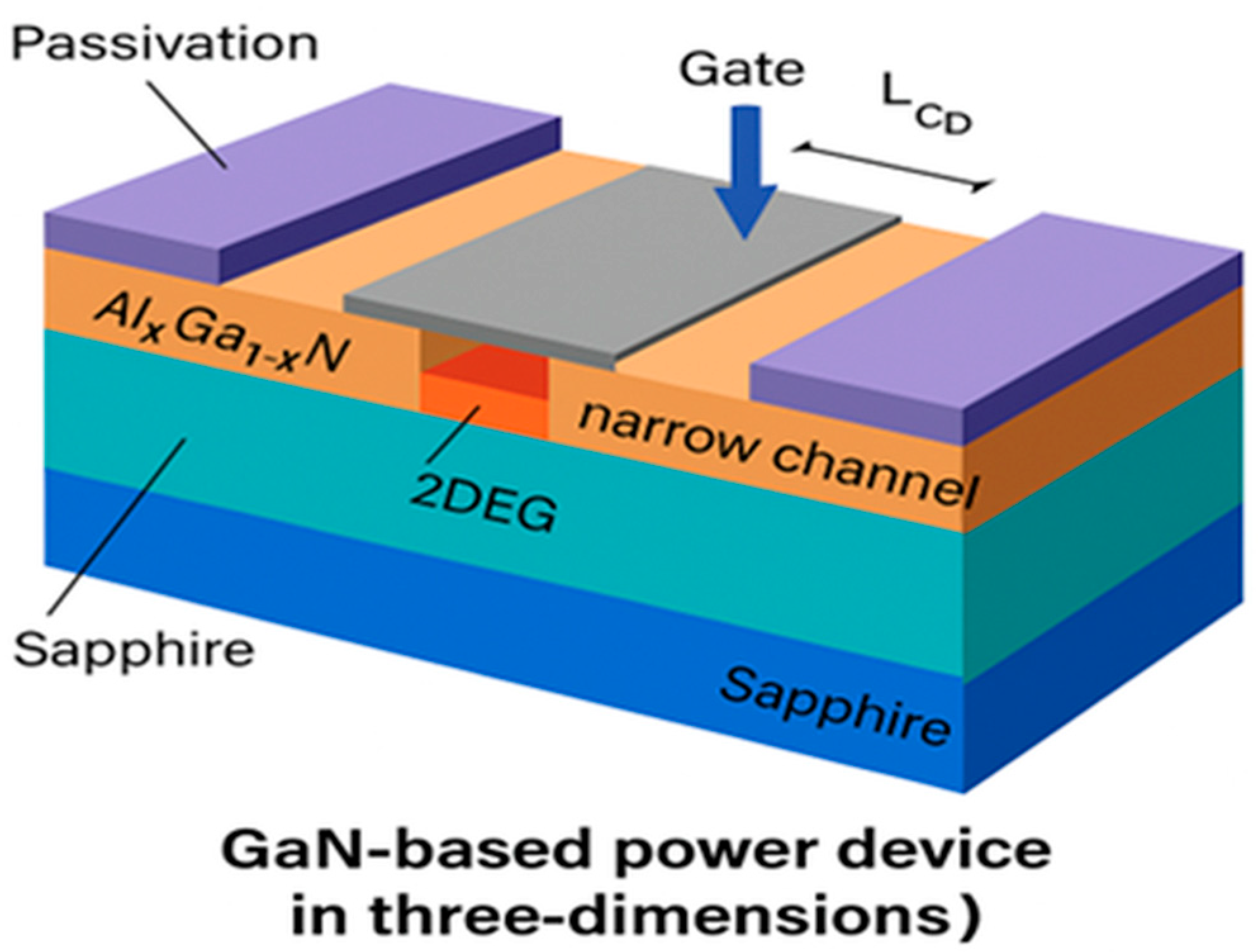

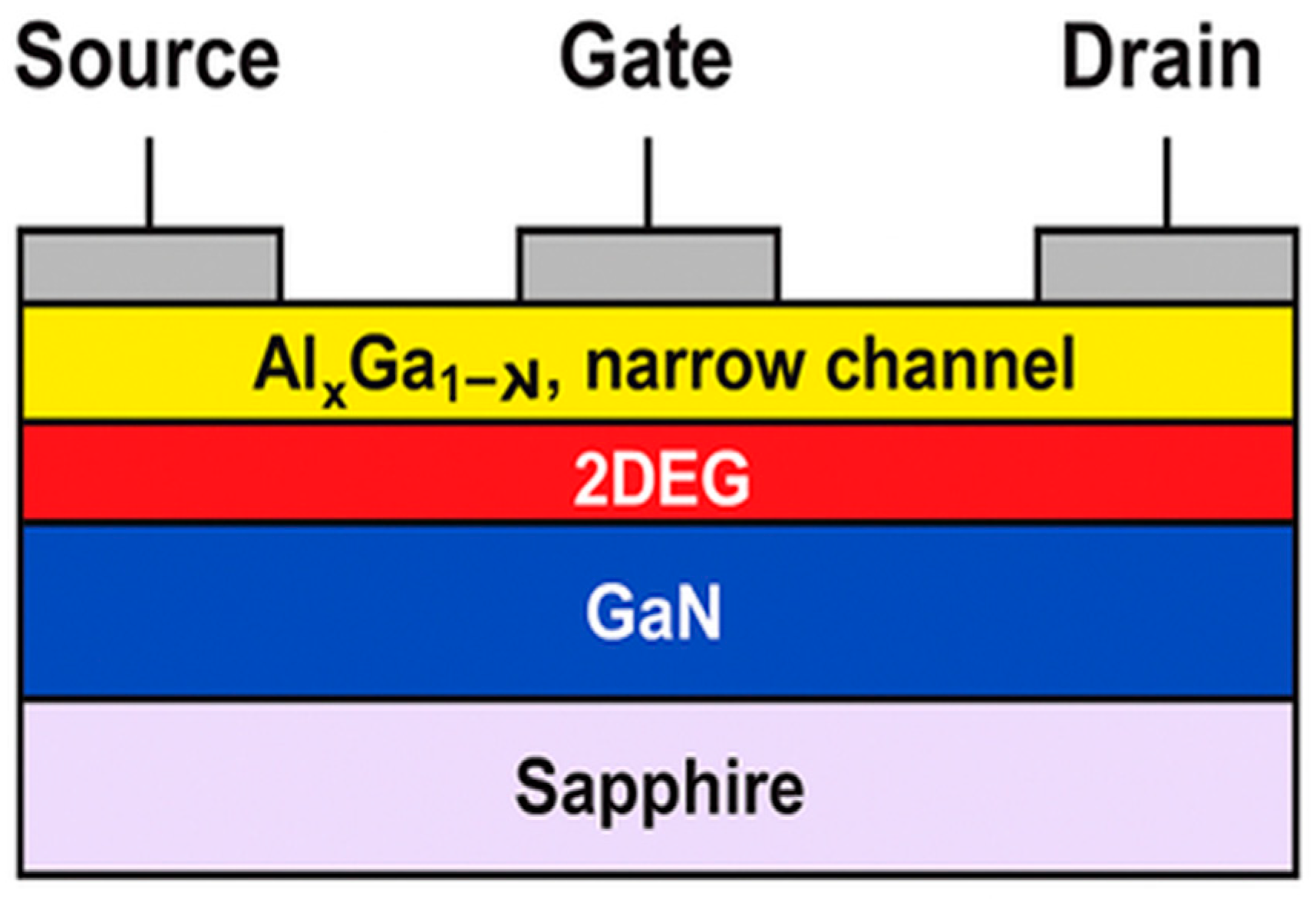

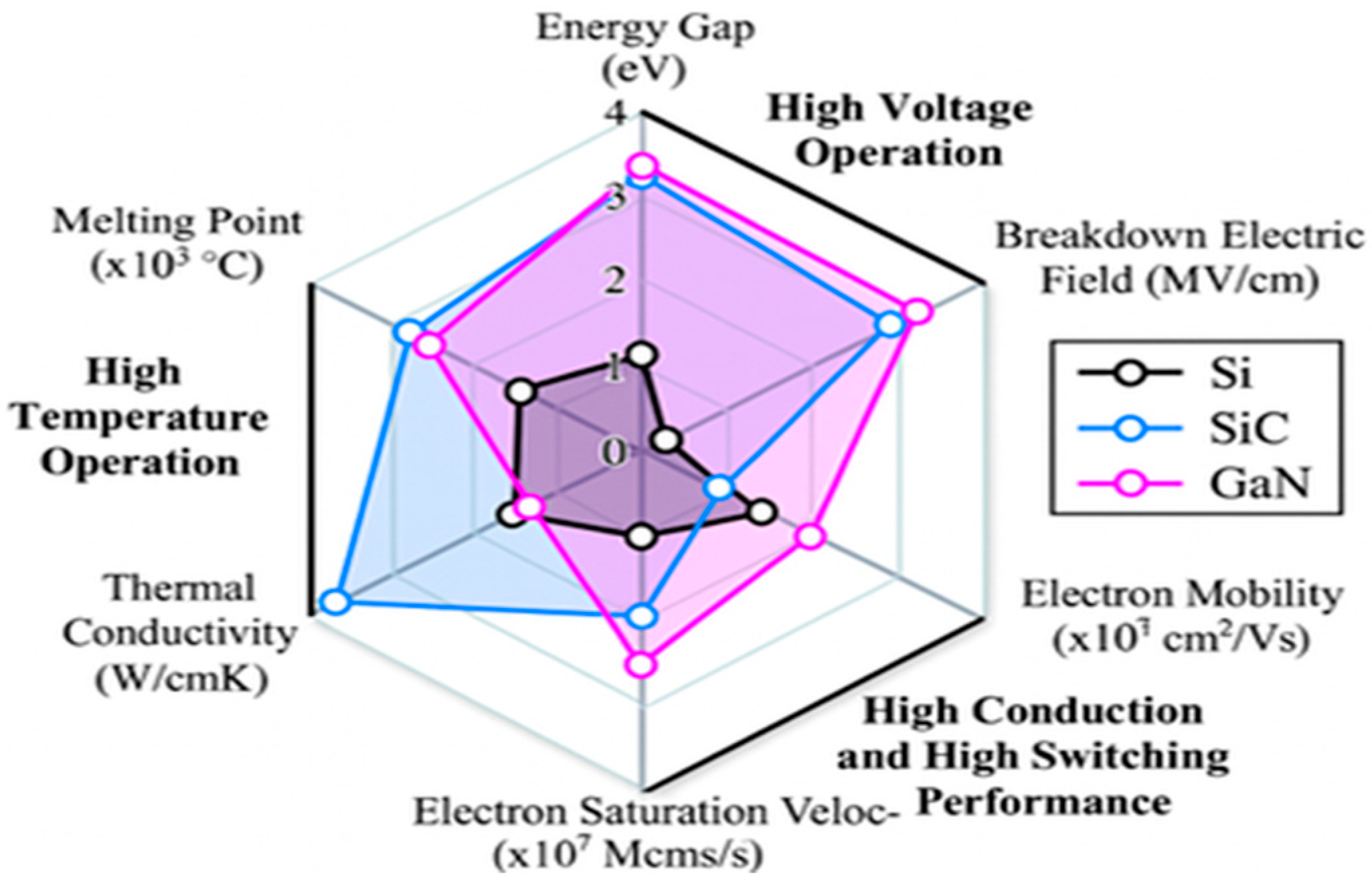

2. GaN Material/Device Background and Review Methodology

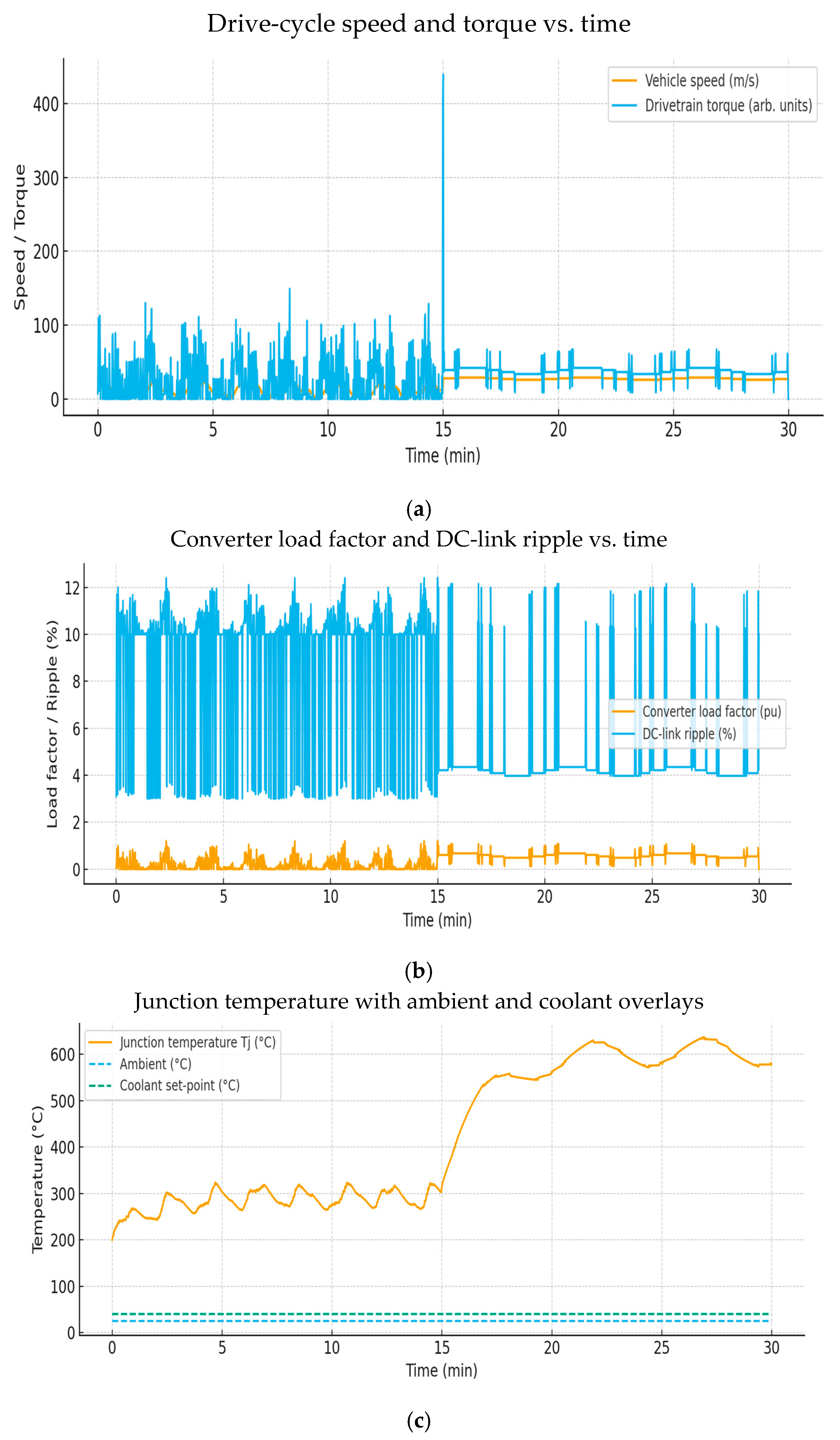

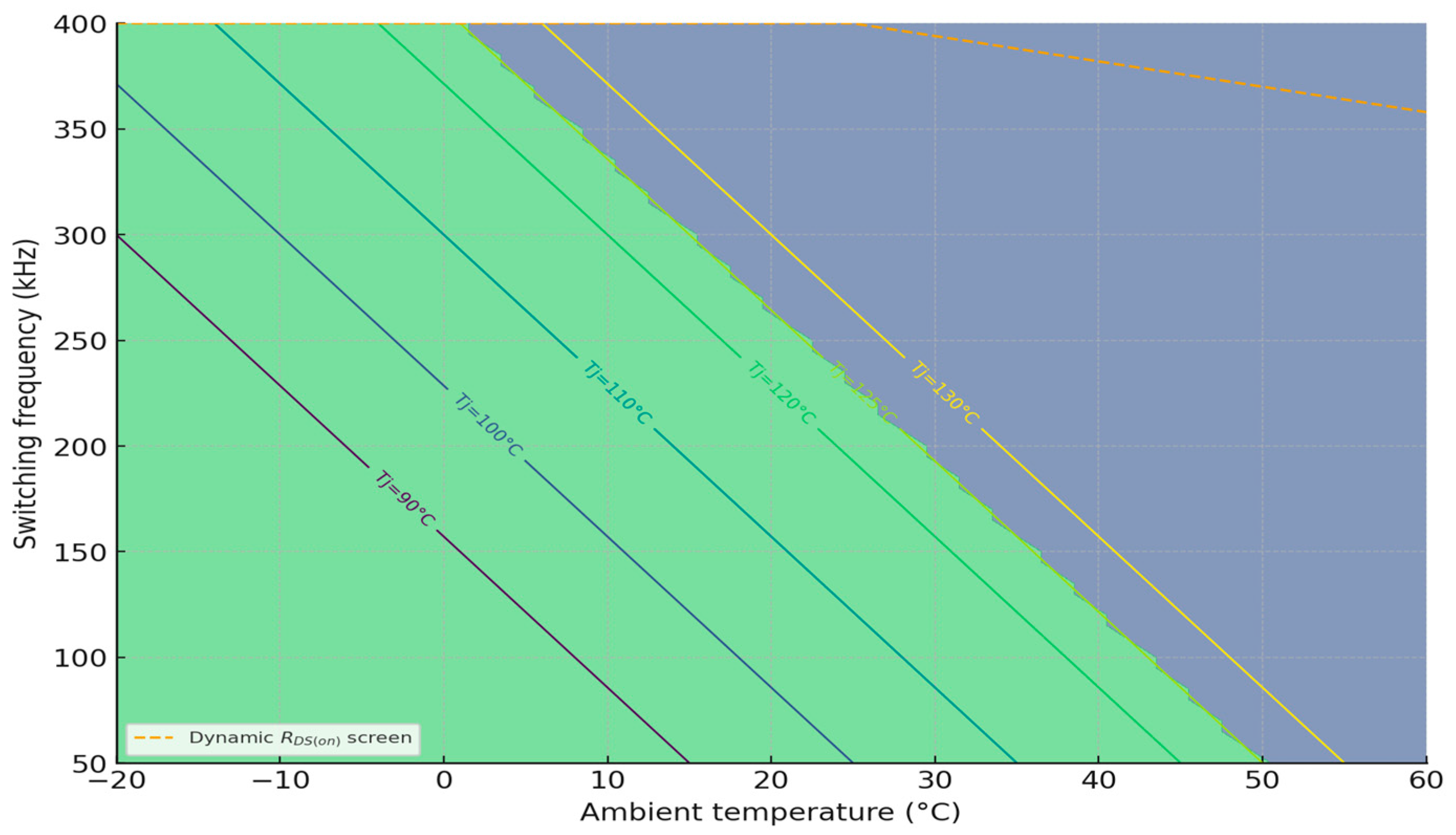

3. Reliability Under Real Drive Cycles and Linkage to the Vehicle Thermal Budget

- (i)

- Arrhenius-type acceleration for steady high-temperature wear mechanisms;

- (ii)

- Coffin–Manson accumulation for thermo-mechanical cycling;

- (iii)

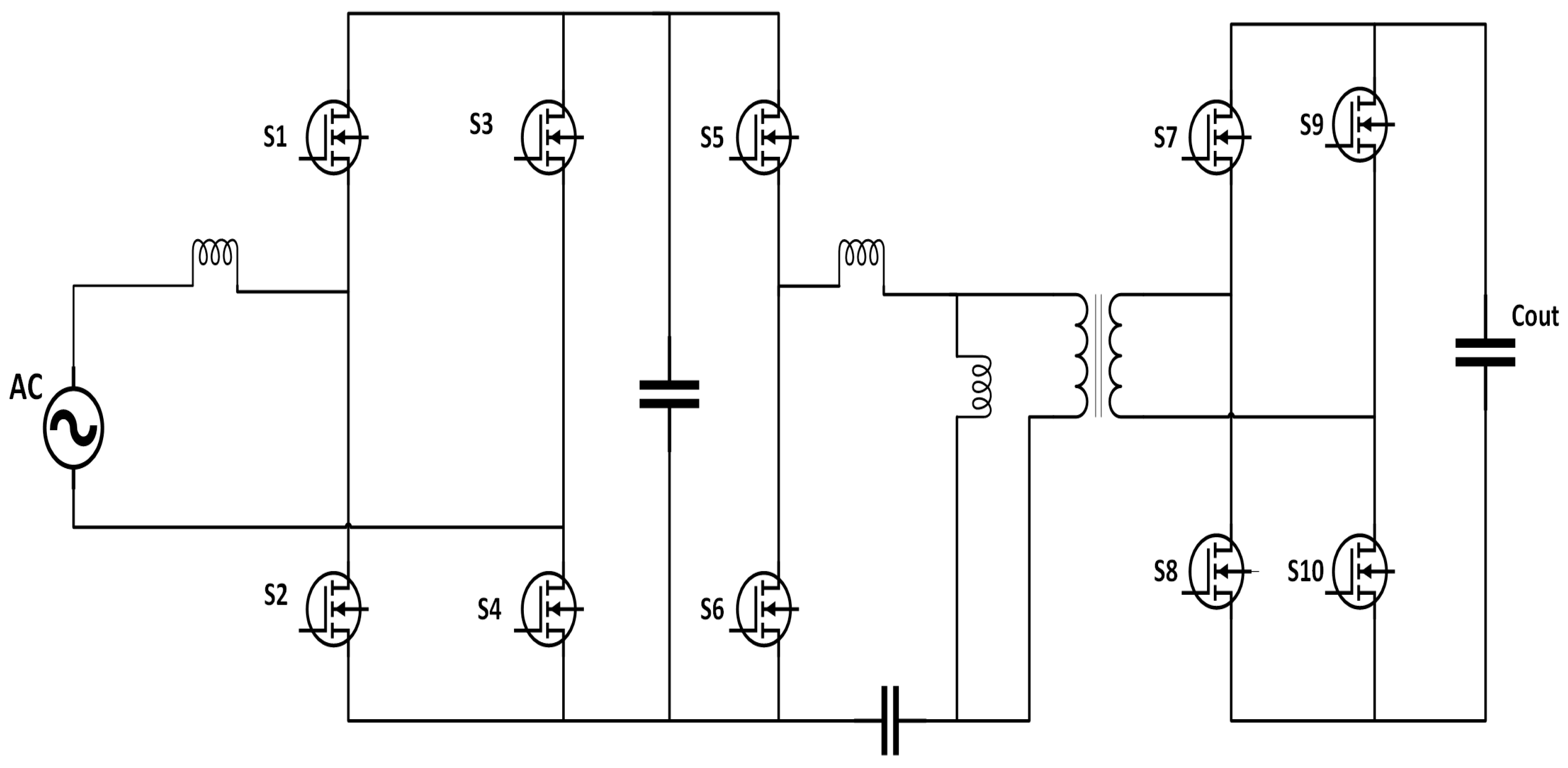

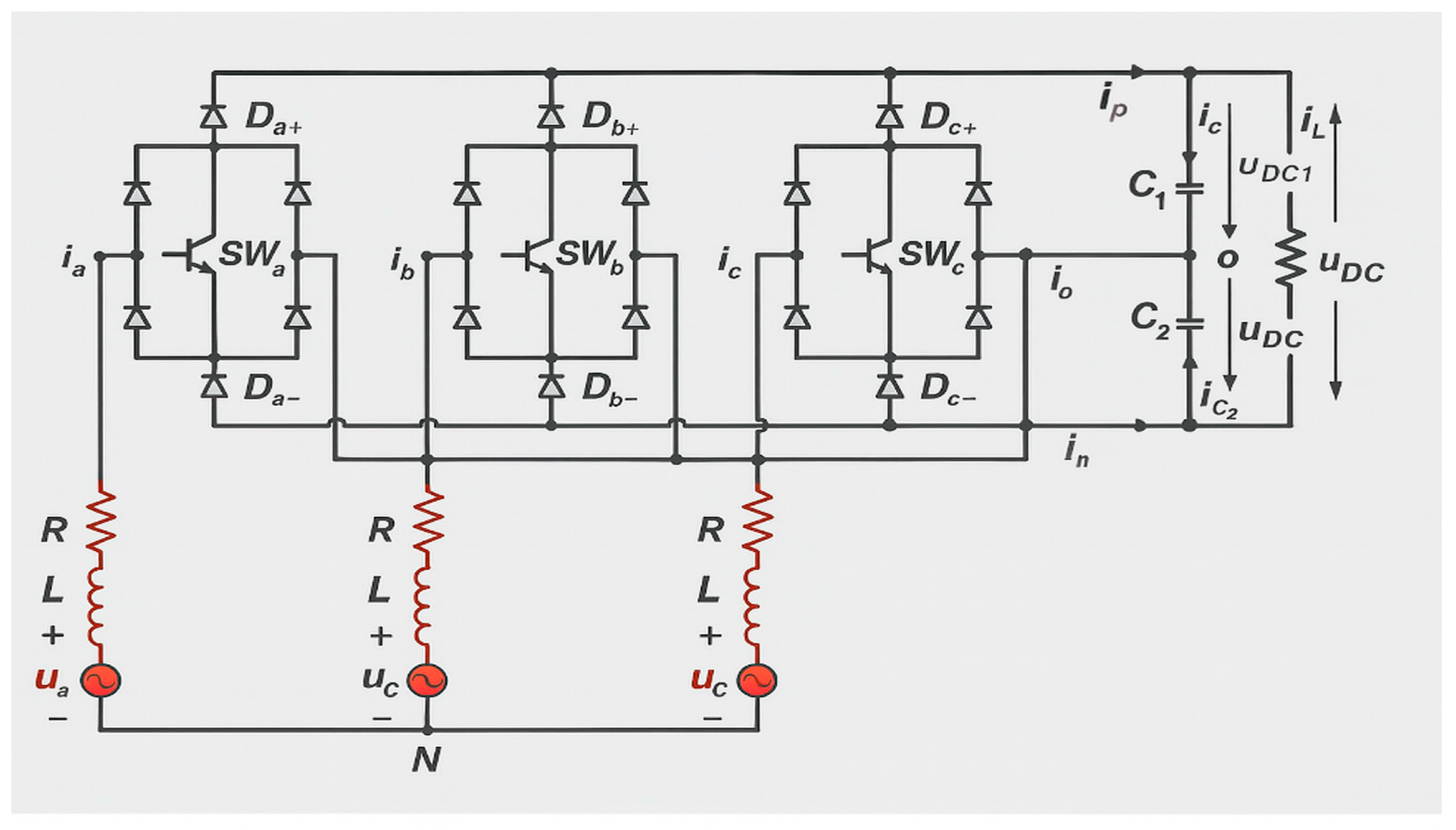

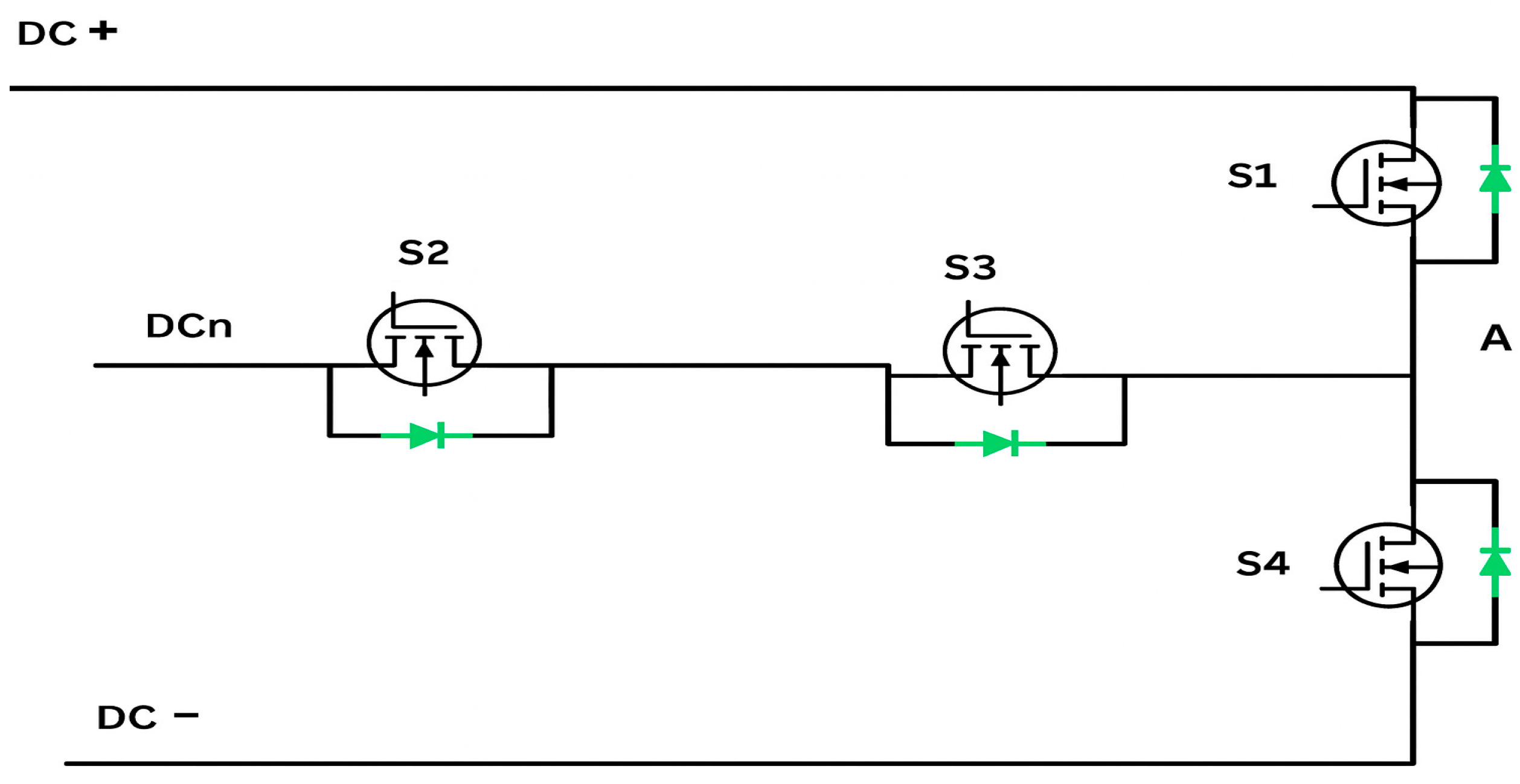

4. GaN-Based AC–DC Front Ends for 400 V/800 V EV Platforms

- Single-phase TP-PFC + resonant DC–DC (LLC/CLLC/DAB)

- b.

- Switching-loss scaling (3L vs. 2L)

- Conduction loss composition. For phase RMS current ,

- Common mode and EMI

- Vienna rectifier (Figure 8)—Unidirectional by default, simple modulation, very low switching loss from (8), and device stress limited by (5). It is a strong choice when peak efficiency and simplicity are priorities and vehicle-to-grid (V2G) is not required.

- T-type NPC (Figure 9)—Naturally bidirectional (V2G/V2H), with the same 3L stress relief. It requires neutral-point control per (7), careful commutation sequencing, and a higher driver/channel count.

- c.

- Quantitative selection rubric

- d.

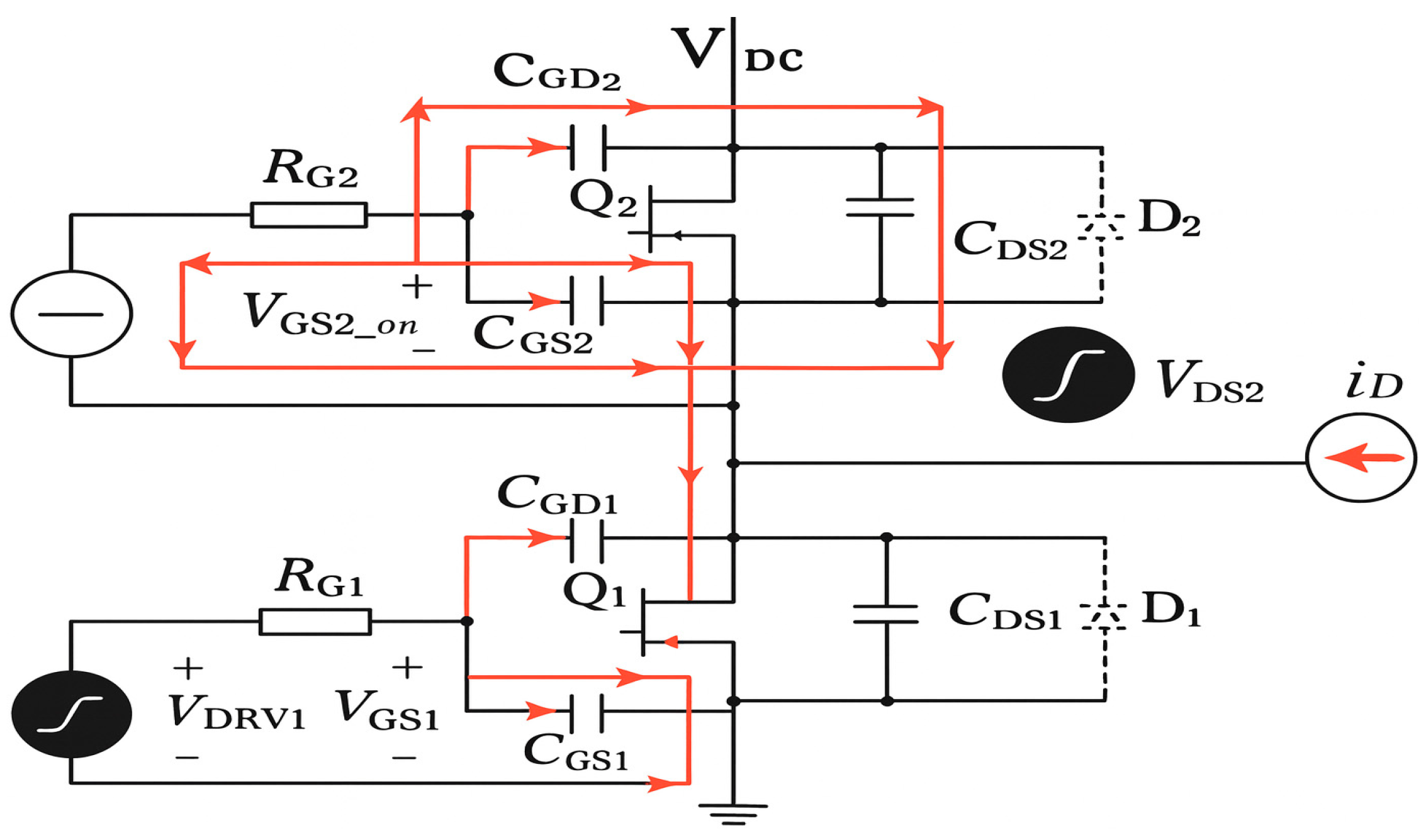

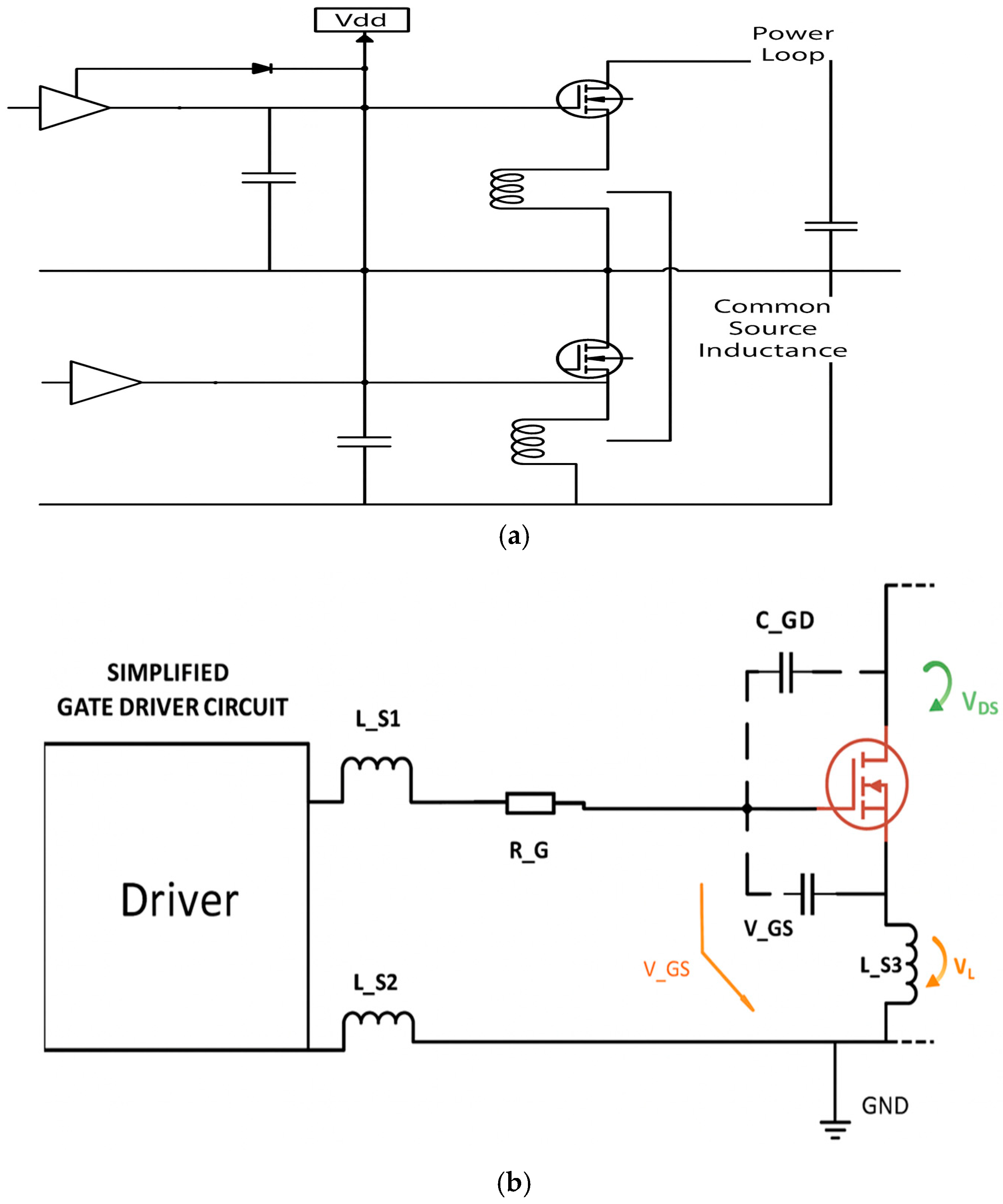

- Gate driver and parasitic control for GaN AC–DC legs (TP-PFC, Vienna, T-type).

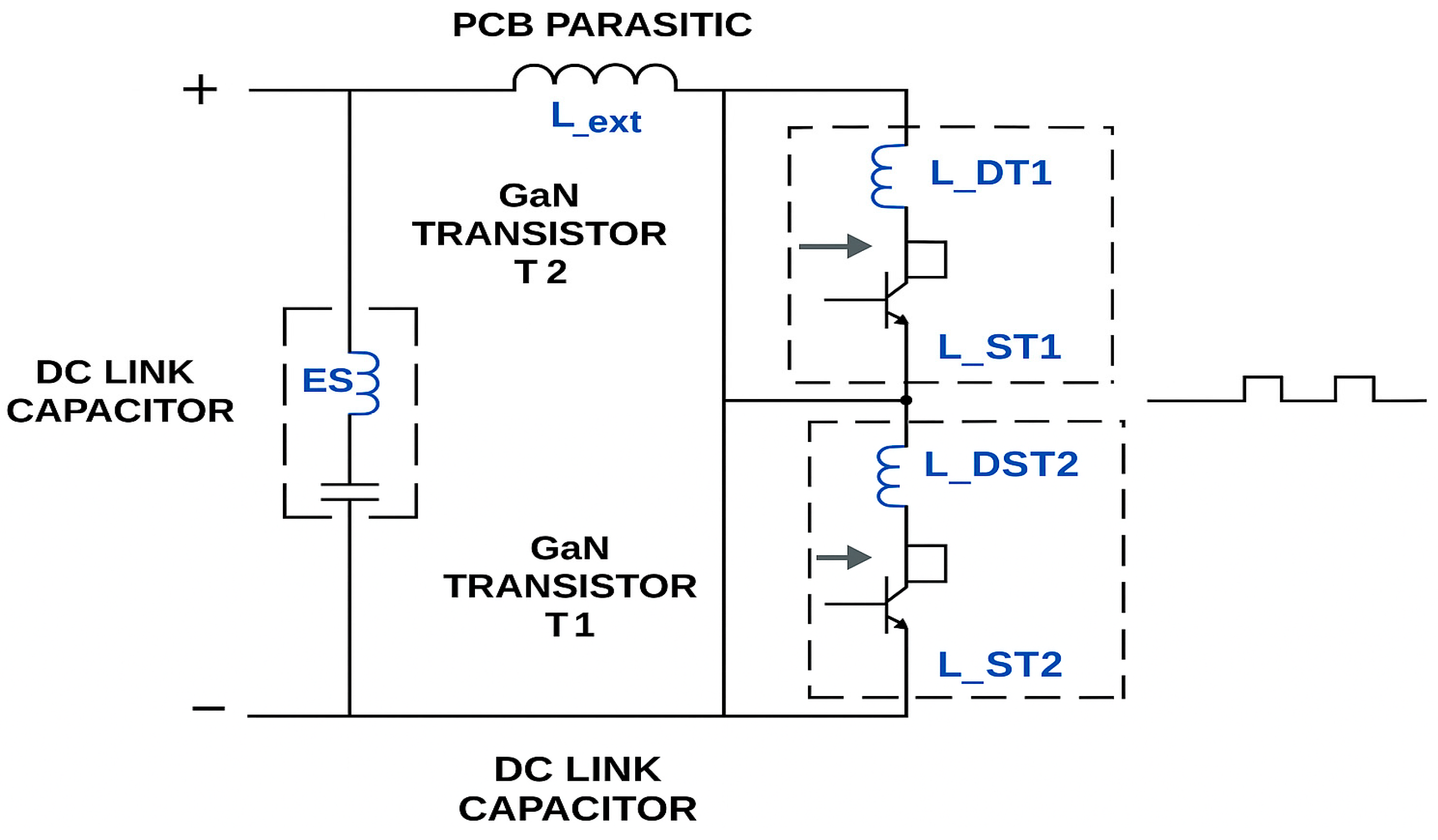

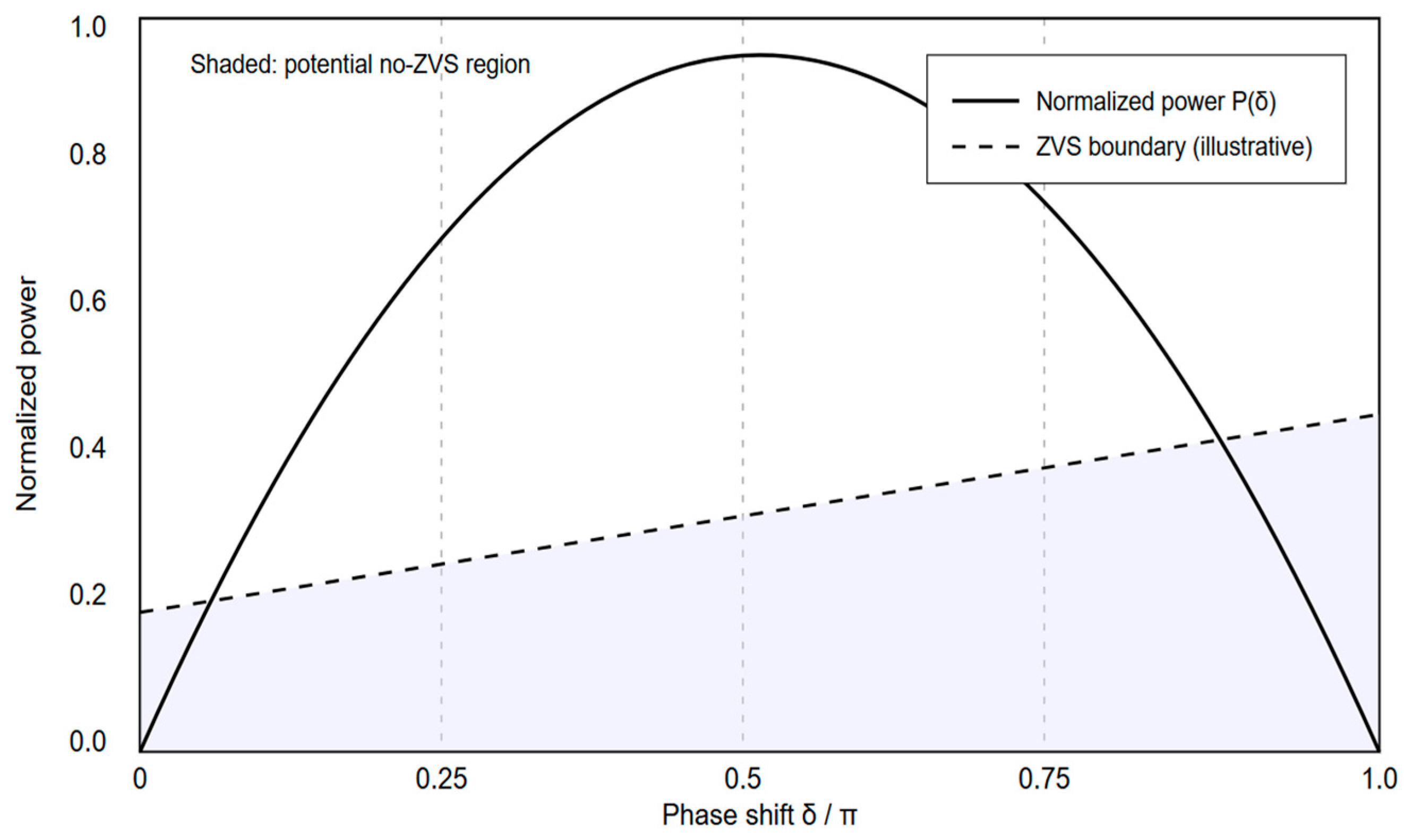

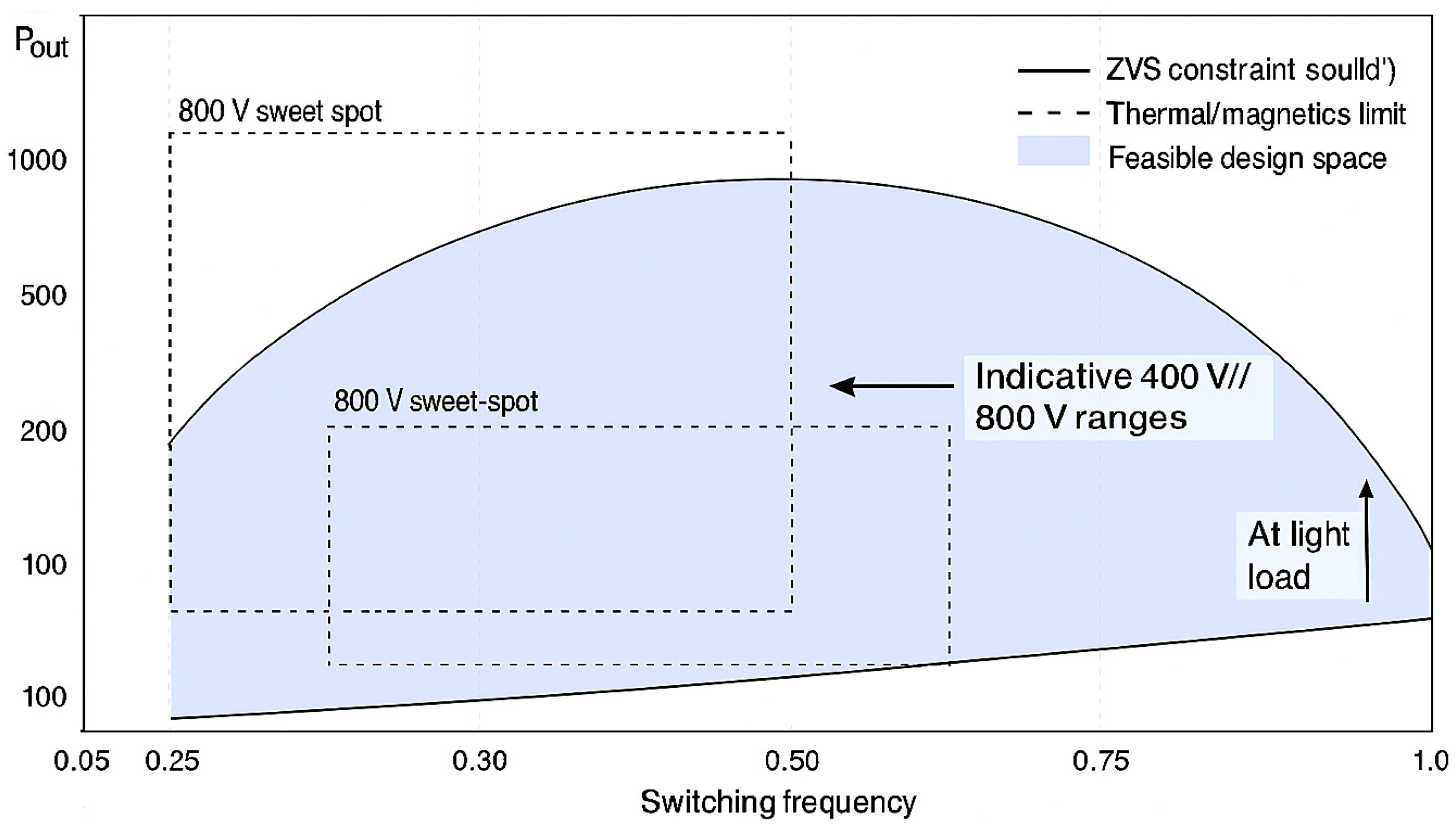

5. DC–DC Stages (LLC/CLLC/DAB): ZVS/ZCS and Scaling Trade-Offs

- I.

- Retain 650/700/900 V GaN in three-level bridges (keeping device well below rating).

- II.

- Driver tuning and parasitic in resonant DC–DC (LLC/CLLC/DAB).

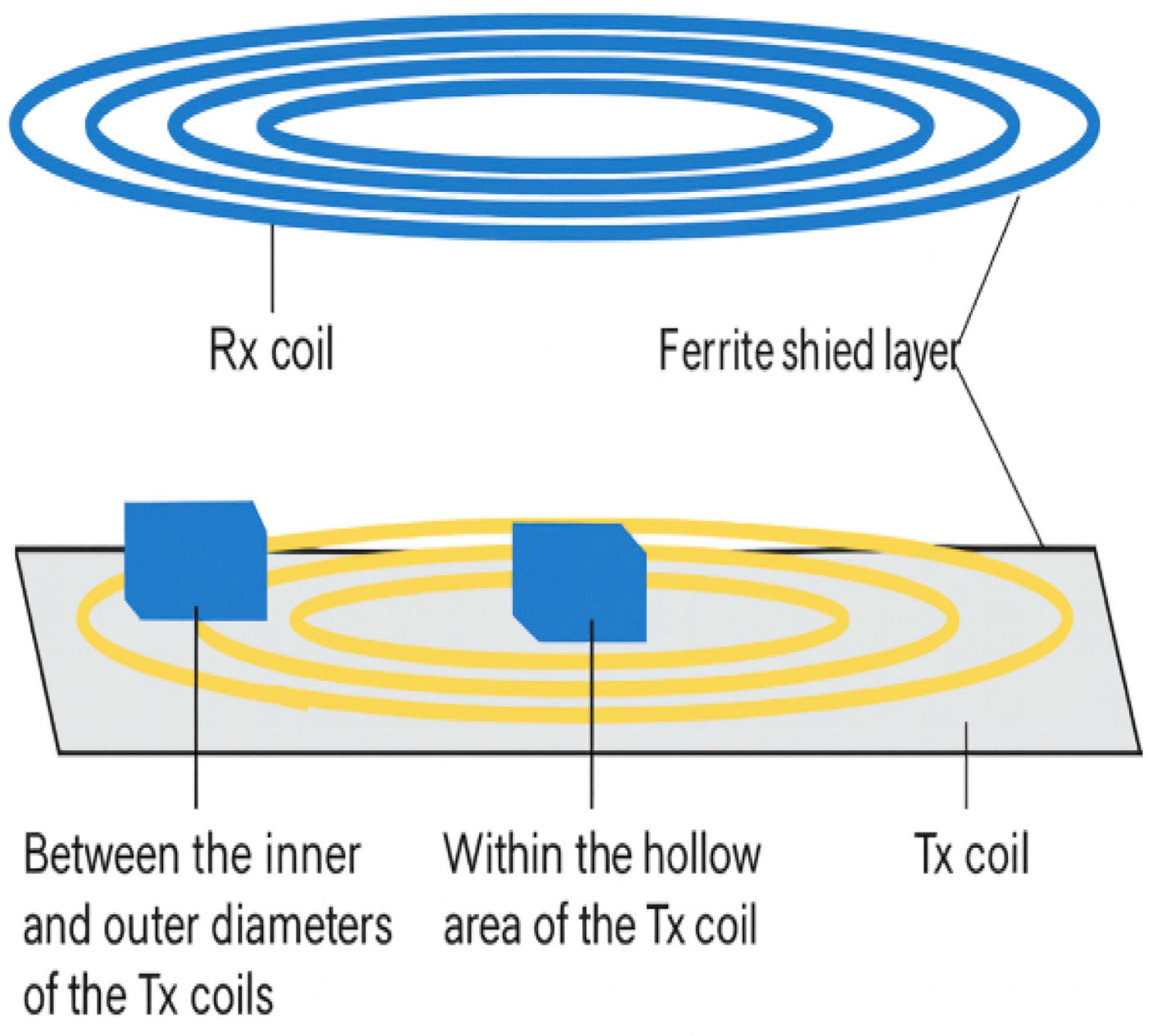

- GaN-Enabled Wireless Transfer and Multidimensional Propulsion Extensions

- I.

- Wireless Power Transfer (WPT) with Ferrite-Guided Circular Coils

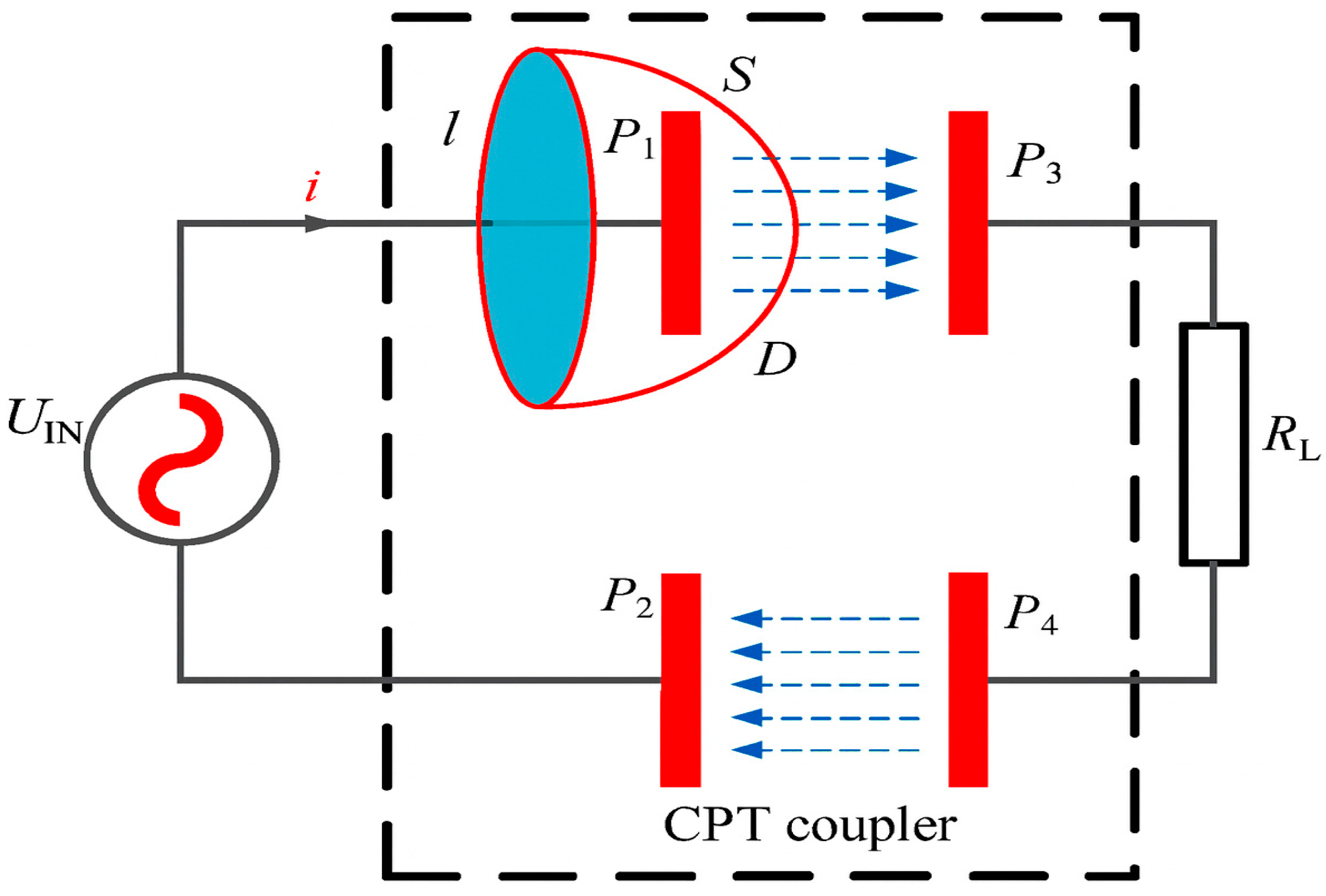

- II.

- Capacitive Power Transfer (CPT) and Compensation Converter Optimization

- III.

- Electrified Propulsion for Three-Dimensional Transportation

- IV.

- Reliability Mapping Across Converter Topologies

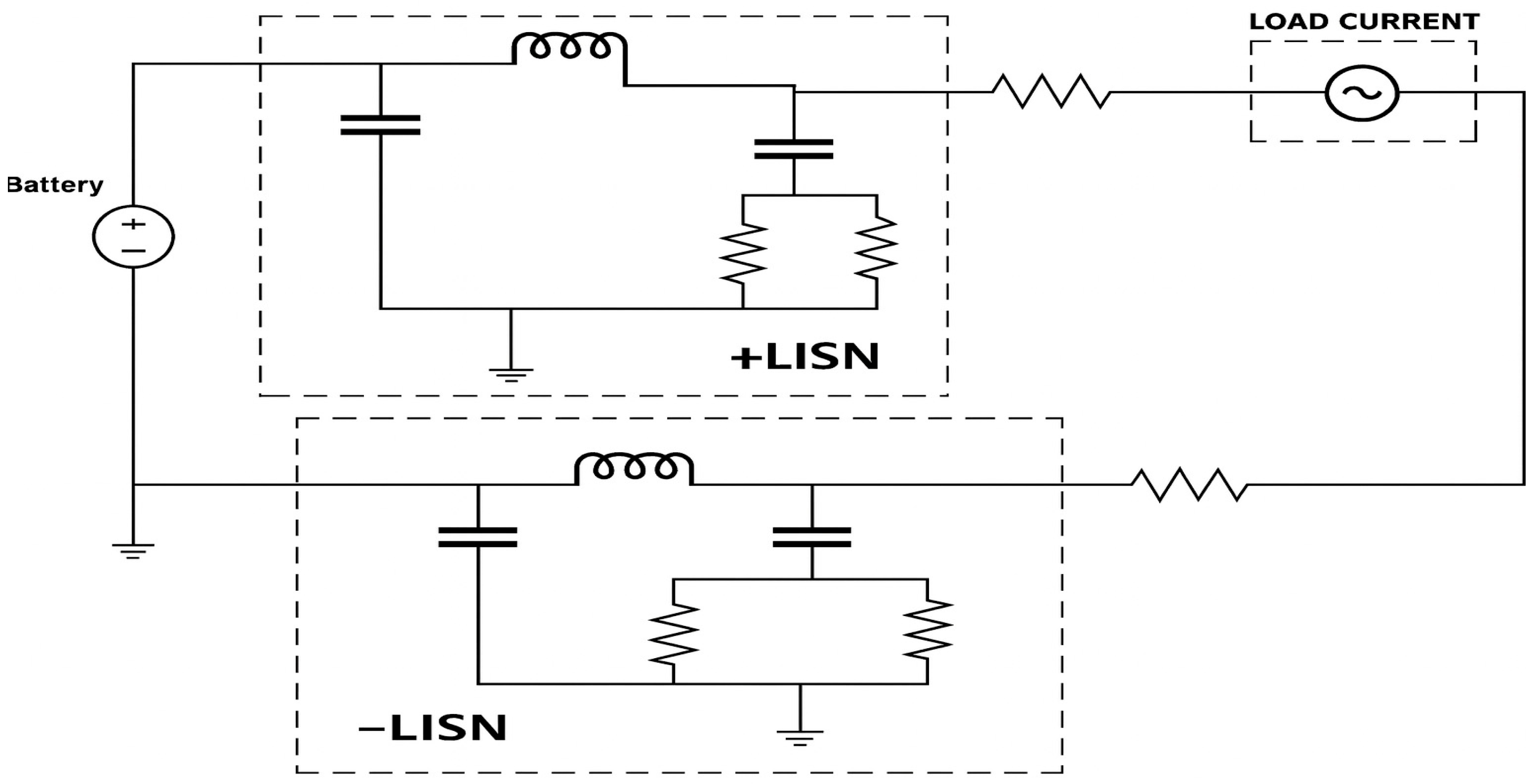

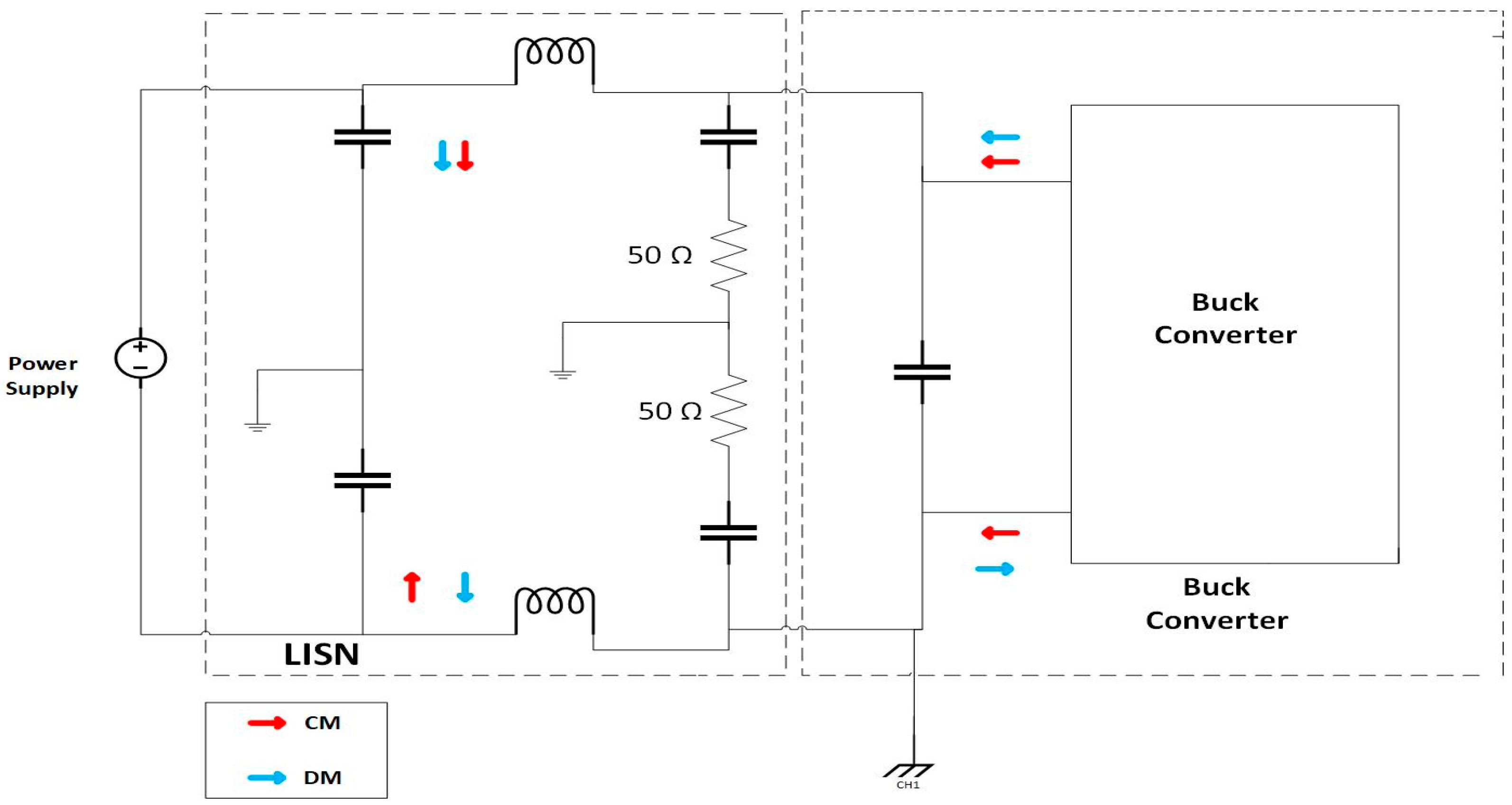

6. EMI and Compliance: Dual-LISN DM/CM Workflow and a Practical Topology-Selection Framework

- A.

- Dual-LISN representation with compact DM/CM emission models

- B.

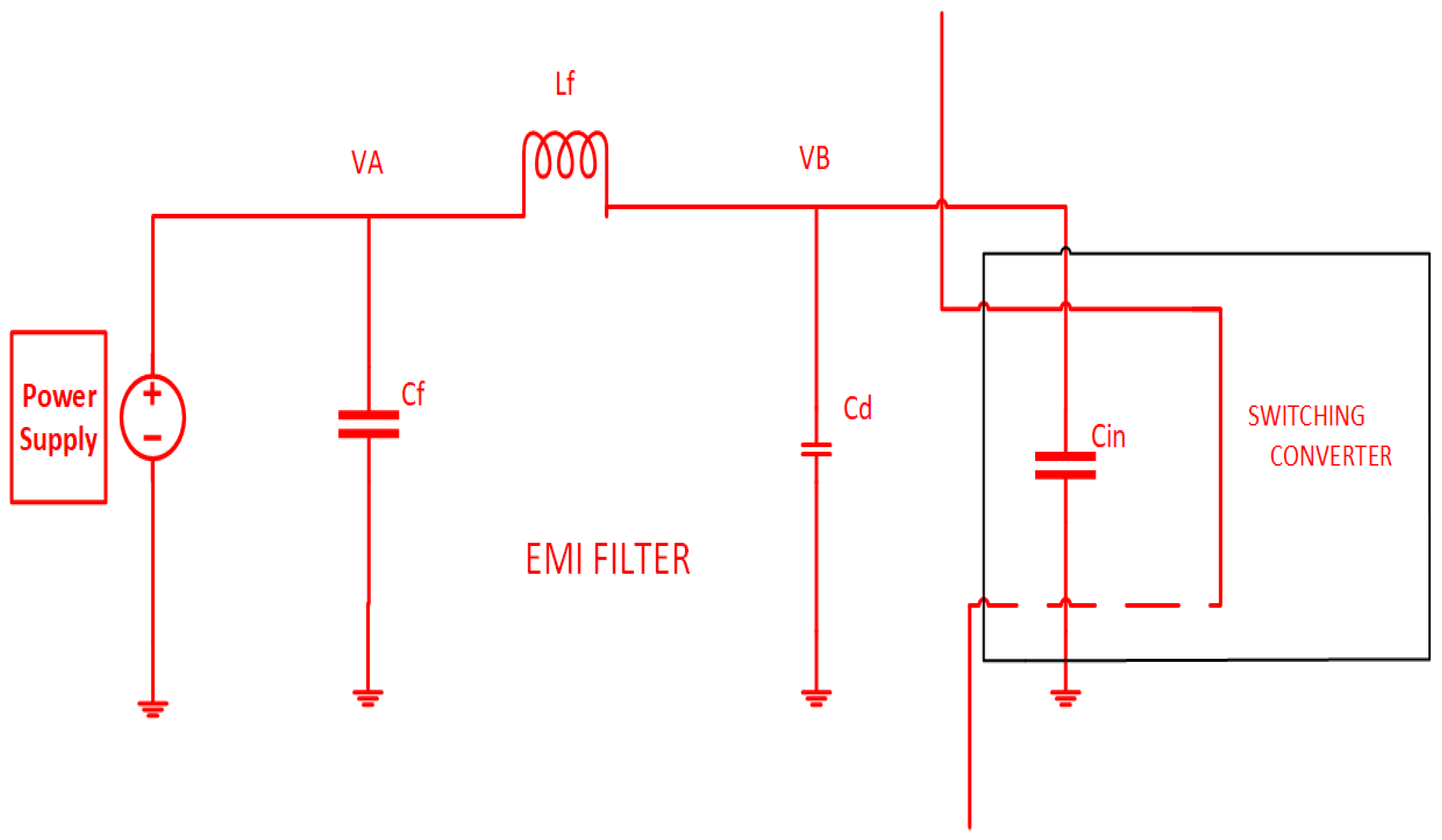

- From attenuation targets to realizable DM/CM networks, with integrated topology/edge-shaping selection and thermal co-constraints

- C.

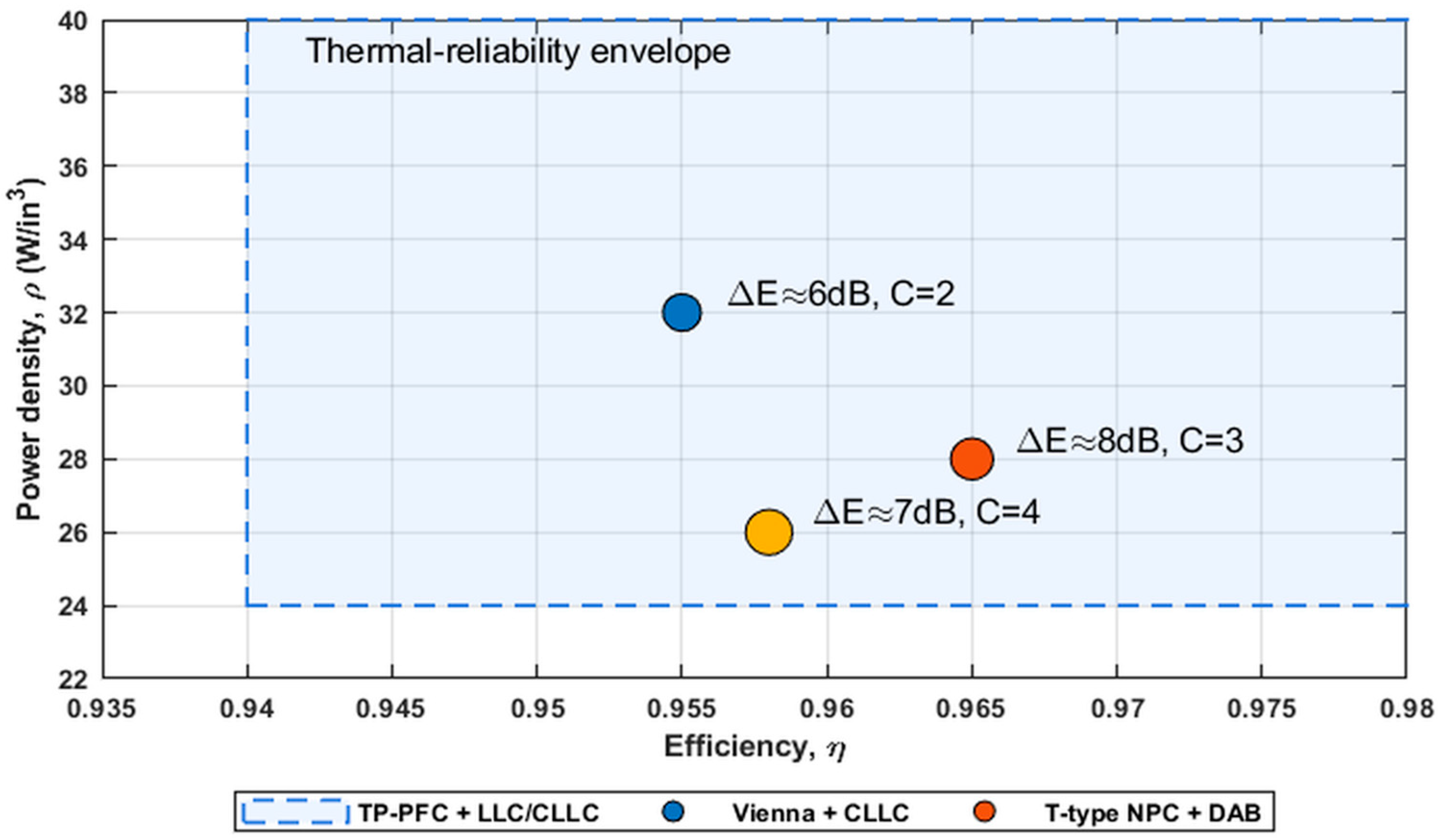

- Decision map linking EMI, efficiency, power density, and complexity

- Sufficient ZVS/ZCS margin from the resonant/bridge analysis;

- The derating map from Section 3 (junction-temperature limit and any dynamic screen);

- A compact DM/CM network that delivers from (34) with acceptable damping and from (40) [167].

- Efficiency: η at rated load (and a light-load point).

- Power density: ρ in W/L (converter volume excludes cabling).

- EMI margin: ΔE = (measured DM/CM level − limit) in dBµV, negative is a compliant margin.

- Power-processing factor: PPF = (Equation (30)).

- Thermal headroom: = − under mission profile load (Equation (4)).

7. Conclusions and Roadmap

Funding

Data Availability Statement

Conflicts of Interest

References

- International Energy Agency (IEA). Global EV Outlook 2024; International Energy Agency (IEA): Paris, France, 2024. [Google Scholar]

- Musumeci, S.; Barba, V. Gallium Nitride Power Devices in Power Electronics Applications: State of Art and Perspectives. Energies 2023, 16, 3894. [Google Scholar] [CrossRef]

- Erramilli, A.; Roughan, M.; Veitch, D.; Willinger, W. Self-Similar Traffic and Network Dynamics. Proc. IEEE 2002, 90, 800–819. [Google Scholar] [CrossRef]

- Udabe, A.; Baraia-Etxaburu, I.; Diez, D.G. Gallium Nitride Power Devices: A State of the Art Review. IEEE Access 2023, 11, 48628–48650. [Google Scholar] [CrossRef]

- Chen, K.J.; Häberlen, O.; Lidow, A.; Tsai, C.L.; Ueda, T.; Uemoto, Y.; Wu, Y. GaN-on-Si Power Technology: Devices and Applications. IEEE Trans. Electron. Devices 2017, 64, 779–795. [Google Scholar] [CrossRef]

- Reimers, J.; Dorn-Gomba, L.; Mak, C.; Emadi, A. Automotive Traction Inverters: Current Status and Future Trends. IEEE Trans. Veh. Technol. 2019, 68, 3337–3350. [Google Scholar] [CrossRef]

- Yilmaz, M.; Krein, P.T. Review of Battery Charger Topologies, Charging Power Levels, and Infrastructure for Plug-In Electric and Hybrid Vehicles. IEEE Trans. Power Electron. 2013, 28, 2151–2169. [Google Scholar] [CrossRef]

- Rahman, K.F.; Falina, S.; Mohamed, M.F.P.; Kawarada, H.; Syamsul, M. The Role of Gallium Nitride in the Evolution of Electric Vehicles: Energy Applications, Technology, and Challenges. Appl. Phys. Rev. 2024, 11, 031322. [Google Scholar] [CrossRef]

- Soomro, H.A.; Khir, M.H.B.M.; Zulkifli, S.A.B.M.; Abro, G.E.M.; Abualnaeem, M.M. Applications of Wide Bandgap Semiconductors in Electric Traction Drives: Current Trends and Future Perspectives. Results Eng. 2025, 26, 104679. [Google Scholar] [CrossRef]

- Dutta, S.; Bauman, J. An Overview of 800 V Passenger Electric Vehicle Onboard Chargers: Challenges, Topologies, and Control. IEEE Access 2024, 12, 105850–105864. [Google Scholar] [CrossRef]

- Thermal Management of Electrified Vehicles—A Review. Available online: https://www.mdpi.com/1996-1073/15/4/1326 (accessed on 6 October 2025).

- Chakraborty, S.; Hasan, M.M.; Paul, M.; Tran, D.-D.; Geury, T.; Davari, P.; Blaabjerg, F.; Baghdadi, M.E.; Hegazy, O. Real-Life Mission Profile-Oriented Lifetime Estimation of a SiC Interleaved Bidirectional HV DC/DC Converter for Electric Vehicle Drivetrains. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 5142–5167. [Google Scholar] [CrossRef]

- Rahman, S.M.I.; Moghassemi, A.; Arsalan, A.; Timilsina, L.; Chamarthi, P.K.; Papari, B.; Ozkan, G.; Edrington, C.S. Emerging Trends and Challenges in Thermal Management of Power Electronic Converters: A State of the Art Review. IEEE Access 2024, 12, 50633–50672. [Google Scholar] [CrossRef]

- Abramushkina, E.; Zhaksylyk, A.; Geury, T.; El Baghdadi, M.; Hegazy, O. A Thorough Review of Cooling Concepts and Thermal Management Techniques for Automotive WBG Inverters: Topology, Technology and Integration Level. Energies 2021, 14, 4981. [Google Scholar] [CrossRef]

- Moreno, G.; Narumanchi, S.; Feng, X.; Anschel, P.; Myers, S.; Keller, P. Electric-Drive Vehicle Power Electronics Thermal Management: Current Status, Challenges, and Future Directions. J. Electron. Packag. 2022, 144, 011004. [Google Scholar] [CrossRef]

- Research Assistant-Bohrium|AI for Science with Global Scientists. Available online: https://www.bohrium.com/paper-details/800-v-electric-vehicle-powertrains-review-and-analysis-of-benefits-challenges-and-future-trends/812529581234847745-3873?utm_source=chatgpt.com (accessed on 6 October 2025).

- Friedli, T.; Hartmann, M.; Kolar, J.W. The Essence of Three-Phase PFC Rectifier Systems—Part II. IEEE Trans. Power Electron. 2014, 29, 543–560. [Google Scholar] [CrossRef]

- Comparison of Unidirectional Three- and Four-Wire-Based Boost PFC-Rectifier Topologies for Non-Isolated Three-Phase EV On-Board Chargers Under Common-Mode Aspects. Available online: https://www.researchgate.net/publication/356836567_Comparison_of_Unidirectional_Three-_and_Four-Wire-Based_Boost_PFC-Rectifier_Topologies_for_Non-Isolated_Three-Phase_EV_On-Board_Chargers_Under_Common-Mode_Aspects (accessed on 6 October 2025).

- Meneghini, M.; De Santi, C.; Abid, I.; Buffolo, M.; Cioni, M.; Khadar, R.A.; Nela, L.; Zagni, N.; Chini, A.; Medjdoub, F.; et al. GaN-Based Power Devices: Physics, Reliability, and Perspectives. J. Appl. Phys. 2021, 130, 181101. [Google Scholar] [CrossRef]

- Texas Instruments. Bidirectional CLLLC Resonant Dual Active Bridge (DAB) Reference Design for HEV/EV Onboard Charger; Texas Instruments: Dallas, TX, USA, 2024. [Google Scholar]

- Reali, A.; Alemanno, A.; Ronchi, F.; Rossi, C.; Florian, C. Development of GaN-Based, 6.6 kW, 450 V, Bi-Directional On-Board Charger with Integrated 1 kW, 12 V Auxiliary DC-DC Converter with High Power Density. Micromachines 2024, 15, 1470. [Google Scholar] [CrossRef]

- Texas Instruments. GaN-Based, 6.6-kW, Bidirectional, Onboard Charger Reference Design; Texas Instruments: Dallas, TX, USA, 2021. [Google Scholar]

- Chou, P.-C.; Hsieh, T.-E.; Cheng, S.; Del Alamo, J.A.; Chang, E.Y. Comprehensive Dynamic On-Resistance Assessments in GaN-on-Si MIS-HEMTs for Power Switching Applications. Semicond. Sci. Technol. 2018, 33, 055012. [Google Scholar] [CrossRef]

- Wang, W.; Liang, Y.; Zhang, M.; Lin, F.; Wen, F.; Wang, H. Mechanism Analysis of Dynamic On-State Resistance Degradation for a Commercial GaN HEMT Using Double Pulse Test. Electronics 2021, 10, 1202. [Google Scholar] [CrossRef]

- Doublet, M.; Defrance, N.; Okada, E.; Pace, L.; Duquesne, T.; Emilien, B.; Yvon, A.; Idir, N.; De Jaeger, J.-C. Investigation of Current Collapse Mechanism on AlGaN/GaN Power Diodes. Electronics 2023, 12, 2007. [Google Scholar] [CrossRef]

- Alemanno, A.; Santarelli, A.; Sangiorgi, E.; Florian, C. Characterization of the Dynamic RON of 600 V GaN Switches under Operating Conditions. Electronics 2023, 12, 943. [Google Scholar] [CrossRef]

- Barbato, A.; Barbato, M.; Meneghini, M.; Silvestri, M.; Detzel, T.; Haeberlen, O.; Spiazzi, G.; Meneghesso, G.; Zanoni, E. Fast System to Measure the Dynamic On-Resistance of on-Wafer 600 V Normally off GaN HEMTs in Hard-Switching Application Conditions. IET Power Electron. 2020, 13, 2390–2397. [Google Scholar] [CrossRef]

- Alemanno, A.; Angelotti, A.M.; Gibiino, G.P.; Santarelli, A.; Sangiorgi, E.; Florian, C. A Reconfigurable Setup for the On-Wafer Characterization of the Dynamic RON of 600 V GaN Switches at Variable Operating Regimes. Electronics 2023, 12, 1063. [Google Scholar] [CrossRef]

- Huang, Z.-H.; Tang, S.-W.; Fan, C.-T.; Lin, M.-C.; Wu, T.-L. Dynamic On-Resistance Stability of SiC and GaN Power Devices during High-Frequency (100–300 kHz) Hard Switching and Zero Voltage Switching Operations. Microelectron. Reliab. 2023, 145, 114983. [Google Scholar] [CrossRef]

- Thönnessen, A.; Baumgaertner, J.; Fronczek, C.; De Doncker, R.W. Comparison of Switching Losses and Dynamic on Resistance of 600 V-Class GaN HEMTs. In Proceedings of the PCIM Europe 2024; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nürnberg, Germany, 11–13 June 2024; VDE Verlag Gmbh: Berlin, Germany, 2024. ISBN 978-3-8007-6262-0. [Google Scholar]

- CISPR 25:2021; Vehicles, Boats and Internal Combustion Engines—Radio Disturbance Characteristics—Limits and Methods of Measurement for the Protection of On-Board Receivers. International Electrotechnical Commission: Geneva, Switzerland, 2021.

- An Experimental Study on Artificial Intelligence-Based Prediction of Capacitance–Voltage Parameters of Polymer-Interface 6H-SiC/MEH-PPV/Al Schottky Diodes-Güzel-2022-Physica Status Solidi (a)-Wiley Online Library. Available online: https://onlinelibrary.wiley.com/doi/epdf/10.1002/pssa.202100821 (accessed on 6 October 2025).

- Temperature-Dependent Dynamic RDS, on Under Different Operating Conditions in Enhancement-Mode GaN HEMTs-Li-2020-IET Power Electronics-Wiley Online Library. Available online: https://ietresearch.onlinelibrary.wiley.com/doi/10.1049/iet-pel.2019.0540 (accessed on 6 October 2025).

- del Alamo, J.A.; Joh, J. GaN HEMT Reliability. Microelectron. Reliab. 2009, 49, 1200–1206. [Google Scholar] [CrossRef]

- Wang, H.; Blaabjerg, F. Power Electronics Reliability: State of the Art and Outlook. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 6476–6493. [Google Scholar] [CrossRef]

- Agirrezabala, E.; Aizpuru, I.; Garrido, D.; Portillo, A. Reliability of Power Semiconductor Modules: A State-of-the-Art Review. IEEE Open J. Power Electron. 2025, 6, 1036–1067. [Google Scholar] [CrossRef]

- Shen, J.; Yang, C.; Jing, L.; Li, P.; Wu, H.; Huang, Z.; Hu, S. A Novel Evaluation Methodology for the Reliability and Lifetime of 200 mm E-Mode GaN-on-Si Power HEMTs. IEEE Trans. Power Electron. 2023, 38, 6073–6080. [Google Scholar] [CrossRef]

- Lumbreras, D.; Vilella, M.; Zaragoza, J.; Berbel, N.; Jordà, J.; Collado, A. Effect of the Heat Dissipation System on Hard-Switching GaN-Based Power Converters for Energy Conversion. Energies 2021, 14, 6287. [Google Scholar] [CrossRef]

- Pace, L.; Idir, N.; Duquesne, T.; De Jaeger, J.-C. Parasitic Loop Inductances Reduction in the PCB Layout in GaN-Based Power Converters Using S-Parameters and EM Simulations. Energies 2021, 14, 1495. [Google Scholar] [CrossRef]

- Wang, L.; Li, Z.; Zheng, H. Investigation of Parallel and Orthogonal MIMO Antennas with Two-Notched Structures for Ultra-Wideband Application. Micromachines 2023, 14, 1406. [Google Scholar] [CrossRef]

- Tahir, M.; Hu, S.; He, X. Performance Improvement Strategies for Discrete Wide Bandgap Devices: A Systematic Review. Front. Energy Res. 2021, 9, 788689. [Google Scholar] [CrossRef]

- Reliability and Qualification|Cirrus Logic. Available online: https://www.cirrus.com/company/quality/product-development/reliability-qualification?utm_source=chatgpt.com (accessed on 6 October 2025).

- JESD22-A104: Thermal Cycling Test Standard. Available online: https://eureka.patsnap.com/article/jesd22-a104-thermal-cycling-test-standard?utm_source=chatgpt.com (accessed on 6 October 2025).

- CISPR 25/ISO 7637 Automotive LISNs. Available online: https://theemcshop.com/categories/emc-test-equipment/line-impedance-stabilization-networks-lisns/cispr-25-iso-7637-automotive-lisns.html?srsltid=AfmBOorgJnxUUGyMeG4omB70qbWIVvW0S-p_QbNhCLEutYNvQey0oGev&utm_source=chatgpt.com (accessed on 6 October 2025).

- Huang, Q.; Huang, A.Q. Review of GaN Totem-Pole Bridgeless PFC. CPSS Trans. Power Electron. Appl. 2017, 2, 187–196. [Google Scholar] [CrossRef]

- Bay, O.; Tran, M.T.; El Baghdadi, M.; Chakraborty, S.; Hegazy, O. A Comprehensive Review of GaN-Based Bi-Directional On-Board Charger Topologies and Modulation Methods. Energies 2023, 16, 3433. [Google Scholar] [CrossRef]

- Dar, A.R.; Haque, A.; Khan, M.A.; Kurukuru, V.S.B.; Mehfuz, S. On-Board Chargers for Electric Vehicles: A Comprehensive Performance and Efficiency Review. Energies 2024, 17, 4534. [Google Scholar] [CrossRef]

- Schweizer, M.; Kolar, J.W. Design and Implementation of a Highly Efficient Three-Level T-Type Converter for Low-Voltage Applications. IEEE Trans. Power Electron. 2013, 28, 899–907. [Google Scholar] [CrossRef]

- Prado, E.O.; Bolsi, P.C.; Sartori, H.C.; Pinheiro, J.R. Design of Uninterruptible Power Supply Inverters for Different Modulation Techniques Using Pareto Front for Cost and Efficiency Optimization. Energies 2023, 16, 1314. [Google Scholar] [CrossRef]

- Texas Instruments. Comparison of AC/DC Power-Conversion Topologies for Three-Phase Industrial Systems; Texas Instruments: Dallas, TX, USA, 2024. [Google Scholar]

- Zhaksylyk, A.; Rasool, H.; Abramushkina, E.; Chakraborty, S.; Geury, T.; El Baghdadi, M.; Hegazy, O. Review of Active Front-End Rectifiers in EV DC Charging Applications. Batteries 2023, 9, 150. [Google Scholar] [CrossRef]

- UCC28070A Data Sheet, Product Information and Support|TI.com. Available online: https://www.ti.com/product/UCC28070A?utm_source=chatgpt.com (accessed on 6 October 2025).

- Abdel-Rahman, S. Resonant LLC Converter: Operation and Design; Infineon Technologies North America: Durham, NC, USA, 2012. [Google Scholar]

- Song, Q.; Zhang, R.; Li, Q.; Zhang, Y. Output Capacitance Loss of GaN HEMTs in Steady-State Switching. IEEE Trans. Power Electron. 2024, 39, 5547–5557. [Google Scholar] [CrossRef]

- Liu, J. Optimal-Design-for-High-Frequency-GaN-Based-Totem-Pole-PFC; EEPower: Newton-Le-Willows, UK, 2020. [Google Scholar]

- Zhao, H.; Li, Y.; Lin, F.; Yan, Y. Neutral-Point Voltage Balance Control of Three-Level Converter Based on Selection Method of Dynamical Adjustment for Small Voltage Vector. Appl. Sci. 2021, 11, 5076. [Google Scholar] [CrossRef]

- Anthon, A.; Zhang, Z.; Andersen, M.A.E.; Franke, T. Efficiency Investigations of a 3 kW T-Type Inverter for Switching Frequencies up to 100 kHz. In Proceedings of the 2014 International Power Electronics Conference (IPEC-Hiroshima 2014-ECCE ASIA), Hiroshima, Japan, 18–21 May 2014; pp. 78–83. [Google Scholar]

- Deng, J.; Cheng, H.; Wang, C.; Wu, S.; Si, M. Evaluation and Comprehensive Comparison of H-Bridge-Based Bidirectional Rectifier and Unidirectional Rectifiers. Electronics 2020, 9, 309. [Google Scholar] [CrossRef]

- Kolar, J.W.; Drofenik, U.; Minibock, J.; Ertl, H. A New Concept for Minimizing High-Frequency Common-Mode EM1 of Three-Phase PWM Rectifier Systems Keeping High Utilization of the Output Voltage. In Proceedings of the APEC 2000. Fifteenth Annual IEEE Applied Power Electronics Conference and Exposition (Cat. No.00CH37058), New Orleans, LA, USA, 6–10 February 2000. [Google Scholar]

- Zhang, H.; Yang, L.; Wang, S.; Puukko, J. Common-Mode EMI Noise Modeling and Reduction with Balance Technique for Three-Level Neutral Point Clamped Topology. IEEE Trans. Ind. Electron. 2017, 64, 7563–7573. [Google Scholar] [CrossRef]

- Ramakrishnan, H.; Rangaraju, J. Power Topology Considerations for Electric Vehicle Charging Stations; Document No. SLLA497; 2020. Available online: https://www.ti.com/lit/an/slla497/slla497.pdf?ts=1763301694825 (accessed on 6 October 2025).

- Texas Instruments. The Benefits of 650-V GaN FETs for 800-V Power Converters; Texas Instruments: Dallas, TX, USA, 2021. [Google Scholar]

- Nouri, S.M.; Alemi-Rostami, M.; Kahe, G. Multi-Objective Optimization of Two-Stage AC–DC Power Supply for Reliability and Efficiency Using NSGA-II and Meta-Heuristic Honey Bee Algorithms. Energy Rep. 2023, 10, 3174–3185. [Google Scholar] [CrossRef]

- Vesali, M. A Method to Calculate and Measure Losses and Efficiency in DC-DC Converters. JAREE J. Adv. Res. Electr. Eng. 2023, 7, 52–57. [Google Scholar] [CrossRef]

- Lidow, A.; Rooij, M.d.; Strydom, J.; Reusch, D.; Glaser, J. GaN Transistors for Efficient Power Conversion; John Wiley & Sons: Hoboken, NJ, USA, 2019; ISBN 978-1-119-59414-7. [Google Scholar]

- EPC. Layout Considerations for GaN-Bodo; EPC: El Segundo, CA, USA, 2021. [Google Scholar]

- STMicroelectronics. E-Mode GaN Technology: Tips for Best Driving—Application Note; STMicroelectronics: Singapore, 2021. [Google Scholar]

- Mueller, J. Optimizing Gate Driver Layout for LiDAR Applications; Texas Instruments: Dallas, TX, USA, 2020. [Google Scholar]

- Ammar, A.M.; Ali, K.; Rogers, D.J. A Bidirectional GaN-Based CLLC Converter for Plug-In Electric Vehicles On-Board Chargers. In Proceedings of the IECON 2020 the 46th Annual Conference of the IEEE Industrial Electronics Society, Singapore, 18–21 October 2020; pp. 1129–1135. [Google Scholar]

- Design and Analysis of GaN and Planar Magnetics Based DAB Converter for EV On-Board Chargers. Available online: https://www.researchgate.net/publication/394638899_Design_and_Analysis_of_GaN_and_Planar_Magnetics_based_DAB_Converter_for_EV_On-Board_Chargers?utm_source=chatgpt.com (accessed on 6 October 2025).

- Xiao, Y.; Zhang, Z.; Andersen, M.A.E.; Sun, K. Impact on ZVS Operation by Splitting Inductance to Both Sides of Transformer for 1-MHz GaN Based DAB Converter. IEEE Trans. Power Electron. 2020, 35, 11988–12002. [Google Scholar] [CrossRef]

- Deng, J.; Li, S.; Hu, S.; Mi, C.C. Ruiqing Ma Design Methodology of LLC Resonant Converters for Electric Vehicle Battery Chargers. IEEE Trans. Veh. Technol. 2014, 63, 1581–1592. [Google Scholar] [CrossRef]

- Toshiba Electronic Devices & Storage Corporation. Resonant Circuits and Soft Switching; Toshiba Electronic Devices & Storage Corporation: Kawasaki, Japan, 2019. [Google Scholar]

- Scuto, A. Half Bridge Resonant LLC Converters and Primary Side MOSFET Selection; STMicroelectronics: Singapore, 2015. [Google Scholar]

- Jung, J.; Kwon, J. Theoretical Analysis and Optimal Design of LLC Resonant Converter. In Proceedings of the 2007 European Conference on Power Electronics and Applications, Aalborg, Denmark, 2–5 September 2007; pp. 1–10. [Google Scholar]

- Truong, C.-T.; Choi, S.-J. Improved ZVS Criterion for Series Resonant Converters. IEEE Access 2024, 12, 5333–5344. [Google Scholar] [CrossRef]

- Mortazavizadeh, S.A.; Palazzo, S.; Amendola, A.; De Santis, E.; Di Ruzza, D.; Panariello, G.; Sanseverino, A.; Velardi, F.; Busatto, G. High Frequency, High Efficiency, and High Power Density GaN-Based LLC Resonant Converter: State-of-the-Art and Perspectives. Appl. Sci. 2021, 11, 11350. [Google Scholar] [CrossRef]

- Jiao, J.; Guo, X.; Wang, C.; You, X.; Li, K. An Improved Time-Domain Analytical Method for LLC Resonant Converters and Dead Time Designs for Zero-Voltage Switching. IET Power Electron. 2023, 16, 1455–1471. [Google Scholar] [CrossRef]

- Zhang, B.; Zhao, M.; Huang, P.; Wang, Q. Optimal Design of GaN HEMT Based High Efficiency LLC Converter. Energy Rep. 2022, 8, 1181–1190. [Google Scholar] [CrossRef]

- Liu, Y.-C.; Chen, C.; Chen, K.-D.; Syu, Y.-L.; Tsai, M.-C. High-Frequency LLC Resonant Converter with GaN Devices and Integrated Magnetics. Energies 2019, 12, 1781. [Google Scholar] [CrossRef]

- Ji, Z.; Min, F.; Dou, Y.; Cao, Z.; Li, X. Optimization of Key Power Loss for LLC Circuits with Planar Transformer in High-Frequency and High-Power Scenarios. AIP Adv. 2021, 11, 055119. [Google Scholar] [CrossRef]

- Yamamoto, T.; Bu, Y.; Mizuno, T.; Yamaguchi, Y.; Kano, T. Loss Reduction of Transformer for LLC Resonant Converter Using a Magnetoplated Wire. IEEJ J. Ind. Appl. 2018, 7, 43–48. [Google Scholar] [CrossRef]

- Farooq, H.; Khalid, H.A.; Khalid, M.U.; Syed, S.A. Efficiency Analysis of GaN Based LLC Resonant Converter for PV Applications. Eng. Proc. 2022, 20, 31. [Google Scholar]

- Shen, K.; Tong, A.; Shao, C.; Hang, L.; He, Y.; Zhang, Y.; Li, G.; Zhang, J. ZVS Control Strategy of Dual Active Bridge DC/DC Converter with Triple-Phase-Shift Modulation Considering RMS Current Optimization-Shen-2019-The Journal of Engineering-Wiley Online Library. J. Eng. 2019, 2019, 4708–4712. Available online: https://ietresearch.onlinelibrary.wiley.com/doi/10.1049/joe.2018.9341?utm_source=chatgpt.com (accessed on 7 October 2025). [CrossRef]

- Orsinger, J. DAB Converter Control Using Phase-Shift Modulation; Imperix: Sion, Switzerland, 2022. [Google Scholar]

- Kirsten, A.L.; Fraytag, J.; Cúnico, L.M.; de Oliveira, T.H.; Carloto, F.G.; Costa, M.A.D. Series Inductance Design of Dual-Active-Bridge Converter: ZVS Range with Practical Considerations. Int. J. Circuit Theory Appl. 2022, 50, 2423–2438. [Google Scholar] [CrossRef]

- Shao, S.; Chen, H.; Wu, X.; Zhang, J.; Sheng, K. Circulating Current and ZVS-on of a Dual Active Bridge DC-DC Converter: A Review. IEEE Access 2019, 7, 50561–50572. [Google Scholar] [CrossRef]

- Fei, C.; Gadelrab, R.; Li, Q.; Lee, F.C. High-Frequency Three-Phase Interleaved LLC Resonant Converter with GaN Devices and Integrated Planar Magnetics. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 653–663. [Google Scholar] [CrossRef]

- Ponnambalam, R.; Vairavasundaram, I. GaN-Based DC-DC Converters for EV Fast Charging: A Review of Wide Bandgap Devices Technology. Results Eng. 2025, 107548. [Google Scholar] [CrossRef]

- Wang, Y.-F.; Chen, B.; Hou, Y.; Meng, Z.; Yang, Y. Analysis and Design of a 1MHz Bi-Directional Multi-CLLC Resonant DC-DC Converter with GaN Devices. IEEE Trans. Ind. Electron. 2019, 67, 1425–1434. [Google Scholar] [CrossRef]

- Wu, X.; Gao, X.; Wang, J.; Li, Z.; Du, S.; Gao, S.; Li, F.; Du, J.; Shchurov, N.I.; Zhang, X. Advances in Modeling and Suppression Methods of EMI in Power Electronic Converters of Third-Generation Semiconductor Devices. Electronics 2023, 12, 2348. [Google Scholar] [CrossRef]

- Dong, M.; Li, H.; Yin, S.; Wu, Y.; Zhao, Z.; Huamin, J.; See, K.Y. Conducted EMI Estimation on GaN Step-up Resonant Converter for Electric Propulsion System. In Proceedings of the 2022 4th International Conference on Smart Power & Internet Energy Systems (SPIES), Beijing, China, 9–12 December 2022. [Google Scholar]

- Sun, B.; Zhang, Z.; Andersen, M.A.E. A Comparison Review of the Resonant Gate Driver in the Silicon MOSFET and the GaN Transistor Application. IEEE Trans. Ind. Appl. 2019, 55, 7776–7786. [Google Scholar] [CrossRef]

- Sun, B.; Zhang, Z.; Andersen, M.A.E. Review of Resonant Gate Driver in Power Conversion. In Proceedings of the 2018 International Power Electronics Conference (IPEC-Niigata 2018-ECCE Asia), Niigata, Japan, 20–24 May 2018; pp. 607–613. [Google Scholar]

- Liu, X.; Shafie, S.; Radzi, M.A.M.; Azis, N.; Karim, A.H.A. Modelling and Mitigating Oscillation in E-Mode GaN HEMT: A Simulation-Based Approach to Parasitic Inductance Optimization. Microelectron. Reliab. 2024, 152, 115293. [Google Scholar] [CrossRef]

- A Gate Driver with a Negative Turn Off Bias Voltage for GaN HEMTs. Available online: https://www.researchgate.net/publication/349934585_A_Gate_Driver_with_a_Negative_Turn_Off_Bias_Voltage_for_GaN_HEMTs?utm_source=chatgpt.com (accessed on 7 October 2025).

- Qin, H.; Wang, W.; Peng, Z.; Liu, A.; Bai, S. Characterization and Optimization of Gate Driver Turn-off Voltage for eGaN HEMTs in a Phase-Leg Configuration. Energy Rep. 2022, 8, 908–919. [Google Scholar] [CrossRef]

- Lu, Y.; Zhu, J.; Sun, W.; Zhang, Y.; Hu, K.; Yu, Z.; Leng, J.; Cheng, S.; Zhang, S. A 600V High-Side Gate Drive Circuit with Ultra-Low Propagation Delay for Enhancement Mode GaN Devices. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 80–83. [Google Scholar] [CrossRef]

- Semiconductor Components Industries, LLC. AND90004-Analysis of Power Dissipation and Thermal Considerations for High Voltage Gate Drivers; Semiconductor Components Industries, LLC: Scottsdale, AZ, USA, 2020. [Google Scholar]

- Fritz, N.; Engelmann, G.; De Doncker, R.W. RC Snubber Design Procedure for Enhanced Oscillation Damping in Wide-Bandgap Switching Cells. In Proceedings of the 2019 21st European Conference on Power Electronics and Applications (EPE ’19 ECCE Europe), Genova, Italy, 3–5 September 2019; pp. 1–10. [Google Scholar]

- Liu, M.; Chen, M. Dual-Band Multi-Receiver Wireless Power Transfer: Architecture, Topology, and Control. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019; pp. 851–859. [Google Scholar]

- Henriques, E.d.M.; Stegen, S. Concave Ferrite Core for Wireless Power Transfer (WPT). Energies 2023, 16, 4553. [Google Scholar] [CrossRef]

- Yadav, A.; Bera, T.K. Ferrite Shielding Thickness and Its Effect on Electromagnetic Parameters in Wireless Power Transfer for Electric Vehicles (EVs). J. Eng. Appl. Sci. 2023, 70, 132. [Google Scholar] [CrossRef]

- Ito, Y.; Imura, T.; Hori, Y. Leakage Magnetic Field Suppression Method Using the Next Transmission Coil as a Cancel Coil with Ferrite and Shield in Dynamic Wireless Power Transfer. In Proceedings of the 6th International Electric Vehicle Technology Conference, Yokohama, Japan, 22–24 May 2023. [Google Scholar]

- Eaker, M.; Berger, D. Understanding CISPR25 Current Probe and Voltage Method for Conducted Emissions; Texas Instruments: Dallas, TX, USA, 2022. [Google Scholar]

- Rhee, J.; Woo, S.; Lee, C.; Ahn, S. Selection of Ferrite Depending on Permeability and Weight to Enhance Power Transfer Efficiency in Low-Power Wireless Power Transfer Systems. Energies 2024, 17, 3816. [Google Scholar] [CrossRef]

- Design and Analysis of Magnetic Shielding Mechanism for Wireless Power Transfer System Based on Composite Materials. Available online: https://www.mdpi.com/2079-9292/11/14/2187?utm_source=chatgpt.com (accessed on 22 October 2025).

- Wu, C.; Kim, H.; Penugonda, S.; Fan, J. Analysis and Modeling of the Common-Mode Conducted EMI From a Wireless Power Transfer System for Mobile Applications. IEEE Trans. Electromagn. Compat. 2021, 63, 2143–2150. [Google Scholar] [CrossRef]

- Variable-Frequency Pulse Width Modulation Circuits for Resonant Wireless Power Transfer. Available online: https://www.mdpi.com/1996-1073/14/12/3656?utm_source=chatgpt.com (accessed on 22 October 2025).

- Reactive Shield for Reducing the Magnetic Field of a Wireless Power Transfer System with Dipole Coil Structure. Available online: https://www.mdpi.com/2079-9292/13/9/1712?utm_source=chatgpt.com (accessed on 22 October 2025).

- Yadav, A.; Bera, T.K. Design and Optimization of Circular and Rectangular Couplers for Wireless Power Transfer: Efficiency Enhancement and Human Safety Assessment. Discov. Energy 2025, 5, 7. [Google Scholar] [CrossRef]

- Jaafari, S.; El Hafdaoui, H.; Ajabboune, K.; Khallaayoun, A.; Ahouzi, E. Optimization of Circular Coils with Ferrite Boxes for Enhanced Efficiency in Wireless Power Transfer for Electric Vehicles. Green Energy Intell. Transp. 2025, 4, 100195. [Google Scholar] [CrossRef]

- Zhu, L.; Liu, Z.; Ma, L.; Zeng, X.; Lu, W. Analytical and Experimental Investigations of Magnetic Field Distribution for Wireless Power Transfer System with Ferrite Core. Space Sol. Power Wirel. Transm. 2025, 2, 110–115. [Google Scholar] [CrossRef]

- Lecluyse, C.; Minnaert, B.; Kleemann, M. A Review of the Current State of Technology of Capacitive Wireless Power Transfer. Energies 2021, 14, 5862. [Google Scholar] [CrossRef]

- Lu, J.; Zhu, G.; Lin, D.; Zhang, Y.; Jiang, J.; Mi, C.C. Unified Load-Independent ZPA Analysis and Design in CC and CV Modes of Higher Order Resonant Circuits for WPT Systems. IEEE Trans. Transp. Electrif. 2019, 5, 977–987. [Google Scholar] [CrossRef]

- Zhang, H.; Lu, F.; Hofmann, H.; Liu, W.; Mi, C.C. A Four-Plate Compact Capacitive Coupler Design and LCL-Compensated Topology for Capacitive Power Transfer in Electric Vehicle Charging Application. IEEE Trans. Power Electron. 2016, 31, 8541–8551. [Google Scholar] [CrossRef]

- Lu, J.; Zhu, G.; Lin, D.; Zhang, Y.; Wang, H.; Mi, C.C. Realizing Constant Current and Constant Voltage Outputs and Input Zero Phase Angle of Wireless Power Transfer Systems with Minimum Component Counts. IEEE Trans. Intell. Transp. Syst. 2021, 22, 600–610. [Google Scholar] [CrossRef]

- Wang, Y.; Zhang, H.; Lu, F. Review, Analysis, and Design of Four Basic CPT Topologies and the Application of High-Order Compensation Networks. IEEE Trans. Power Electron. 2022, 37. [Google Scholar] [CrossRef]

- A Review of Capacitive Power Transfer Technology for Electric Vehicle Applications. Available online: https://www.mdpi.com/2079-9292/12/16/3534?utm_source=chatgpt.com (accessed on 22 October 2025).

- Liu, X.; Clare, L.; Yuan, X.; Wang, C.; Liu, J. A Design Method for Making an LCC Compensation Two-Coil Wireless Power Transfer System More Energy Efficient Than an SS Counterpart. Energies 2017, 10, 1346. [Google Scholar] [CrossRef]

- Luo, B.; Mai, R.; Guo, L.; Wu, D.; He, Z. LC–CLC Compensation Topology for Capacitive Power Transfer System to Improve Misalignment Performance. IET Power Electron. 2019, 12, 2626–2633. [Google Scholar] [CrossRef]

- Chen, T.; Cheng, C.; Zhang, X.; Li, G.; Guo, Y.; Mi, C.C. A Double-Sided LCL-Compensated Network for the Strongly Coupled CPT System with Minimum Plate Voltage Stresses. IEEE J. Emerg. Sel. Top. Power Electron. 2024, 12, 4275–4287. [Google Scholar] [CrossRef]

- Namiki, H.; Imura, T.; Hori, Y. Comparison of Multiple Circuits Including LCL in Inductive Power Transfer and Capacitive Power Transfer. In Proceedings of the IECON 2023-49th Annual Conference of the IEEE Industrial Electronics Society, Singapore, 16–19 October 2023; pp. 1–7. [Google Scholar]

- Cheng, C.; Lu, F.; Zhou, Z.; Li, W.; Deng, Z.; Li, F.; Mi, C. A Load-Independent LCC-Compensated Wireless Power Transfer System for Multiple Loads with a Compact Coupler Design. IEEE Trans. Ind. Electron. 2020, 67, 4507–4515. [Google Scholar] [CrossRef]

- ElGhanam, E.; Hassan, M.; Osman, A. Design of a High Power, LCC-Compensated, Dynamic, Wireless Electric Vehicle Charging System with Improved Misalignment Tolerance. Energies 2021, 14, 885. [Google Scholar] [CrossRef]

- Lian, J.; Qu, X.; Chen, X.; Mi, C.C. Design of a Double-Sided LCLC -Compensated Capacitive Power Transfer System with Predesigned Coupler Plate Voltage Stresses. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 128–137. [Google Scholar] [CrossRef]

- Lu, F.; Zhang, H.; Mi, C. A Review on the Recent Development of Capacitive Wireless Power Transfer Technology. Energies 2017, 10, 1752. [Google Scholar] [CrossRef]

- Muharam, A.; Mostafa, T.M.; Ahmad, S.; Masuda, M.; Obara, D.; Hattori, R.; Hapid, A. Preliminary Study of 50 W Class-E GaN FET Amplifier for 6.78 MHz Capacitive Wireless Power Transfer. J. Mechatron. Electr. Power Veh. Technol. 2020, 11, 22–29. [Google Scholar] [CrossRef]

- Kasper, M. Analysis of Capacitive Power Transfer GaN ISOP Multi-Cell DC/DC Converter Systems for Single-Phase Telecom Power Supply Modules. In Proceedings of the IECON 2016-42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, Italy, 23–26 October 2016. [Google Scholar] [CrossRef]

- Amir, M.; Saifi, I.A.; Waseem, M.; Tariq, M. A Critical Review of Compensation Converters for Capacitive Power Transfer in Wireless Electric Vehicle Charging Circuit Topologies. Green Energy Intell. Transp. 2025, 4, 100196. [Google Scholar] [CrossRef]

- Iero, D.; Carotenuto, R.; Merenda, M.; Pezzimenti, F.; Della Corte, F.G. Performance Evaluation of Silicon and GaN Switches for a Small Wireless Power Transfer System. Energies 2022, 15, 3029. [Google Scholar] [CrossRef]

- A Very-High-Power-Transfer-Density GaN-Based Capacitive Wireless Power Transfer System. Available online: https://www.researchgate.net/publication/321788602_A_very-high-power-transfer-density_GaN-based_capacitive_wireless_power_transfer_system?utm_source=chatgpt.com (accessed on 22 October 2025).

- Wang, Z.; Zhang, Y.; He, X.; Luo, B.; Mai, R. Research and Application of Capacitive Power Transfer System: A Review. Electronics 2022, 11, 1158. [Google Scholar] [CrossRef]

- Lecluyse, C.; Minnaert, B.; Ravyts, S.; Kleemann, M. Influence of a Medium on Capacitive Power Transfer Capability. In Proceedings of the 2022 Wireless Power Week (WPW), Bordeaux, France, 5–8 July 2022; pp. 589–594. [Google Scholar]

- Li, W.; Liu, J.; Gong, C. High-Frequency Response Current Direct Demodulation Method for Sensorless Control of Interior Permanent Magnet Synchronous Motor Drives. J. Power Electron. 2022, 22, 784–795. [Google Scholar] [CrossRef]

- He, H.; Lu, Z.; Zhang, C.; Wang, Y.; Guo, W.; Zhao, S. A Data-Driven Method for Dynamic Load Forecasting of Scraper Conveyer Based on Rough Set and Multilayered Self-Normalizing Gated Recurrent Network. Energy Rep. 2021, 7, 1352–1362. [Google Scholar] [CrossRef]

- Luo, L.; Qu, Y.; Gong, W.; Qin, L.; Li, W.; Sun, Y. Effect of Particle Size on the Aerobic and Anaerobic Digestion Characteristics of Whole Rice Straw. Energies 2021, 14, 3960. [Google Scholar] [CrossRef]

- Sun, R.; Lai, J.; Chen, W.; Zhang, B. GaN Power Integration for High Frequency and High Efficiency Power Applications: A Review. IEEE Access 2020, 8, 15529–15542. [Google Scholar] [CrossRef]

- Shivani; Kaur, D.; Ghosh, A.; Kumar, M. A Strategic Review on Gallium Oxide Based Power Electronics: Recent Progress and Future Prospects. Mater. Today Commun. 2022, 33, 104244. [Google Scholar] [CrossRef]

- Shermukhamedov, S.; Probst, M. Sputtering from Rough Tungsten Surfaces: Data-Driven Molecular Dynamics Simulations. Phys. Plasmas 2023, 12, 123901. Available online: https://pubs.aip.org/aip/pop/article/30/12/123901/2925622/Sputtering-from-rough-tungsten-surfaces-Data (accessed on 22 October 2025). [CrossRef]

- He, P.; Mallik, A.; Sankar, A.; Khaligh, A. Design of a 1-MHz High-Efficiency High-Power-Density Bidirectional GaN-Based CLLC Converter for Electric Vehicles. IEEE Trans. Veh. Technol. 2019, 68, 213–223. [Google Scholar] [CrossRef]

- Embarking on a New Frontier of Power Density with GaN|Electronic Design. Available online: https://www.electronicdesign.com/technologies/power/article/55241919/electronic-design-embarking-on-a-new-frontier-of-power-density-with-gan?utm_source=chatgpt.com (accessed on 22 October 2025).

- Wei, Y.; Maksudul Hossain, M.; Alan Mantooth, H. GaN HEMT and Air Core Magnetics Based Power Converters Evaluations at Cryogenic Temperature. IOP Conf. Ser. Mater. Sci. Eng. 2024, 1302, 012026. [Google Scholar] [CrossRef]

- High-Density Power-Conversion Technology Enablers Using GaN-Power Electronic Tips. Available online: https://www.powerelectronictips.com/high-density-power-conversion-technology-enablers-using-gan/?utm_source=chatgpt.com (accessed on 22 October 2025).

- Assessing Reliability and Lifetime of GaN Power Devices-Power Electronics News. Available online: https://www.powerelectronicsnews.com/assessing-reliability-and-lifetime-of-gan-power-devices/?utm_source=chatgpt.com (accessed on 22 October 2025).

- Ma, C.-T.; Gu, Z.-H. Review of GaN HEMT Applications in Power Converters over 500 W. Electronics 2019, 8, 1401. [Google Scholar] [CrossRef]

- Talukder, A.; Ifty, M.R.; Al Fahad, A. Comprehensive Review of GaN HEMTs: Architectures, Recent Developments, Reliability Concerns, Challenges, and Multifaceted Applications. E-Prime-Adv. Electr. Eng. Electron. Energy 2025, 13, 101059. [Google Scholar] [CrossRef]

- Cook, T.; Franconi, N.; Shea, B.; Wilson, C.; Grainger, B.M.; George, A.D.; Barchowsky, A. Radiation-Tolerant, GaN-Based Point of Load Converters for Small Spacecraft Missions. In Proceedings of the 32nd Annual AIAA/USU Conference on Small Satellites, Logan, UT, USA, 4–9 August 2018. [Google Scholar]

- Mondy, T. Reliability Study of Enhancement Mode Gallium Nitride Field Effect Transistors; NASA: Washington, DC, USA, 2022. [Google Scholar]

- Islam, N.; Mohamed, M.F.P.; Khan, M.F.A.J.; Falina, S.; Kawarada, H.; Syamsul, M. Reliability, Applications and Challenges of GaN HEMT Technology for Modern Power Devices: A Review. Crystals 2022, 12, 1581. Available online: https://www.mdpi.com/2073-4352/12/11/1581?utm_source=chatgpt.com (accessed on 23 October 2025). [CrossRef]

- Cusumano, P.; Sirchia, A.; Vella, F. Evaluation of Dynamic On-Resistance and Trapping Effects in GaN on Si HEMTs Using Rectangular Gate Voltage Pulses. Electronics 2025, 14, 2791. [Google Scholar] [CrossRef]

- Niu, P.; Guo, J.; Gao, Z.; Yan, J.; Gao, S. Research on Improved Technology of Totem-Pole Bridgeless PFC Circuit Based on Triangular Current Mode. Energies 2025, 18, 3886. Available online: https://www.mdpi.com/1996-1073/18/14/3886?utm_source=chatgpt.com (accessed on 23 October 2025). [CrossRef]

- Zhou, K.; Wu, Y.; Wu, X.; Sun, Y.; Teng, D.; Liu, Y. Research and Development Review of Power Converter Topologies and Control Technology for Electric Vehicle Fast-Charging Systems. Electronics 2023, 12, 1581. [Google Scholar] [CrossRef]

- Xu, S.; Xu, S.; Xu, D.; Qian, Q.; Sun, W.; Zhu, J. A Review on Recent Effort of Conductive EMI Suppression Methods in High-Frequency Power Converters. IET Power Electron. 2022, 15, 1921–1935. Available online: https://digital-library.theiet.org/doi/full/10.1049/pel2.12348?utm_source=chatgpt.com (accessed on 23 October 2025). [CrossRef]

- Krismer, F.; Schroth, S.; Ertl, H.; Kostov, K.S.; Nee, H.-P.; Kolar, J.W. Analysis and Practical Relevance of CM/DM EMI Noise Separator Characteristics. IEEE Trans. Power Electron. 2017, 32, 3112–3127. [Google Scholar] [CrossRef]

- Rebholz, H.; Tenbohlen, S. Prospects and Limits of Common- and Differential-Mode Separation for the Filter Development Process. In Proceedings of the 2008 International Symposium on Electromagnetic Compatibility-EMC Europe, Hamburg, Germany, 8–12 September 2008; pp. 1–6. [Google Scholar]

- Wang, S.; Lee, F.C.; Odendaal, W.G. Characterization, Evaluation, and Design of Noise Separator for Conducted EMI Noise Diagnosis. IEEE Trans. Power Electron. 2005, 20, 974–982. [Google Scholar] [CrossRef]

- Nussbaumer, T.; Heldwein, M.L.; Kolar, J.W. Differential Mode Input Filter Design for a Three-Phase Buck-Type PWM Rectifier Based on Modeling of the EMC Test Receiver. IEEE Trans. Ind. Electron. 2006, 53, 1649–1661. [Google Scholar] [CrossRef]

- Kotny, J.-L.; Margueron, X.; Idir, N. High-Frequency Model of the Coupled Inductors Used in EMI Filters. IEEE Trans. Power Electron. 2012, 27, 2805–2812. [Google Scholar] [CrossRef]

- Wang, Q.; An, Z.; Zheng, Y.; Yang, Y. Parameter Extraction of Conducted Electromagnetic Interference Prediction Model and Optimisation Design for a DC–DC Converter System. IET Power Electron. 2013, 6, 1449–1461. [Google Scholar] [CrossRef]

- Kasper, M.; Burkart, R.M.; Deboy, G.; Kolar, J.W. ZVS of Power MOSFETs Revisited. IEEE Trans. Power Electron. 2016, 31, 8063–8067. [Google Scholar] [CrossRef]

- Zhang, B.; Wang, S. A Survey of EMI Research in Power Electronics Systems with Wide-Bandgap Semiconductor Devices. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 626–643. [Google Scholar] [CrossRef]

- Lai, R.; Maillet, Y.; Wang, F.; Wang, S.; Burgos, R.; Boroyevich, D. An Integrated EMI Choke for Differential-Mode and Common-Mode Noise Suppression. IEEE Trans. Power Electron. 2010, 25, 539–544. [Google Scholar] [CrossRef]

- Erickson, R.W. Optimal Single Resistors Damping of Input Filters. In Proceedings of the APEC ’99. Fourteenth Annual Applied Power Electronics Conference and Exposition, 1999 Conference Proceedings (Cat. No.99CH36285), Dallas, TX, USA, 14–18 March 1999; Volume 2, pp. 1073–1079. [Google Scholar]

- Todd, C. Snubber Circuits: Theory, Design and Application; Texas Instruments: Dallas, TX, USA, 1993. [Google Scholar]

- Gulur, S.; Iyer, V.M.; Bhattacharya, S. Improved Common Mode Noise Models for Three Level T-Type Neutral Point Clamped Converters. In Proceedings of the 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018; pp. 6398–6403. [Google Scholar]

- Kolar, J.W.; Biela, J.; Minibock, J. Exploring the Pareto Front of Multi-Objective Single-Phase PFC Rectifier Design Optimization-99.2% Efficiency vs. 7 kW/Dm3 Power Density. In Proceedings of the 2009 IEEE 6th International Power Electronics and Motion Control Conference, Wuhan, China, 17–20 May 2009. [Google Scholar]

- Oh, H.-S.; Hong, S.-Y.; Lee, J.; Lee, J.-B. Comparison of Bi-Directional Topologies for On-Board Charger: A 10.9 kW High-Efficiency High Power Density of DC-DC Stage. Energies 2024, 17, 5496. [Google Scholar] [CrossRef]

- Kundu, A.; Patrick, E.; Currlin, S.; Madler, R.; Delgado, F.; Fahmy, A.; Verplancke, R.; Ballini, M.; Braeken, D.; de Beeck, M.O.; et al. Using Compound Neural Action Potentials for Functional Validation of a High-Density Intraneural Interface: A Preliminary Study. Micromachines 2024, 15, 280. [Google Scholar] [CrossRef] [PubMed]

- Cacciato, M.; Aiello, G.; Gennaro, F.; Mita, S.; Patti, D.; Scelba, G.; Sujeeth, A. Power Loss Modelling of GaN HEMT Based 3L ANPC Three Phase Inverter for Different PWM Techniques. arXiv 2022. [Google Scholar] [CrossRef]

- Varga, D. Analysis of Benford’s Law for No-Reference Quality Assessment of Natural, Screen-Content, and Synthetic Images. Electronics 2021, 10, 2378. [Google Scholar] [CrossRef]

- Martin, D.; Curbow, A. High Power Density GaN-Based Power Converters for Grid-Tied Energy Storage Applications; Cree Fayetteville, Inc. (formerly Arkansas Power Electronics International, Inc.): Fayetteville, AR, USA, 2016. [Google Scholar]

- Nazerian, E.; Yu, R.; Huang, Q.; Heydari, M.; Salimian, H.; Huang, A.Q. High Efficiency, High Power Density 10 kW Flying Capacitor Converter Based on 650V GaN for 800V EV Applications. In Proceedings of the 2023 IEEE Energy Conversion Congress and Exposition (ECCE), Nashville, TN, USA, 29 October–2 November 2023. [Google Scholar]

- Hu, C.; Cui, C.; Li, H.; Tang, X.; Guo, S.; Yan, J.; Zhang, P.; Cao, W. GaN-Based LLC Converters with Digital Synchronous Rectifier and Copper Foil Planar Transformer in High-Output Current Applications. IEEE Trans. Power Electron. 2024, 39, 5411–5423. [Google Scholar] [CrossRef]

- Liu, Y.; Du, G.; Wang, X.; Lei, Y. Analysis and Design of High-Efficiency Bidirectional GaN-Based CLLC Resonant Converter. Energies 2019, 12, 3859. [Google Scholar] [CrossRef]

- Sujeeth, A.; Di Cataldo, A.; Tornello, L.D.; Pulvirenti, M.; Salvo, L.; Sciacca, A.G.; Scelba, G.; Cacciato, M. Power Loss Modelling and Performance Comparison of Three-Level GaN-Based Inverters Used for Electric Traction. Energies 2024, 17, 595. [Google Scholar] [CrossRef]

- Satpathy, S.; Das, P.P.; Bhattacharya, S. Power Layout Design of a GaN HEMTs-Based High-Power High-Efficiency Three-Level ANPC Inverter for 800 V DC Bus System. IEEE J. Emerg. Sel. Top. Ind. Electron. 2024, 5, 565–576. [Google Scholar] [CrossRef]

| Property | Silicon (Si) | Silicon Carbide (SiC) | Gallium Nitride (GaN) | Significance |

|---|---|---|---|---|

| Bandgap Energy (eV) | 1.1 | 3.3 | 3.4 | A wider bandgap enables higher temperature and voltage operation. |

| Breakdown Electric Field (MV/cm) | 0.3 | 2.8 | 3.0 | Higher values allow thinner drift regions and smaller devices. |

| Electron Mobility (cm2/V·s) | 1500 | 900 | 1500 | Higher mobility supports faster switching. |

| Saturation Velocity (cm/s) | 1 × | 2 × | 2.5 × | Enables high-frequency, low-loss switching. |

| Thermal Conductivity (W/cm·K) | 1.5 | 3.7 | 1.3 | Affects heat dissipation efficiency. |

| Reverse Recovery Charge () | High | Moderate | 0 | Zero reduces switching losses and EMI. |

| Gate Charge () | High | Moderate | Low | Lower supports fast switching with low drive loss. |

| Converter Type | Stress Mechanism | (°C) | Reliability Concern | Remarks/Mitigation |

|---|---|---|---|---|

| Synchronous Buck/Boost | High repetitive hard-switching, asymmetric conduction | 40–60 | Dynamic drift and hot-carrier injection at high | Use soft-gate drive and active snubber to minimize overshoot |

| Totem-Pole PFC (TPPFC) | Alternating conduction between the fast GaN leg and the slow SiC/SBR leg | 50–70 | Cross-conduction and body-diode dynamic recovery heating | Optimize dead time; synchronous mode with gate-voltage shaping reduces reverse stress [152] |

| CLLC Resonant/Dual Active Bridge | ZVS/ZCS transitions minimize switching stress; thermal stress from circulating current | 20–40 | Bias temperature instability in continuous operation | Design for balanced magnetizing current; ensure minimal residual hard commutation |

| Vienna/T-type NPC | Multi-device series paths share voltage but increase thermal imbalance risk | 45–65 | Unequal device aging, gate charge mismatch | Thermal coupling through the baseplate and dynamic current sharing improve lifetime consistency [153] |

| Bidirectional OBC/DC-link SST | High-frequency bidirectional power flow | 30–55 | Repetitive dynamic stress; EMI–thermal co-coupling | Spread-spectrum modulation and digital THD control reduce repetitive EMI-induced heating [154] |

| Subsystem | Topology | (kHz) | η (%) | Power Density (W/L) | (dBµV Below Limit) | Reference Range (2019–2025) |

|---|---|---|---|---|---|---|

| OBC (400 V) | GaN TP-PFC + CLLC | 200–500 | 96–98 | 3.5–5.0 | −5 to −8 | [46] |

| OBC (800 V) | GaN T-Type 3L + DAB | 150–300 | 95–97 | 4.2–4.8 | −4 to −7 | [169] |

| DC–DC Stage | LLC/CLLC | 300–1000 | 96–98 | 6.0–9.0 | −3 to −6 | [141] |

| Traction Inverter | 3-Phase GaN NPC | 100–200 | 98–99 | 7.5–10 | −2 to −5 | [170] |

| EMI Filter Benchmarks | Hybrid CM/DM Filter + GaN Leg | 500–1000 | - | - | −6 to −10 | [171] |

| Subsystem | Platform | Topology Band (Favored) | (kHz) | Target η (%) | (W/L) | (dBµV) | |

|---|---|---|---|---|---|---|---|

| OBC AC-DC [46] | 400 V | TP-PFC → LLC/CLLC | 150–400 kHz | ≥97.5% | ≥4.5 | ≤−6 (150 k–30 MHz) | ≥15 °C at = 15 °C |

| OBC AC-DC | 800 V [173] | 3L Vienna/T-type NPC | 120–300 kHz | ≥97.0% (Vienna), ≥96.5% (T-type) | ≥4.2 | ≤−5 | ≥12 °C |

| Isolated DC-AC [174] | 400 V | LLC/CLLC, DAB | 300–900 kHz | ≥97.8% (peak), ≥97.0% (rated) | ≥6.5 | ≤−6 | ≥15 °C |

| Isolated DC-AC [175] | 800 V | 3L-LLC/CLLC or DAB | 250–700 kHz | ≥97.2% | ≥5.8 | ≤−5 | ≥12 °C |

| Traction Inverter [176] | 400 V | 3-phase NPC (GaN) | 60–150 kHz | ≥98.8% | ≥8.0 | ≤−3 (DM bands; CM shaping) | ≥10 °C |

| Traction Inverter [177] | 800 V | 3-phase NPC (GaN, stacked/3L) | 50–120 kHz | ≥98.3% | ≥7.0 | ≤−3 | ≥10 °C |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Adeloye, I.A.; Bhattacharya, I.; Ezugwu, E.O.; Antony Dhason, M.V. GaN Electric Vehicle Systems—A Comparative Review. Energies 2025, 18, 6020. https://doi.org/10.3390/en18226020

Adeloye IA, Bhattacharya I, Ezugwu EO, Antony Dhason MV. GaN Electric Vehicle Systems—A Comparative Review. Energies. 2025; 18(22):6020. https://doi.org/10.3390/en18226020

Chicago/Turabian StyleAdeloye, Ifeoluwa Ayomide, Indranil Bhattacharya, Ernest Ozoemela Ezugwu, and Mary Vinolisha Antony Dhason. 2025. "GaN Electric Vehicle Systems—A Comparative Review" Energies 18, no. 22: 6020. https://doi.org/10.3390/en18226020

APA StyleAdeloye, I. A., Bhattacharya, I., Ezugwu, E. O., & Antony Dhason, M. V. (2025). GaN Electric Vehicle Systems—A Comparative Review. Energies, 18(22), 6020. https://doi.org/10.3390/en18226020