1. Introduction

With the advantages of cleanliness, energy saving and high efficiency [

1,

2], new energy vehicles have gradually become an indispensable mode of transport for people who travel. However, due to the long charging time of conventional electric vehicles and the difference in charging voltage levels of different manufacturers, the voltage fluctuation ranges from 200 V to 920 V [

3], and some of them even reach 1000 V [

4]. Therefore, the solution of DC/DC fast-charging technology with adaptable high voltage, high power, and wide voltage range has received extensive attention from researchers.

The buck–boost converter has been widely adopted in electric vehicle charging stations, energy storage systems, and DC micro grids due to its non-inverting output and flexible voltage regulation capabilities [

5,

6]. However, as fast-charging power levels increase from tens of kilowatts to hundreds of kilowatts, there exists an urgent demand for power conversion solutions that support ultra-wide voltage ranges. A novel buck–boost flying capacitor converter for electric vehicle (EV) fast-charging station DC–DC stages has been proposed in [

7]. On this basis, an improved DC–DC buck–boost partial power converter with better efficiency compared to [

7] is subsequently developed in [

8]. However, conventional two-level buck–boost converters with single-leg topology have inherent limitations—switching devices experience increased voltage stress at high output voltages, which raises the susceptibility to overvoltage damage. This operational constraint necessitates the selection of devices with higher voltage class, resulting in increased cost and challenges in increasing the switching frequency. Consequently, existing two-level buck–boost converter architectures are proving inadequate to meet the requirements of high-power, fast-charging systems.

To address the trade-offs between voltage stress and switching frequency, three-level buck–boost topologies have been investigated. These configurations achieve multi-level output characteristics through flying capacitors or cascaded structures [

9,

10], effectively reducing device voltage stress to 50% of conventional topologies. The three-level framework offers dual advantages: (1) filter size can be reduced, and power density can be improved by multi-level waveform generation, and (2) lower-voltage devices facilitate higher switching frequency operation, thereby enhancing the dynamic response. However, the three-level topology presents significant challenges in implementing control strategies such as multi-mode operation, input/output capacitor voltage balance, and switching state optimization.

In terms of control strategies, conventional two-level buck–boost converters have inherent defects during mode transitions due to minimum pulse width limitation [

11]. Specifically, when the input and output voltages approach equilibrium, the voltage gain dead zone in the buck–boost mode transition region occurs in conventional control strategies, resulting in regulation failure [

12]. To address this problem, a variety of strategies have been investigated to improve performance. For non-inverting buck–boost topologies, a multi-mode operation strategy has been proposed in [

13], where an additional buck–boost mode is introduced alongside the conventional buck and boost modes to mitigate the dead-zone effects. However, this approach can lead to switching oscillations in the region of critical transition thresholds. To suppress such oscillations, a hysteresis control has been implemented in [

14].

To further enhance the dynamic characteristics of the converter, the MPC strategy is widely adopted. A modulated MPC is proposed in [

15], where the operating state is divided into four modes and the optimal duty cycle is selected via a voltage-based cost function. A key drawback, however, is that this algorithm requires explicit monitoring of the operating mode. To overcome this problem, three operating modes are classified in [

16], and the cost function is selected as the minimum fluctuation of inductor current in each control cycle, so that the optimized duty cycle for the subsequent control interval is preferred. For FCS-MPC, a state-space model including switching states is established in [

17], and four switching states are polled to optimize the output voltage tracking effect. Since the cost function does not include the inductor current, it is prone to cause current inrush. Building on [

17], the work in [

18] refines this approach by incorporating both the inductor current and its limit into the cost function. This dual-objective optimization ensures smooth output voltage transitions while effectively suppressing current inrush. Unlike that with two levels, the three-level buck–boost converter confronts the following problems: Firstly, the capacitor voltage balancing control on the input and output sides needs to be regulated. Secondly, the four half-bridge topologies can generate 16 switching states [

19], and the global polling computational burden increases dramatically. Finally, the voltage oscillation phenomenon still exists when the input and output voltages are close to each other. To address these issues, Ref. [

20] proposes a modulated MPC that introduces two extended operating modes and employs duty cycle hysteresis control to prevent mode oscillations. Notably, the monitor of the converter operating mode is also required, and the optimal number of switching actions cannot be guaranteed. For FCS-MPC, the duty cycle is solved in [

21], and the optimal duty cycle is polled in the range of 0 to 1 as a way to achieve optimal control. However, the duty cycle has continuous characteristics, and its accuracy under discrete polling does not meet the demand for control accuracy.

Aiming to address limitations in existing FCS-MPC strategies, a switch-state-optimized FCS-MPC method is proposed in this paper. The contributions can be listed as follows:

- (1)

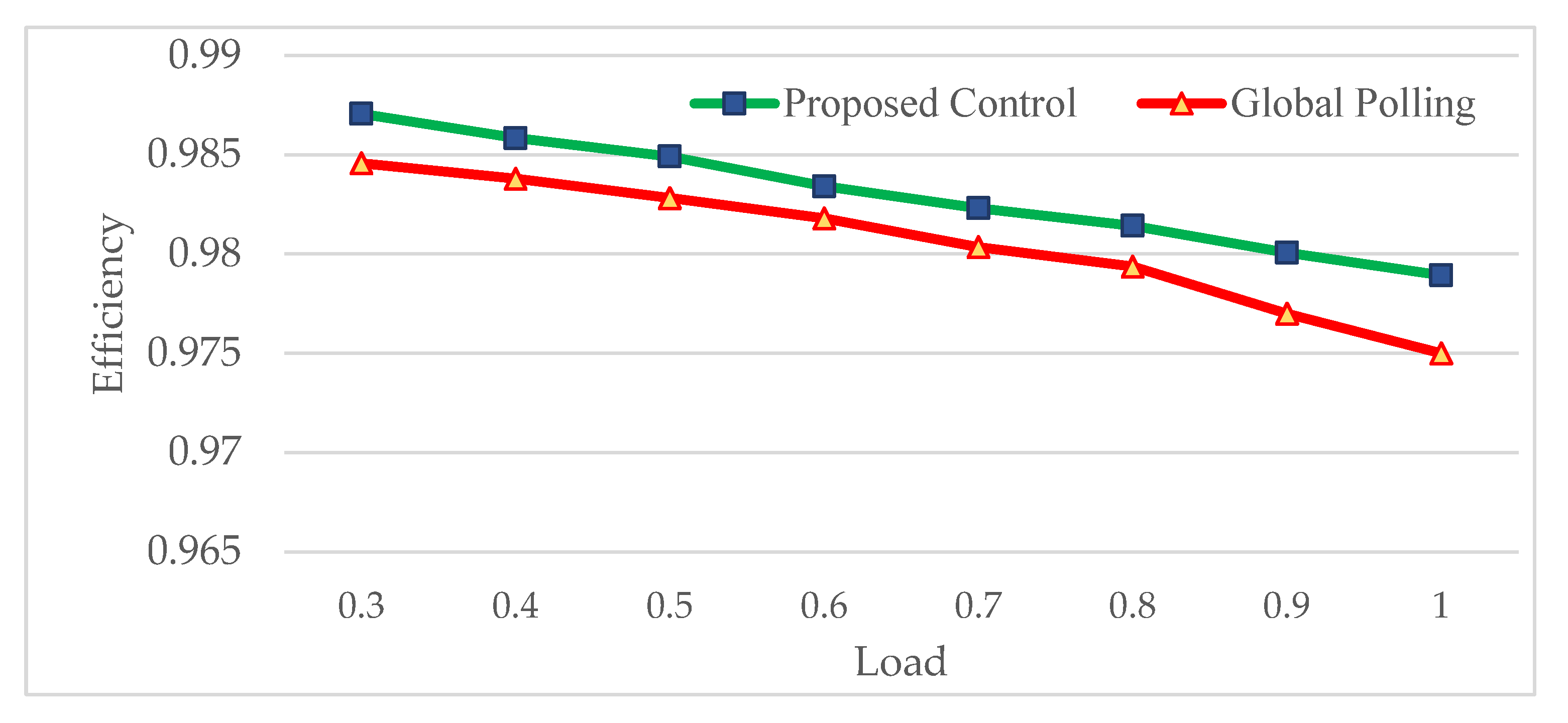

The total number of switching states is reduced from 16 to 11 while retaining full-range buck–boost operation and capacitor voltage balancing capabilities, thereby reducing control complexity. Additionally, the proposed adjacent-state polling strategy further limits candidate states per control cycle to a maximum of five, substantially decreasing computational load and switching losses.

- (2)

A multi-objective cost function integrating mode transitions, capacitor voltage balancing, and current tracking is established to enable systematic trade-offs among objectives.

- (3)

Seamless mode switching through shared bridging state (M1) ensures smooth transition for different load scenarios.

Ultimately, the proposed control dynamically optimizes switching actions and mode transitions, offering a novel solution for efficient control of three-level topologies. This paper is organized as follows: The principle and discrete state-space model of the three-level buck–boost converter are analyzed in

Section 2. The switching state optimization method is proposed in

Section 3. Next, the FCS-MPC algorithm is presented in

Section 4.

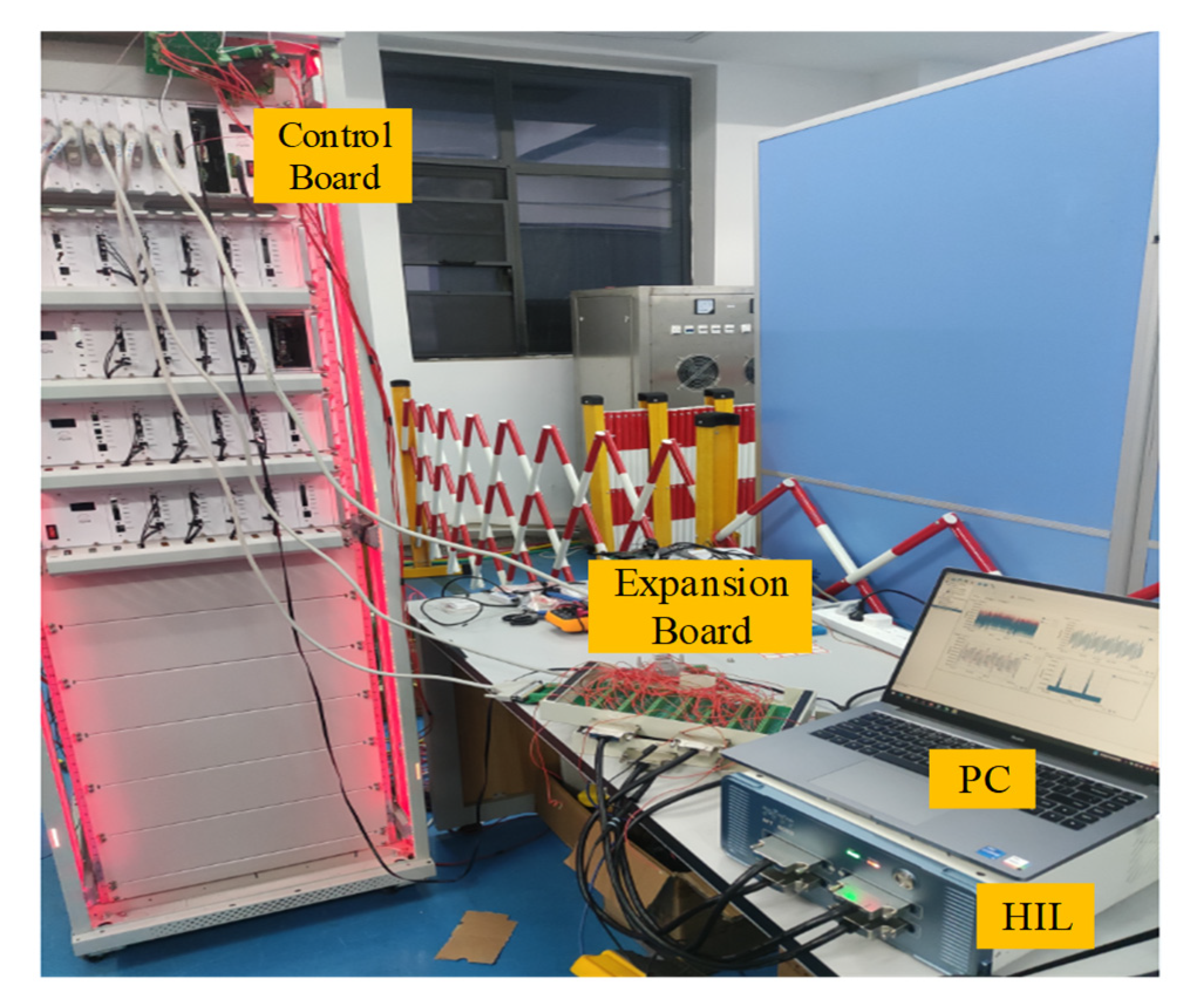

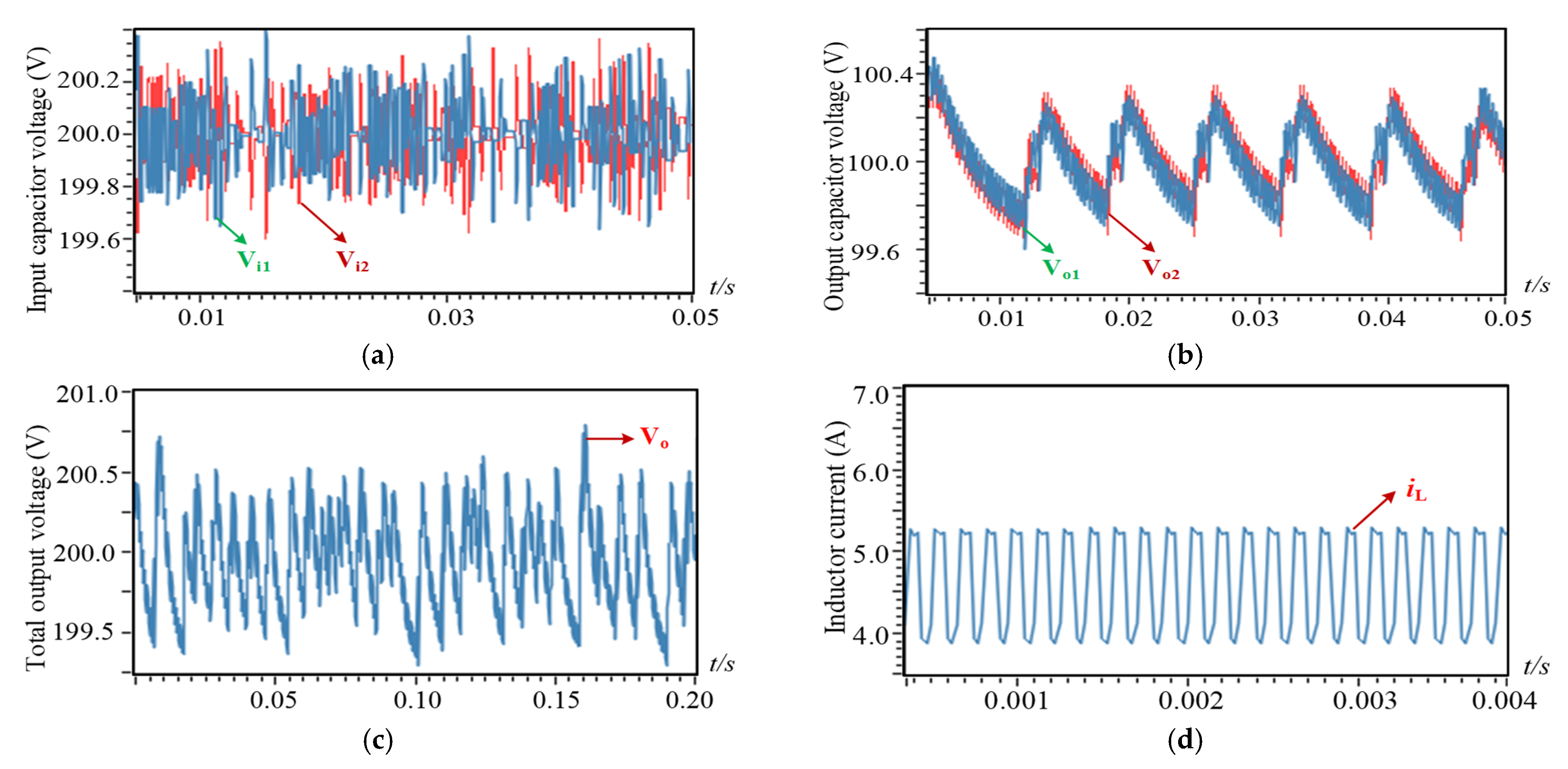

Section 5 validates the effectiveness of the proposed method through hardware-in-the-loop. Finally, the conclusions are presented in

Section 6.

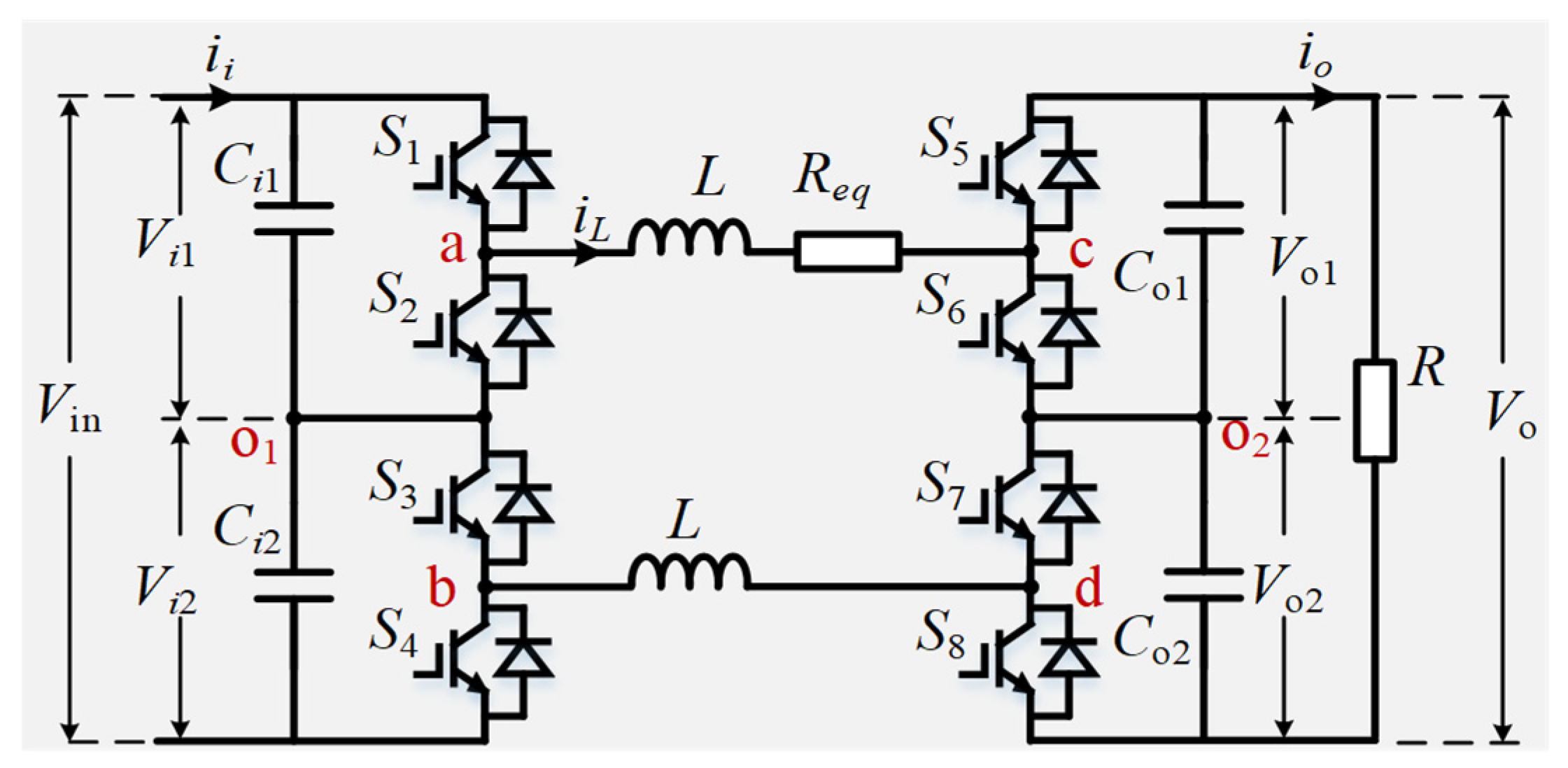

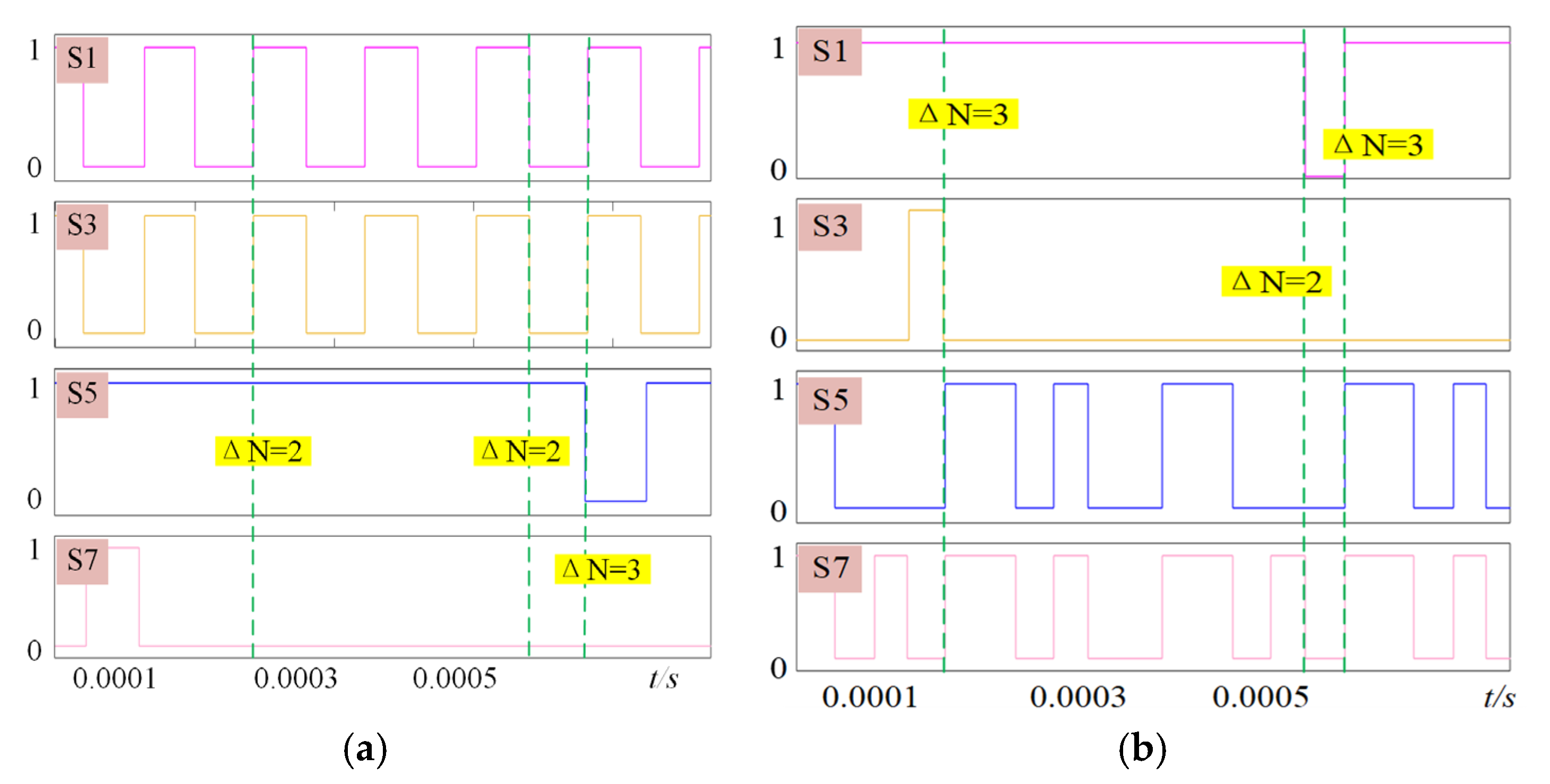

3. Optimization of Multi-Mode Switching States

The discrete-time model is defined by switching state variables Q1–Q4, where each binary variable Qi (i = 1, 2, 3, 4) is constrained to two states (0 or 1). Consequently, 11 distinct mathematical expressions are derived for the discrete-time model. When a conventional MPC algorithm is applied, the discrete state variables must be evaluated 16 times per control cycle, resulting in an excessive computational burden on the controller. More critically, if each switch state is polled exactly according to the inner-loop current prediction, the number of switching actions in the neighboring control cycle is severely increased, and the performance of the converter deteriorates. For instance, a direct transition from the switching state 1010 to 0101 would require all eight switches to be toggled simultaneously, causing significant switching losses that are highly detrimental to converter efficiency. To mitigate these issues, systematic classification and optimization of converter modes are necessitated. The optimization strategies under three operational scenarios—buck mode, boost mode, and transient alternating states—are elaborated in the following sections.

3.1. Switching State Optimization in Buck Mode

The current paths corresponding to the four modes (M1–M4) of the three-level non-inverting converter operating in buck mode are illustrated in

Figure 3. In

Figure 3a, the switching states of

Q1–

Q4 are configured as 1010, where the load power is supplied jointly by the input voltage source and the inductor. In M2, with switching state 1110, the input capacitor

Ci1 and the inductor power the load, causing

Ci1 to discharge. Similarly, for the switching state 0110 shown in

Figure 3c, the load is supplied by the inductor and supporting capacitors, with both

Ci1 and

Ci2 being bypassed. Finally, in

Figure 3d, state 0010 is activated, enabling the load power to be provided by the input-side capacitor

Ci2 and inductor, accompanied by the discharge of

Ci2.

The four operational states of the buck mode are systematically concluded in

Table 1. It is observed that the switching state transitions between adjacent operational states are characterized by a single-bit variation in the states of

Q1–

Q4. Therefore, in order to suppress the drastic increase in the number of switching actions in the adjacent control cycle of the converter, three alternative states in the next control cycle are polled: one is to keep the state of the previous cycle unchanged, and the other two are to go into the adjacent states. Thus, the schematic of the state transfer in buck mode of the three-level converter is obtained, as shown in

Figure 4.

If the current control cycle is in state M1, the range for state optimization in the next control cycle is M1, M2, and M4. As the number of switching actions between M1 and M3 is two, state M3 is excluded in the next cycle. In addition, the decision as to which of the modes, M1, M2, or M4, to select is determined by the cost function described later.

3.2. Switching State Optimization in Boost Mode

The current paths corresponding to the four operational states (M1, M5–M7) of the three-level non-inverting converter in boost mode are illustrated in

Figure 5. In

Figure 5a, the switching states of

Q1–

Q4 are configured as 1010, where the load power is supplied by both the input source and the inductor. In

Figure 5b, the switching states of

Q1–

Q4 are set to 1011. Here, the load power is provided by the output capacitors, while capacitor

Co1 is charged and

Co2 discharged. As shown in

Figure 5c, when the switching states of

Q1–

Q4 are 1001, the load is supplied by supporting capacitors, and energy is stored in both inductors during the state. Finally, in

Figure 5d, the switching states of

Q1–

Q4 are 1000. The load power is provided by the supporting capacitors, with capacitor

Co2 being charged and

Co1 discharged.

Four operational states of the three-level non-inverting converter in boost mode are summarized in

Table 2. Similar to the buck mode, only one switching state variation is permitted between adjacent operational states for switching devices

Q1–

Q4. To mitigate excessive switching actions across consecutive control cycles, the candidate states for the next control cycle are restricted to three possibilities: one is to keep the state of the previous cycle unchanged, and the other two are to go into the adjacent states. A schematic representation of the state transition constraints for boost mode is illustrated in

Figure 6.

If the current control cycle is in state M1, the range for state optimization in the next control cycle is M1, M5, and M7. As the number of switching actions between M1 and M6 is two, state M6 is excluded in the next cycle. In addition, the decision as to which of the modes, M1, M5, or M7, to select is determined by the cost function described later.

3.3. Transient Switching Process Within Two Operation Modes

The state transition processes of the converter in both buck and boost modes are analyzed separately in the preceding sections. However, in practical applications where the input or output voltage varies over a wide range, transitions between buck and boost modes must be considered. Under such conditions, the transitional process between the two modes termed the bridging mode is required to be addressed.

It is worth noting that state M1 is identified as a common mode shared by both buck and boost operations. Therefore, M1 serves as a critical intermediary bridge for mode transitions. When the converter operates in state M1, five potential operational states—M1, M2, M4, M5, and M7—are permitted in the subsequent control cycle. By leveraging M1 as the bridging state, it is ensured that only one switch variation occurs during transients, thereby effectively suppressing excessive switching actions.

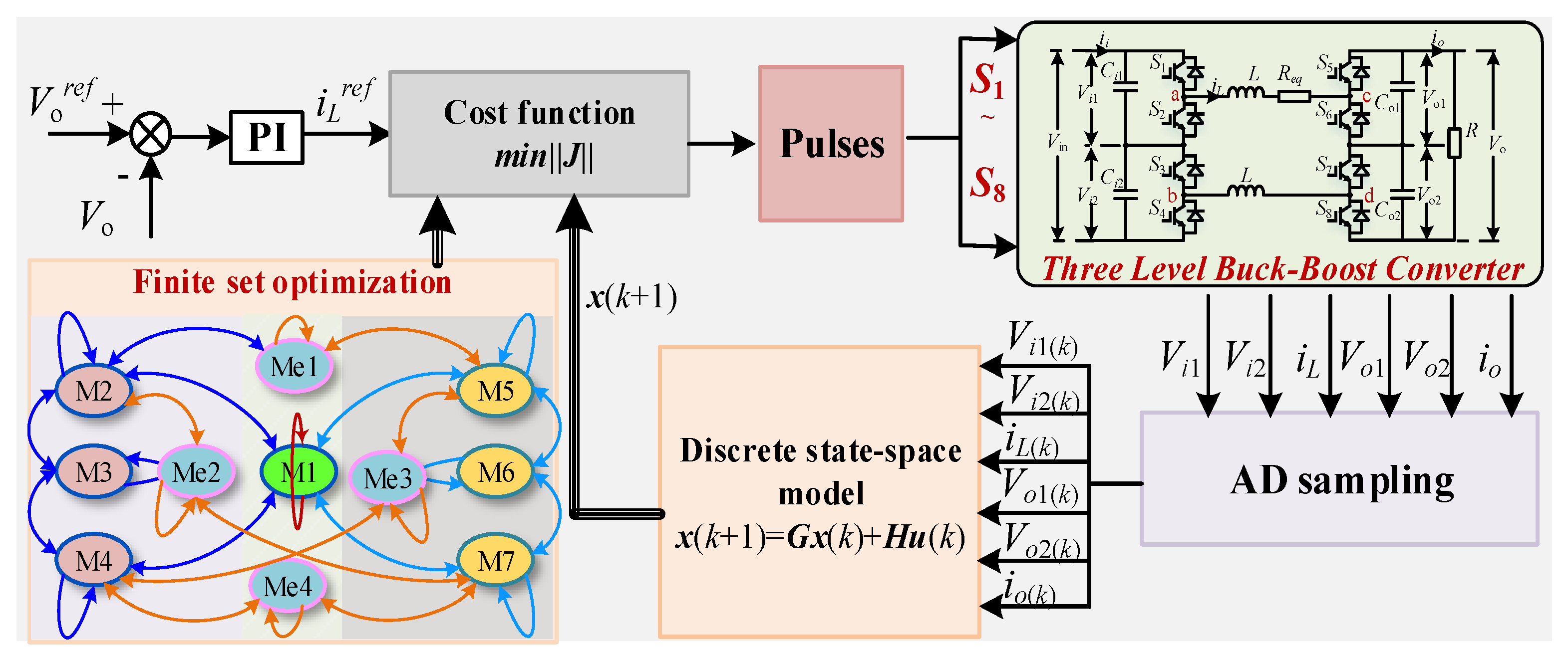

4. The Proposed FCS-MPC

MPC has been widely adopted in power electronics and motor drive systems due to its fast dynamic response, simplified control structure, and straightforward implementation of switching states. For these reasons, the FCS-MPC architecture is adopted in this paper. The block diagram of the proposed FCS-MPC is shown in

Figure 7.

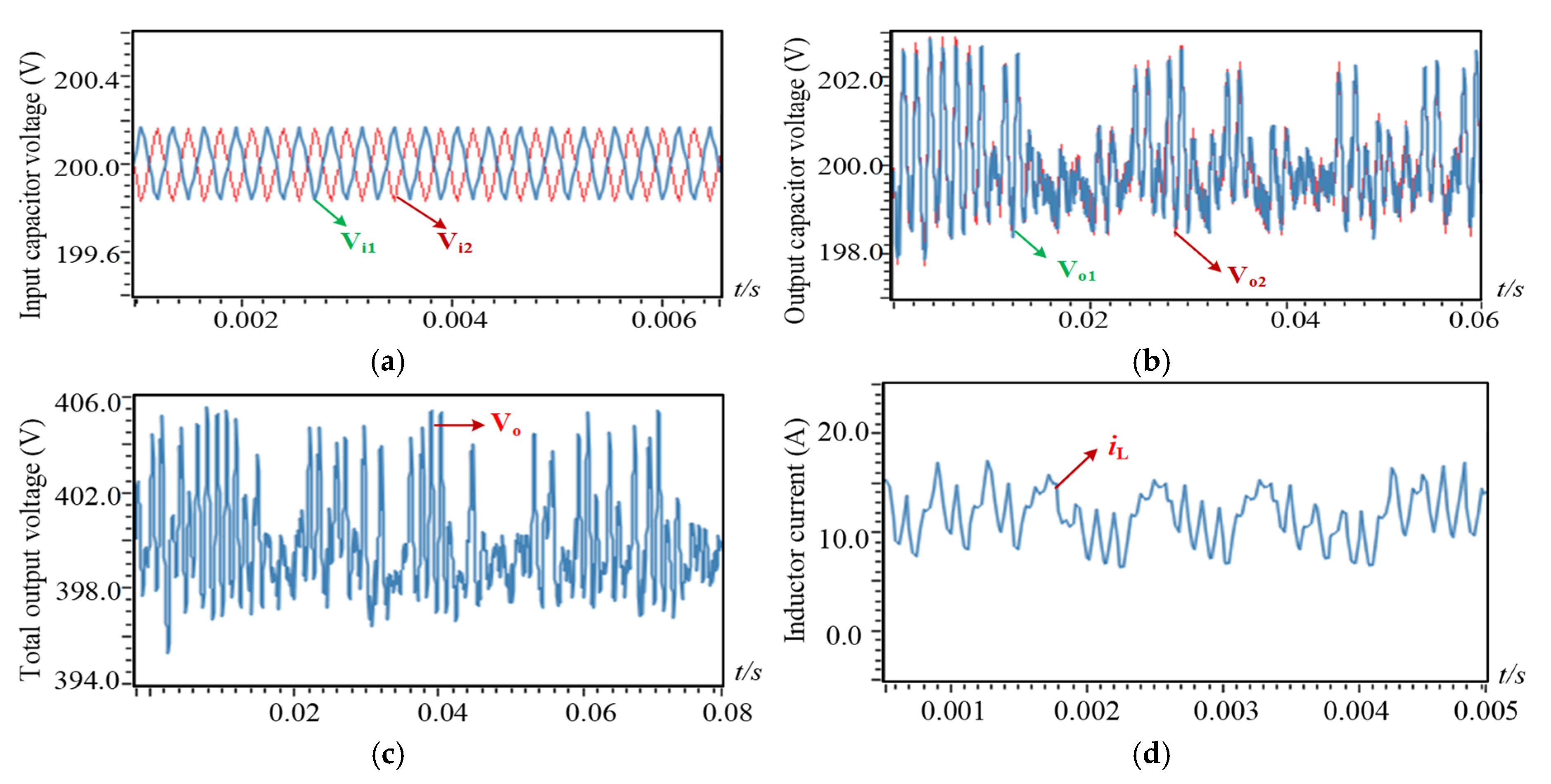

The proposed FCS-MPC method is composed of two control loops: a voltage outer loop and a predictive current inner loop. First, the output voltage Vo is sampled and compared with its reference value Vref. The resulting error is processed by a PI controller, thereby generating the reference current iLref for the inner loop. Furthermore, the input capacitor voltage Vin, output capacitor voltage Vo, and inductor current iL are sampled and substituted into the discrete state-space prediction model (8) to derive the predicted state variables. These predicted values, along with their reference values, are incorporated into the cost function. Subsequently, the cost function is evaluated for all candidate switching states using the proposed operational state optimization strategy. The switching state that minimizes the cost function is selected as the optimal solution across the next control cycle. Finally, the corresponding pulse signals are distributed to the switching devices.

4.1. Selection of the Cost Function

As illustrated in

Figure 7, the reference current for the inner loop is obtained via the outer-loop voltage PI controller. To ensure accurate tracking of the inductor current, the inductor current is incorporated into the cost function. However, a critical concern arises from the three-level topology: both the input and output voltages are the sum of two capacitor voltages. If the upper and lower capacitor voltages are not actively regulated, voltage unbalance may be induced, leading to capacitor voltage deviation. More critically, such deviation can result in uneven voltage stress across the switching devices, which may ultimately lead to device failure due to overvoltage under severe conditions. Therefore, to effectively balance the capacitor voltages on both the input and output sides, the capacitor voltages should also be included as control objectives in the cost function. Therefore, the cost function can be formulated as follows:

where

λ1 and

λ2 are designated as the weighting coefficients for output-side voltage balancing control and input-side voltage balancing control, respectively. The cost function is formulated with four terms: inductor current tracking, output-side voltage balancing, input-side voltage balancing, and inductor current limitation. To address overcurrent issues,

λiL_limit is introduced as the weighting coefficient for inductor current protection. Specifically, the inductor current is constrained to prevent excessive values, and thus,

λiL_limit is defined as follows:

where

iL_max is defined as the inductor current protection threshold. Once the predicted inductor current exceeds

iL_max, the weighting coefficient is set to infinity, thereby ensuring that the corresponding switching states are excluded from consideration. Conversely, when the current below

iL_max, the weighting coefficient is assigned as zero, eliminating its impact on the remaining terms of the cost function.

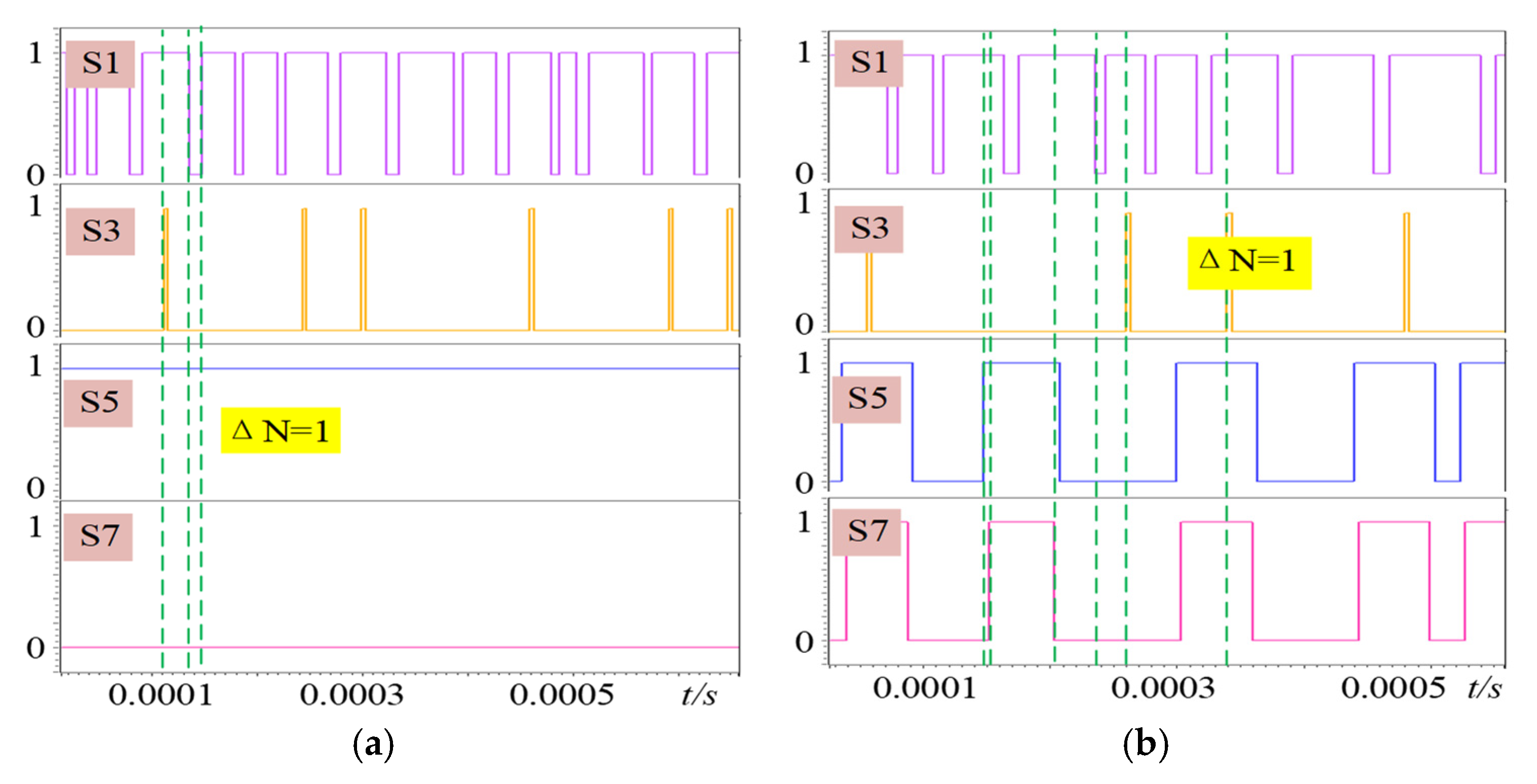

4.2. Switching State Optimization Based on Capacitor Voltage Balance Control

After the cost function is finalized, the switching states for each control cycle are optimized such that the following objectives are achieved:

When the converter operates in buck mode, the switching states are polled and optimized among M1–M4. It is noteworthy that, in buck mode, voltage balancing of the input-side capacitors can be achieved by adjusting the duration of states M2 and M4. However, output-side capacitor voltage unbalance cannot be resolved through modes M1–M4. Therefore, to ensure simultaneous voltage balancing on both input and output sides, four additional modes (Me1–Me4) are introduced. The rules for the additional state introductions should be satisfied:

- (1)

Voltage balancing on both input and output sides must be achievable in any selected mode.

- (2)

The number of switching actions during transitions between adjacent modes must be minimized.

By adhering to these rules, the four supplementary states are incorporated into the control set, as illustrated in

Figure 8.

Similarly, to ensure input-side capacitor voltage balancing in boost mode, the aforementioned four supplementary states (Me1–Me4) are incorporated into it. Consequently, the optimized mode selection diagram in

Figure 7 is revised and reoptimized as shown in

Figure 9. By evaluating all candidate states through (16), the state that satisfies the predefined conditions is selected as the optimal solution for the subsequent control cycle. Notably, out of the total 16 possible switching states, only 11 states are utilized in the proposed control strategy, with the remaining 5 states excluded from consideration.

Since only one switching state variation is permitted between consecutive control cycles, the subsequent candidate states are restricted to M1, M2, M3, Me1, and Me2 when the current state is M2 and input voltage unbalance occurs. If voltage deviation dominates the cost function, the converter may oscillate among M2, M3, and Me2, failing to reach M4 and causing optimization failure. To ensure effective optimization, mode M4 is forcibly included in the candidate set when the converter operates in M2 at moment k. If mode M4 is determined as the optimal state for moment k + 1 via cost function evaluation, mode M1 is temporarily applied at moment k + 1, enabling a feasible transition to M4 at moment k + 2 while maintaining the single switch variation constraint. This strategy prevents optimization failure while ensuring minimal switching actions. A similar approach is adopted for modes M5 and M7.

Therefore, switching transitions are strictly confined to adjacent modes, significantly reducing the computational overhead of state polling and suppressing unnecessary switching state changes.

4.3. Optimal Control Algorithm for Three-Level Non-Inverting Buck–Boost Converter

To elaborate on the proposed MPC algorithm, the procedural flowchart of the control strategy is illustrated in

Figure 10. The steps of the FCS-MPC are detailed as follows:

First, the previous switching state M

i(k) is analyzed, and the cost function is initialized with J

opt = ∞. Subsequently, the input voltage, output voltage, and inductor current of the buck–boost converter are sampled. Based on the state transition diagram in

Figure 9, the candidate switching states for the current control cycle are identified, and the total number of candidate modes is denoted as N. The indices of all candidate states are stored in an array order [N]. Following this, the cost function values for all N candidate states are computed using (14). If the candidate cost function value J

j is found to be less than J

opt, J

j is assigned to J

opt, and the index j is recorded. After all N states are polled, the j-th state is selected as the optimal state for the next control cycle, and the corresponding eight switching pulse signals are generated. Finally, the switching devices are driven via the gate driver circuit.

The aforementioned process is repeated for each control cycle, iteratively determining the optimal state while minimizing computational overhead and switching transients.