Active-Clamp Dual-Transformer ZVS Flyback Converter

Abstract

1. Introduction

- (1)

- Resonant Converter [3]

- (2)

- Quasi-resonant Converter (QRC) [4]

- (3)

- (4)

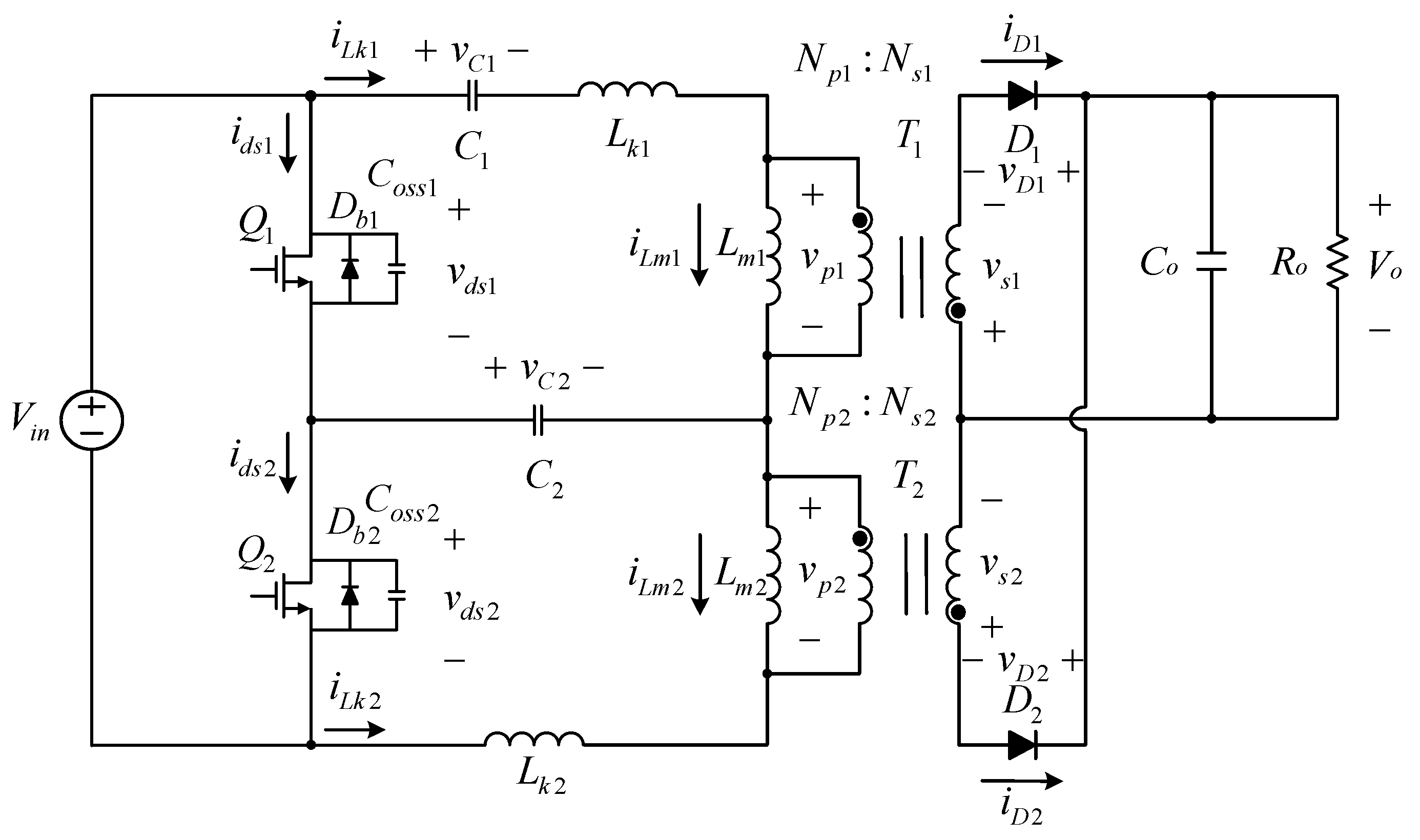

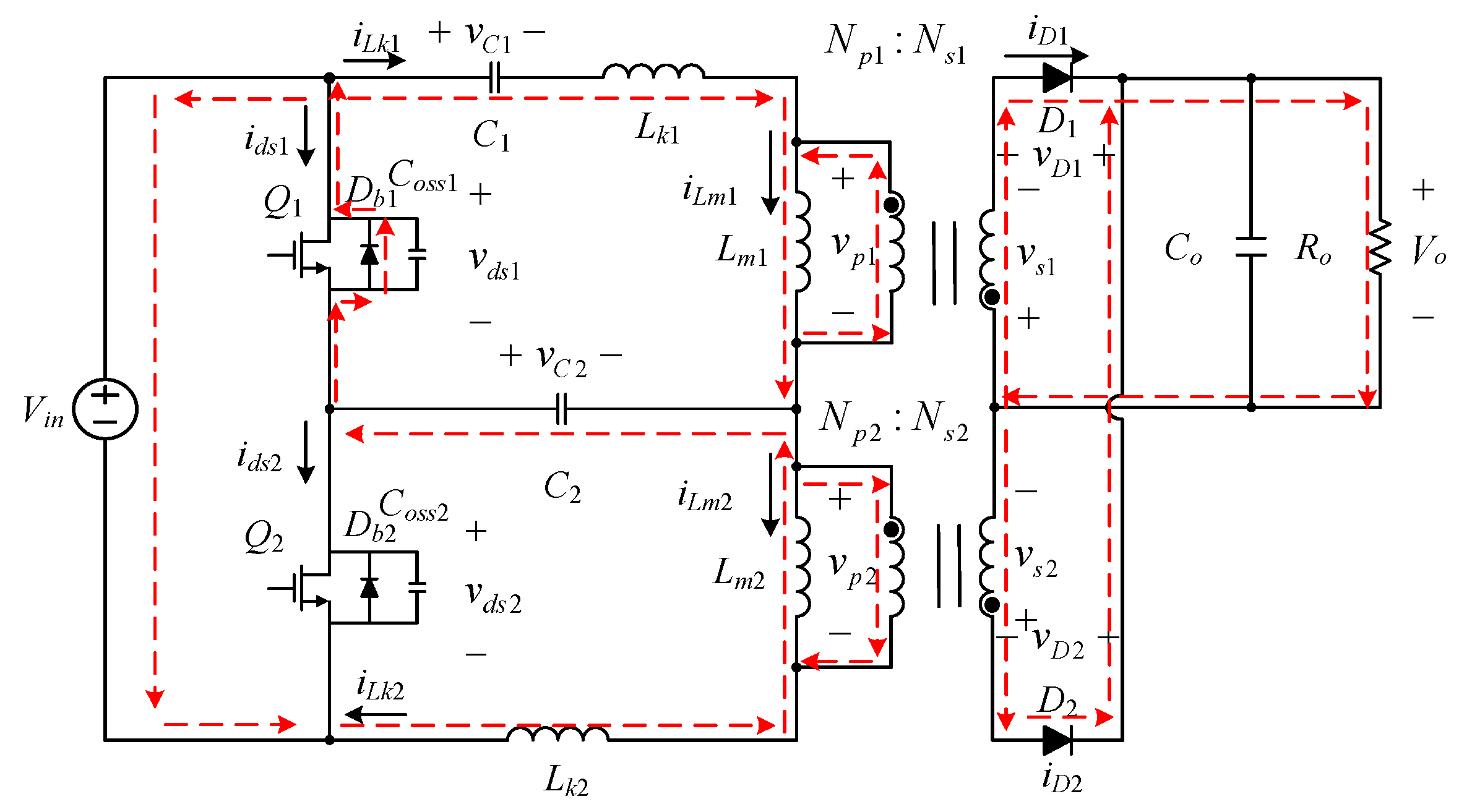

2. Proposed Active-Clamp Dual-Transformer ZVS Flyback Converter

2.1. Symbol Definitions and Assumptions

- (1)

- Vin is the input DC voltage, the output capacitance Co is large enough, and the output voltage is denoted as Vo.

- (2)

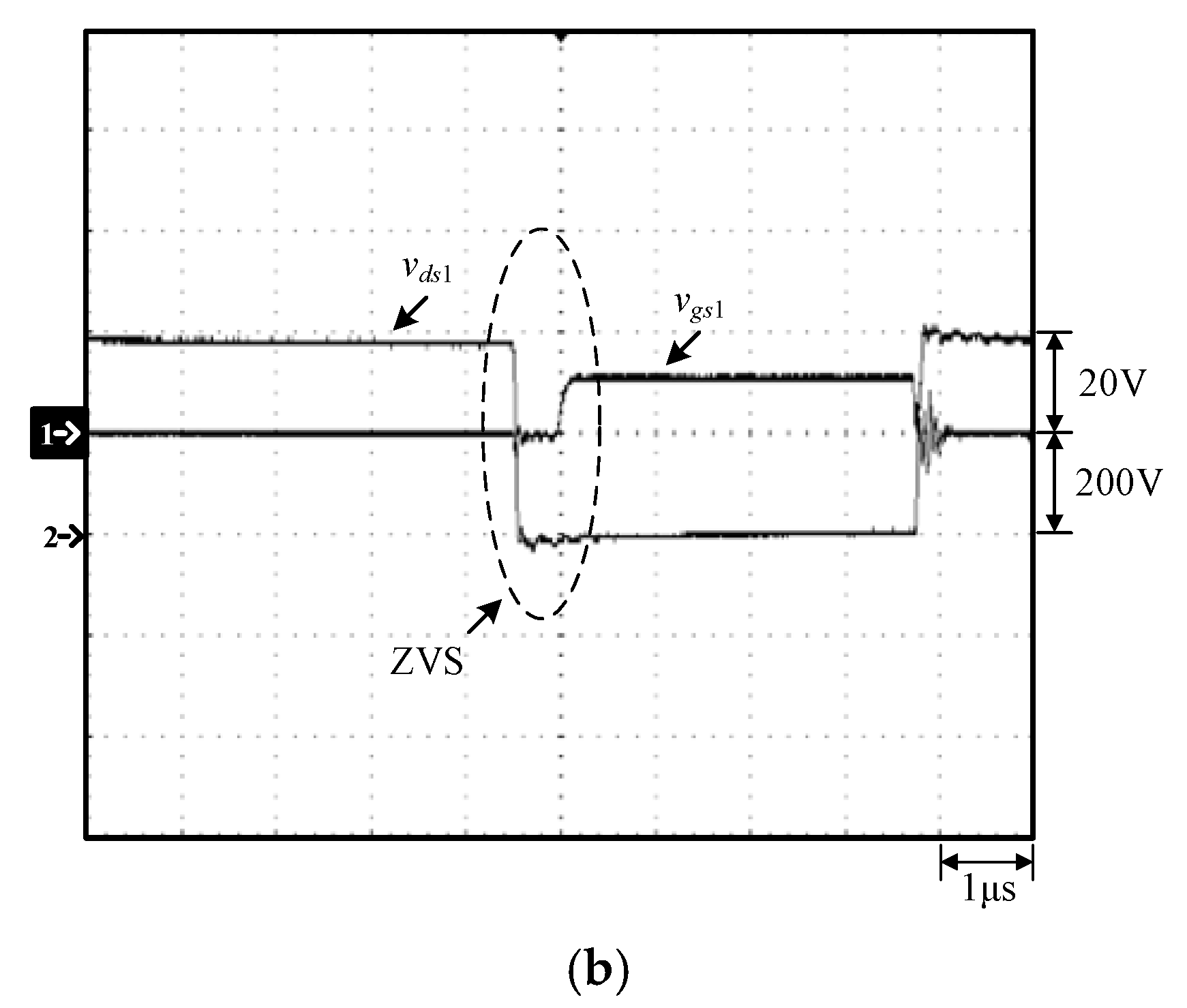

- Db1 and Db2 are the body diodes of the auxiliary switch Q1 and the main switch Q2, respectively; Coss1 and Coss2 are the output capacitors of the auxiliary switch Q1 and the main switch Q2, respectively.

- (3)

- ids1 and ids2 are the currents in the auxiliary switch Q1 and the main switch Q2, respectively; vds1 and vds2 are the voltages on the auxiliary switch Q1 and the main switch Q2, respectively; vgs1 is the gate driving signal for the auxiliary switch Q1, vgs2 is the gate driving signal for the main switch Q2, and these two signals are complementary signals, namely, 1 − D and D for Q1 and Q2, respectively.

- (4)

- Lk1 and Lk2 are the leakage inductances of the first transformer and the second transformer, respectively, and are also the resonant inductances; Lm1 and Lm2 are the magnetizing inductances of the first transformer and the second transformer, respectively.

- (5)

- iLk1 and iLk2 are the leakage inductance currents of the first transformer and the second transformer, respectively, and are also the resonant inductor currents; iLm1 and iLm2 are the magnetizing inductance currents of the first transformer and the second transformer, respectively.

- (6)

- Np1 and Ns1 are the turns of the primary and secondary sides of the first transformer, and their turns ratio is ; Np2 and Ns2 are the turns of the primary and secondary sides of the second transformer, and their ratio is ; let .

- (7)

- vp1 and vp2 are the primary-side voltages of the first transformer and the second transformer, respectively; vs1 and vs2 are the secondary-side voltages of the first transformer and the second transformer, respectively.

- (8)

- vC1 and vC2 are the voltages on the clamping capacitor C1 and the energy-capacitor C2, respectively.

- (9)

- vD1 and vD2 are the voltages on two output rectifier diodes D1 and D2, respectively; iD1 and iD2 are the currents in two output rectifier diodes D1 and D2, respectively.

- (10)

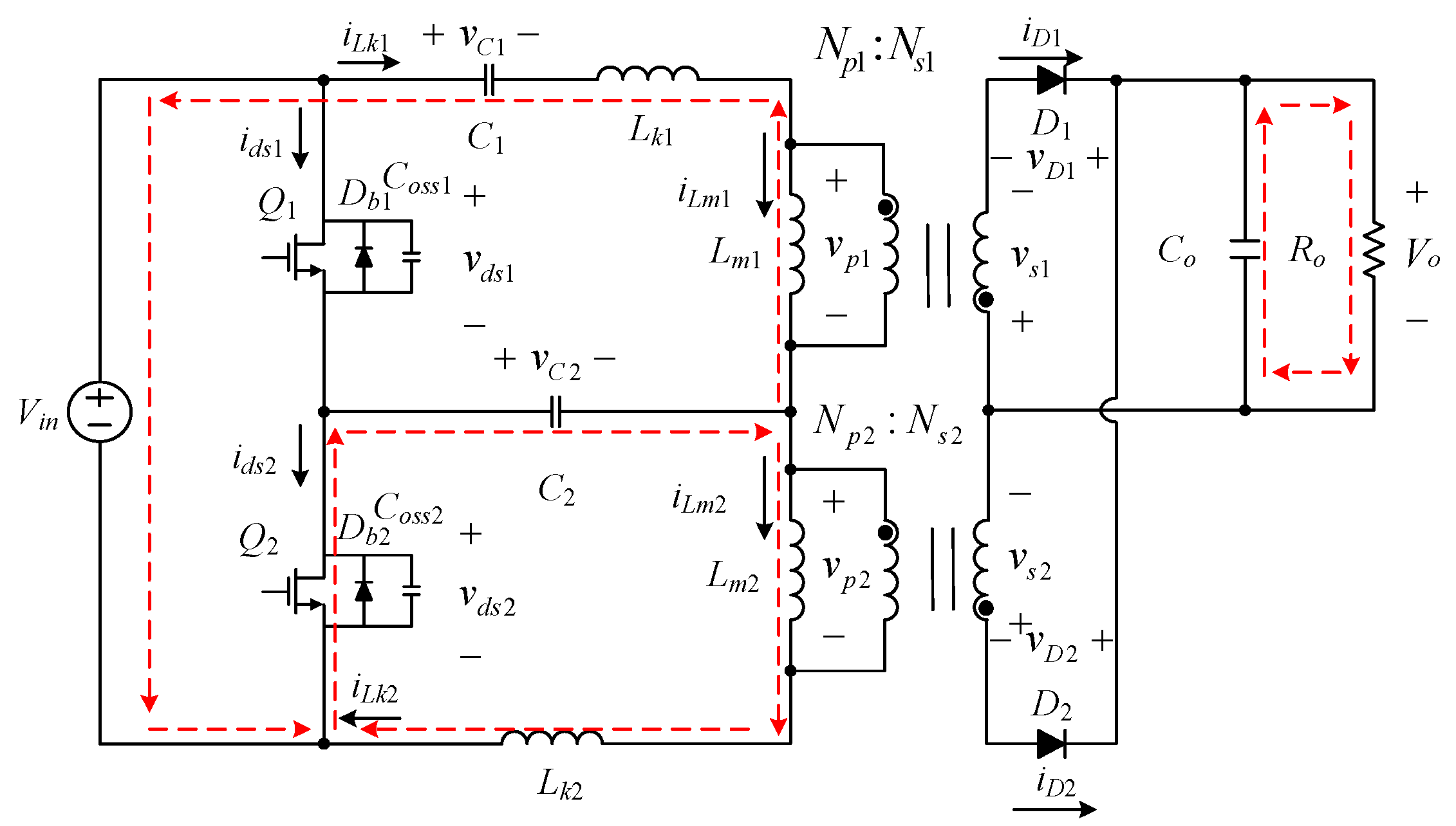

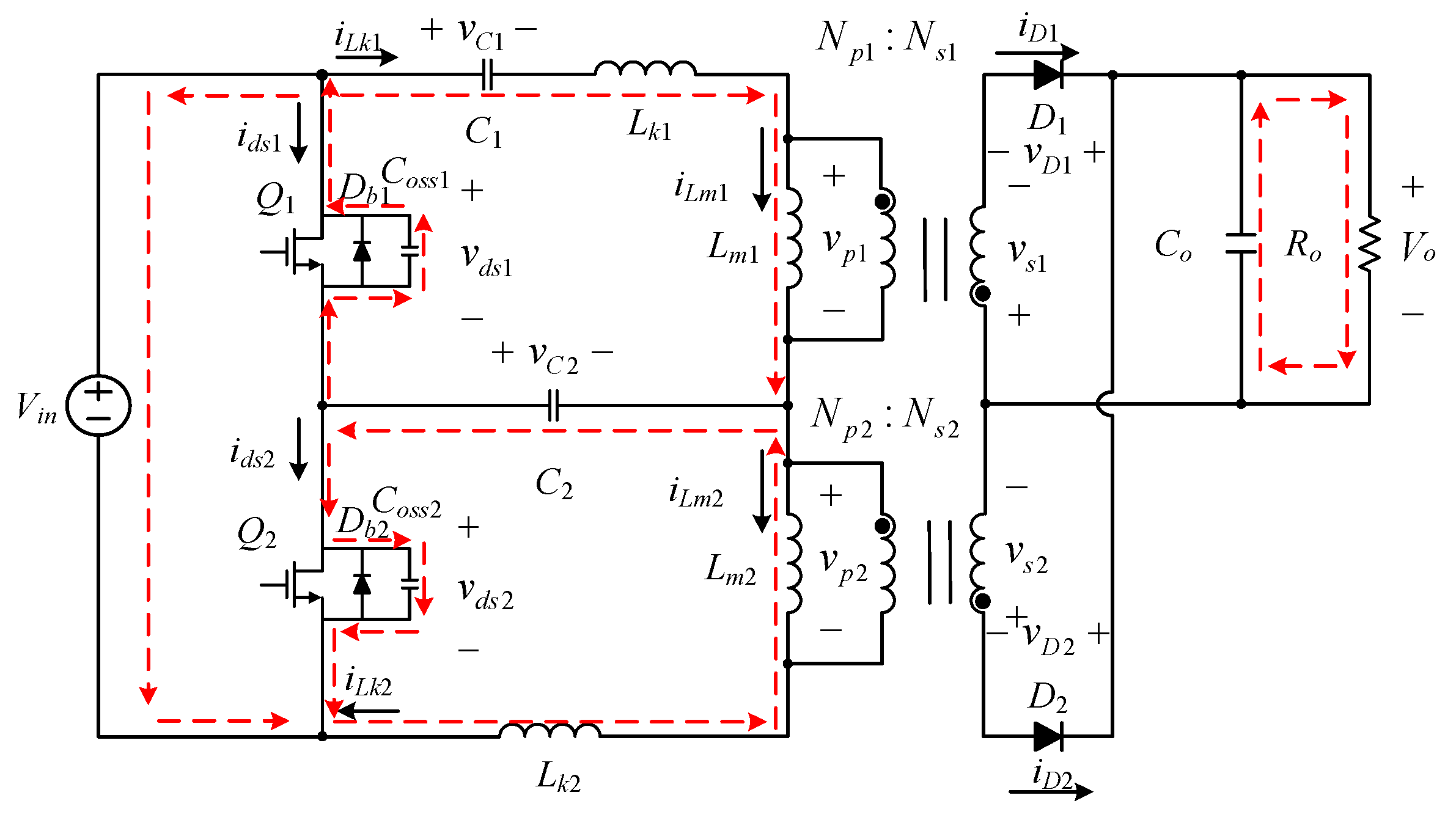

- For brief analysis convenience, the circuit is operated under positive and negative currents, and Figure 2 shows the behavior of the circuit in one cycle. For brief analysis convenience, only the time interval between t0 and t6 will be taken into account; that is, the positive magnetizing current of T1 and the negative magnetizing current of T2 both occurring at the same time will be discussed.

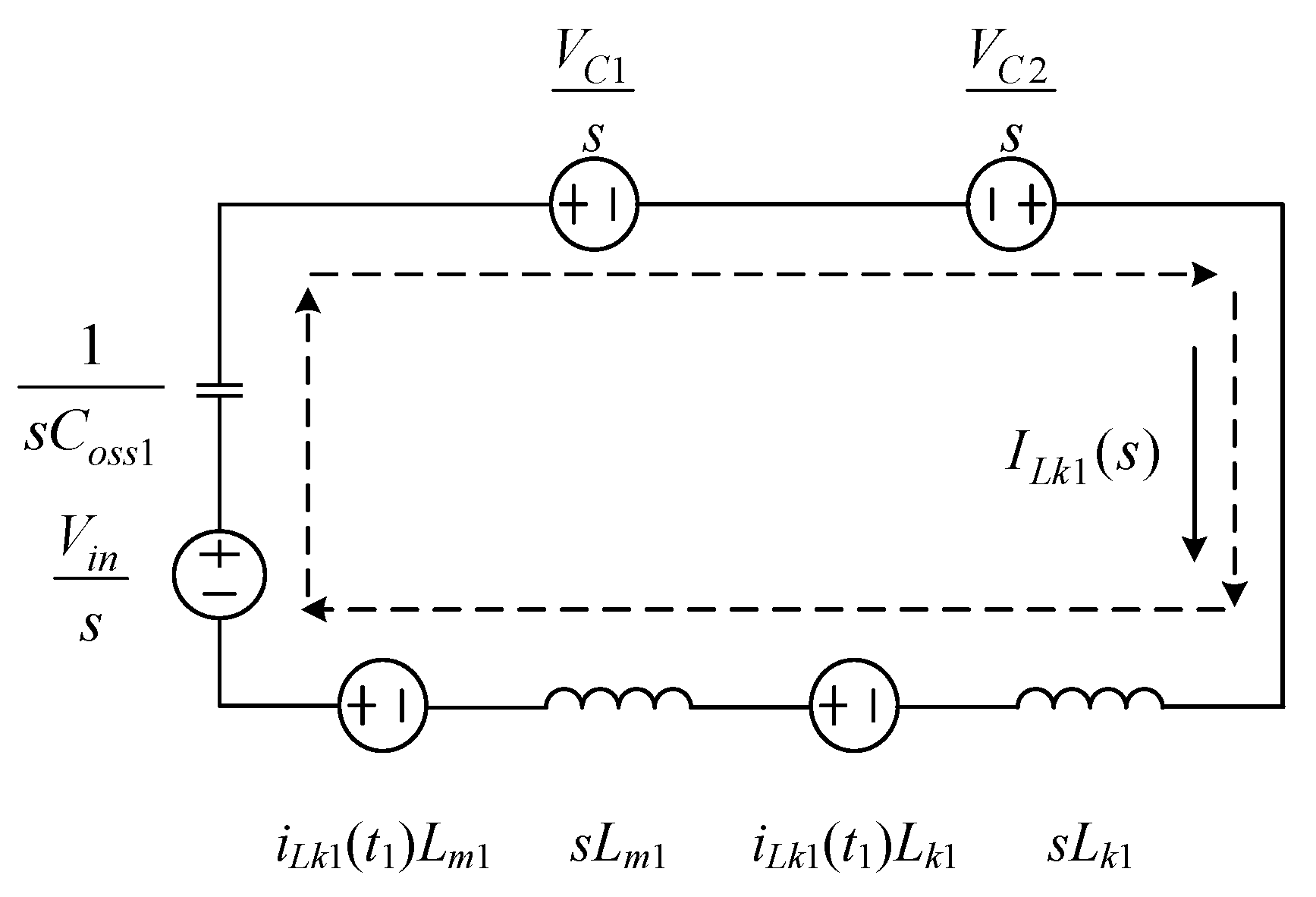

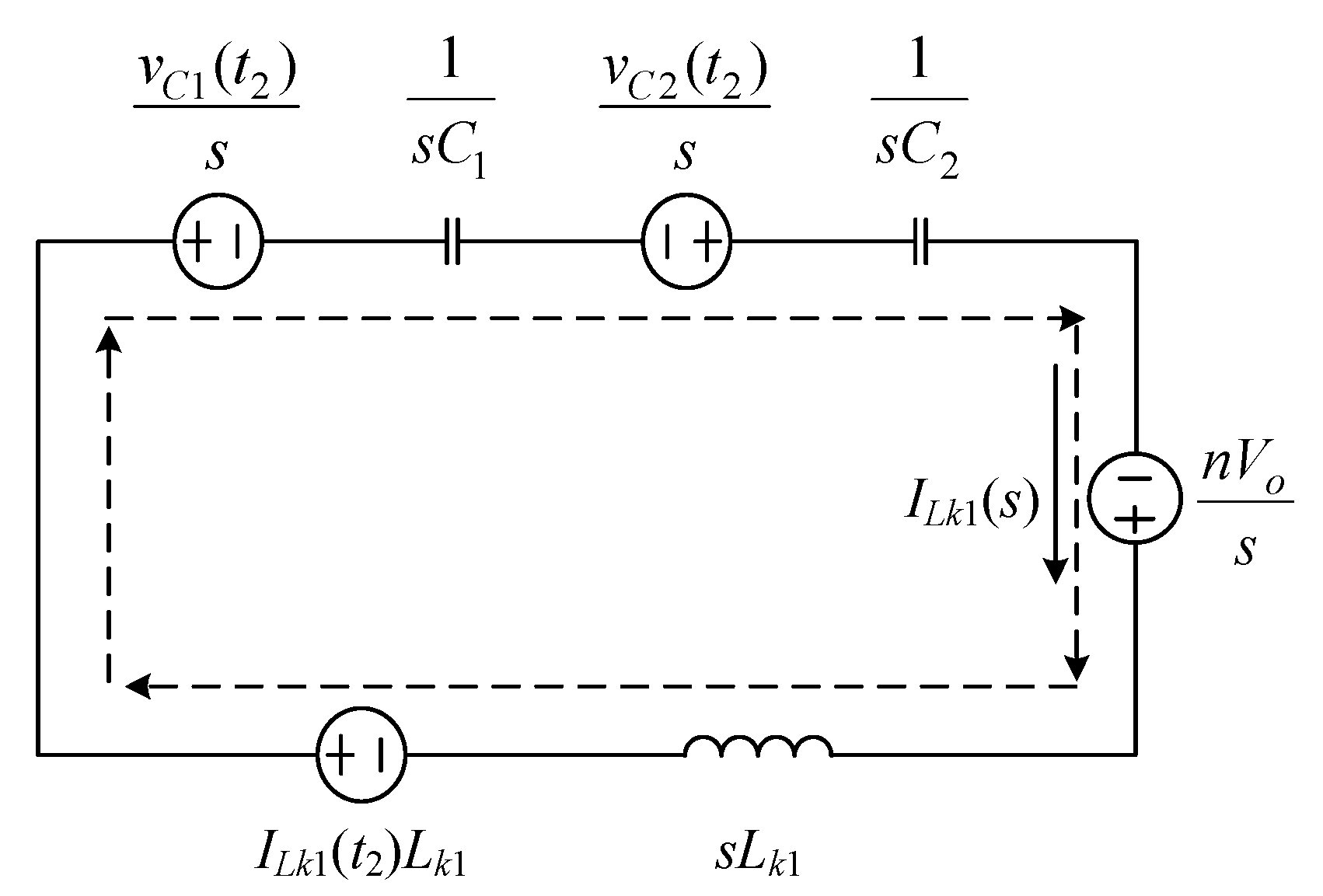

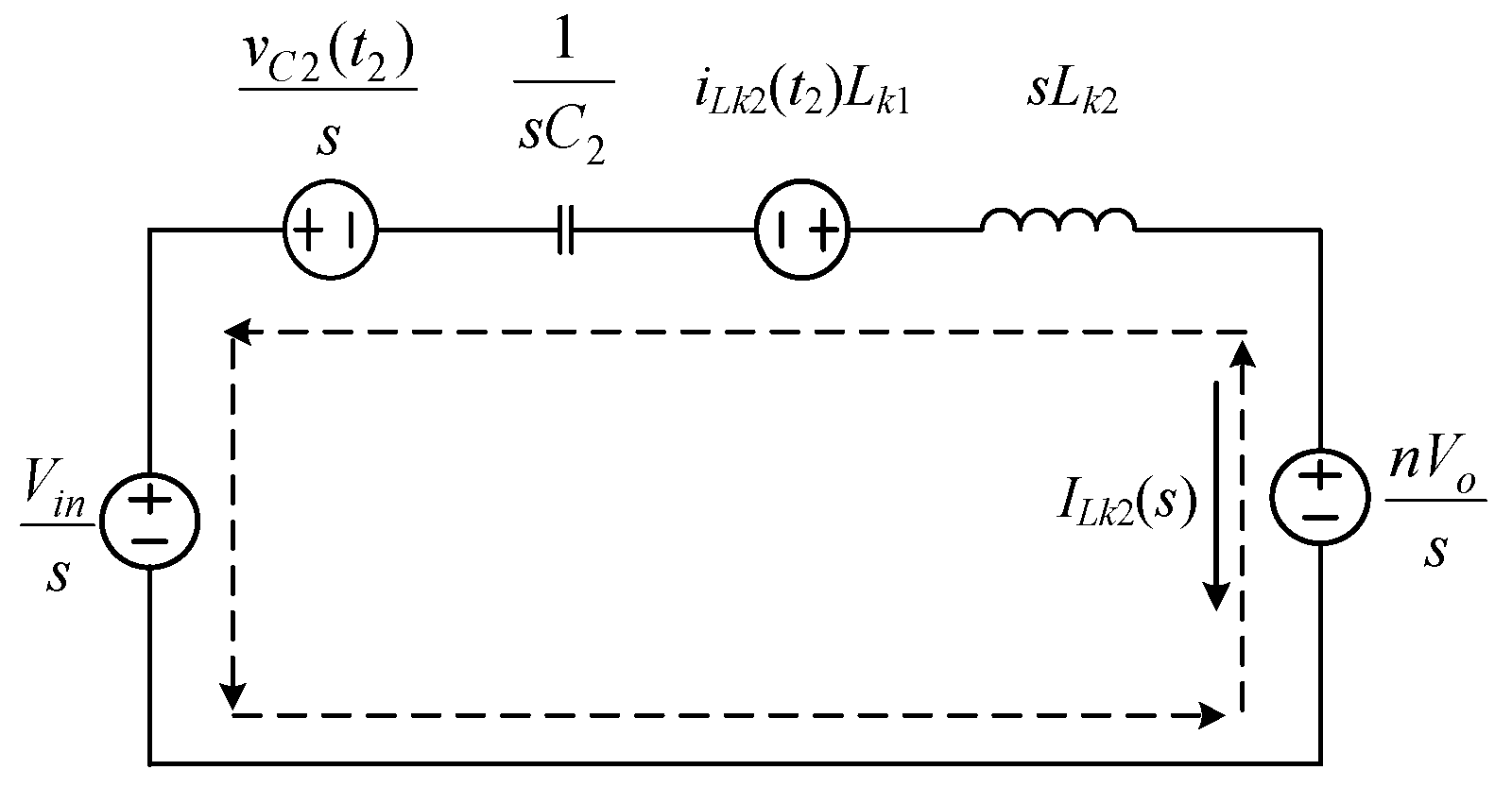

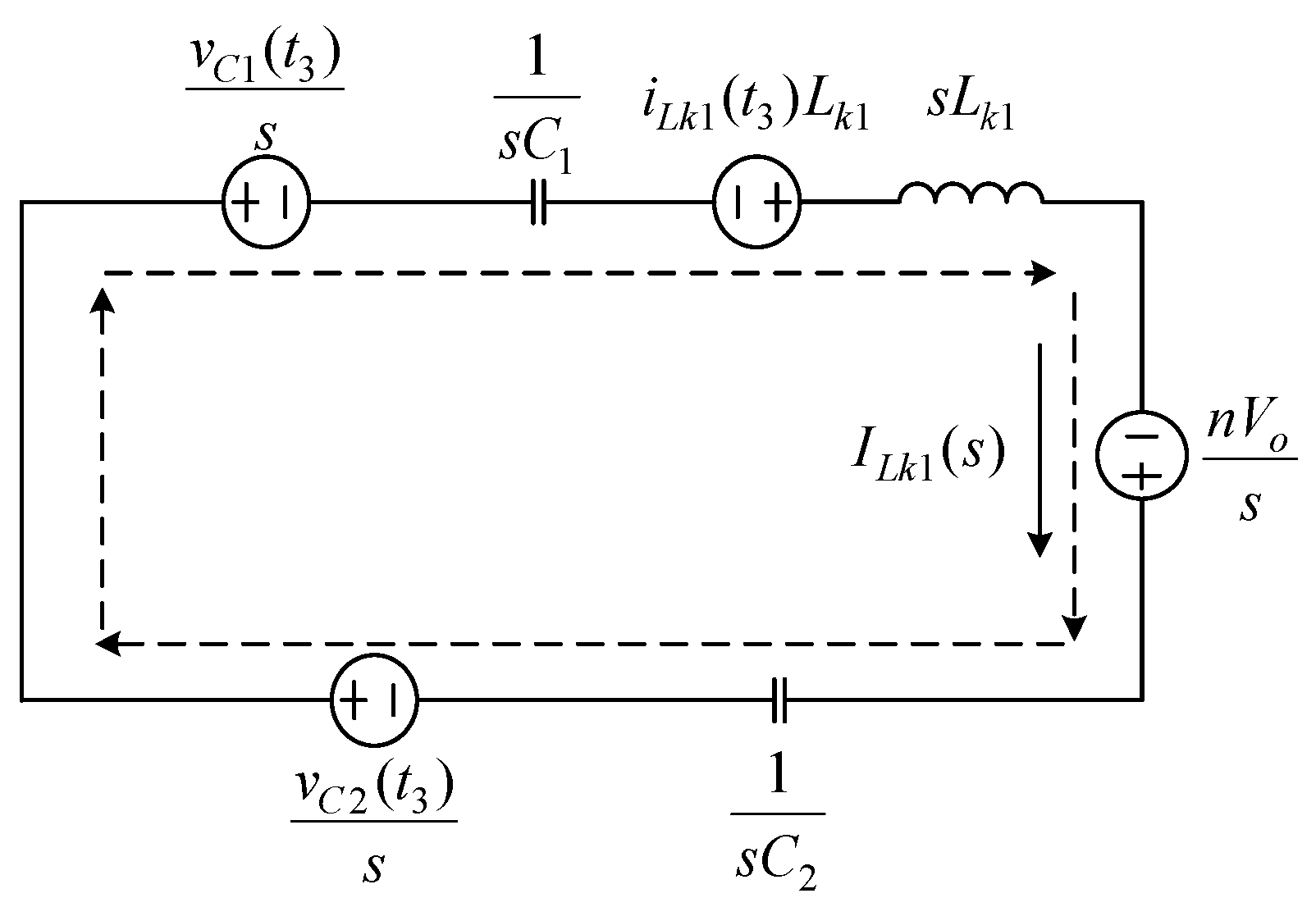

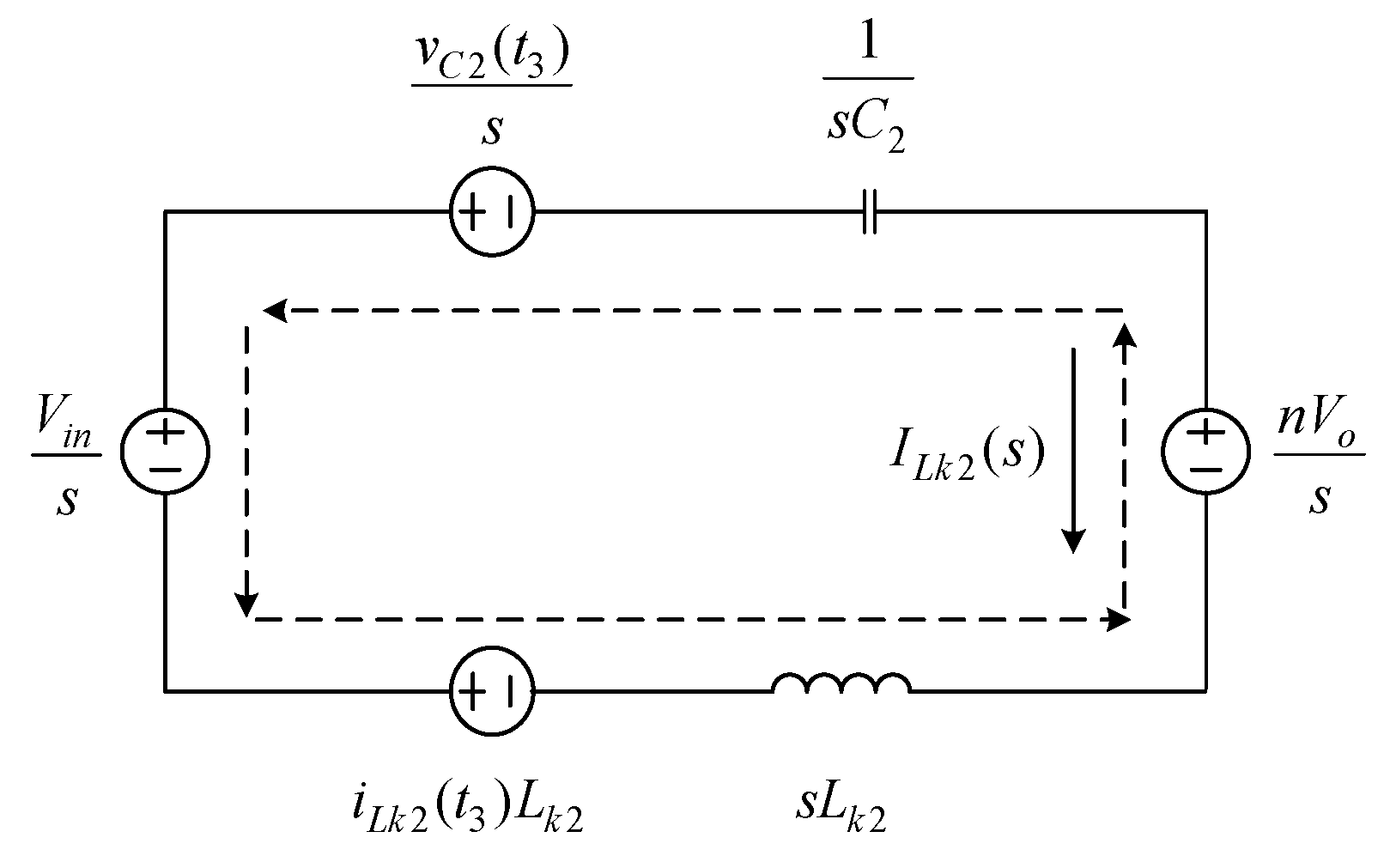

2.2. Operating Principle

2.3. Voltage Gain

3. Design Considerations

3.1. System Configuration

3.2. System Specifications

3.3. Parameter Design

3.3.1. Design of Magnetizing Inductance Lm1 of First Transformer

Turns Ratio n1

Design of Magnetizing Inductance Lm.1 for the First Transformer

3.3.2. Design of Magnetizing Inductance Lm2 of Second Transformer

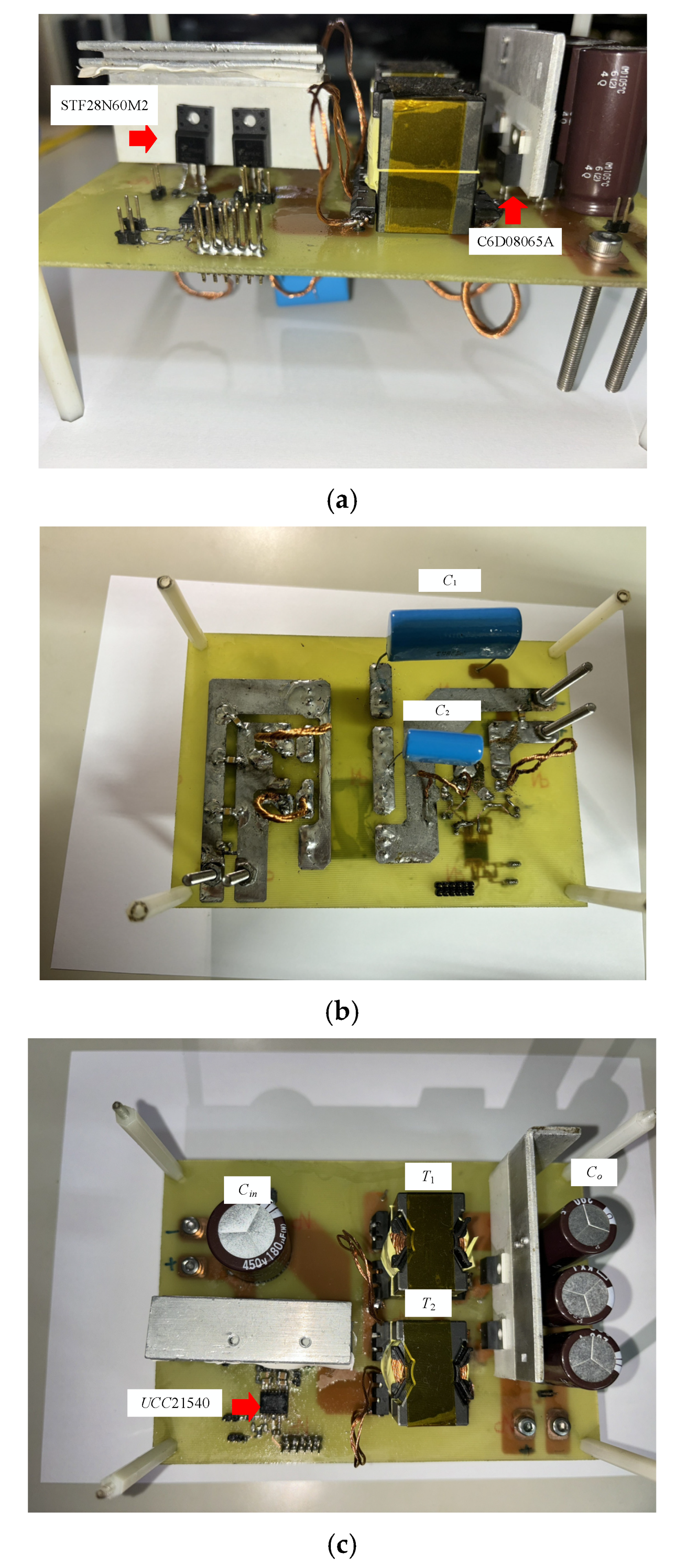

3.3.3. Design of Clamping Capacitor C1 and Energy-Transferring Capacitor C2

4. Experimental Results

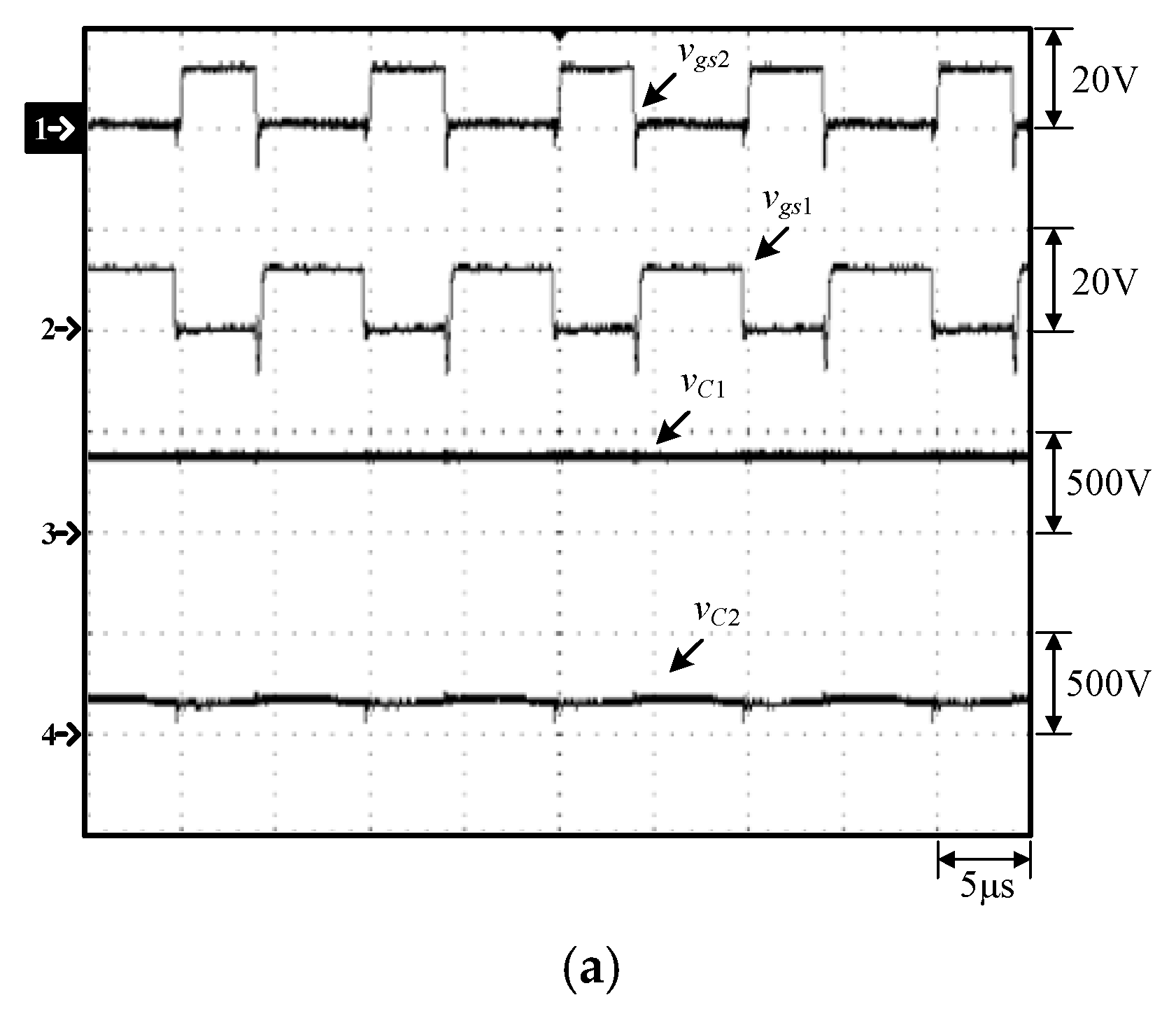

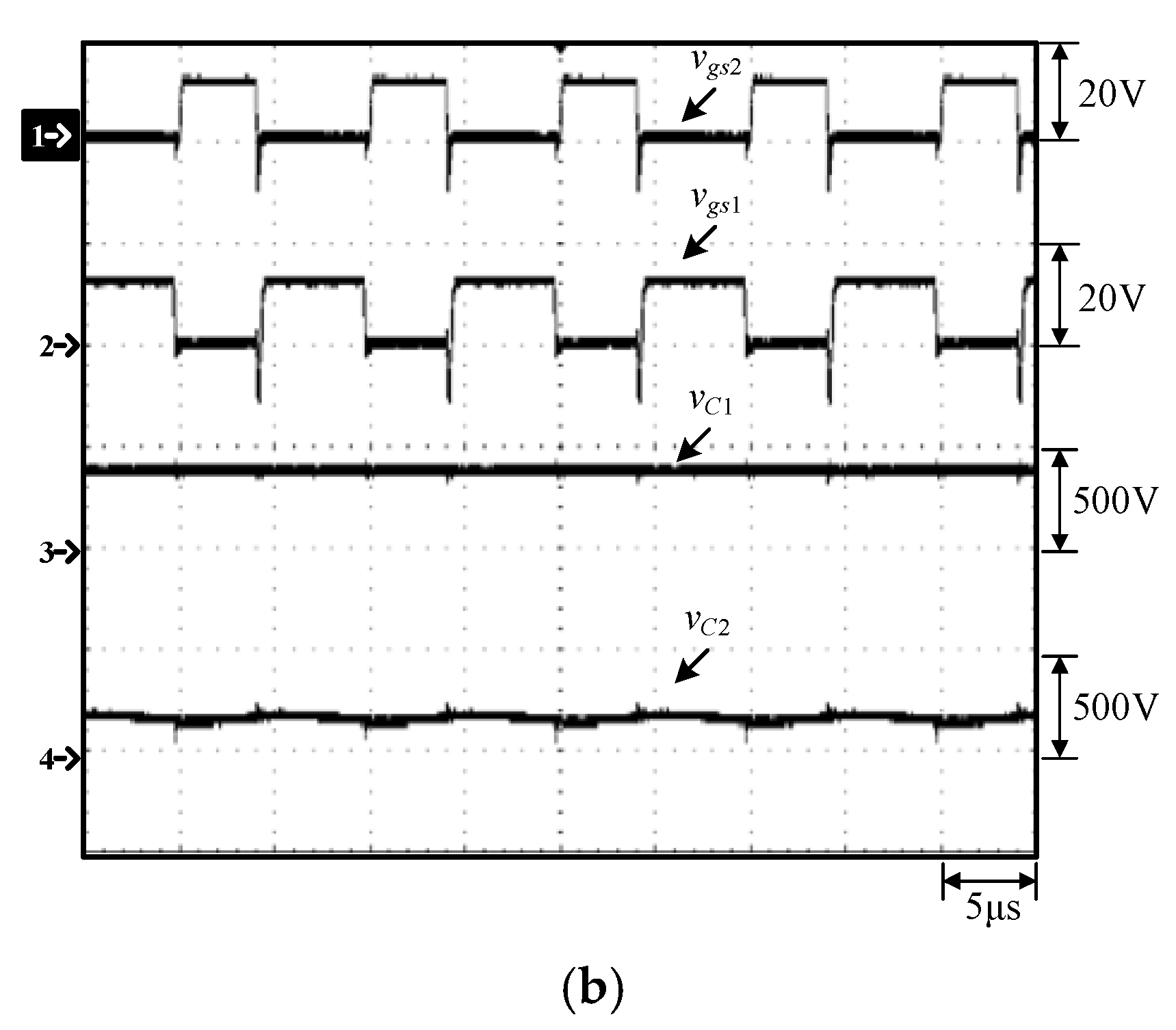

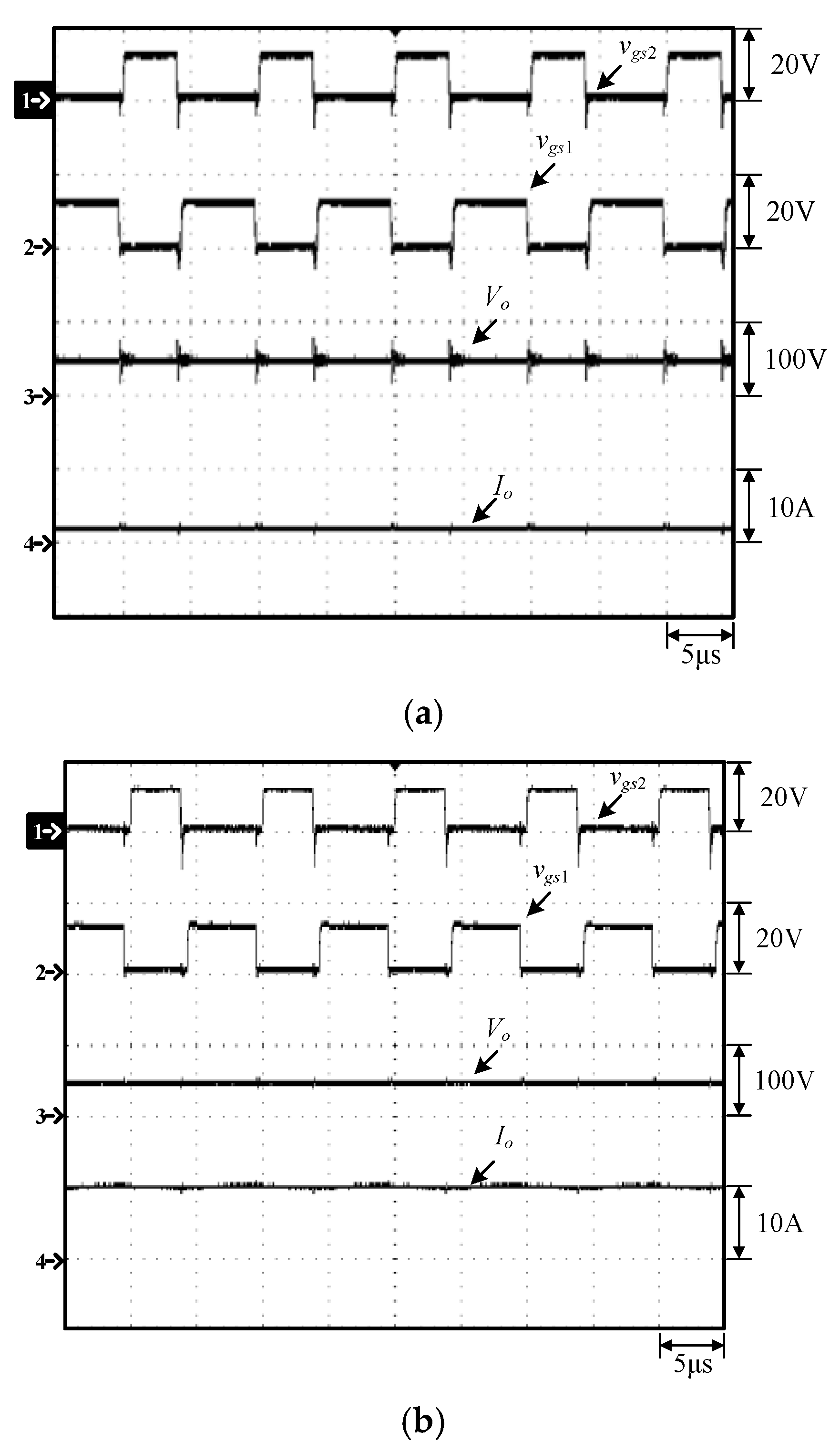

4.1. Measured Waveforms and Discussions

4.2. Comparison Between Proposed and Other Topologies

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Ali, A.; Khan, S.A.; Khan, M.U.; Ali, H.; Mughal, M.R.; Praks, J. Design of modular power management and attitude control subsystems for a microsatellite. Int. J. Aerosp. Eng. 2018, 2018, 2515036. [Google Scholar] [CrossRef]

- Khan, S.A.; Ali, A.; Tahir, M.; Tao, Z. Efficient power conditioning: Enhancing electric supply for small satellite missions. Aerospace 2024, 11, 920. [Google Scholar] [CrossRef]

- Tabisz, W.A.; Lee, F.C. Zero-voltage-switching multi-resonant technique-a novel approach to improve performance of high frequency quasi-resonant converters. In Proceedings of the IEEE Power Electronics Specialists Conference, Kyoto, Japan, 11–14 April 1998; pp. 9–17. [Google Scholar]

- Jia, P.; Su, Z.; Shao, T.; Mei, Y. An isolated high step-up converter based on the active secondary-side quasi-resonant loops. IEEE Trans. Power Electron. 2022, 37, 659–673. [Google Scholar] [CrossRef]

- Akhlaghi, B.; Farzanehfard, H.; Thiruvady, D.; Faraji, R.; Shiri, F. ZVT interleaved high step-up converter for renewable energy systems. In Proceedings of the 14th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Babol, Iran, 31 January–2 February 2023; pp. 1–6. [Google Scholar]

- Javed, U.; Veerachary, M. ZVT boost converter integrated with charging and discharging topologies. In Proceedings of the IEEE International Power and Renewable Energy Conference (IPRECON), Kollam, India, 24–26 September 2021; pp. 1–6. [Google Scholar]

- Rani, N.C.; Amuthan, N. THD minimization of ZVT-ZCT quasi resonant SEPIC converter with proposed Harris Hawks optimization technique. In Proceedings of the 10th International Conference on Computing for Sustainable Global Development (INDIACom), New Delhi, India, 15–17 March 2023; pp. 1149–1154. [Google Scholar]

- Bodur, H.; Yıldırmaz, S. A new ZVT snubber cell for PWM-CCM boost converters. In Proceedings of the 25th European Conference on Power Electronics and Applications (EPE’23 ECCE Europe), Aalborg, Denmark, 4–8 September 2023; pp. 1–6. [Google Scholar]

- Guo, Y.L.; Chen, X.Y.; Sun, Z.; You, X. Analytical dVCE/dt model of high-power trench gate/field-stop IGBT modules considering dynamical conduction current at near-ZCT transient. IEEE J. Emerg. Sel. Top. Power Electron. 2024, 12, 4993–5003. [Google Scholar]

- Yau, Y.-T.; Hwu, K.-I.; Shieh, J.-J. Simple structure of soft switching for boost converter. Energies 2020, 13, 5448. [Google Scholar] [CrossRef]

- Hwu, K.-I.; Shieh, J.-J.; Jiang, W.-Z. Interleaved boost converter with ZVT-ZCT for main switches and ZCS for auxiliary switch. Appl. Sci. 2020, 10, 2033. [Google Scholar] [CrossRef]

- Hwu, K.-I.; Lin, Z.-F.; Tseng, P.-C. Boost converter with main switch possessing ZVT and ZCT and auxiliary switch possessing ZCS. Energies 2023, 16, 5504. [Google Scholar] [CrossRef]

- Wang, L.; Li, H.; Li, S. Burst mode control of active-power-decoupling integrated active clamp flyback PFC rectifiers. IEEE Trans. Power Electron. 2023, 38, 6337–6350. [Google Scholar] [CrossRef]

- Tang, C.-Y.; Lin, W.-Z.; Tan, Y.-C. An active clamp flyback converter with high precision primary-side regulation strategy. IEEE Trans. Power Electron. 2022, 37, 10281–10289. [Google Scholar] [CrossRef]

- Yan, Y.; Wang, T.; Wang, Y.; Zhu, M.; Tang, H.; Qian, Q. Adaptive dead-time and partial-ZVS regulation for GaN-based active clamp flyback converter with predictive hysteresis current mode control. IEEE Trans. Power Electron. 2023, 38, 10782–10797. [Google Scholar] [CrossRef]

- Rao, B.T.; De, D. A coupled inductor-based high-gain ZVS DC–DC converter with reduced voltage stresses. IEEE Trans. Power Electron. 2023, 38, 15956–15967. [Google Scholar] [CrossRef]

- Lin, J.-Y.; Chen, C.-T.; Lin, Y.-F. A novel hybrid cascaded and stacked coupled inductor boost converter with active clamping zero-voltage switching. IEEE Access 2025, 13, 608–617. [Google Scholar] [CrossRef]

- Wu, T.-F.; Lai, Y.-S.; Hung, J.-C.; Chen, Y.-M. Boost converter with coupled inductors and buck–boost type of active clamp. IEEE Trans. Ind. Electron. 2023, 55, 154–162. [Google Scholar] [CrossRef]

- Li, H.; Liu, M.; Yang, Y.; Song, Z.; Wang, Y. A multi-MHz active clamp topology for high cost-performance wireless power transfer. IEEE Trans. Power Electron. 2022, 37, 12828–12840. [Google Scholar] [CrossRef]

- Yau, Y.-T.; Hung, T.-L. A flyback converter with novel active dissipative snubber. IEEE Access 2022, 10, 108145–108158. [Google Scholar] [CrossRef]

| Input Voltage (Vin) | 380 V |

| Output Voltage (Vo) | 48 V |

| Rated Output Power (Po,rated) | 500 W |

| Minimum Output Power (Po,min) | 100 W |

| Switching Frequency (fs) | 100 kHz |

| Maximum Duty Cycle of Main Switch (Dmax) | 0.4 |

| [14] | [15] | [16] | [17] | [18] | [19] | Proposed | |

|---|---|---|---|---|---|---|---|

| Rated-load Power (W) | 100 | 65 | 250 | 400 | 200 | 120 | 500 |

| Input Voltage (V) | 400 | 150 | 30 | 40 | 30 | 250 | 380 |

| Output Voltage (V) | 48 | 19.5 | 360 | 400 | 200 | 48 | 48 |

| Voltage Gain | --- | ||||||

| Switching Frequency (kHz) | 100 | 600 | 70 | 100 | 66 | 1000 | 100 |

| No. of Switches | MOSFET (2) | GaN (2) + MOSFET (1) | MOSFET (2) | MOSFET (2) | MOSFET (2) | MOSFET (2) | MOSFET (2) |

| No. of Transformers (Coupled Inductors) | 1(0) | 1(0) | 1(2) | 0(2) | 0(2) | 1(0) | 2(0) |

| No. of Capacitors | 1 | 1 | 5 | 3 | 1 | 3 | 2 |

| No. of Diodes | 1 | 0 | 5 | 2 | 1 | 4 | 2 |

| Maximum Efficiency (%) | --- | 93.74 | 96.1 | 94.6 | 92.0 | 92.4 | 96.4 |

| Control Strategy | PSRS | PHCM | PWM | PWM | PWM | PWM | PWM |

| Isolation | v | v | x | x | x | v | v |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tseng, P.-C.; Hwu, K.-I.; Chen, Y.-L.; Shieh, J.-J. Active-Clamp Dual-Transformer ZVS Flyback Converter. Energies 2025, 18, 3331. https://doi.org/10.3390/en18133331

Tseng P-C, Hwu K-I, Chen Y-L, Shieh J-J. Active-Clamp Dual-Transformer ZVS Flyback Converter. Energies. 2025; 18(13):3331. https://doi.org/10.3390/en18133331

Chicago/Turabian StyleTseng, Pei-Ching, Kuo-Ing Hwu, Yu-Lin Chen, and Jenn-Jong Shieh. 2025. "Active-Clamp Dual-Transformer ZVS Flyback Converter" Energies 18, no. 13: 3331. https://doi.org/10.3390/en18133331

APA StyleTseng, P.-C., Hwu, K.-I., Chen, Y.-L., & Shieh, J.-J. (2025). Active-Clamp Dual-Transformer ZVS Flyback Converter. Energies, 18(13), 3331. https://doi.org/10.3390/en18133331