Time-Domain Fault Detection and Location Scheme for Flexible DC Distribution Networks

Abstract

1. Introduction

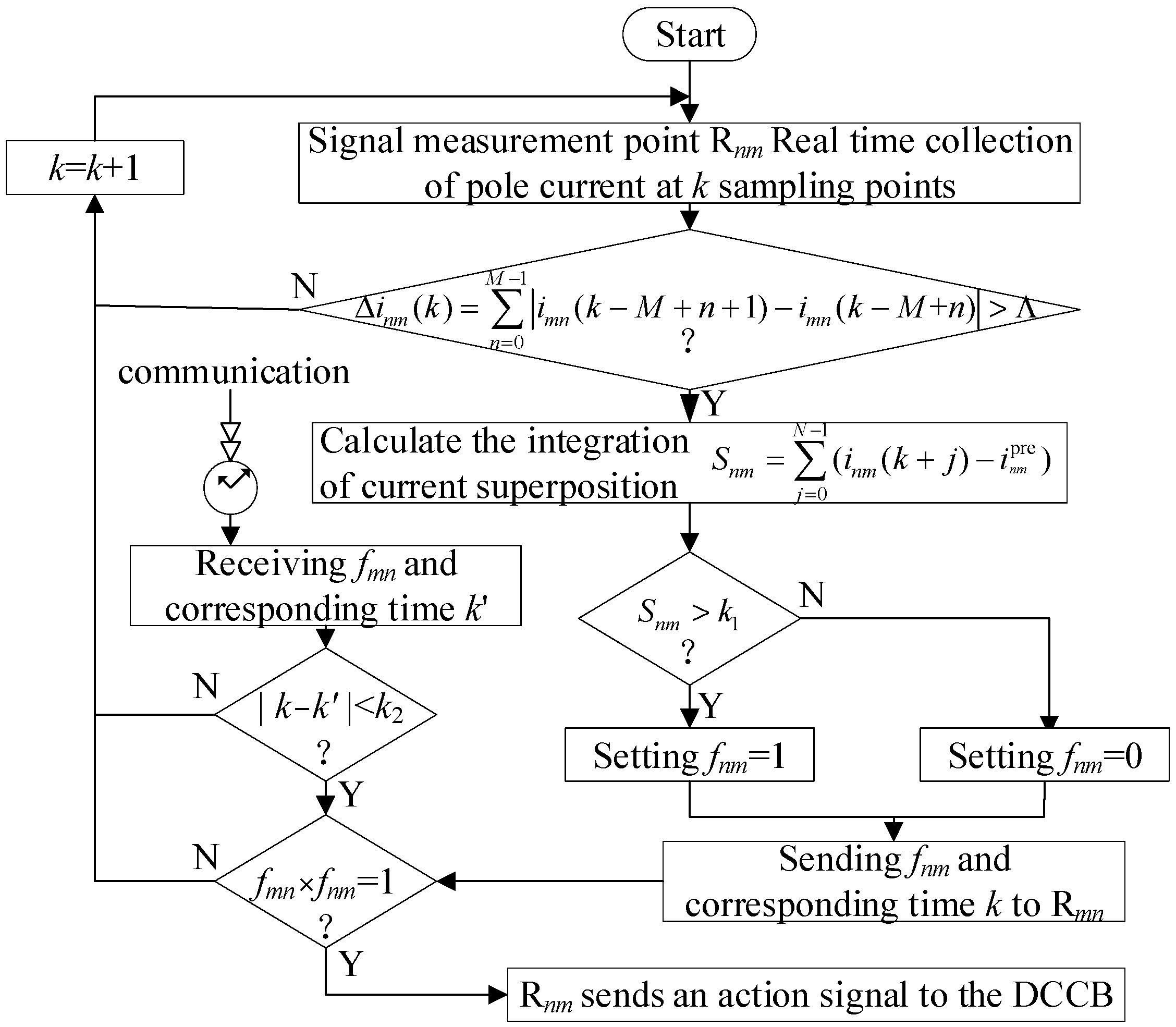

2. Fault Detection for Flexible DC Networks

3. Principle of Fault Location Scheme

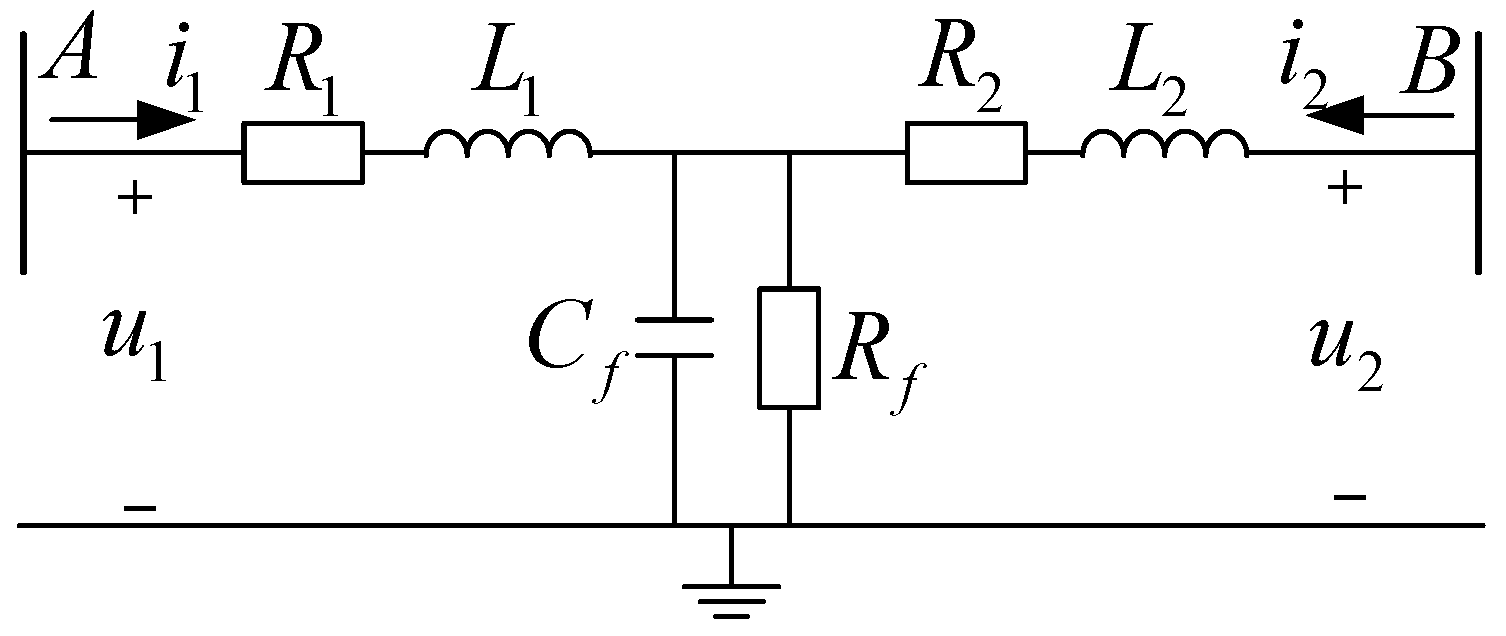

3.1. DC Lines without CLRs

3.2. DC Lines with CLRs

3.3. Design of Online Fault Location Scheme

- (a)

- After satisfying criterion Equation (1), record the fault current data at a higher sampling rate (such as 10 kHz).

- (b)

- After the faulty line is cutoff, the local IED sends fault-recording data to the opposite end of the faulty line IED’ and receives the recording data sent by IED’. The length of the recorded data starts from fault detection to DCCB, cutting off the faulty line.

- (c)

- Calculate the parameters of the fault circuit. If there is no CLR, calculate the fault circuit parameters through Equations (6) and (9). If CLR is installed, perform low-pass filtering first, then calculate the fault circuit parameters using Equations (9) and (11).

- (d)

- Calculate the fault distance. If the line parameters are known, the fault distance can be directly calculated. If the line parameters are unknown, the fault circuit parameters are calculated at both end IEDs, and the fault distance is calculated by Equation (10).

4. Simulation Results

4.1. Simulation System and Parameters

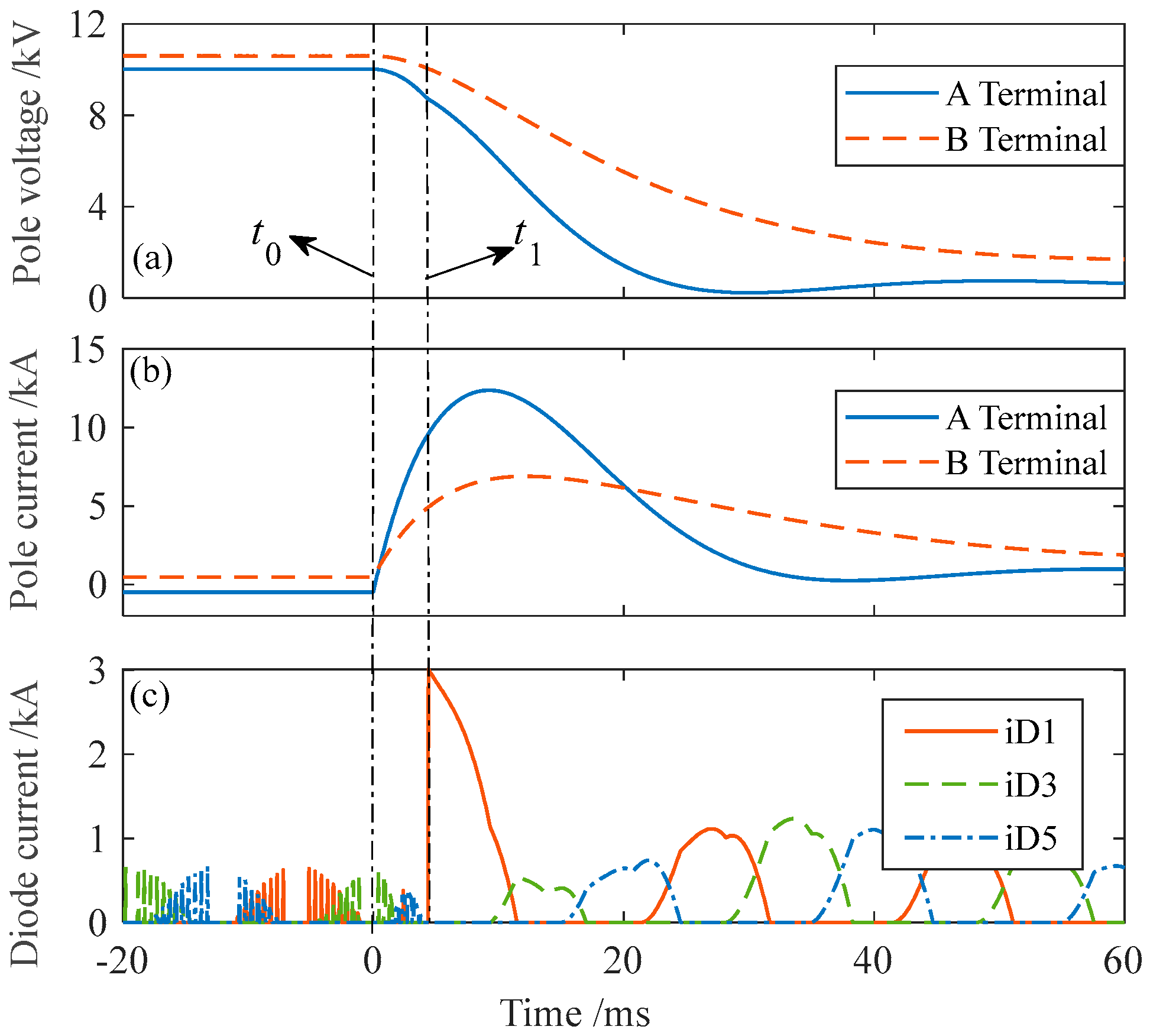

4.2. Transient Characteristics of DC Faults

- (1)

- PTG Faults

- (2)

- PTP Faults

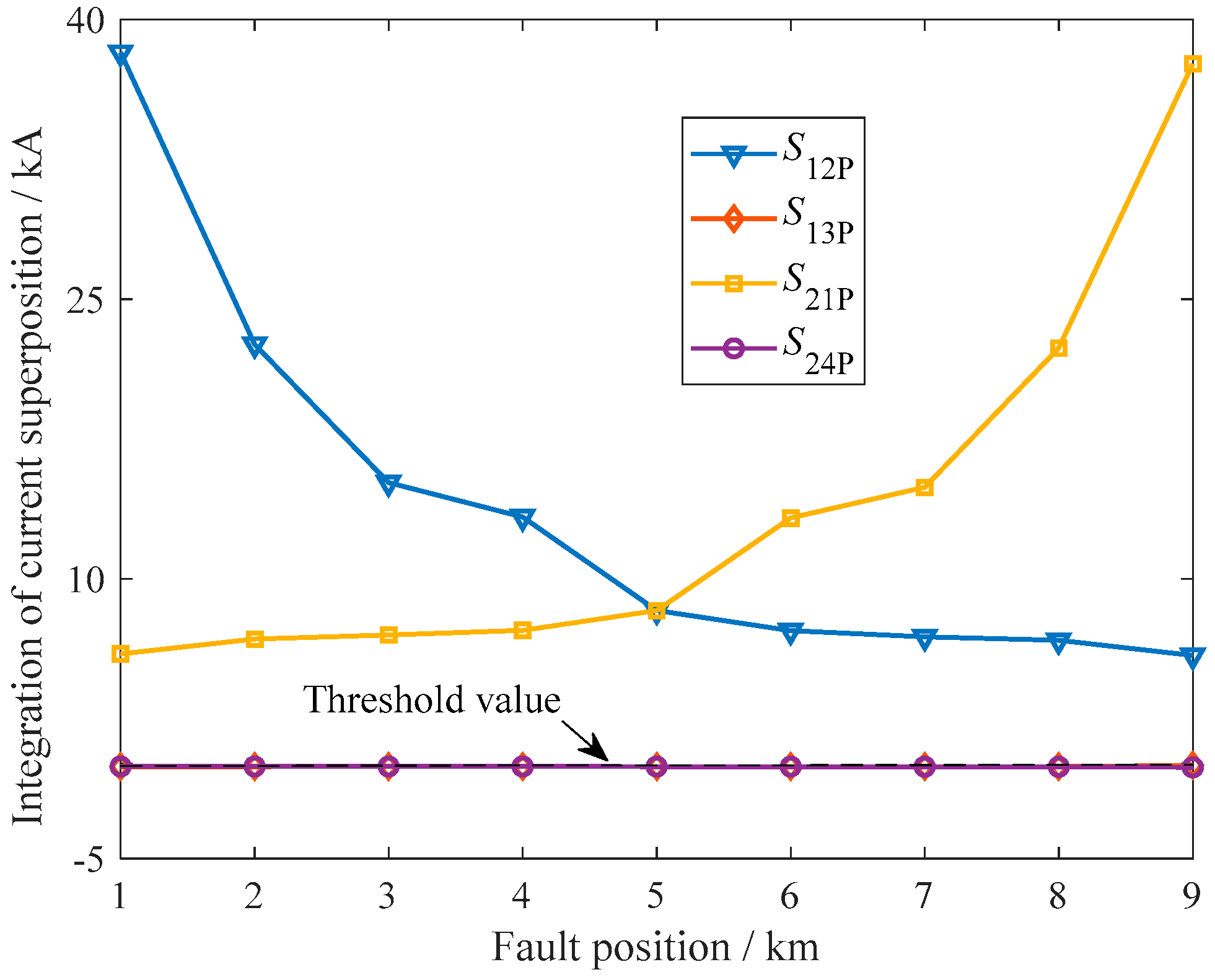

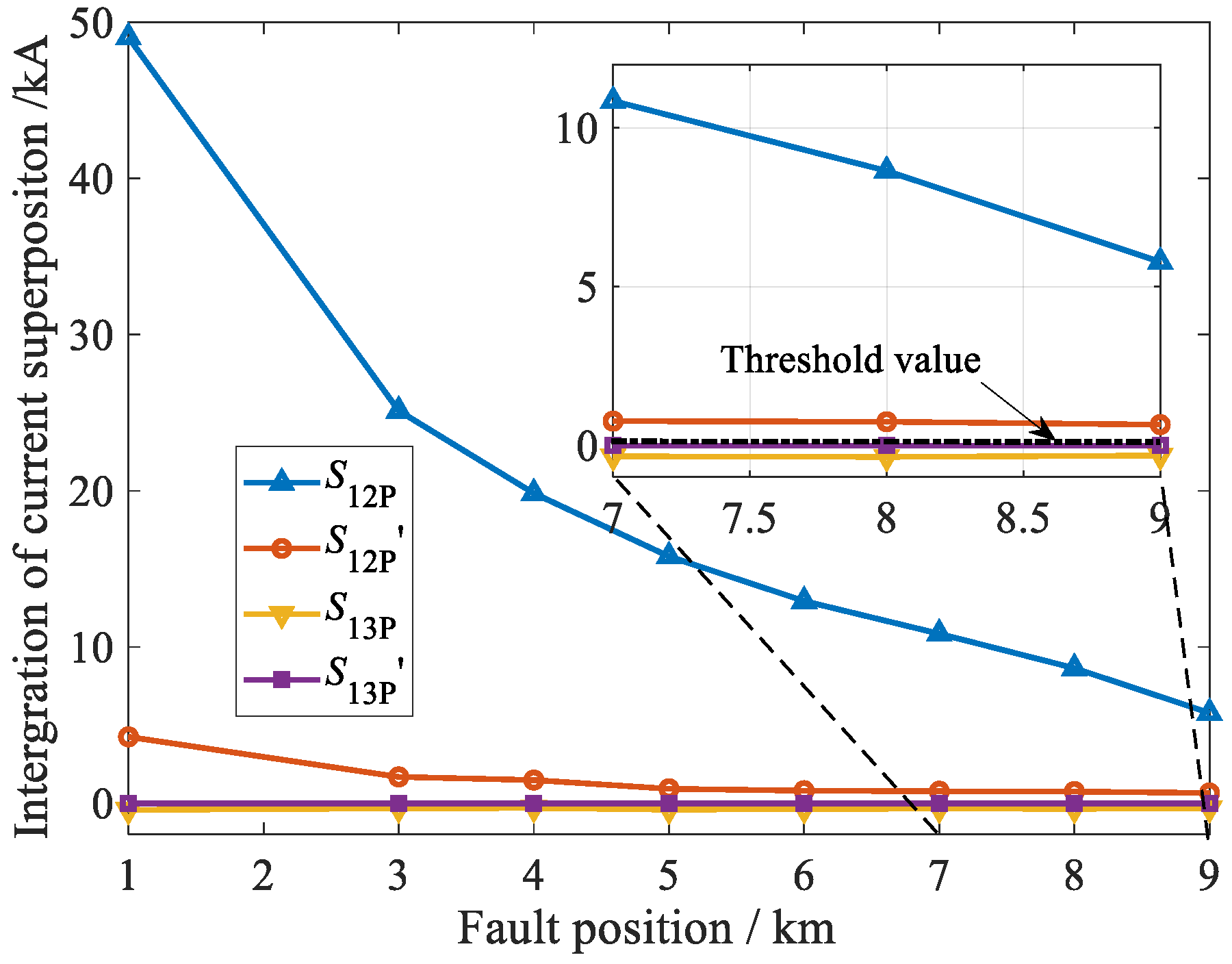

4.3. Performance Analysis of Fault Detection Scheme

- (1)

- Influence of the Fault Positions

- (2)

- Influence of the Fault Resistances

4.4. Results of the Proposed Fault Location Scheme

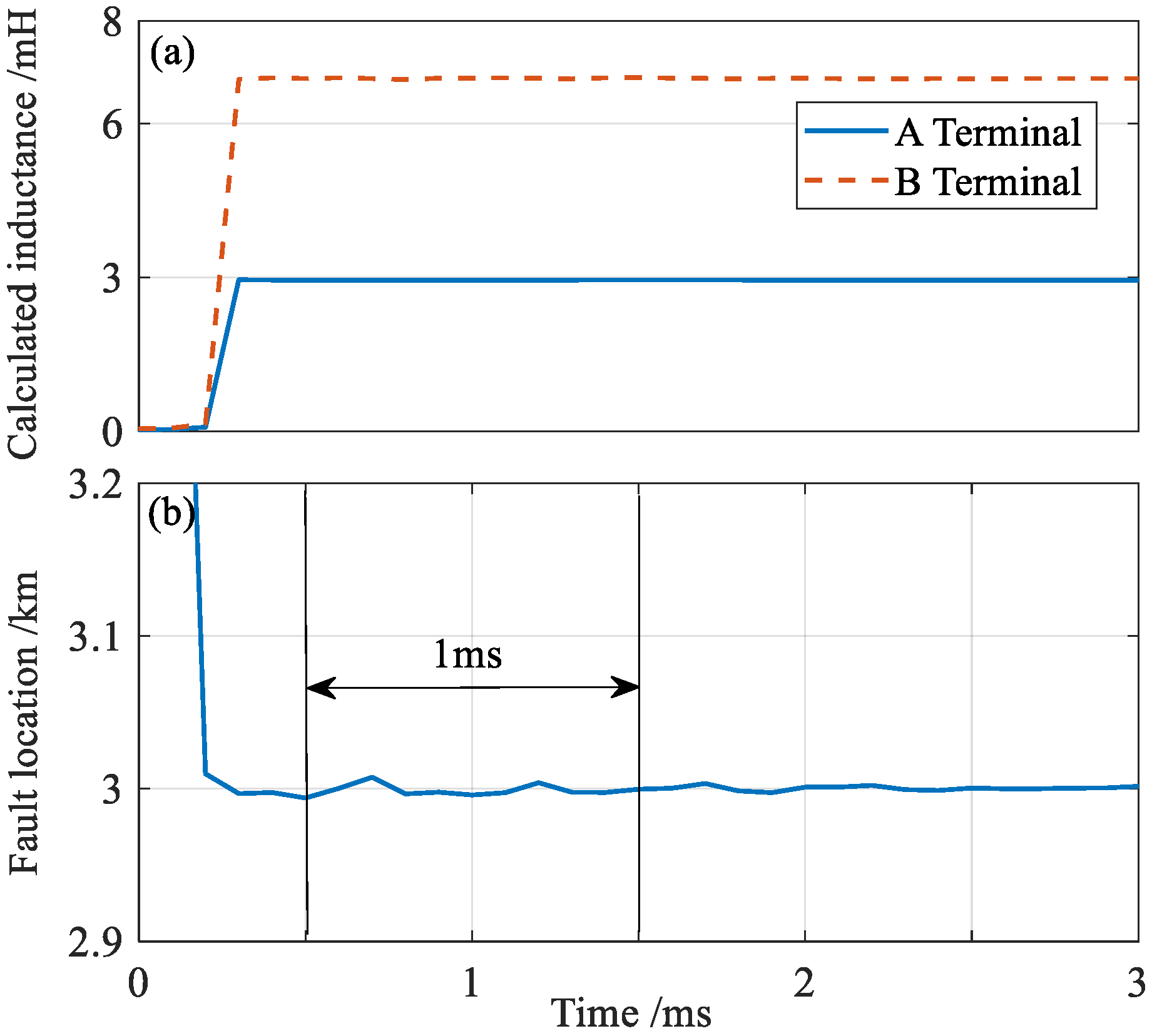

- (1)

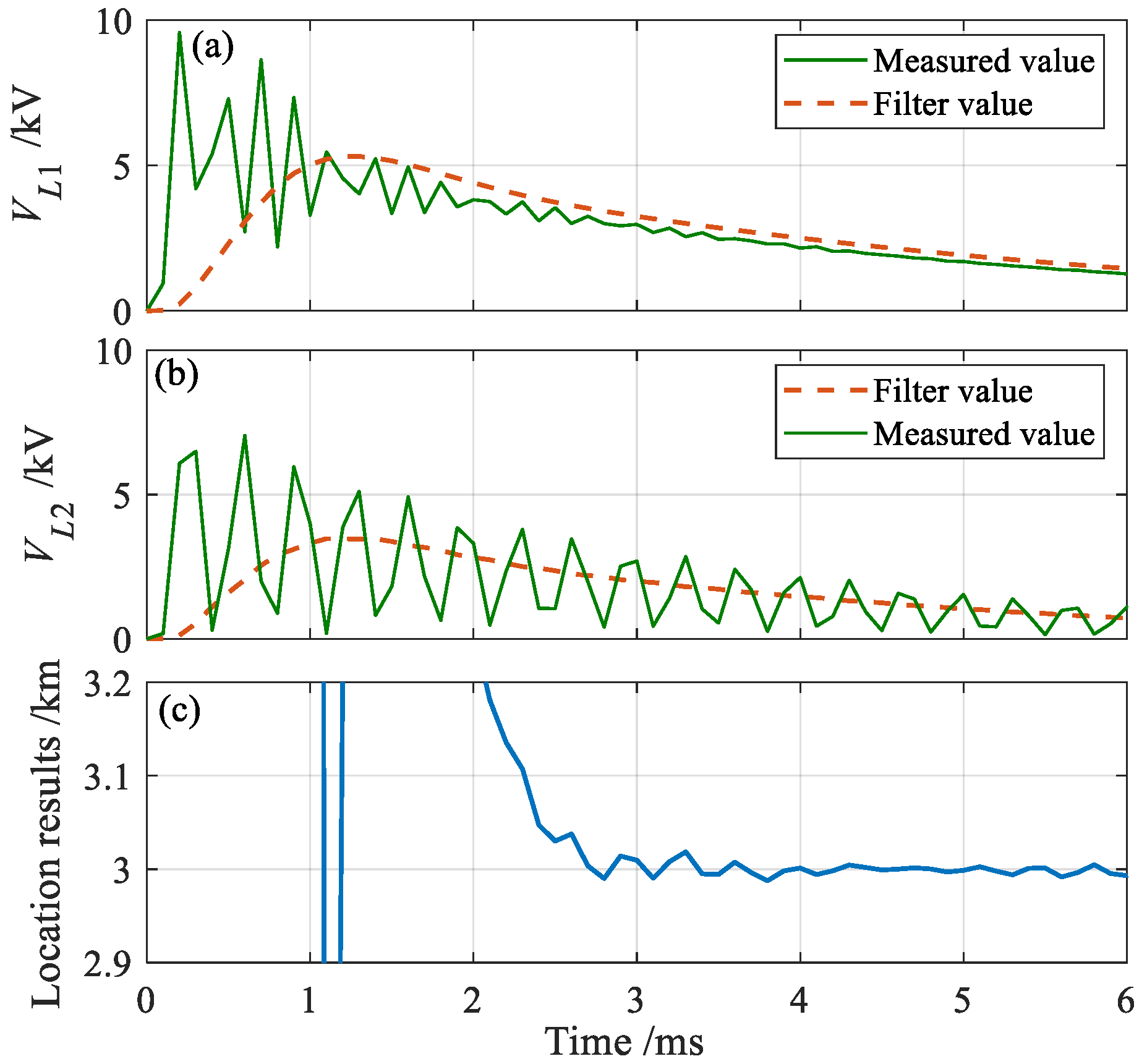

- Fault Location Process

- (2)

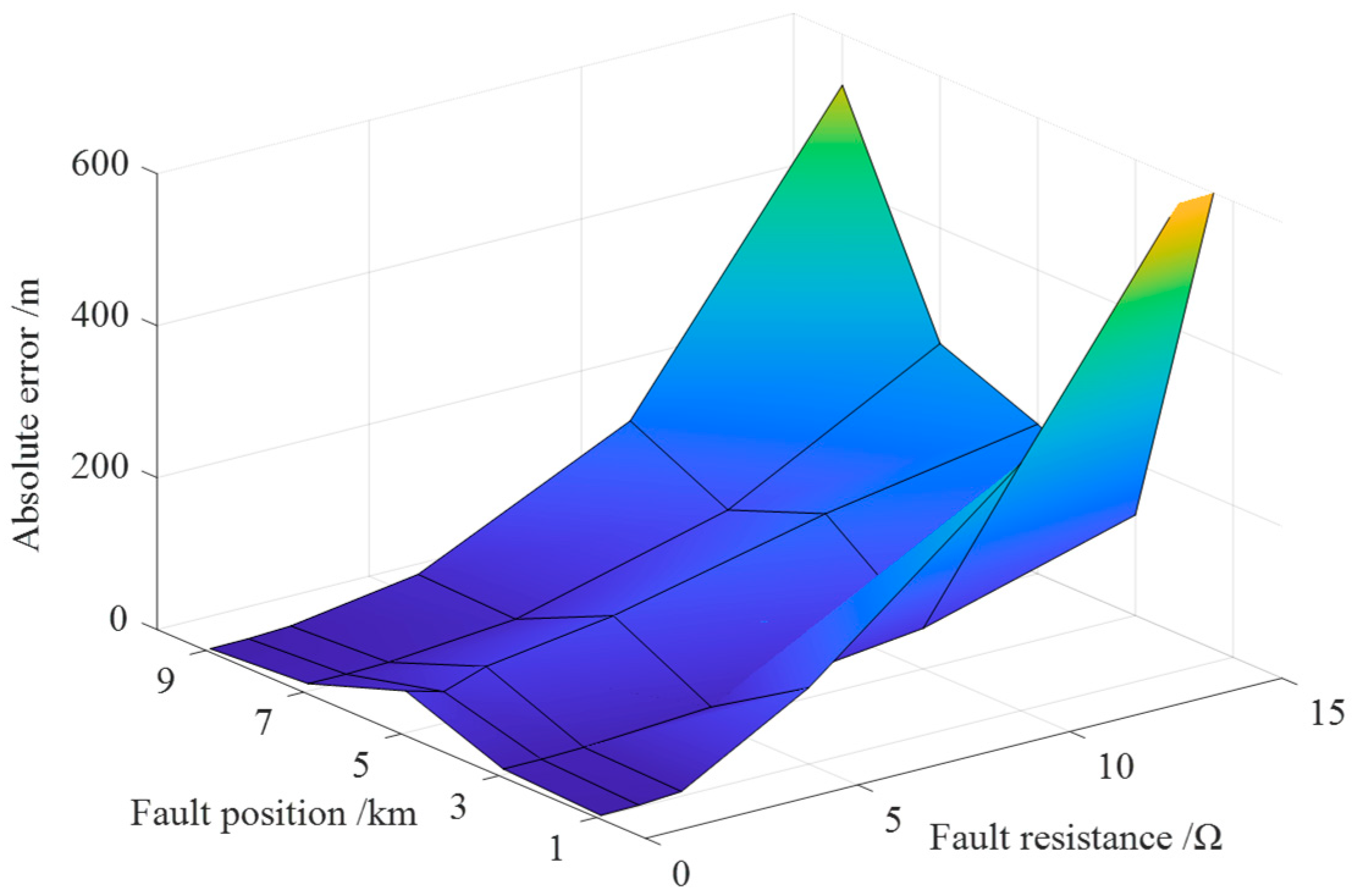

- Impact of Fault Resistances and Distances

- (3)

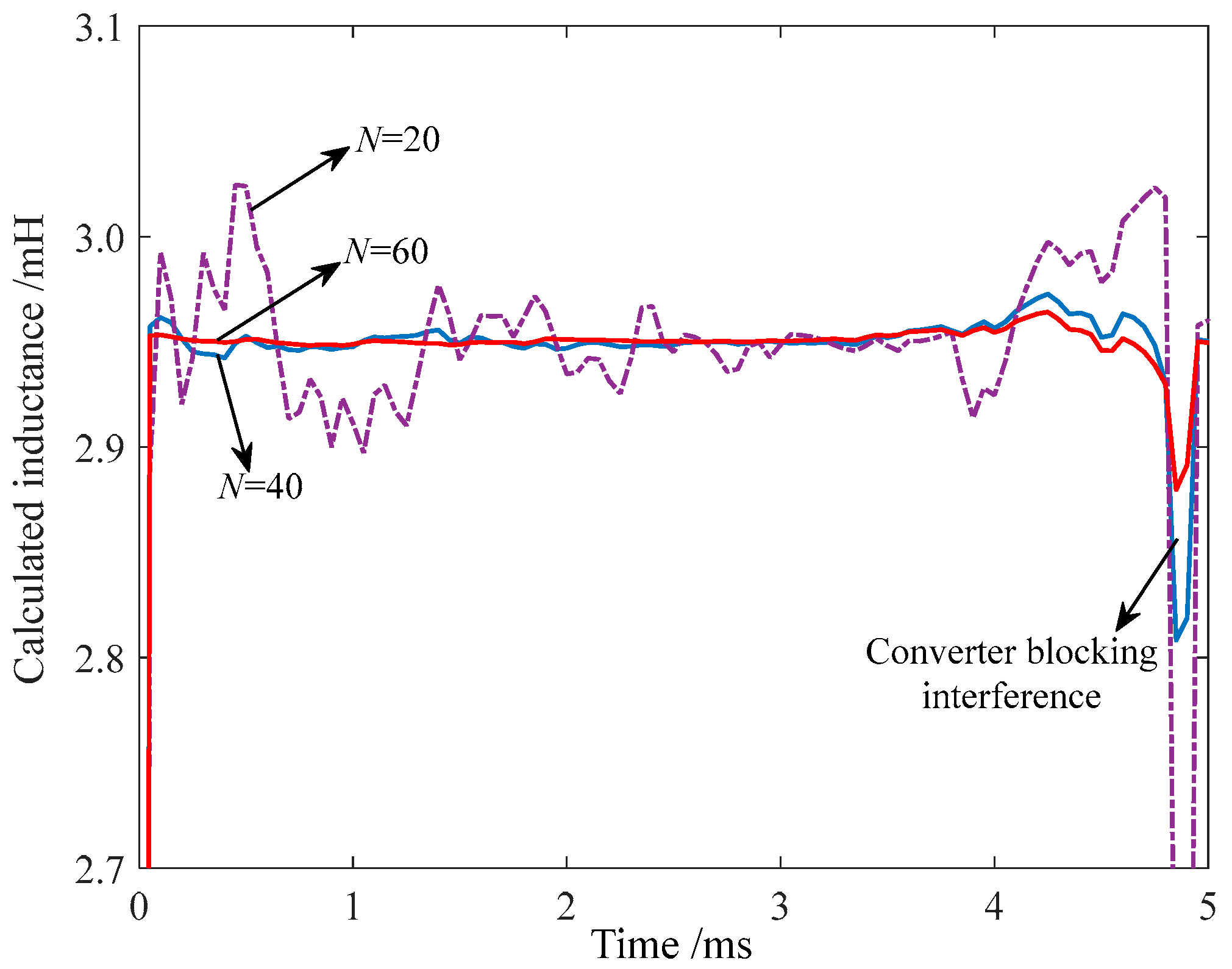

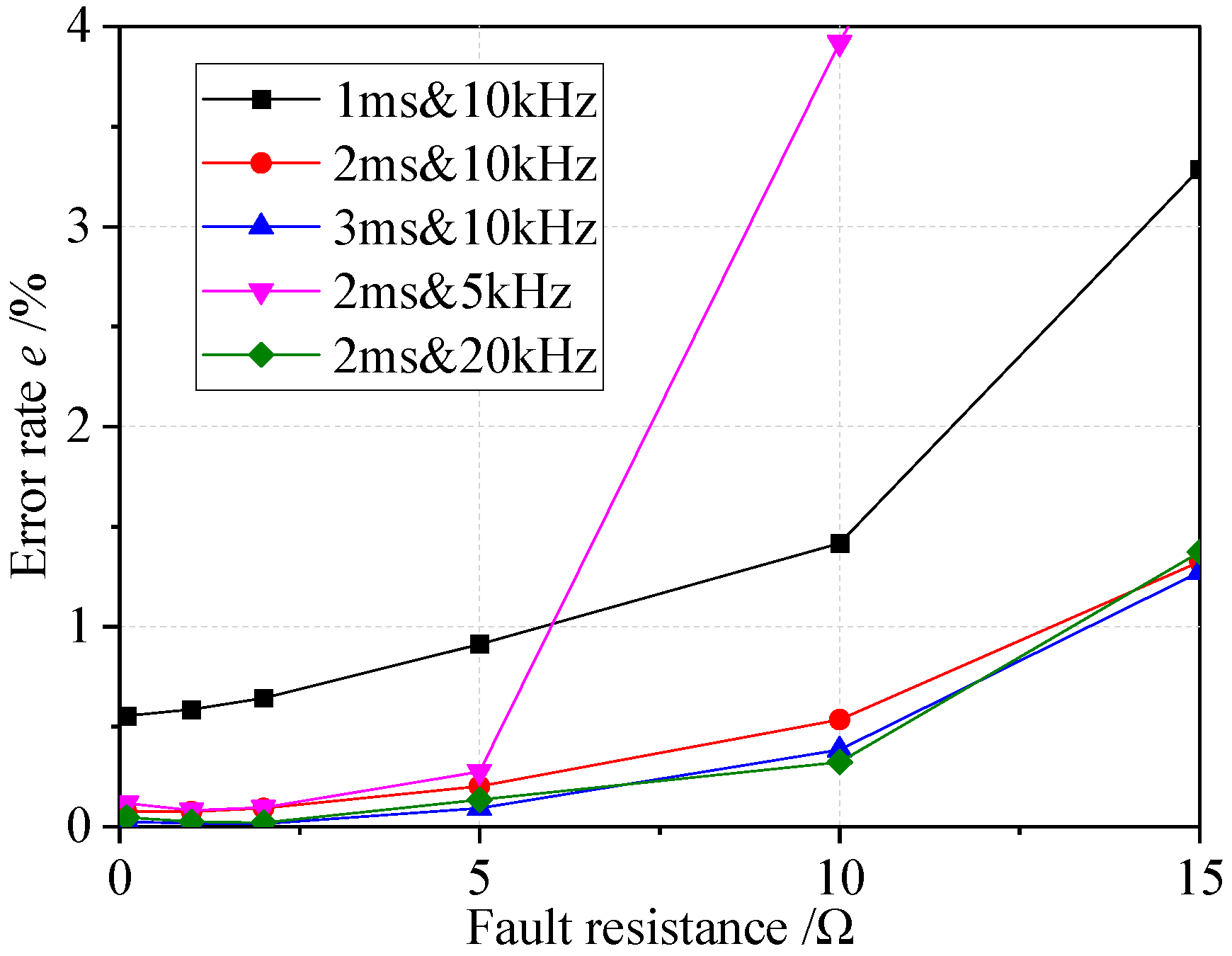

- Influence of the Data Length and Sampling Rate

- (4)

- Influence of the Asynchronous Sampling

- (5)

- Influence of DC Line with CLRs

4.5. Comparison Results

- (1)

- Comparison Results of the Fault Detection Scheme

- (2)

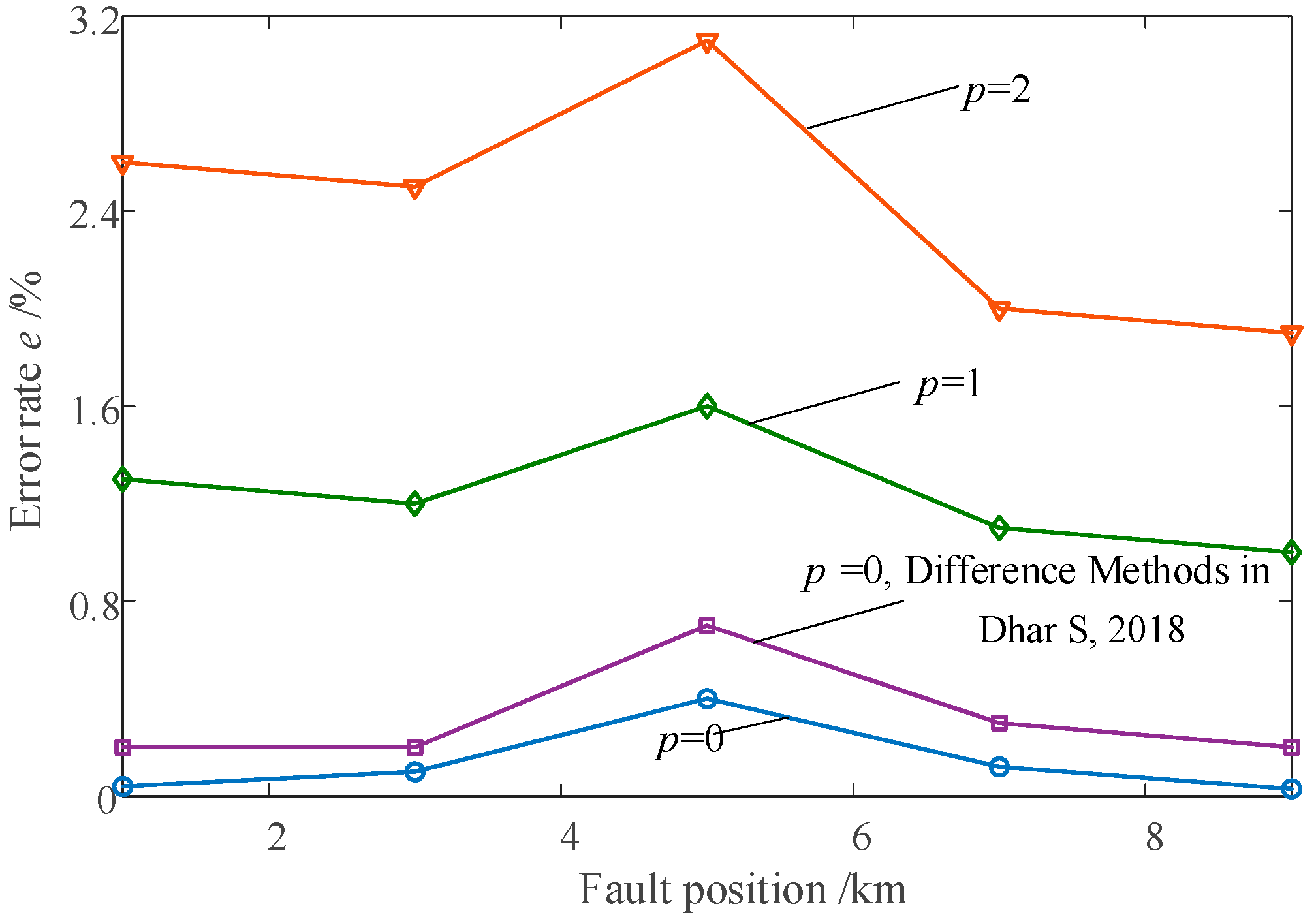

- Comparison Results of the Fault Location Scheme

5. Conclusions

- (a)

- The proposed fault detection scheme applies to complex DC distribution networks and can reliably detect grounding faults with high fault resistances.

- (b)

- The proposed fault location scheme considers the influence of distributed capacitance and improves the calculation method of the current differential to reduce the fault location error.

- (c)

- The proposed scheme is a time-domain scheme, does not require a high sampling rate and data length, is suitable for complex networks with multiple sources, and can achieve online fault location, reducing the cost and complexity of the location scheme.

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Nomenclature

| LS | least square |

| CLR | current-limiting reactor |

| DG | distributed generation |

| DCCB | DC circuit breaker |

| PPU | probe power unit |

| IED | intelligent electronic device |

| SMP | signal measurement point |

| PTG | pole-to-ground |

| PTP | pole-to-pole |

| KVL | Kirchhoff’s voltage law |

| VSC | voltage source converter |

| Imn | DC flowing from the DC bus m to the DC bus n |

| ΔImn(k) | DC change, where k is the corresponding sampling point |

| Λ | set threshold value for the start-up criterion |

| M | data length to calculate the DC change start-up criterion |

| ipre | steady-state current |

| P | number of sampling points to obtain the steady-state current |

| Snm | integral of the current superposition |

| N | data length of calculating Snm |

| k1 | reliability coefficient of the direction criterion |

| Rmn | relay of a signal measurement point at line nm close to bus n |

| fnm | label symbol of fault direction |

| k2 | set value of the mis-operation criterion |

| f | fault point |

| R1 and L1 | equivalent line resistance and reactance from A to f |

| Cf and Rf | equivalent line capacitance and fault resistance at f |

| xc | equivalent impedance of Cf during the fault transient process |

| u1, u2, and uf | equivalent voltage at A, B, and f |

| i1, i2, and i3 | currents at terminals A, B, and f |

| difference between the previous and the subsequent sampling point at k-th sampling | |

| Δt | sampling interval |

| U and V | matrixes of currents and voltages for calculating fault distance |

| LAB | total length of line AB |

| x1 | distance from end A to f |

| Ldc | size of the CLR |

| uL | voltage of the CLR |

References

- Azizi, M.; Husev, O.; Veligorskyi, O.; Rahimpour, S.; Roncero-Clemente, C. Grounding and isolation requirements in dc microgrids: Overview and critical analysis. Energies 2023, 16, 7747. [Google Scholar] [CrossRef]

- Emhemed, A.A.S.; Fong, K.; Fletcher, S.; Burt, G.M. Validation of fast and selective protection scheme for an LVDC distribution network. IEEE Trans. Power Deliv. 2017, 32, 1432–1440. [Google Scholar] [CrossRef]

- Hategekimana, P.; Ferre, A.J.; Bernuz, J.M.R.; Ntagwirumugara, E. Fault detecting and isolating schemes in a low-voltage dc microgrid network from a remote village. Energies 2022, 15, 4460. [Google Scholar] [CrossRef]

- Xu, Y.; Hu, Z.; Ma, T. Monopolar grounding fault location method of dc distribution network based on improved relieff and weighted random forest. Energies 2022, 15, 7261. [Google Scholar] [CrossRef]

- Yang, R.; Fang, K.; Chen, J.; Chen, Y.; Liu, M.; Meng, Q. A novel protection strategy for single pole-to-ground fault in multi-terminal dc distribution network. Energies 2023, 16, 2921. [Google Scholar] [CrossRef]

- Ma, T.; Hu, Z.; Xu, Y.; Dong, H. Fault location based on comprehensive grey correlation degree analysis for flexible dc distribution network. Energies 2022, 15, 7820. [Google Scholar] [CrossRef]

- Larik, N.A.; Li, M.S.; Wu, Q.H. Enhanced fault detection and localization strategy for high-speed protection in medium-voltage DC distribution networks using extended kalman filtering algorithm. IEEE Access 2024, 12, 30329–30344. [Google Scholar] [CrossRef]

- Wei, X.; Zou, G.; Zhang, S.; Xu, C. Frequency domain impedance based protection for flexible DC distribution grid. IEEE Access 2022, 10, 114203–114213. [Google Scholar] [CrossRef]

- Monadi, M.; Zamani, M.A.; Koch-Ciobotaru, C.; Candela, J.I.; Rodriguez, P. A communication-assisted protection scheme for direct-current distribution networks. Energy 2016, 109, 578–591. [Google Scholar] [CrossRef]

- Fletcher, S.D.A.; Norman, P.J.; Fong, K.; Galloway, S.J.; Burt, G.M. High-speed differential protection for smart DC distribution systems. IEEE Trans. Smart Grid 2014, 5, 2610–2617. [Google Scholar] [CrossRef]

- Monadi, M.; Gavriluta, C.; Luna, A.; Candela, J.I.; Rodriguez, P. Centralized protection strategy for medium voltage DC microgrids. IEEE Trans. Power Deliv. 2017, 32, 430–440. [Google Scholar] [CrossRef]

- Emhemed, A.A.S.; Burt, G.M. An advanced protection scheme for enabling an LVDC last mile distribution network. IEEE Trans. Smart Grid 2014, 5, 2602–2609. [Google Scholar] [CrossRef]

- Mohanty, R.; Pradhan, A.K. A superimposed current based unit protection scheme for DC microgrid. IEEE Trans. Smart Grid 2018, 9, 3917–3919. [Google Scholar] [CrossRef]

- Park, J.-D.; Candelaria, J.; Ma, L.; Dunn, K. DC ring-bus microgrid fault protection and identification of fault location. IEEE Trans. Power Deliv. 2013, 28, 2574–2584. [Google Scholar] [CrossRef]

- Mohanty, R.; Balaji, U.S.M.; Pradhan, A.K. An accurate noniterative fault-location technique for low-voltage DC microgrid. IEEE Trans. Power Deliv. 2016, 31, 475–481. [Google Scholar] [CrossRef]

- Lin, F.; Wu, J.; Hao, L. One-terminal on-line fault location method for DC distribution cable based on apparent pseudo-impedance identification. Power Syst. Technol. 2016, 40, 2555–2561. [Google Scholar]

- Mumtaz, F.; Khan, T.S.; Alqahtani, M.; Sher, H.A.; Aljumah, A.S.; Almutairi, S.Z. Ultra high-speed fault diagnosis scheme for DC distribution systems based on discrete median filter and mathematical morphology. IEEE Access 2024, 12, 45796–45810. [Google Scholar] [CrossRef]

- He, J.; Zhang, M.; Luo, G.; Yu, B.; Hong, Z. A fault location method for flexible DC distribution network based on fault transient process. Power Syst. Technol. 2017, 41, 985–992. [Google Scholar]

- Wei, Y.; Sun, P.; Song, Z.; Wang, P.; Zeng, Z.; Wang, X. Fault location of VSC based DC distribution network based on traveling wave differential current with hausdorff distance and cubic spline interpolation. IEEE Access 2021, 9, 31246–31255. [Google Scholar] [CrossRef]

- Yang, J.; Fletcher, J.E.; O’Reilly, J. Short-circuit and ground fault analyses and location in VSC-based DC network cables. IEEE Trans. Ind. Electron. 2012, 59, 3827–3837. [Google Scholar] [CrossRef]

- Li, M.; Jia, K.; Bi, T.; Yang, G.; Liu, Y.; Yang, Q. Fault distance estimation-based protection for DC distribution networks. Power Syst. Technol. 2016, 40, 719–724. [Google Scholar]

- Mohanty, R.; Pradhan, A.K. Protection of smart DC microgrid with ring configuration using parameter estimation approach. IEEE Trans. Smart Grid 2018, 9, 6328–6337. [Google Scholar] [CrossRef]

- Feng, X.; Qi, L.; Pan, J. A novel fault location method and algorithm for DC distribution protection. IEEE Trans. Ind. Appl. 2017, 53, 1834–1840. [Google Scholar] [CrossRef]

- Dhar, S.; Patnaik, R.K.; Dash, P.K. Fault detection and location of photovoltaic based DC microgrid using differential protection strategy. IEEE Trans. Smart Grid 2018, 9, 4303–4312. [Google Scholar] [CrossRef]

| Simulation Parameters | Values | Simulation Parameters | Values |

|---|---|---|---|

| DC voltage/kV | ±10 | DC line length of AB/km | 10 |

| AC line voltage/kV | 10 | Unit resistance/(Ω/km) | 0.123 |

| AC reactor/mH | 10 | Unit reactance/(mH/km) | 0.984 |

| DC capacitor/μF | 20,000 | Unit capacitance/(μF/km) | 0.283 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, Y.; Li, J.; Qian, K.; Yu, X.; Zhang, X. Time-Domain Fault Detection and Location Scheme for Flexible DC Distribution Networks. Energies 2024, 17, 5128. https://doi.org/10.3390/en17205128

Li Y, Li J, Qian K, Yu X, Zhang X. Time-Domain Fault Detection and Location Scheme for Flexible DC Distribution Networks. Energies. 2024; 17(20):5128. https://doi.org/10.3390/en17205128

Chicago/Turabian StyleLi, Yafei, Jie Li, Kejun Qian, Xiuyong Yu, and Xinsong Zhang. 2024. "Time-Domain Fault Detection and Location Scheme for Flexible DC Distribution Networks" Energies 17, no. 20: 5128. https://doi.org/10.3390/en17205128

APA StyleLi, Y., Li, J., Qian, K., Yu, X., & Zhang, X. (2024). Time-Domain Fault Detection and Location Scheme for Flexible DC Distribution Networks. Energies, 17(20), 5128. https://doi.org/10.3390/en17205128