Efficiency and Power Loss Distribution in a High-Frequency, Seven-Level Diode-Clamped Inverter

Abstract

:1. Introduction

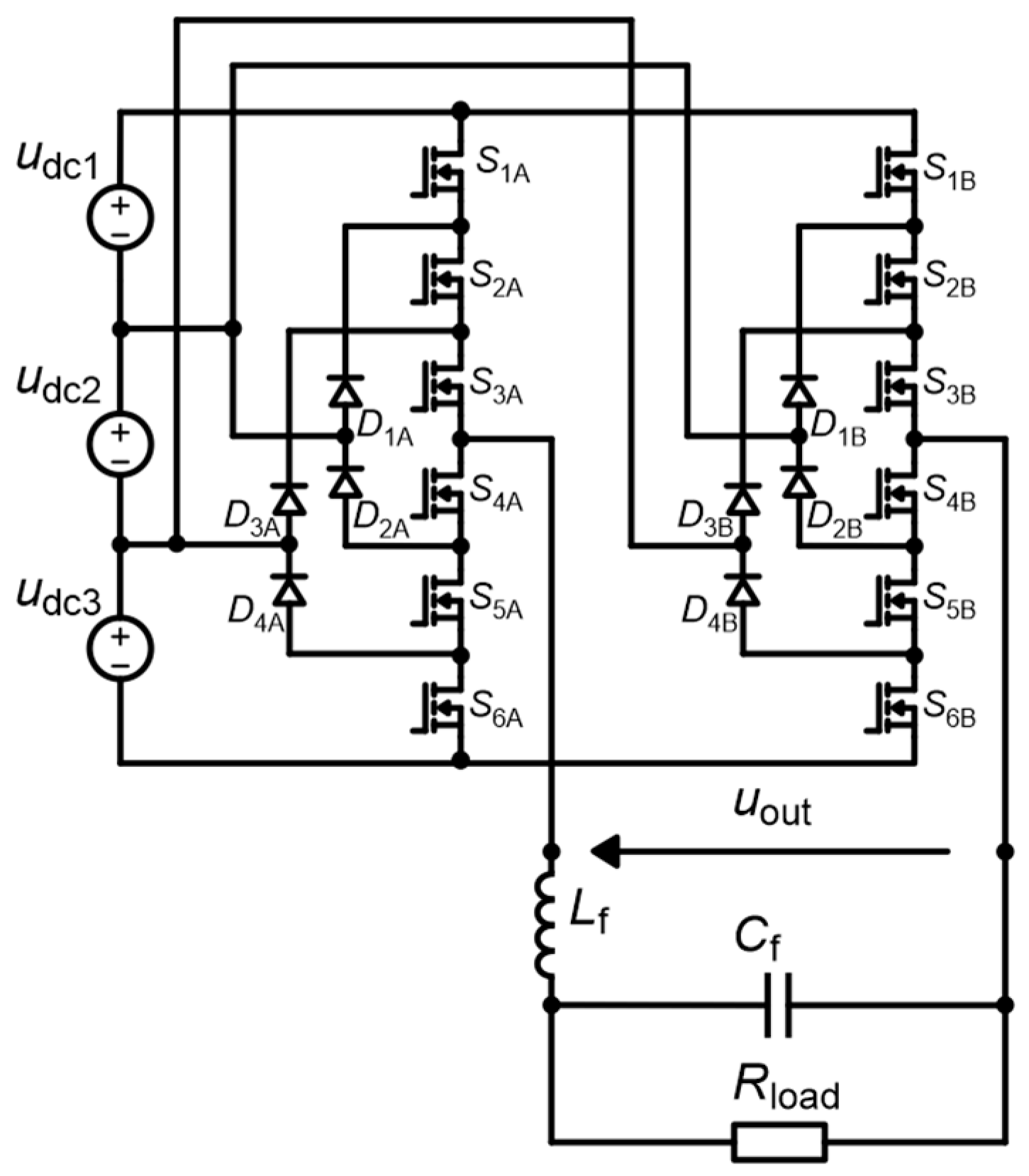

2. Four-Level Diode-Clamped Bridge Inverter Configuration and Modulation Concepts

2.1. Inverter Configuration

- Efficiency analysis in a high-frequency circuit based on MOSFETs and Schottky diodes;

- Studies of the influence of the switching frequency on the efficiency of the system in the range of 100–300 kHz;

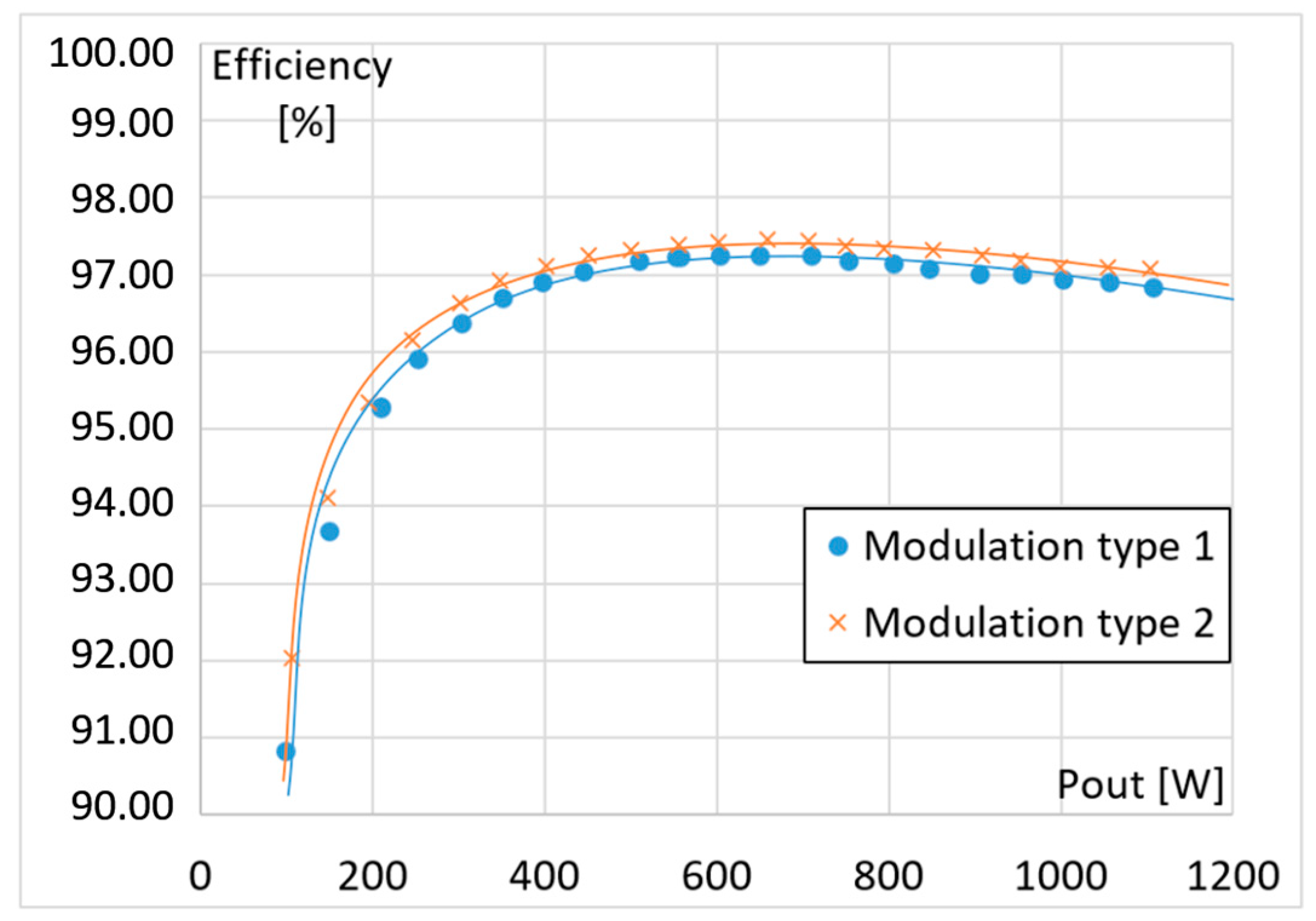

- Studies of the influence of the applied modulation on the efficiency of the system and the uniformity of the distribution of energy losses in its components;

- Simulation studies of energy losses and converter efficiency with the use of physical elements implemented in the Matlab/Simulink environment with the Simscape library;

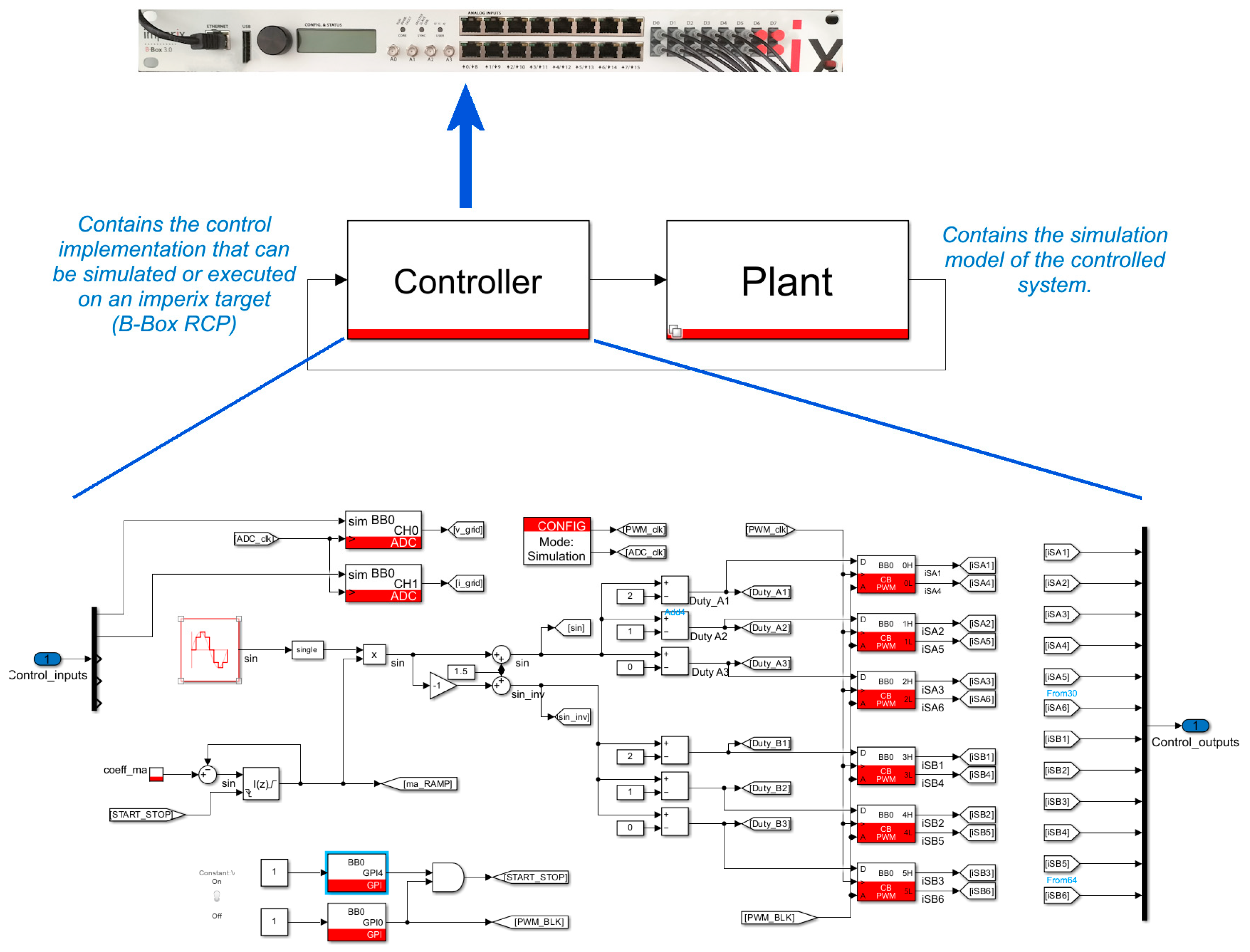

- Hardware implementation of the modulation algorithm for research with the use of the Imperix RCP system, developed in MATLAB/Simulink R2022b Software.

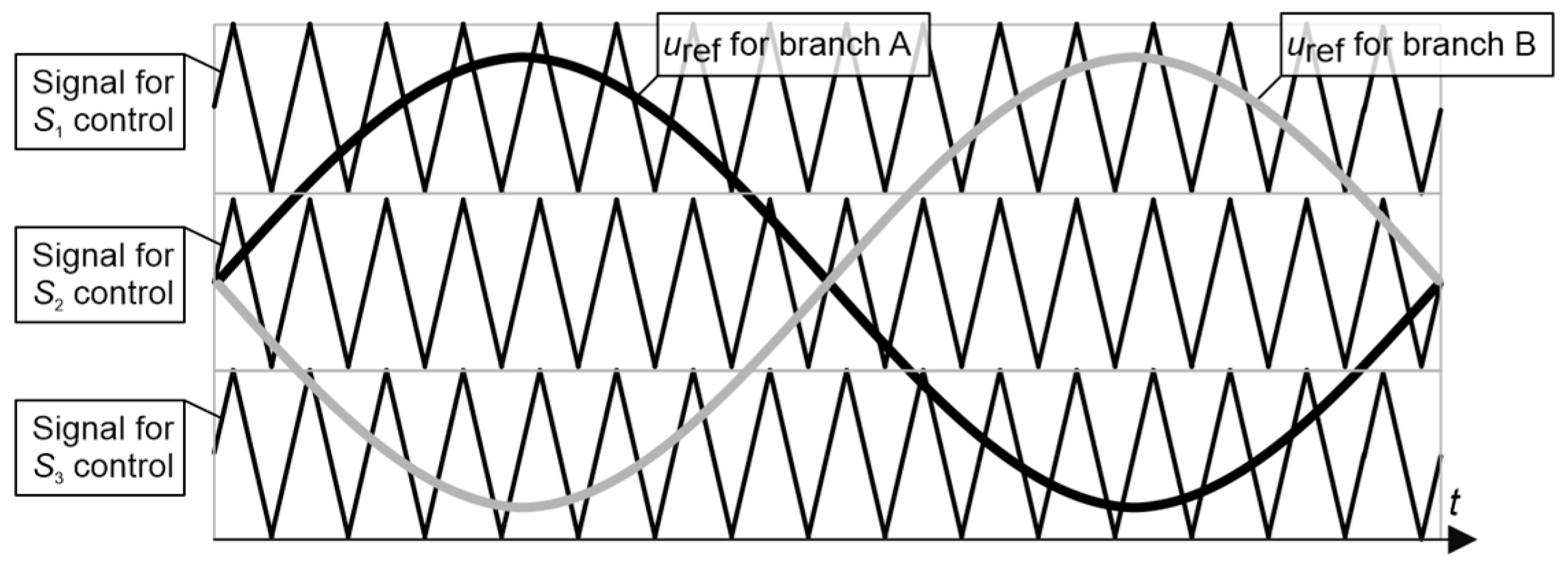

2.2. Modulation Concepts

M3 states order for levels 1–2: {1a, 2a, 1c, 2b, …},

M3 states order for levels: 1–3: {3, 1a, 3, 1b, 3, 1c, 3, 1c, 3, 1b, 3, 1a, 1a, …}

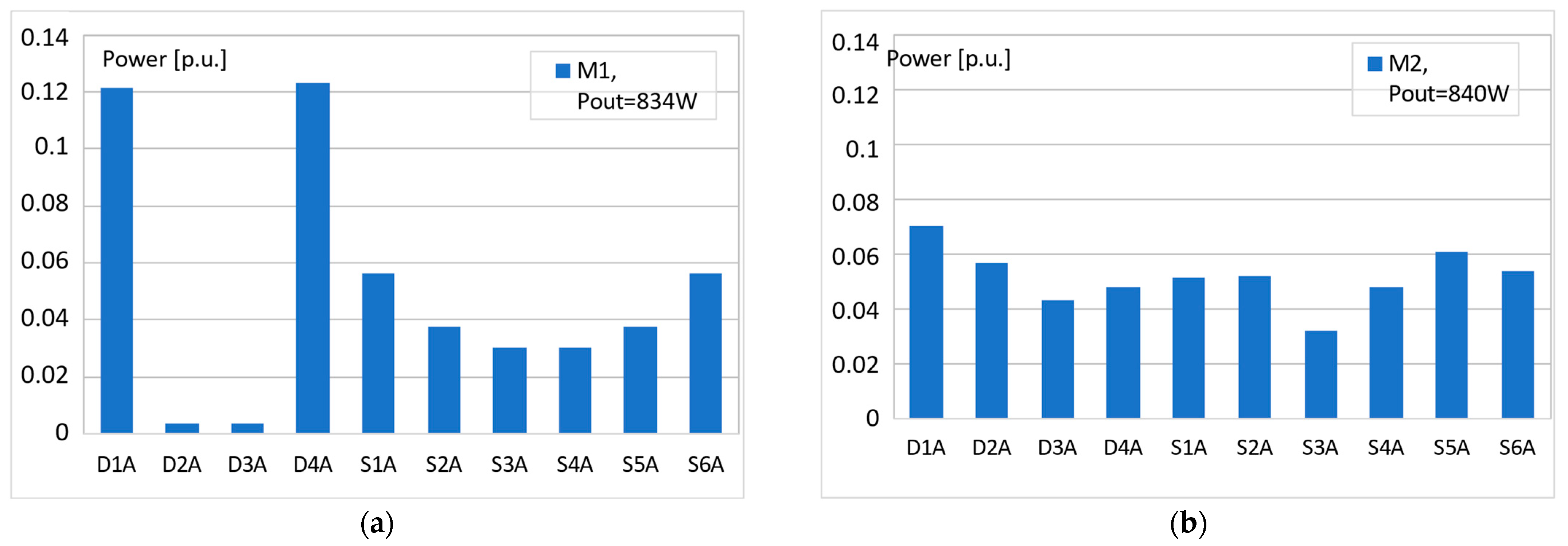

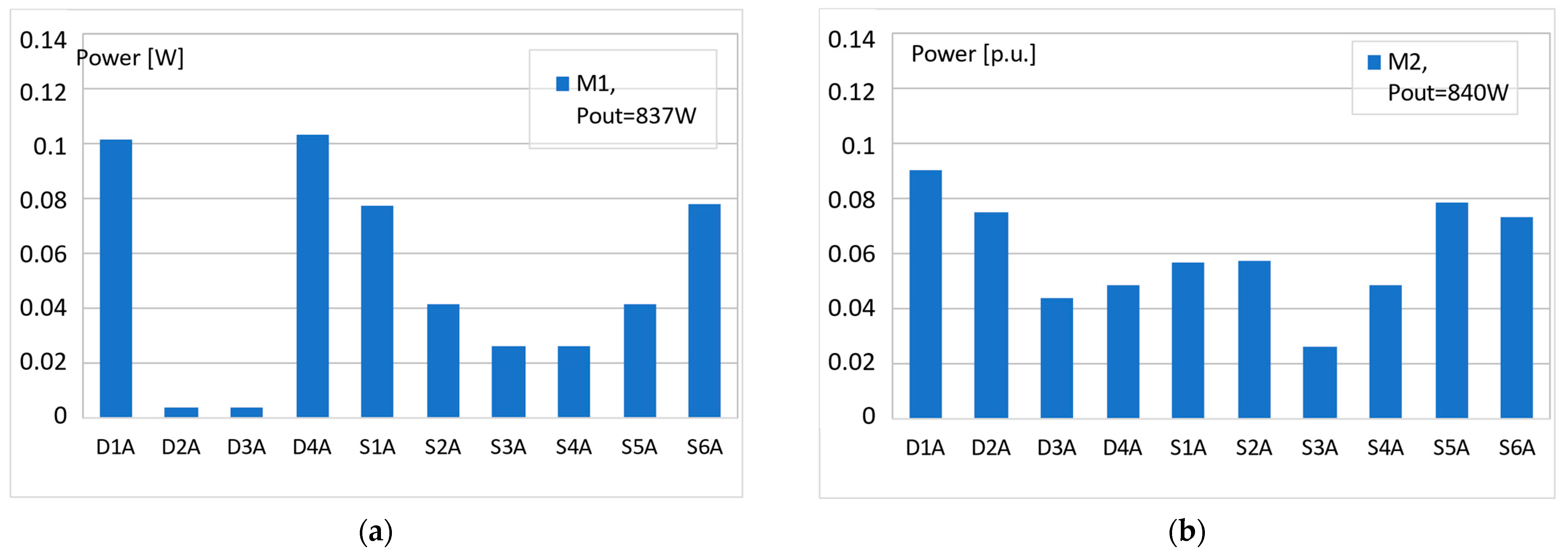

3. Simulation Research

4. Experimental Tests

4.1. Experimental Setup

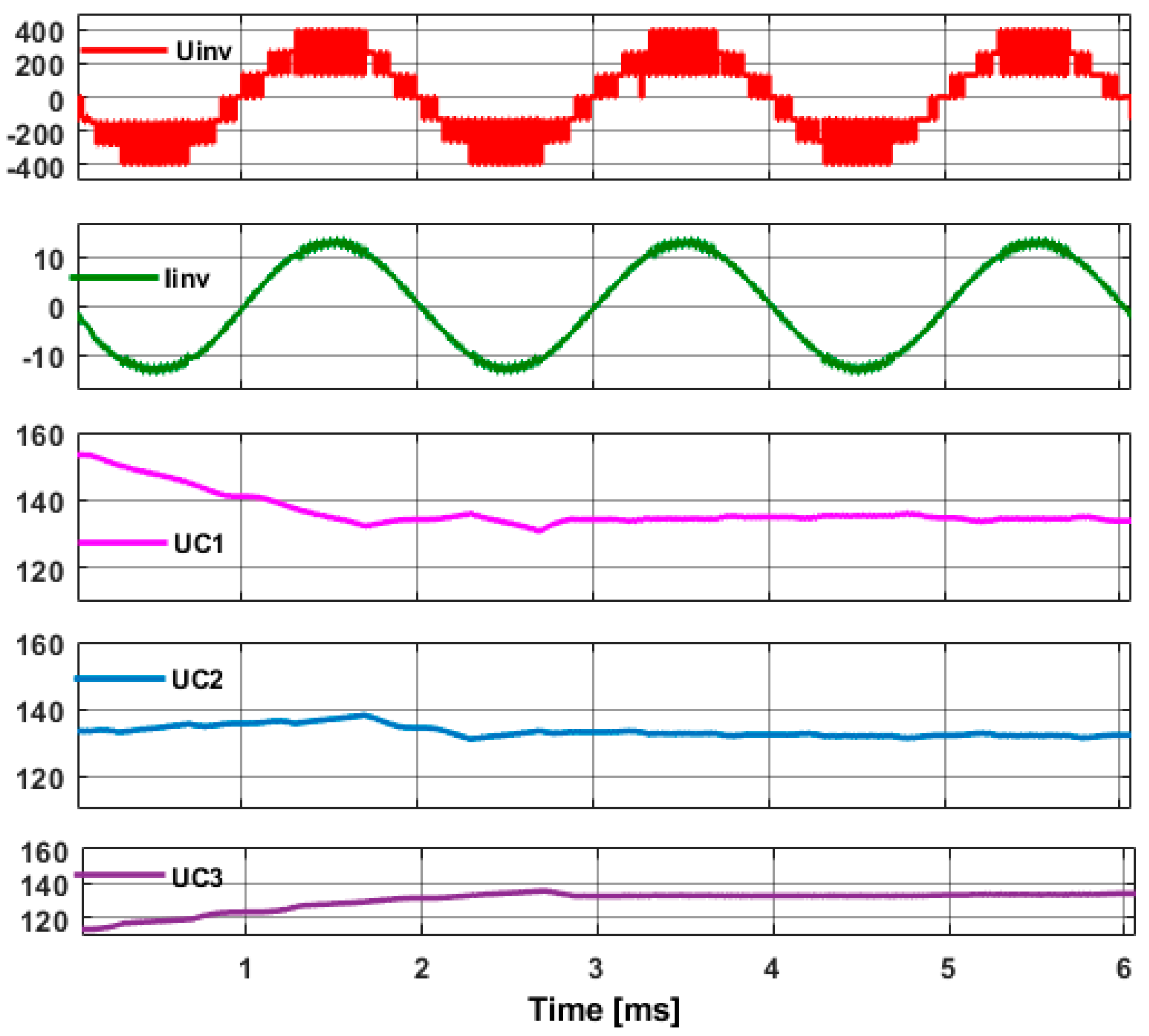

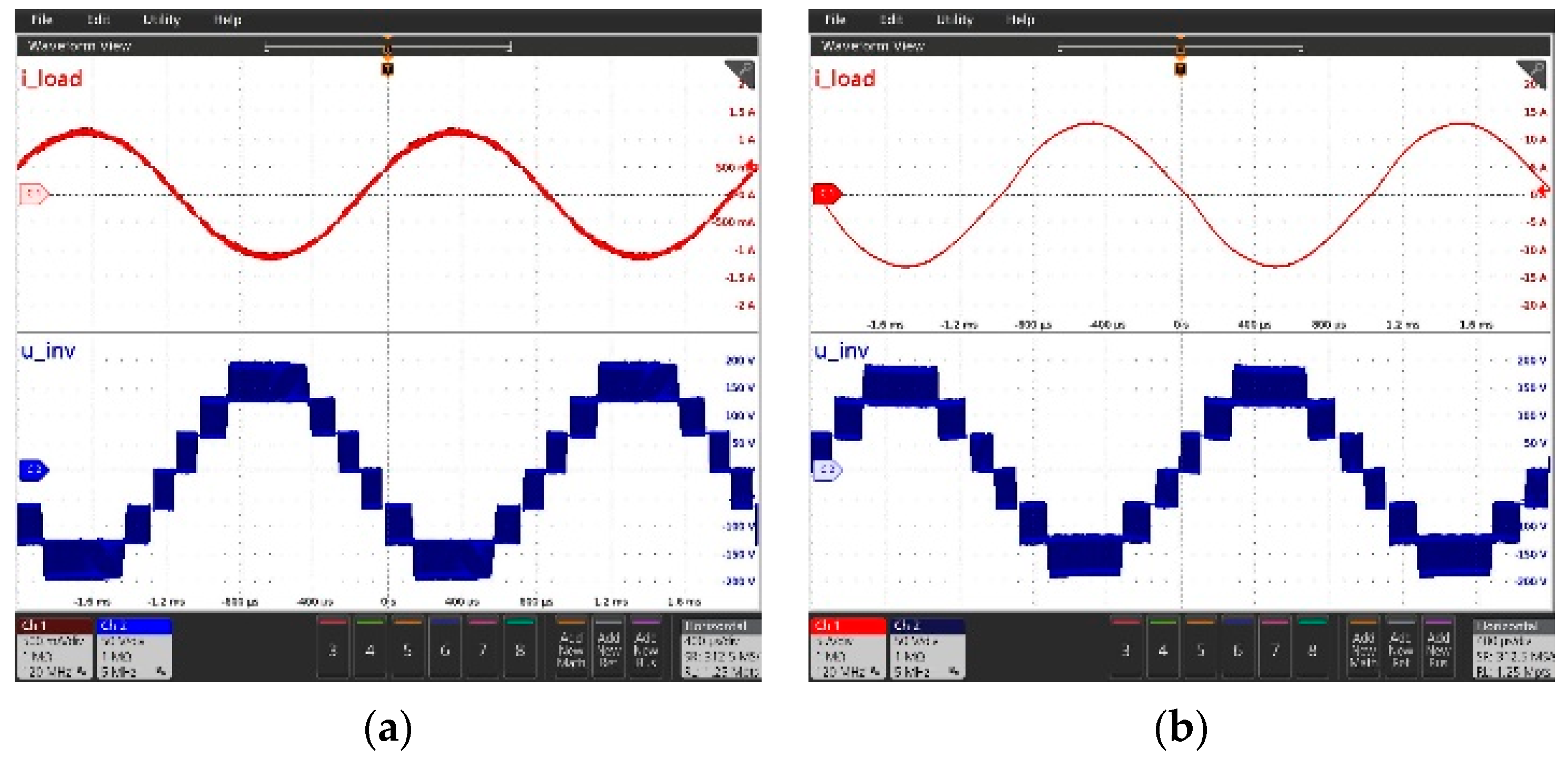

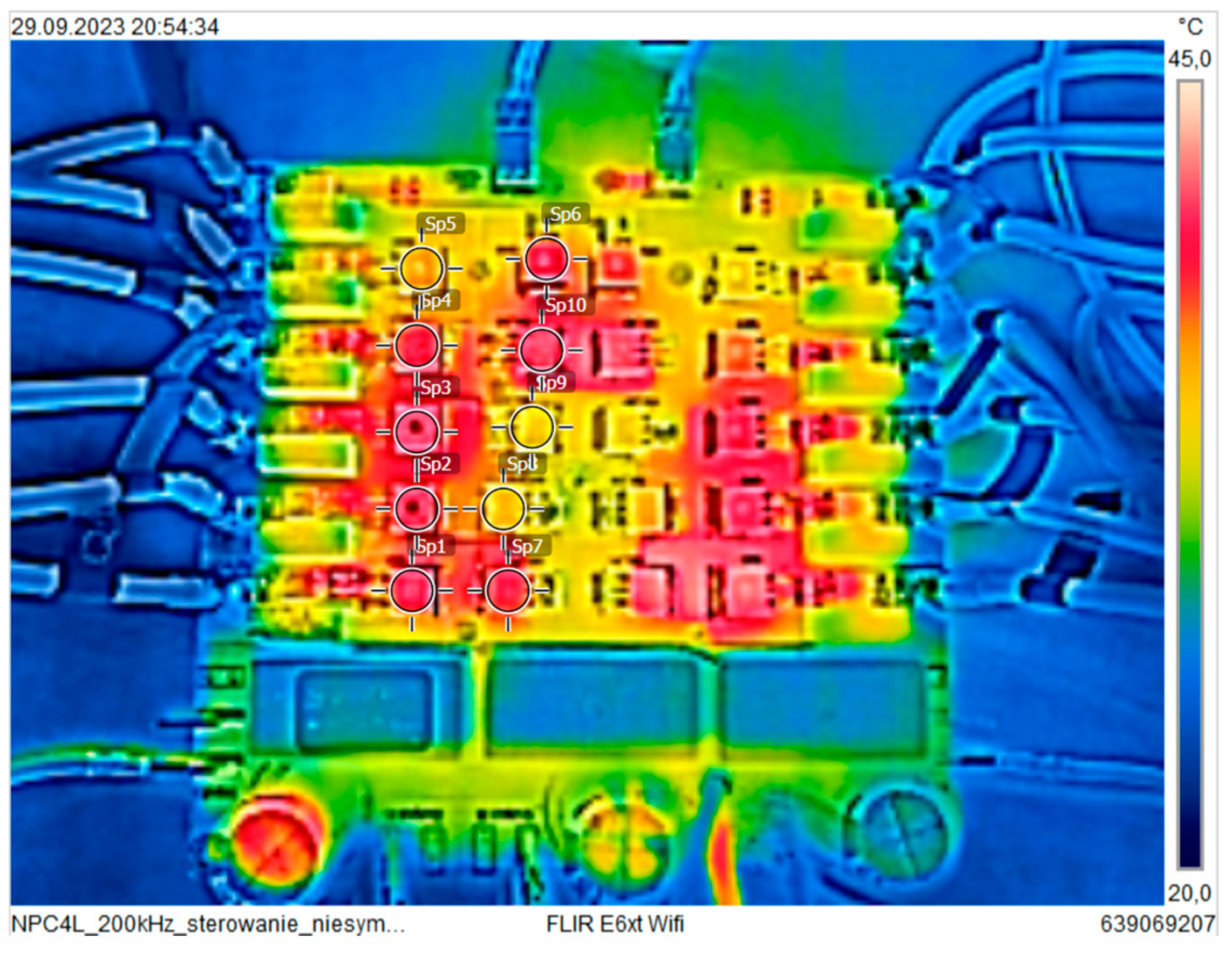

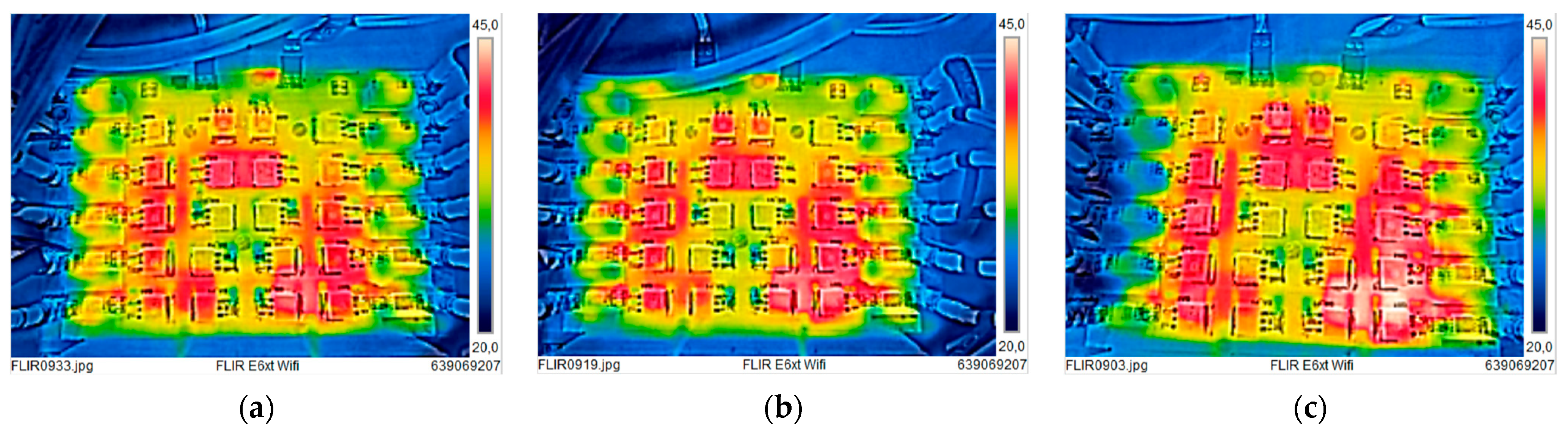

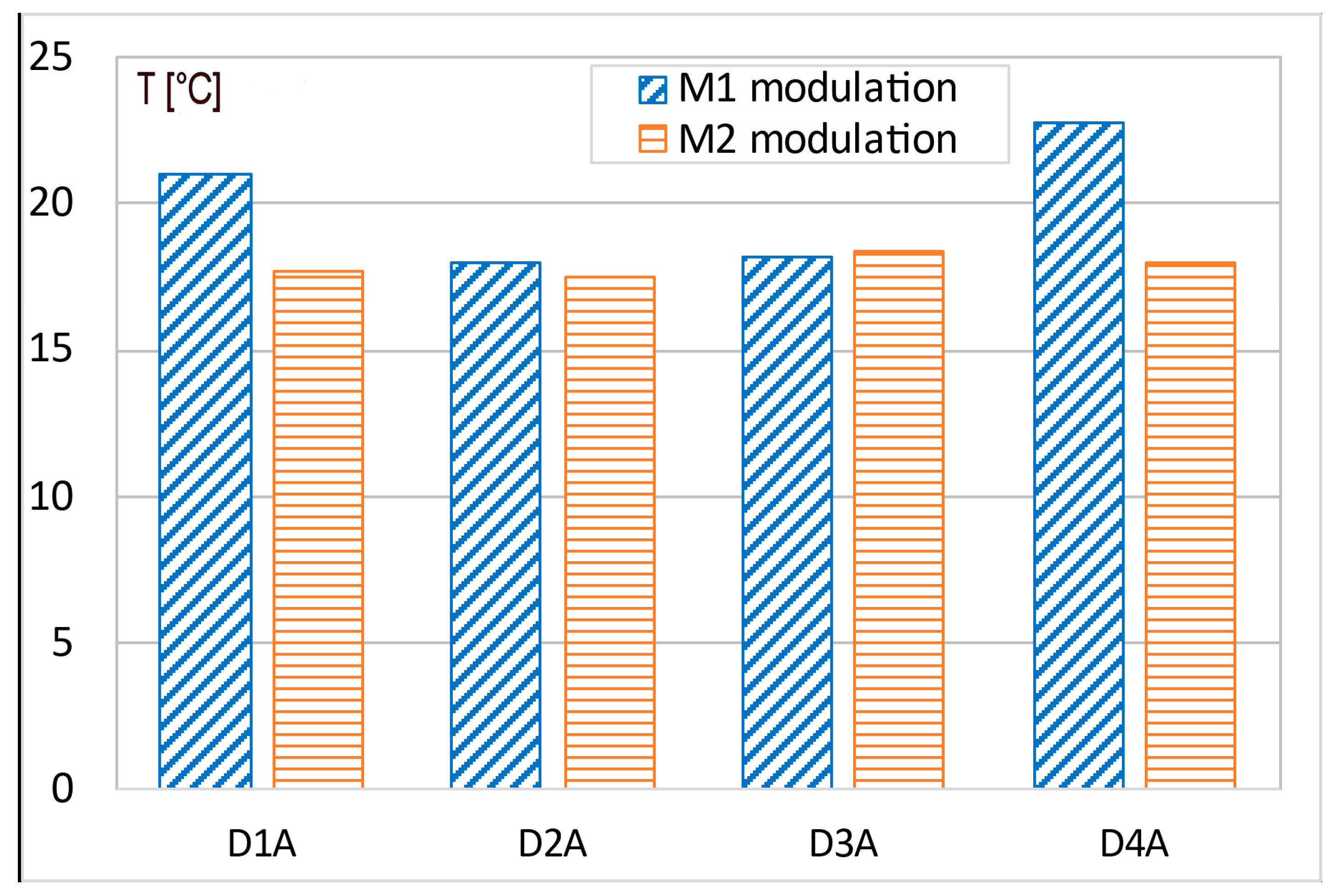

4.2. Experimental Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Shieh, J.-J.; Hwu, K.-I.; Chen, S.-J. Perspective of Voltage-Fed Single-Phase Multilevel DC-AC Inverters. Energies 2023, 16, 898. [Google Scholar] [CrossRef]

- Khan, M.N.H.; Forouzesh, M.; Siwakoti, Y.P.; Li, L.; Kerekes, T.; Blaabjerg, F. Transformerless Inverter Topologies for Single-Phase Photovoltaic Systems: A Comparative Review. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 805–835. [Google Scholar] [CrossRef]

- Anderson, J.A.; Zulauf, G.; Papamanolis, P.; Hobi, S.; Mirić, S.; Kolar, J.W. Three Levels Are Not Enough: Scaling Laws for Multilevel Converters in AC/DC Applications. IEEE Trans. Power Electron. 2021, 36, 3967–3986. [Google Scholar] [CrossRef]

- Stala, R. Natural DC-link voltage balance in a single-phase NPC inverter with four-level legs and novel modulation method. IET Power Electron. 2020, 13, 3764–3776. [Google Scholar] [CrossRef]

- Stala, R.; Hachlowski, J.; Penczek, A. NPC Seven-Level Single-Phase Inverter with DC-Link Voltage Balancing, Input Voltage Boosting, and AC Power Decoupling. Energies 2022, 15, 3729. [Google Scholar] [CrossRef]

- Mecke, R. Multilevel Inverter with New Wide-Bandgap SiC and GaN Power Switches. In Proceedings of the 2021 IEEE 15th International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG), Florence, Italy, 14–16 July 2021; pp. 1–6. [Google Scholar] [CrossRef]

- Mecke, R. Wide-bandgap Semiconductors for Multilevel Inverters—A Comparison with Si IGBT. In Proceedings of the 2023 International Conference on Electrical Drives and Power Electronics (EDPE), The High Tatras, Slovakia, 25–27 September 2023; pp. 1–6. [Google Scholar] [CrossRef]

- Rojas, R.; Ohnishi, T.; Suzuki, T. PWM control method for a four-level inverter. IEE Proc. Electr. Power Appl. 1995, 142, 390–396. [Google Scholar] [CrossRef]

- Wang, K.; Zheng, Z.; Li, Y. A novel carrier-overlapped PWM method for four-level neutral-point clamped converters. IEEE Trans. Power Electron. 2019, 34, 7–12. [Google Scholar] [CrossRef]

- Wang, K.; Zheng, Z.; Xu, L.; Li, Y. A composite voltage balancing method for four- level NPC inverters. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 9, 3394–3406. [Google Scholar] [CrossRef]

- Busquets-Monge, S.; Ruderman, A. Carrier-based PWM strategies for the comprehensive capacitor voltage balance of multilevel multileg diode-clamped converters. In Proceedings of the 2010 IEEE International Symposium on Industrial Electronics, Bari, Italy, 4–7 July 2010; pp. 688–693. [Google Scholar]

- Strzelecki, R.; Szczepankowski, P.; Strzelecka, N. Four level diode-clamped back-to-back converter with active DC link voltage control. In Proceedings of the 2013 International Conference-Workshop Compatibility and Power Electronics, Ljubljana, Slovenia, 5–7 June 2013; pp. 182–187. [Google Scholar]

- Hachlowski, J.; Stala, R. DC-link Voltage Balancing Converter with Resonant Switched-Capacitor Circuit for Four-Level and Six-Level NPC Inverter. In Proceedings of the 2019 21st European Conference on Power Electronics and Applications (EPE 19 ECCE Europe), Genova, Italy, 3–5 September 2019. [Google Scholar]

- Kuo, S.-H.; Lin, Z.-A.; Liu, Y.-H.; Hsieh, Y.-C.; Chiu, H.-J. Study and Implementation of a Single-Phase Diode- Clamped Five-Level Inverter with Auto Equalization. In Proceedings of the 2018 Asian Conference on Energy, Power and Transportation Electrification (ACEPT), Singapore, 30 October–2 November 2018. [Google Scholar]

- Maheshwari, R.; Busquets-Monge, S.; Nicolas-Apruzzese, J. A novel approach to generate effective carrier-based pulse width modulation strategies for diode-clamped multilevel DC–AC converters. IEEE Trans. Ind. Electron. 2016, 63, 7243–7252. [Google Scholar] [CrossRef]

- Dutta, S.; Negi, S.; Yadav, A.K.; Tripathi, A. A New Carrier Based PWM for a 3-Phase 5-Level Neutral Point Clamped Inverter. In Proceedings of the 2023 IEEE 3rd International Conference on Sustainable Energy and Future Electric Transportation (SEFET), Bhubaneswar, India, 9–12 August 2023. [Google Scholar]

- Carrara, G.; Gardella, S.; Marchesoni, M.; Salutar, R.; Sciutto, G. A new multilevel PWM method: A theoretical analysis. IEEE Trans. Power Electron. 1992, 7, 497–505. [Google Scholar] [CrossRef]

- Bharathsrinivas, R.; Angadi, S.; Hombal, G.; Raju, A.B. Investigation of Diode Clamped Multilevel Inverter Using Multicarrier PWM Techniques. In Proceedings of the 2021 IEEE International Conference on Electronics, Computing and Communication Technologies (CONECCT), Bangalore, India, 9–11 July 2021. [Google Scholar]

- Sarker, R. Phase Disposition PWM (PD-PWM) Technique to Minimize WTHD from a Three-Phase NPC Multilevel Voltage Source Inverter. In Proceedings of the 2020 IEEE 1st International Conference for Convergence in Engineering (ICCE), Kolkata, India, 5–6 September 2020; pp. 220–224. [Google Scholar] [CrossRef]

- Stala, R. Nine-level inverter based on NPC topology for high frequency operation. In Proceedings of the 2023 25th European Conference on Power Electronics and Applications (EPE’23 ECCE Europe), Paris, France, 4–8 September 2023. [Google Scholar]

- Li, C.; Chen, J. Simplified SVPWM Capacitor Voltage Balancing Control Method for Four-Level Neutral Point Clamped Inverters. In Proceedings of the 2023 IEEE 14th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Shanghai, China, 9–12 June 2023; pp. 127–132. [Google Scholar] [CrossRef]

- Najah, A.; Essalam, B.A.; Merahi, F.; Laib, A.; Lazhar, R. Performance Analysis of Four Level NPC Inverters using FCS-MPC Voltage Balancing Method. In Proceedings of the 2022 19th International Multi-Conference on Systems, Signals & Devices (SSD), Sétif, Algeria, 6–10 May 2022; pp. 1450–1455. [Google Scholar] [CrossRef]

- Wang, J.; Yuan, X.; Jin, B. Carrier-based Closed-loop DC-link Voltage Balancing Algorithm for Four Level NPC Converters Based on Redundant Level Modulation. IEEE Trans. Ind. Electron. 2021, 68, 11707–11718. [Google Scholar] [CrossRef]

- Wang, J.; Xu, W.; Yuan, X.; Xie, L. Investigation and Mitigation of Common-mode Voltage in Four-level NPC Converters Modulated by Redundant Level Modulation. In Proceedings of the 2022 24th European Conference on Power Electronics and Applications (EPE’22 ECCE Europe), Hanover, Germany, 5–9 September 2022; pp. 1–9. [Google Scholar]

- Gopi, A.K.; Kumar, M.A.; Biswas, J.; Barai, M. An Optimized Hybrid PWM Strategy for Five Level NPC VSI With Unequal DC-Links in a PV System. IEEE J. Emerg. Sel. Top. Ind. Electron. 2022, 3, 766–776. [Google Scholar] [CrossRef]

- Pham, L.N.; Phan, Q.D.; Nguyen, N.-V. Simplified Space Vector Pulse Width Modulation for Four-Level Neutral Point Clamped Inverter. In Proceedings of the 2023 International Symposium on Electrical and Electronics Engineering (ISEE), Ho Chi Minh, Vietnam, 19–20 October 2023; pp. 244–249. [Google Scholar] [CrossRef]

- Tolbert, L.M.; Habetler, T.G. Novel multilevel inverter carrier-based PWM method. IEEE Trans. Ind. Appl. 1999, 35, 1098–1107. [Google Scholar] [CrossRef]

| Level 1 and State Name | Used Switches and DC-Link Capacitors | ||

|---|---|---|---|

| {S1A, S2A, S3A, S4A, S5A, S6A} | {S1B, S2B, S3B, S4B, S5B, S6B} | DC-Link Capacitor | |

| 3 | {1, 1, 1, 0, 0, 0} | {0, 0, 0, 1, 1, 1} | C1, C2, C3 |

| 2 (2a) | {1, 1, 1, 0, 0, 0} | {0, 0, 1, 1, 1, 0} | C1, C2 |

| 2 (2b) | {0, 1, 1, 1, 0, 0} | {0, 0, 0, 1, 1, 1} | C2, C3 |

| 1 (1a) | {1, 1, 1, 0, 0, 0} | {0, 1, 1, 1, 0, 0} | C1 |

| 1 (1b) | {0, 1, 1, 1, 0, 0} | {0, 0, 1, 1, 1, 0} | C2 |

| 1 (1c) | {0, 0, 1, 1, 1, 0} | {0, 0, 0, 1, 1, 1} | C3 |

| Modulation Step 1 (One or Two Repetition Periods), and DC-Link Capacitor Use | |||||||

|---|---|---|---|---|---|---|---|

| n | n + 1 | n + 2 | n + 3 | … | |||

| Levels used for modulation | 0–1 | state: | 1b C2 | 0 none | 1b C2 | 0 none | … |

| 1–2 | state: | 1b C2 | 2a C1, C2 | 1b C2 | 2b C2, C3 | … | |

| 2–3 | state: | 2a C1, C2 | 3 all | 2b C2, C3 | 3 all | … | |

| Modulation Step 1 (One Repetition Periods), and DC-Link Capacitor Use | |||||||||

|---|---|---|---|---|---|---|---|---|---|

| n | n + 1 | n + 2 | n + 3 | n + 4 | n + 5 | … | |||

| Levels used for modulation | 0–1 | State: | 1a C1 | 0 None | 1b C2 | 0 None | 1c C3 | 0 None | … |

| 1–2 | State: | 1a C1 | 2a C1, C2 | 1c C3 | 2b C2, C3 | … | |||

| 2–3 | State: | 1a C1 | 3 All | 1b C2 | 3 All | 1c C3 | 3 All | … | |

| Parameter | Value |

|---|---|

| All the MOSFETS Rds(on) [mΩ] | 12–30 |

| MOSFETS COSS [pF] | 395 and 900 |

| Schottky clamping diodes VF [V] | 0.72 |

| Input voltage Uin [V] | 400 |

| Switching frequency fS [kHz] | 100 |

| Parameter | Value |

|---|---|

| Transistors | IPB073N15N5 UDS = 150 V ID = 114 A RDS(on) = 7.3 mΩ |

| Diodes | VBT10202C-M3/4W IF(AV) = 2 × 5 A URRM = 200 V UF = 0.65 V at IF = 5 A |

| LC filter | 150 uH/2 × 4.7 uF |

| Input voltage Uin | 400 (3 × 133) V |

| Switching frequency fS | 100–300 kHz |

| Output voltage Uout | 150 V (RMS) |

| Output power Pout | 50–1100 W |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Stala, R.; Folmer, S.; Penczek, A.; Hachlowski, J.; Mikoś, Z. Efficiency and Power Loss Distribution in a High-Frequency, Seven-Level Diode-Clamped Inverter. Energies 2023, 16, 7866. https://doi.org/10.3390/en16237866

Stala R, Folmer S, Penczek A, Hachlowski J, Mikoś Z. Efficiency and Power Loss Distribution in a High-Frequency, Seven-Level Diode-Clamped Inverter. Energies. 2023; 16(23):7866. https://doi.org/10.3390/en16237866

Chicago/Turabian StyleStala, Robert, Szymon Folmer, Adam Penczek, Jakub Hachlowski, and Zbigniew Mikoś. 2023. "Efficiency and Power Loss Distribution in a High-Frequency, Seven-Level Diode-Clamped Inverter" Energies 16, no. 23: 7866. https://doi.org/10.3390/en16237866

APA StyleStala, R., Folmer, S., Penczek, A., Hachlowski, J., & Mikoś, Z. (2023). Efficiency and Power Loss Distribution in a High-Frequency, Seven-Level Diode-Clamped Inverter. Energies, 16(23), 7866. https://doi.org/10.3390/en16237866