Research on the Modulation and Control Strategy for a Novel Single-Phase Current Source Inverter

Abstract

:1. Introduction

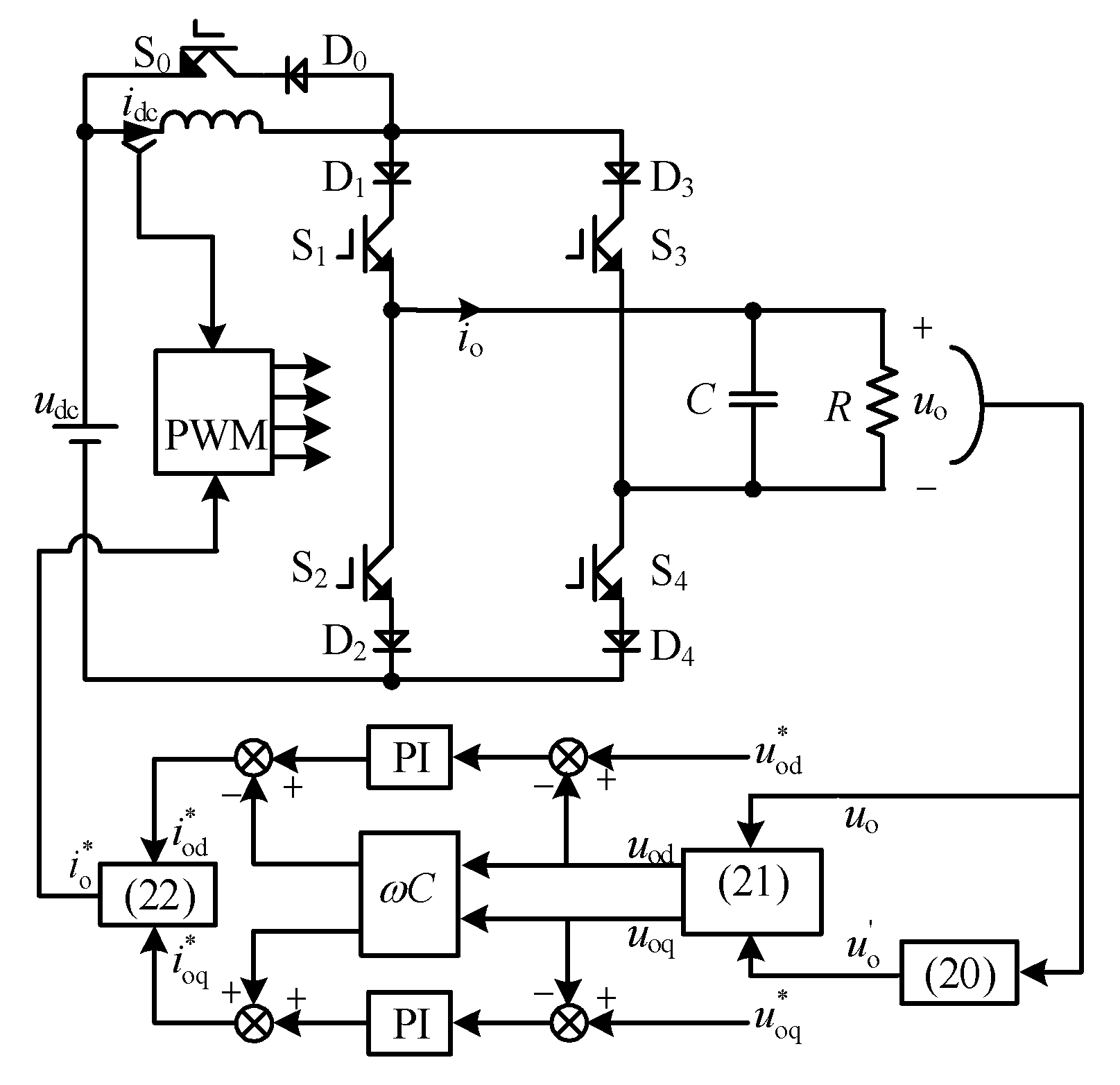

2. Topology and Operating Modes of the Proposed Single-Phase CSI

2.1. Analysis of the Proposed Single-Phase CSI’s Operating Modes

2.2. Comparison of Different CSI Topologies

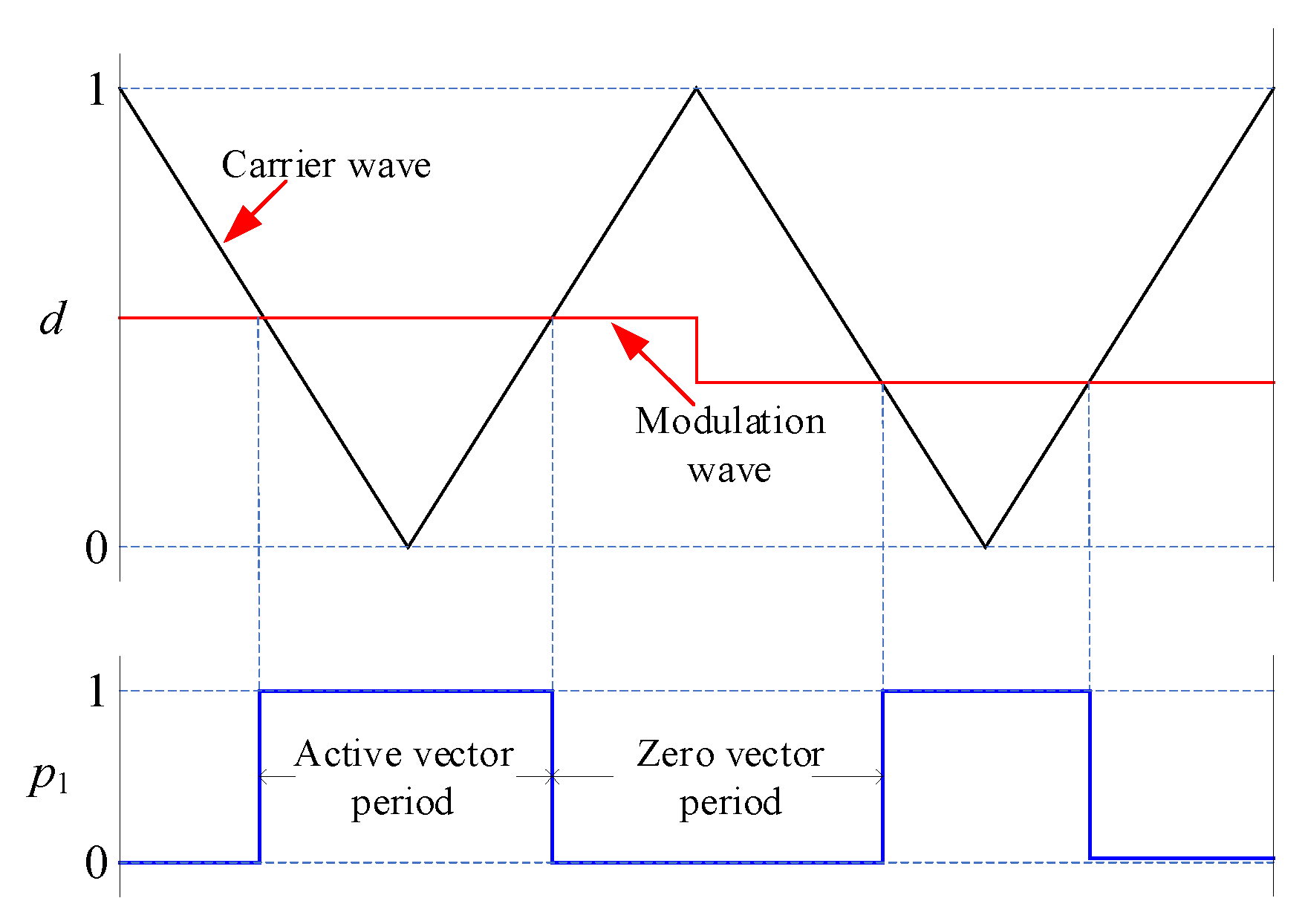

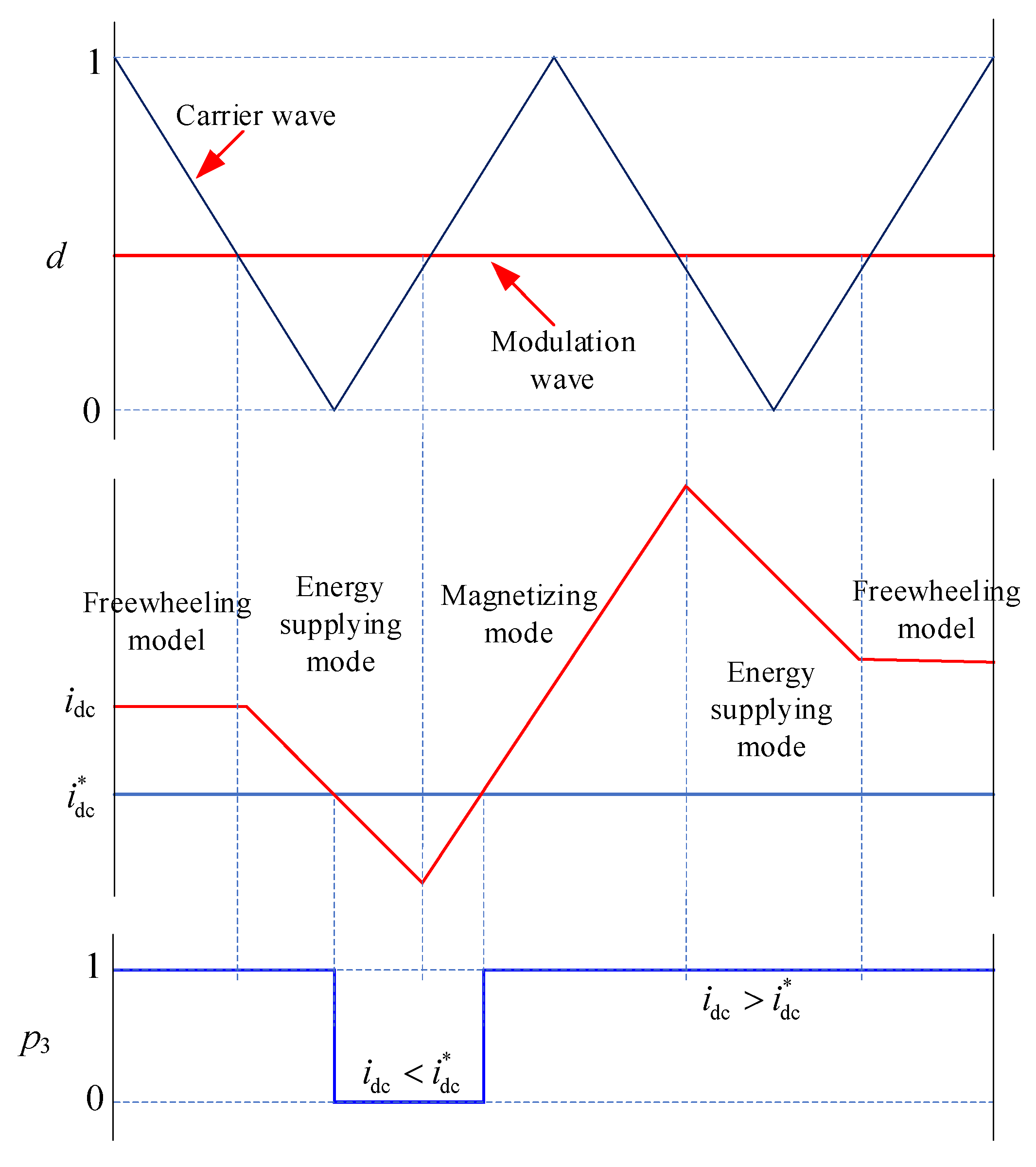

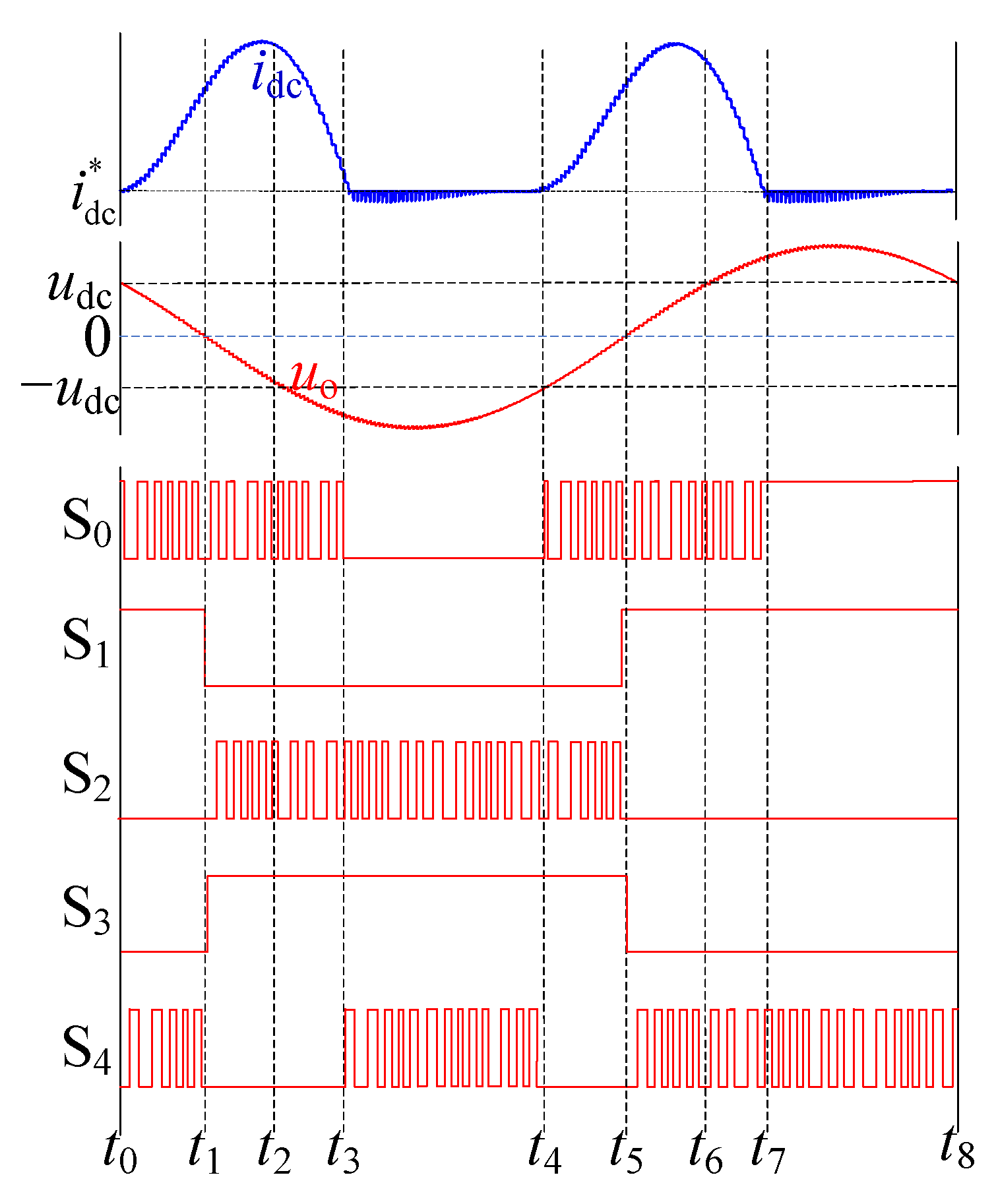

3. Modulation Strategy Based on DC-Link Current Control

4. Calculation for the Optimal Reference of DC-Link Current

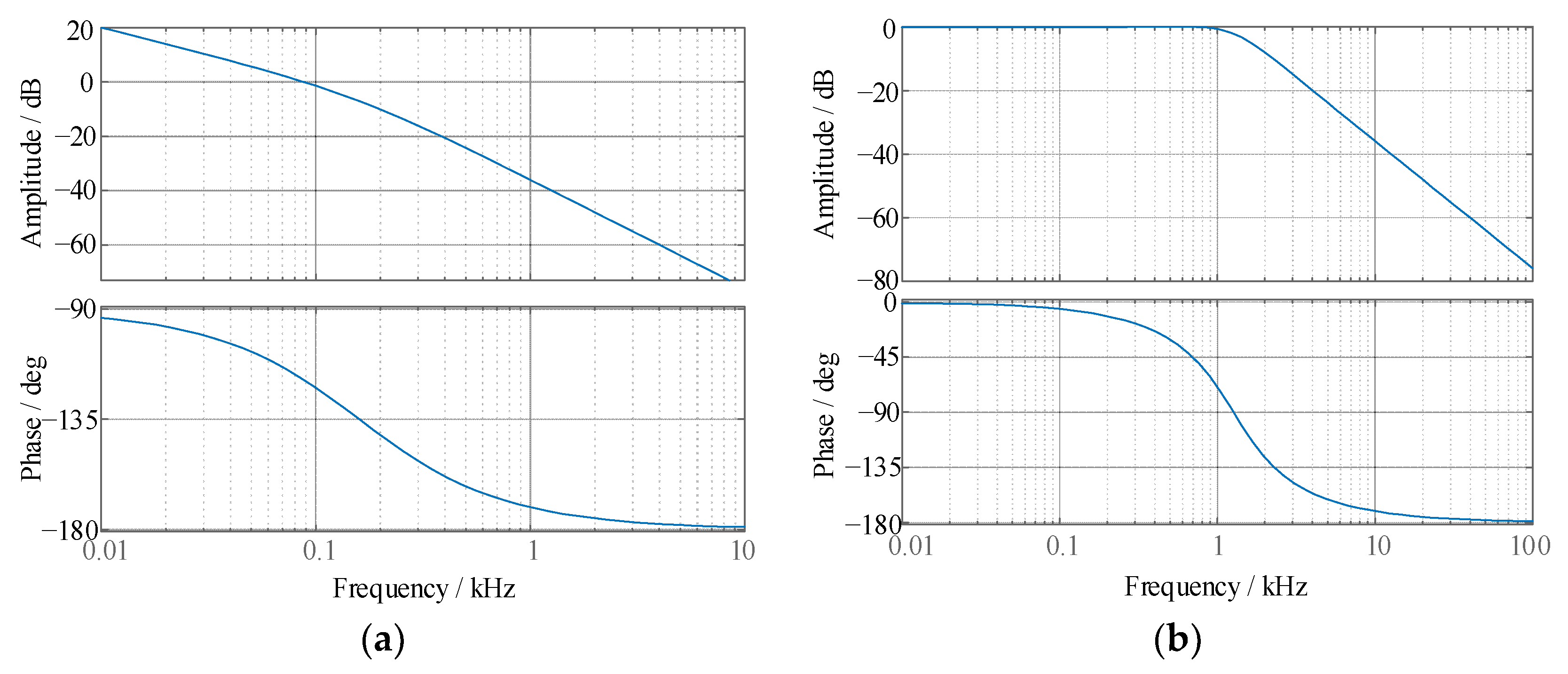

5. Control Strategy of the Output Voltage

6. Experimental Results

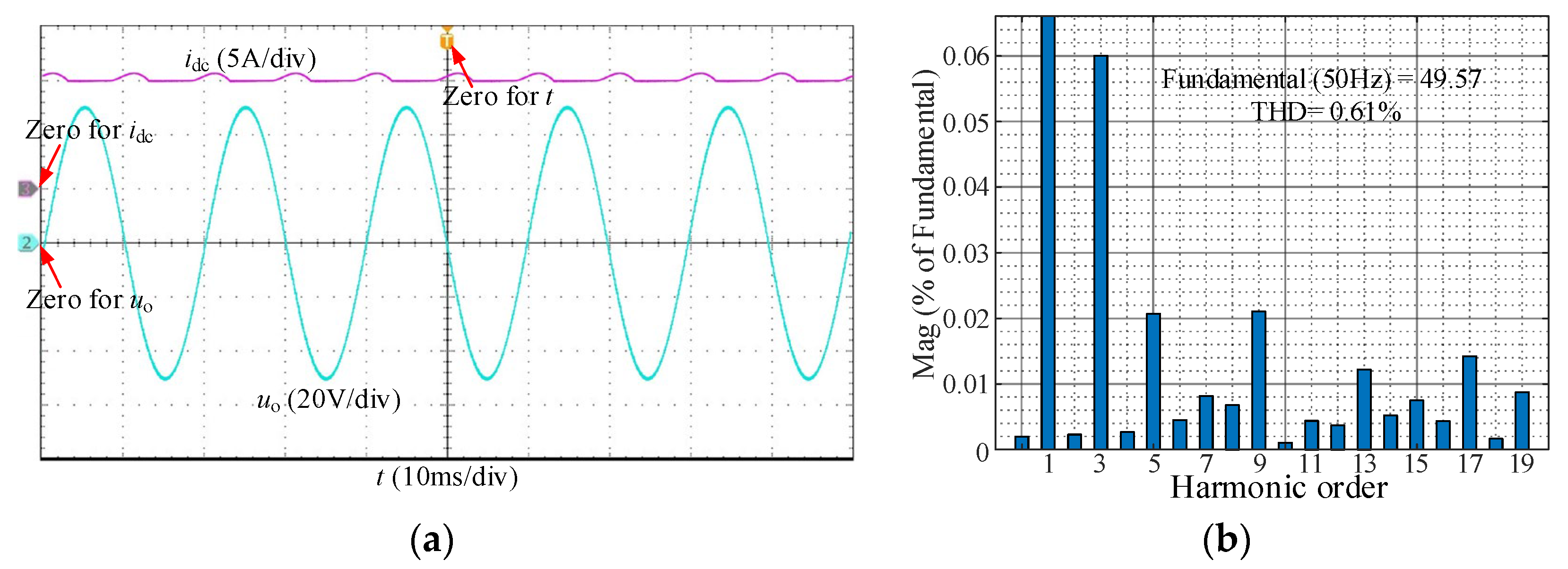

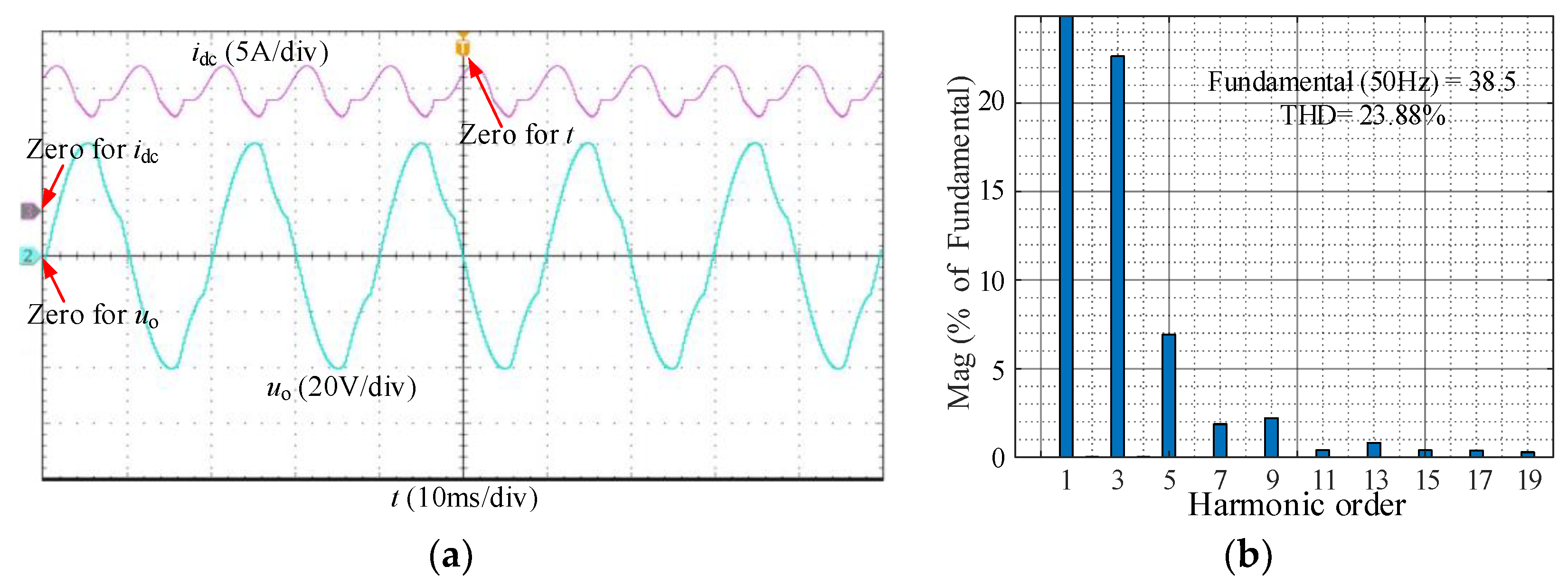

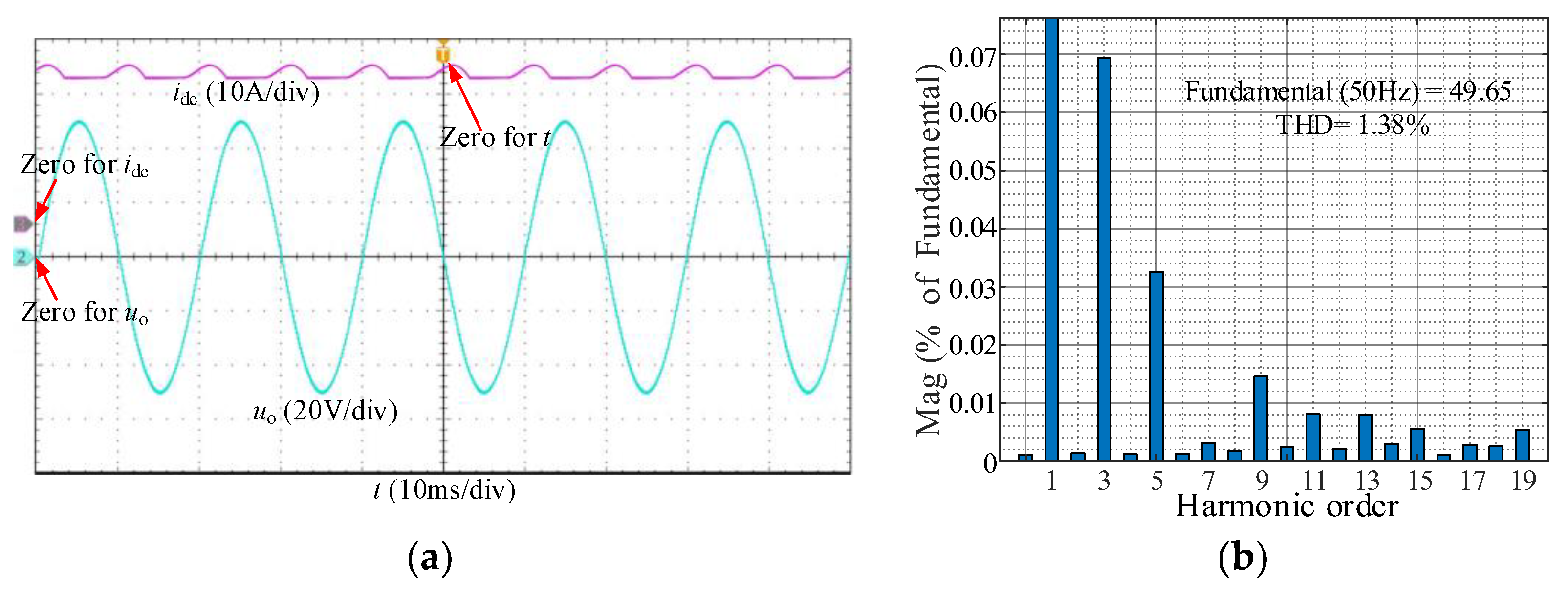

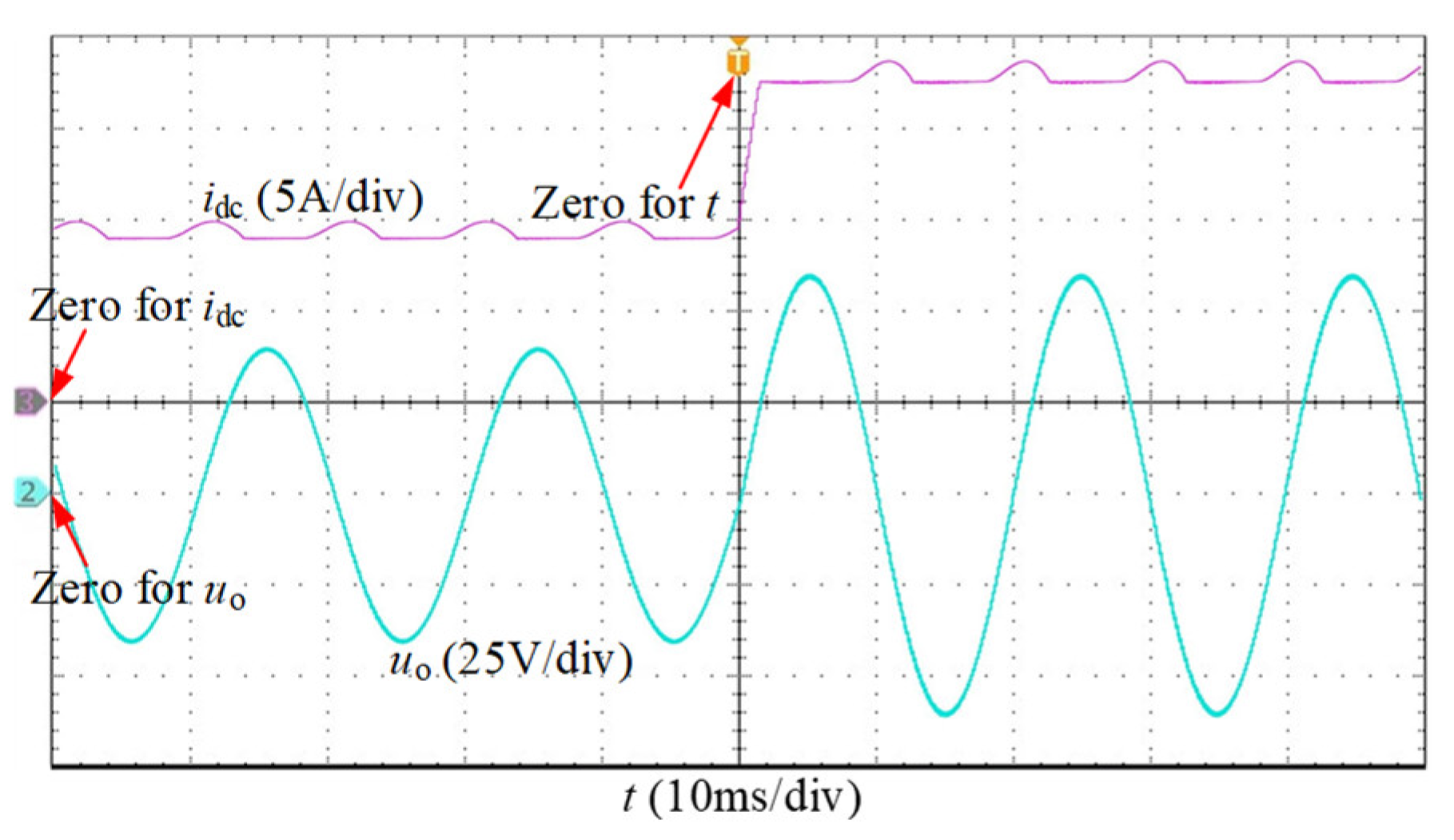

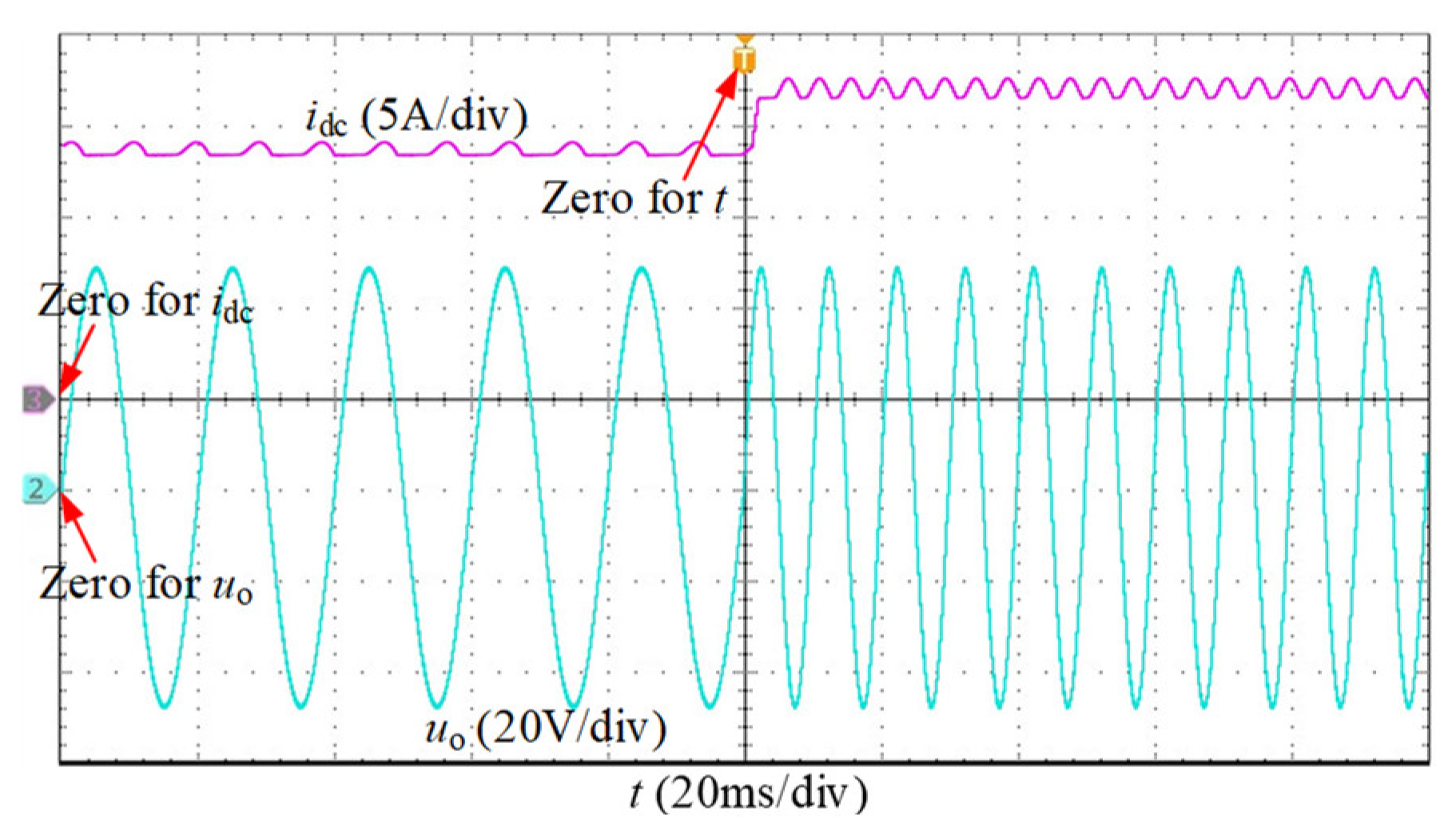

6.1. Experimental Results of Steady-State

6.2. Experimental Results of Dynamic-State

7. Conclusions

Supplementary Materials

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Nomenclature

| VSI | Voltage Source Inverter |

| CSI | Current Source Inverter |

| HVDC | High Voltage Direct Current |

| Ldc | DC-link inductance (mH) |

| C | AC side’s filter capacitor (μF) |

| R | AC side’s resistive load (Ω) |

| idc | DC side’s current (A) |

| io | Output current on the resistive load R (A) |

| udc | DC side’s voltage (V) |

| uo | Output voltage on the resistive load R (A) |

| p/q | Switching functions for S0, S1, S2, S3, and S4 (-) |

| d | Duty cycle (%) |

| Reference of the output current io (A) | |

| Reference of the DC side’s current idc (A) | |

| ∆idc_down | Decrement of idc when discharging (A) |

| ∆idc_up | Increment of idc when charging (A) |

| Ts | Switching period (s) |

| U | Fundamental amplitude of uo (V) |

| I | Fundamental amplitude of io (A) |

| θ | Initial phase of io (rad) |

| ω | Fundamental frequency of io (Hz) |

| ∆idcmax | Maximum reduction of idc (A) |

| uod/uod | d-q frame components of uo |

| Reference of uod/uod | |

| iod/iod | d-q frame components of io |

| Reference of iod/iod |

References

- Chakrabarti, A.; Sarkar, K.; Kasari, P.R.; Das, B.; Biswas, S.K. A CB-PWM Technique for Eliminating CMV in Multilevel Multiphase VSI. IEEE Trans. Ind. Electron. 2022, 70, 8666–8675. [Google Scholar] [CrossRef]

- He, J.; Zhang, C.; Lei, M.; Han, J.; Guo, P.; Li, Y. An Active Bypass Pulse Injection-Based Low Switching Frequency PWM Approach for Harmonic Compensation of Current-Source Converters. IEEE Trans. Power Electron. 2021, 36, 1614–1625. [Google Scholar] [CrossRef]

- Rajeev, M.; Agarwal, V. Single phase current source inverter with multiloop control for transformerless grid–PV interface. IEEE Trans. Ind. Appl. 2018, 54, 2416–2424. [Google Scholar] [CrossRef]

- Titus, J.; Harikrishnan, P.; Hatua, K. An SCR-Based CSI-Fed Induction Motor Drive for High Power Medium Voltage Applications. IEEE Trans. Ind. Electron. 2020, 68, 4657–4666. [Google Scholar] [CrossRef]

- Guo, X.-Q.; Sui, S.; Wang, B.; Zhang, W. A Current-Based Approach for Short-Circuit Fault Diagnosis in Closed-Loop Current Source Inverter. IEEE Trans. Ind. Electron. 2019, 67, 7941–7950. [Google Scholar] [CrossRef]

- Miao, Y.; Liao, W.; Huang, S.; Liu, P.; Wu, X.; Song, P.; Li, G. DC-Link Current Minimization Scheme for IM Drive System Fed by Bidirectional DC Chopper-Based CSI. IEEE Trans. Transp. Electrif. 2023, 9, 2839–2850. [Google Scholar] [CrossRef]

- Li, Y.W.; Pande, M.; Zargari, N.R.; Wu, B. DC-link current minimization for high-power current-source motor drives. IEEE Trans. Power Electron. 2008, 24, 232–240. [Google Scholar]

- Geng, Y.; Yang, K.; Lai, Z.; Zheng, P.; Liu, H.; Deng, R. A Novel Low Voltage Ride Through Control Method for Current Source Grid-Connected Photovoltaic Inverters. IEEE Access 2019, 7, 51735–51748. [Google Scholar] [CrossRef]

- Wang, W.; Gao, F.; Yang, Y.; Blaabjerg, F. Operation and modulation of H7 current-source inverter with hybrid SiC and Si semiconductor switches. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 6, 387–399. [Google Scholar] [CrossRef]

- Yang, S.; Peng, F.Z.; Lei, Q.; Inoshita, R.; Qian, Z. Current-fed quasi-Z-source inverter with voltage Buck–Boost and regeneration capability. IEEE Trans. Ind. Appl. 2010, 47, 882–892. [Google Scholar] [CrossRef]

- Guo, X.; Wang, N.; Zhang, J.; Wang, B.; Nguyen, M.-K. A Novel Transformerless Current Source Inverter for Leakage Current Reduction. IEEE Access 2019, 7, 50681–50690. [Google Scholar] [CrossRef]

- Nascimento, A.J.P.; de Menezes, B.F.; de Mesquita, S.J.; Costa, K.R.; Tofoli, F.L.; Daher, S.; Antunes, F.L.M. Bidirectional Isolated Asymmetrical Multilevel Inverter. IEEE Trans. Circuits Syst. II Express Briefs 2022, 70, 151–155. [Google Scholar] [CrossRef]

- Sun, R.; Wang, X.; Ye, Y. Seventeen-Level Inverter Based on Switched-Capacitor and Flying-Capacitor-Fed T-type Unit. IEEE Access 2022, 10, 33561–33570. [Google Scholar] [CrossRef]

- Ding, L.; Li, Y.W. Simultaneous DC current balance and common-mode voltage control with multilevel current source inverters. IEEE Trans. Power Electron. 2018, 33, 9188–9197. [Google Scholar] [CrossRef]

- Guo, Q.; Zhou, C.; Li, S. A Multiple Loops Control Strategy Based on DC Link Voltage of Current Source PWM Rectifiers. Trans. China Electrotech. Soc. 2022, 37, 2051–2063. [Google Scholar]

- Wu, F.; Feng, F.; Luo, L.; Duan, J.; Sun, L. Sampling period online adjusting-based hysteresis current control without band with constant switching frequency. IEEE Trans. Ind. Electron. 2014, 62, 270–277. [Google Scholar] [CrossRef]

- Wang, Z.; Wu, B.; Xu, D.; Cheng, M.; Xu, L. DC-link current ripple mitigation for current-source grid-connected converters under unbalanced grid conditions. IEEE Trans. Ind. Electron. 2016, 63, 4967–4977. [Google Scholar] [CrossRef]

| Operating Modes | Switching State | Switching Function p and q |

|---|---|---|

| magnetizing mode | S1 and S2 ON, S0, S3, and S4 OFF | p = 0, q = 1 |

| energy-supplying mode I | S1 and S4 ON, S0, S2, and S3 OFF | p = 1, q = 0 |

| energy-supplying mode II | S2 and S3 ON, S0, S1, and S4 OFF | p = −1, q = 0 |

| freewheeling model | S0 ON, S1, S2, S3, and S4 OFF | p = 0, q = 0 |

| Operating Mode | Withstand Voltage S0 | Withstand Voltage S1 | Withstand Voltage S2 | Withstand Voltage S3 | Withstand Voltage S4 |

|---|---|---|---|---|---|

| Magnetizing mode | udc | 0 | 0 | −uo | uo |

| Energy-supplying mode | udc − uo | 0 | −uo | −uo | 0 |

| Freewheeling model | 0 | uo | −udc − uo | 0 | −udc |

| Parameter | Current Source Rectifier | Buck Converter | Quasi-Z Source Network | Bidirectional DC Chopper | Proposed Single-Phase CSI |

|---|---|---|---|---|---|

| NV | 1 | 1 | 1 | 1 | 1 |

| NUS | 0 | 0 | 0 | 0 | 0 |

| NBS | 8 | 5 | 4 | 6 | 5 |

| ND | 8 | 5 | 5 | 6 | 5 |

| NC | 2 | 1 | 2 | 1 | 1 |

| Ndrv | 8 | 5 | 4 | 6 | 5 |

| NT | 0 | 0 | 1 | 0 | 0 |

| Nl | 3 | 3 | 3 | 3 | 3 |

| CF | 11.33 | 7 | 6.67 | 8.33 | 7 |

| Input H Bridge | Yes | No | No | Yes | No |

| Modulation | PWM | PWM | PWM | PWM | PWM |

| Name | Value |

|---|---|

| DC input voltage (V) | 25 |

| AC output voltage (V) | 30~150 |

| Load power (W) | ≤103 |

| Output frequency (Hz) | ≤500 Hz |

| Switching frequency (Hz) | 10 k |

| Sampling frequency (Hz) | 10 k |

| Ldc (mH) | 4 |

| C (μF) | 265 |

| R (Ω) | 25 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, Y.; Yang, T.; Miao, Y. Research on the Modulation and Control Strategy for a Novel Single-Phase Current Source Inverter. Energies 2023, 16, 6729. https://doi.org/10.3390/en16186729

Zhang Y, Yang T, Miao Y. Research on the Modulation and Control Strategy for a Novel Single-Phase Current Source Inverter. Energies. 2023; 16(18):6729. https://doi.org/10.3390/en16186729

Chicago/Turabian StyleZhang, Yi, Tao Yang, and Yiru Miao. 2023. "Research on the Modulation and Control Strategy for a Novel Single-Phase Current Source Inverter" Energies 16, no. 18: 6729. https://doi.org/10.3390/en16186729

APA StyleZhang, Y., Yang, T., & Miao, Y. (2023). Research on the Modulation and Control Strategy for a Novel Single-Phase Current Source Inverter. Energies, 16(18), 6729. https://doi.org/10.3390/en16186729