High-Performance Charge Pump Regulator with Integrated CMOS Voltage Sensing Control Circuit

Abstract

1. Introduction

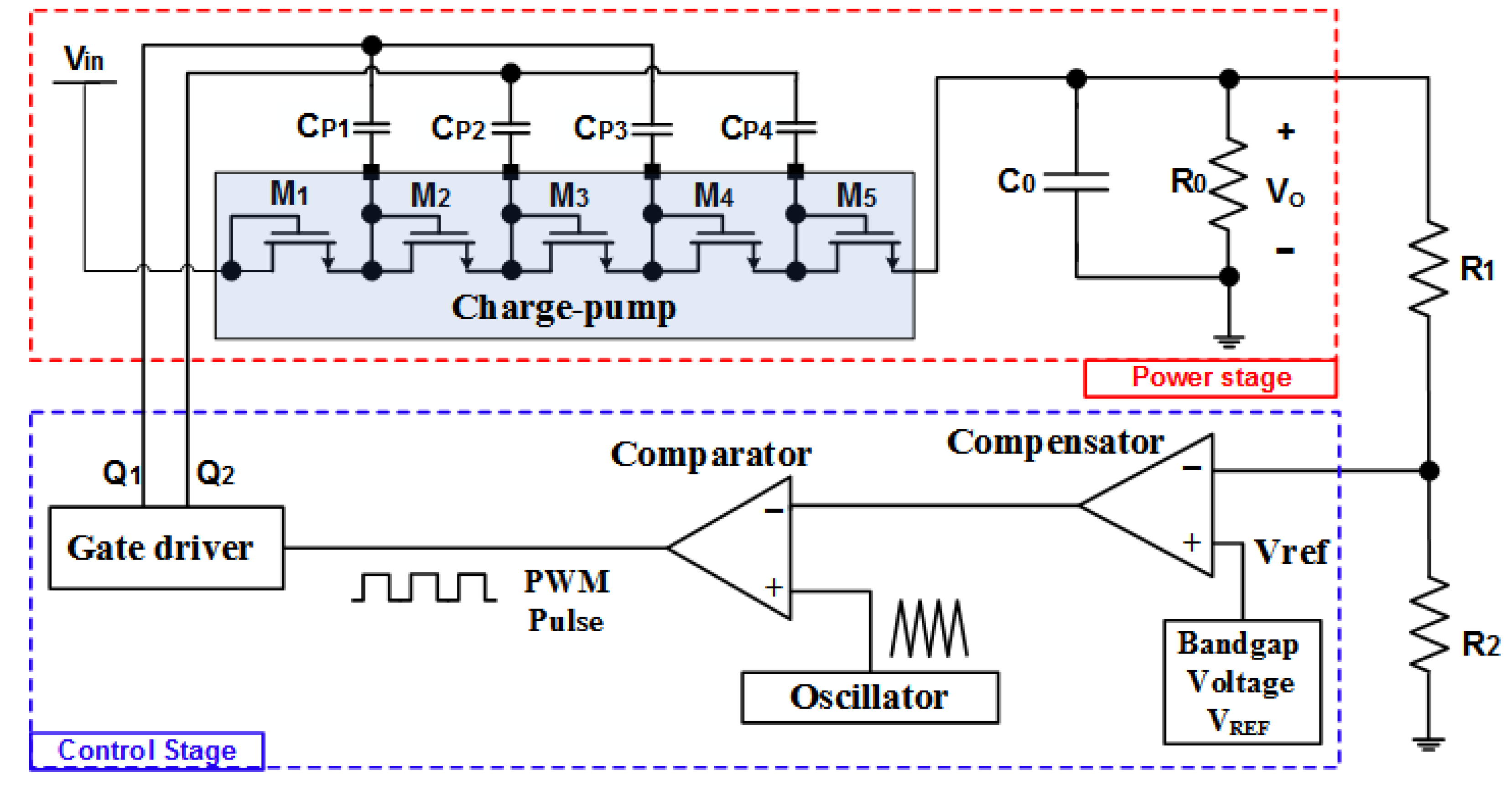

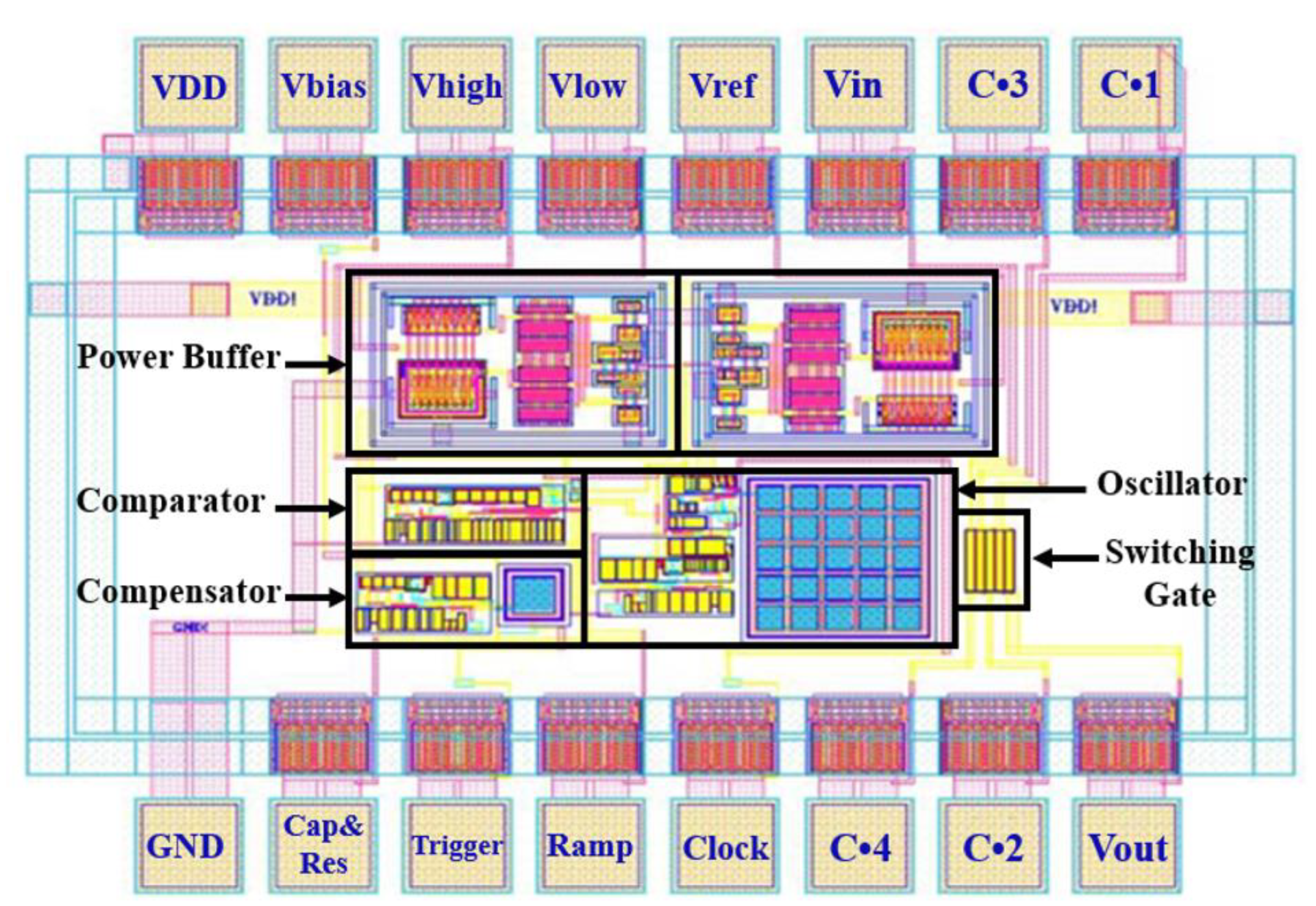

2. Circuit Implementations

2.1. Charge Pump Circuit

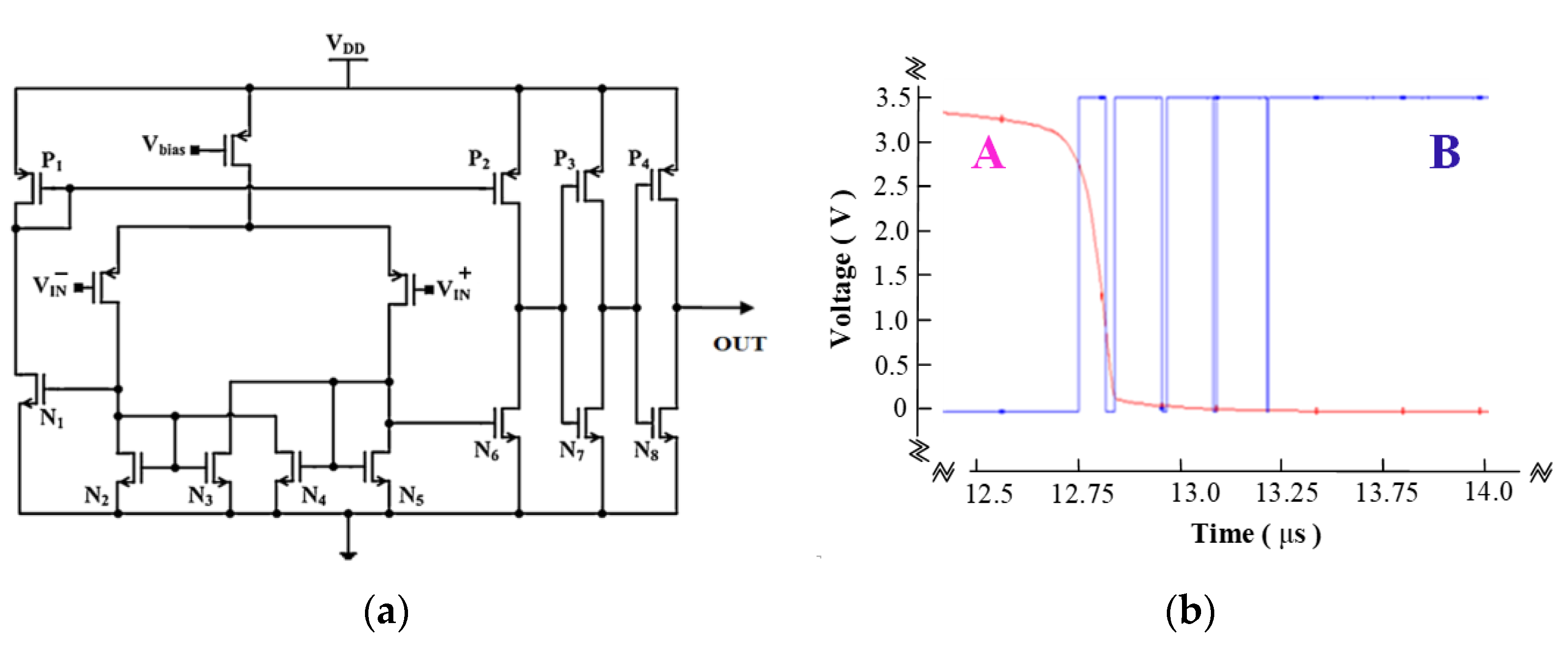

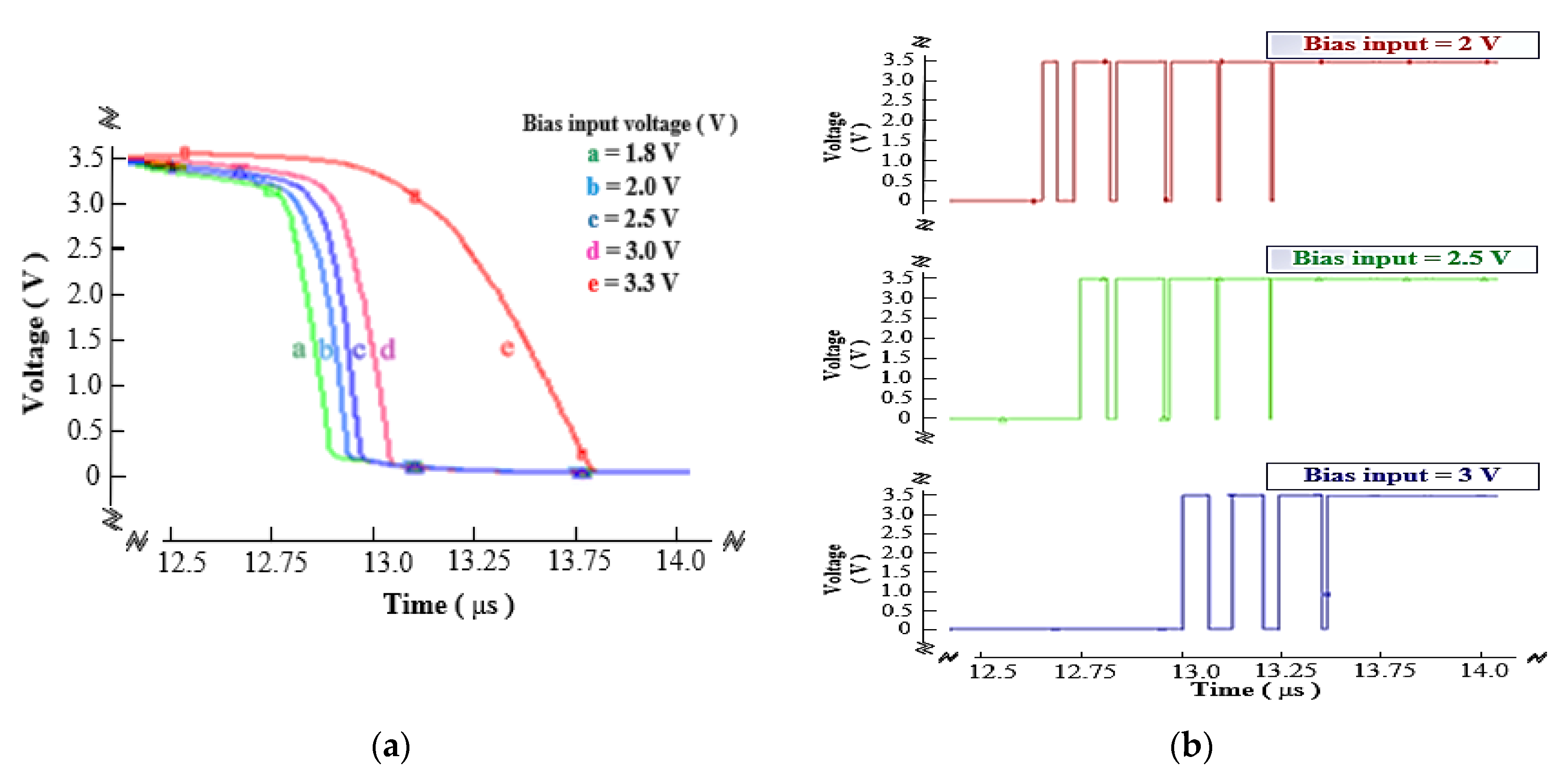

2.2. Error-Amp Circuit

2.3. Comparator Circuit

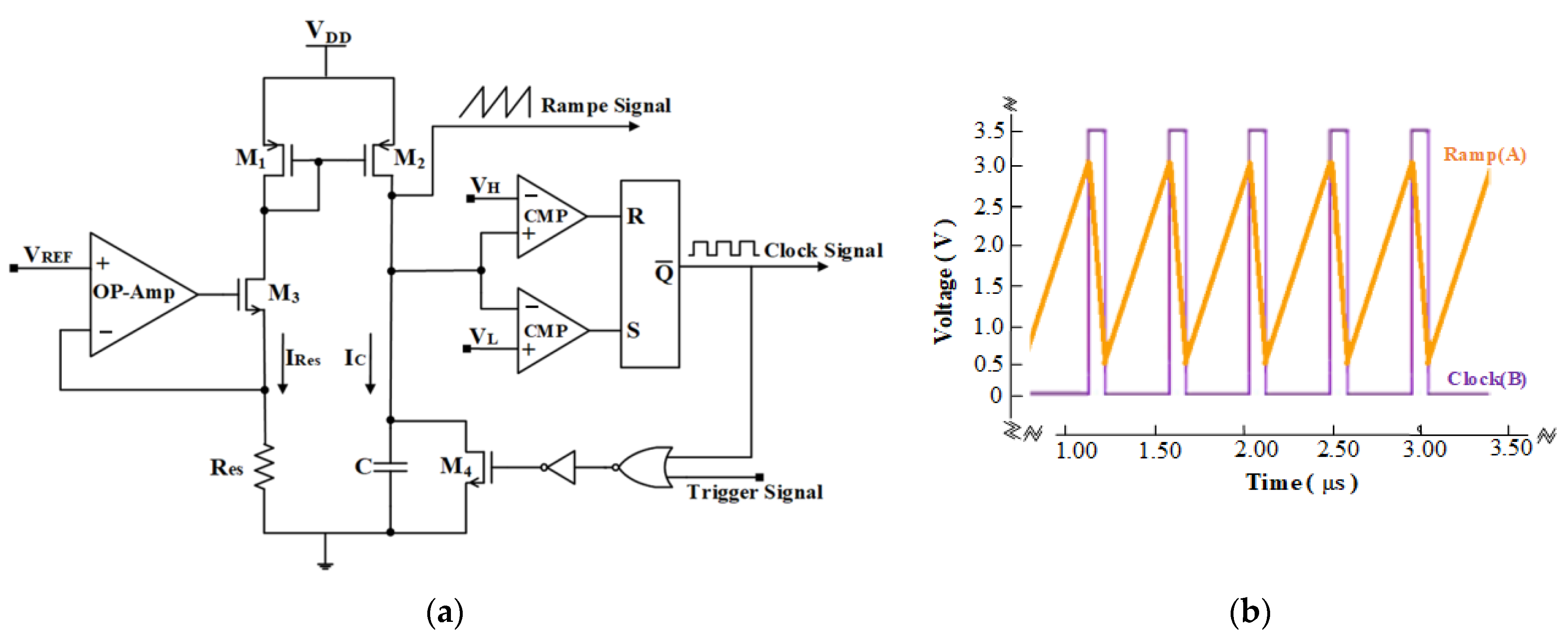

2.4. Oscillator Circuit

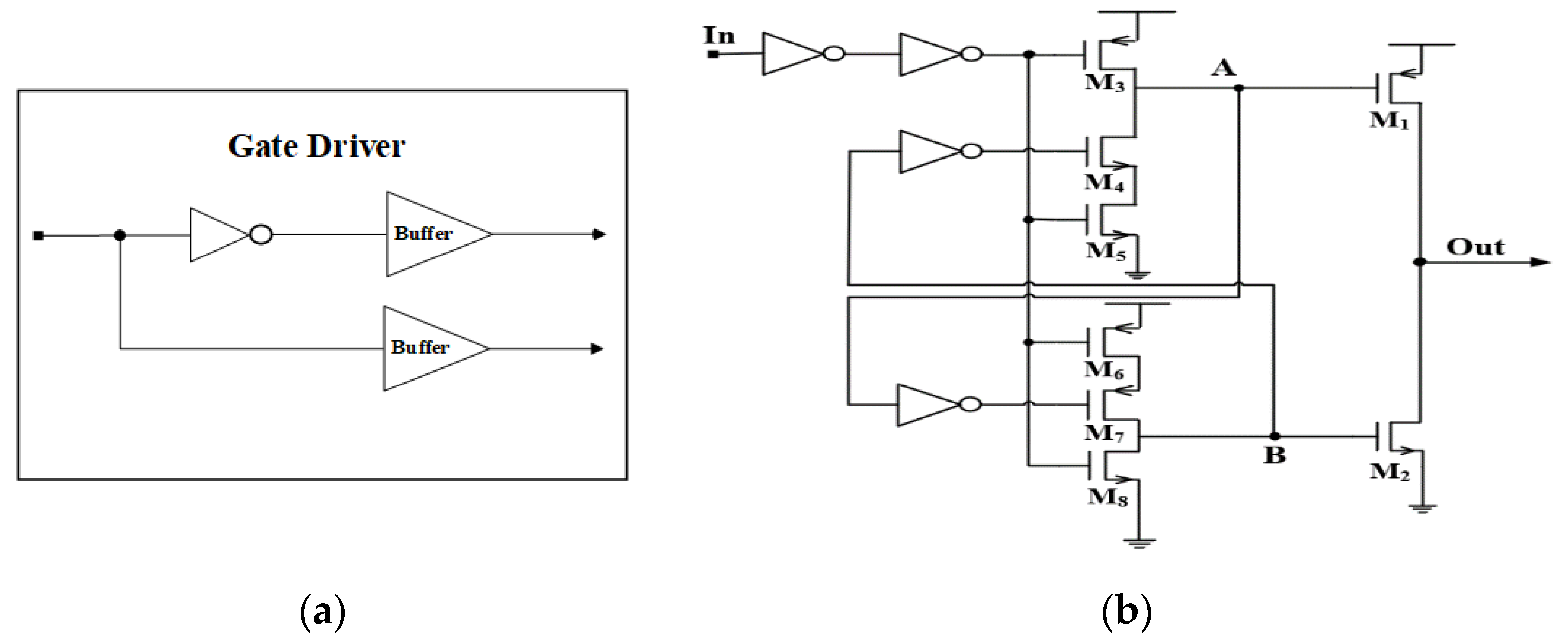

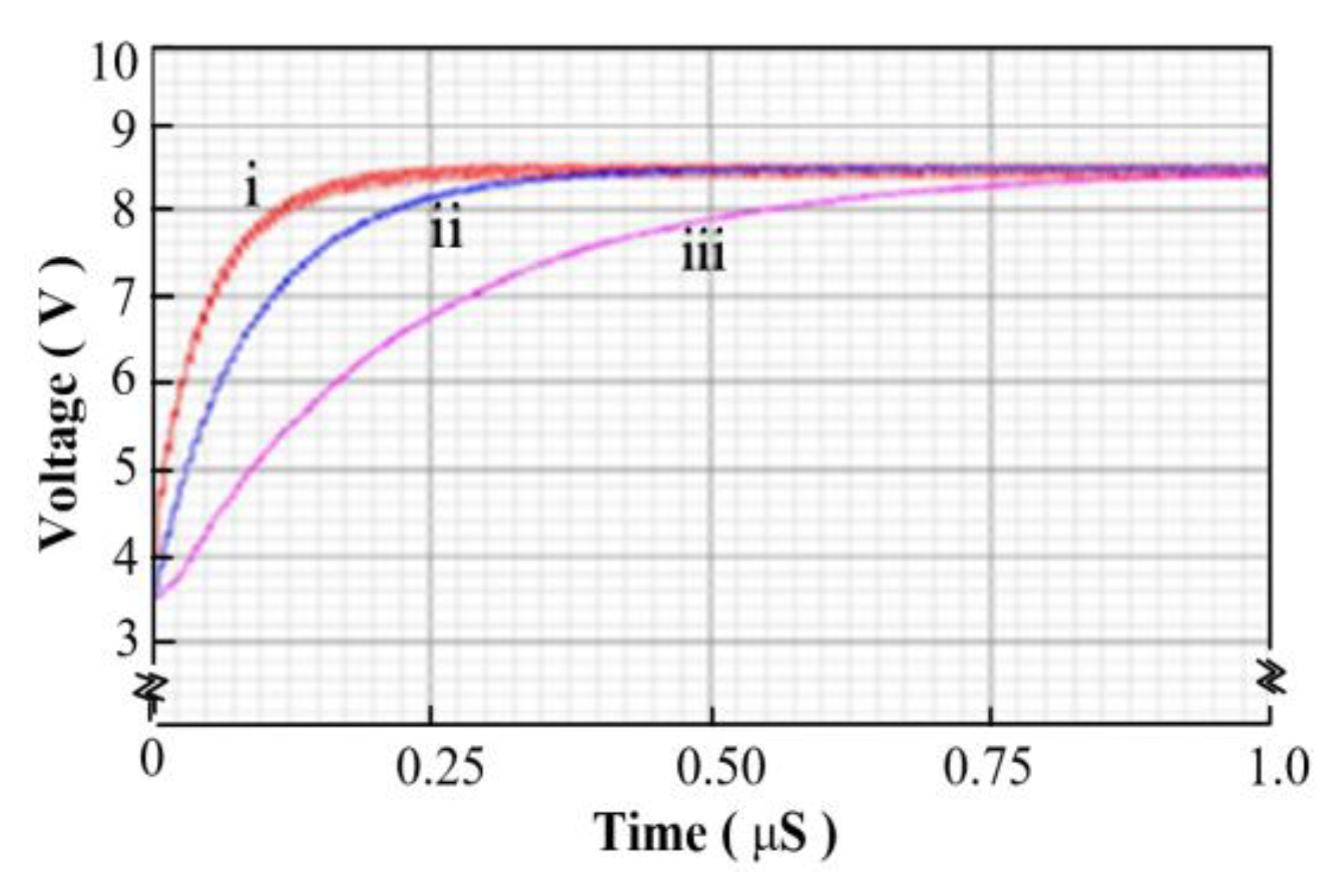

2.5. Gate Driver Circuit

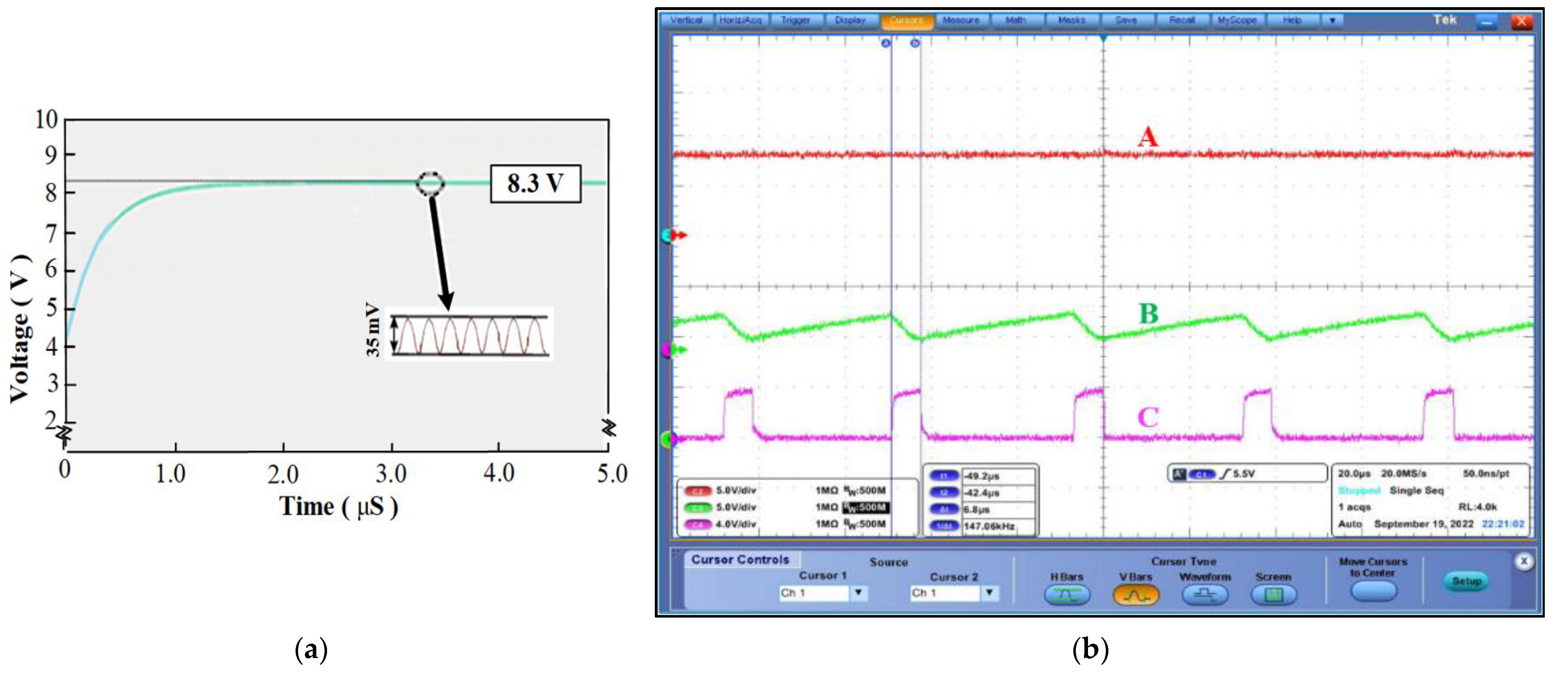

3. Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Tao, X.; Xu, J. Integrated current–sensing circuit with offset-current cancellation for boost regulators. In Proceedings of the 2008 International Conference on Communications, Circuits and Systems, Xiamen, China, 25–27 May 2008; pp. 1328–1331. [Google Scholar]

- Lee, C.S.; Ko, H.H.; Kim, N.S. Current-mode DC–DC boost regulator with high-performance control circuit. Analog. Integr. Circuits Signal Process. 2014, 80, 105–112. [Google Scholar] [CrossRef]

- Lee, C.S.; Gendensuren, M.; Bayarsaikhan, D.; Ahn, B.C.; Choi, S.G. Integrated 0.35-µm CMOS Control Circuits for High Performance Voltage-Mode DC-DC Boost Regulator. Electronics 2022, 12, 133. [Google Scholar] [CrossRef]

- Park, J.W.; Gendensuren, M.; Lee, C.S.; Lee, H.G.; Kim, N.S. Charge Pump Regulation with Integrated 0.35 µm CMOS Control Circuit. In Proceedings of the 2012 International Symposium on Signals, Systems, and Electronics (ISSSE), Potsdam, Germany, 3–5 October 2012; pp. 391–394. [Google Scholar]

- Chae, C.S.; Le, H.P.; Lee, K.C.; Cho, G.H. A single- inductor step-up DC-DC switching regulator with bipolar outputs for active matrix OLED mobile display panels. IEEE J. Solid-State Circuits 2009, 44, 509–524. [Google Scholar] [CrossRef]

- Rahman, L.F.; Marufuzzaman, M.; Alam, L.; Mokhtar, M.B. Design topologies of a CMOS charge pump circuit for low power applications. Electronics 2021, 10, 676. [Google Scholar] [CrossRef]

- Ma, X.; Wang, L.; Yu, J. A 5 V-to-32 V input PVT-robust charge-pump circuit with adjustable output in a 0.18 μm BCD process. Electronics 2022, 11, 2828. [Google Scholar] [CrossRef]

- Navidi, M.M.; Graham, D.W. A regulated charge pump with extremely low output ripple. Electronics 2022, 8, 1293. [Google Scholar] [CrossRef]

- Ballo, A.; Grasso, A.D.; Palumbo, G. A review of charge pump topologies for the power management of IoT nodes. Electronics 2019, 8, 480. [Google Scholar] [CrossRef]

- Lim, M.I.; Mi, S.; Sampe, J.; Ali, S.H.M. Review of Charge Pump Topologies for Micro Energy Harvesting Systems. Am. J. Appl. Sci. 2016, 13, 628–645. [Google Scholar]

- Mahmoud, A.; Alhawari, M.; Mohammad, B.; Saleh, H.; Ismail, M. A gain-controlled low-leakage Dickson charge pump for energy-harvesting applications. IEEE Trans. J. 2019, 27, 1114–1123. [Google Scholar] [CrossRef]

- Kuo, P.H.; Wong, O.-Y.; Tzeng, C.K.; Wu, P.W.; Chiao, C.C.; Chen, P.H.; Chen, P.C.; Tsai, Y.C.; Chu, F.L.; Ohta, J.; et al. Improved charge pump design and ex vivo experimental validation of CMOS 256-pixel photovoltaic-powered subretinal prosthetic chip. IEEE Trans. J. Biomed. Eng. 2020, 67, 1490–1504. [Google Scholar] [CrossRef]

- Toru, T. An Analytical Model of Charge Pump DC-DC Voltage Multiplier Using Diodes. IEICE Trans. Fundam. Electron. Commun. Comput. Sci. 2017, E100, 1137–1144. [Google Scholar]

- Ballo, A.; Grasso, A.D.; Palumbo, G.; Tanzawa, T. A Charge Loss Aware Advanced Model of Dickson Voltage Multipliers. IEEE Access J. Vol. 2022, 10, 118082–118092. [Google Scholar] [CrossRef]

- Aloqlah, A.S.; Alhawari, M. A resistor-network model of Dickson charge pump using steady-state analysis. Energ. J. Mar. 2022, 15, 1899. [Google Scholar] [CrossRef]

- Du, H.; Lai, X.; Liu, C.; Chi, Y. Low quiescent current linear regulator using combination structure of bandgap and error amplifier. Electron. Lett. 2014, 50, 771–773. [Google Scholar] [CrossRef]

- Liu, P.; Chen, T.; Hsu, S. Area-efficient error amplifier with current-boosting module for fast-transient buck regulators. IET Power Electron. 2016, 9, 2147–2153. [Google Scholar] [CrossRef]

- Feng, P.; Li, Y.; Wu, N. A high efficiency charge pump circuit for low power applications. J. Semicond. 2010, 31, 015009. [Google Scholar]

- Ballo, A.; Grasso, A.D.; Palumbo, G. Current-mode body-biased switch to increase performance of linear charge pumps. Int. J. Circuit Theory Appl. 2020, 48, 1864–1872. [Google Scholar] [CrossRef]

- Lilic, N.; Kappel, R.; Roehrer, G.; Zimmermann, H. Methods for the Charge Pump Power Efficiency Improvement in Triple Well Technologies. In Proceedings of the 2020 27th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Glasgow, UK, 23–25 November 2020; pp. 1–4. [Google Scholar]

- Tanzawa, T.; Tanaka, T. A dynamic analysis of the Dickson charge pump. IEEE J. Solid-State Circuits 1997, 32, 1231–1240. [Google Scholar] [CrossRef]

- Roh, J. High-performance error amplifier for fast transient DC-DC regulators. IEEE Trans. Circuits Syst. II Express Briefs 2005, 52, 591–595. [Google Scholar]

- Dickson, F.F. On-chip high-voltage generation in nMOS integrated circuits using an improved voltage multiplier technique. IEEE J. Solid-State Circuits 1976, SC-1142, 374–378. [Google Scholar] [CrossRef]

- Yoo, C.S.; Lee, K.L. A low ripple poly-Si TFT charge pump for driver-integrated LCD pane. IEEE Trans. Consum. Electron. 2005, 51, 606–610. [Google Scholar]

- Dong-Sheng, L.; Xue-Cheng, Z.; Fan, Z.; Min, D. Embeded EEPROM memory achieving lower power-new design of EEPROM memory for RFID tag IC. IEEE Circuits Devices Mag. 2006, 22, 53–59. [Google Scholar] [CrossRef]

- Rumberg, B.; Graham, D.W.; Navidi, M.M. A regulated charge pump for tunneling floating-gate transistors. IEEE Trans. Circuit Syst. Express Briefs 2017, 64, 516–527. [Google Scholar]

- Rahman, L.F.; Alam, L.; Marufuzzaman, M. Design of a Low Power and High-Efficiency Charge Pump Circuit for RFID Transponder EEPROM. Inf. MIDEM 2021, 50, 255–262. [Google Scholar]

| Parameters | Proposed Charge Pump | Only Charge Pump |

|---|---|---|

| Load Resistor (R0) | 20 kΩ | 20 kΩ |

| Load Capacitor (C0) | 47 nF | 47 nF |

| Input Voltage (VIN) | 1.8–3.5 V | 1.8–3.5 V |

| Output Voltage (Vout) | 7.5–9.5 V | 7.5–9.5 V (Unregulated) |

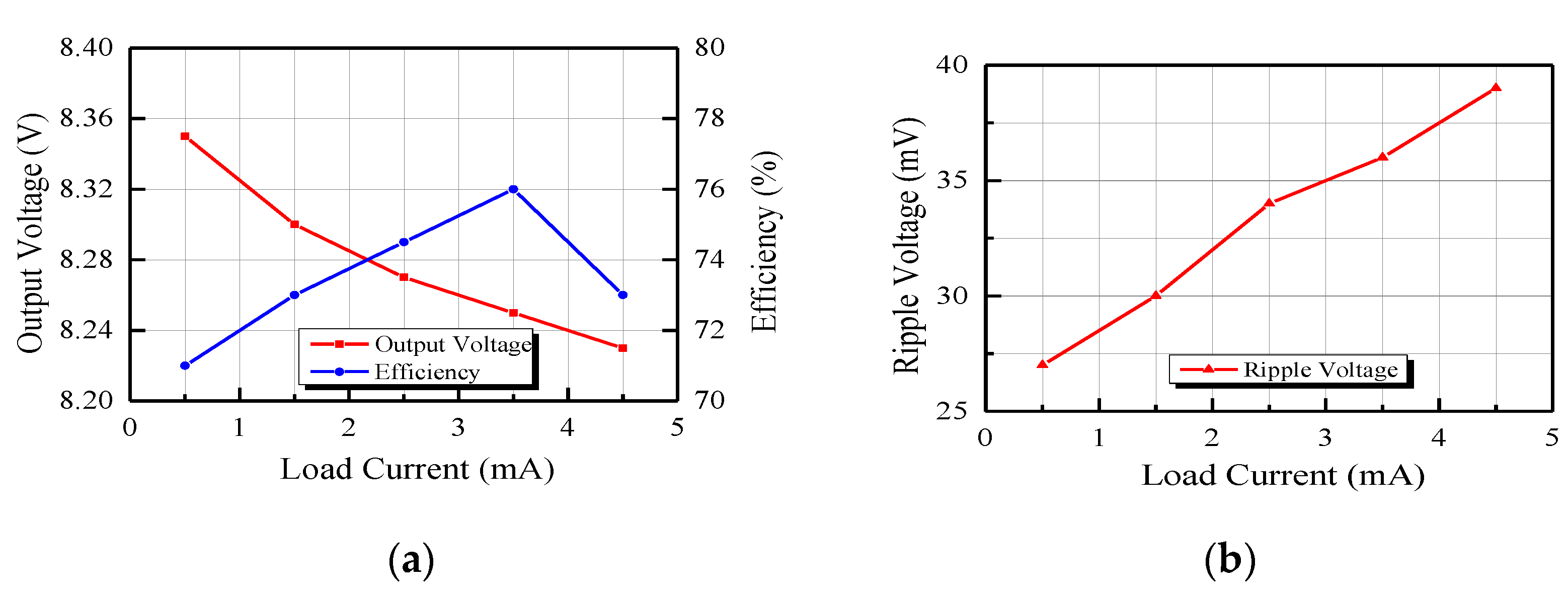

| Load Current (IL) | 4.5 mA (max) | 4.5 mA (max) |

| Switching Frequency (fs) | 2 MHz | 2 MHz |

| Ripple Voltage (Vripple) | 27–38 mV | 52–95 mV |

| Efficiency (Sim) | 76% (max) | 50% (max) |

| Sample No. | This Work | [25] | [26] | [27] |

|---|---|---|---|---|

| Regulator type | Charge pump | Dynamic CTS | Regulated CP | Enhanced-NCP2CTS |

| Process (μm) | 0.35 | 0.35 | 0.35 | 0.18 |

| Input Voltage (V) | 1.8–3.5 | 3.3 | 2.5 | 1.8 |

| Output Voltage (V) | 7.5–9.5 | 2.5–5 | 16 | 5.95 |

| Die Area (mm2) | 1.0 | 0.6 | 69 | 2.4 |

| Switching Frequency (MHz) | 2 | 3 | 30 | 20 |

| Efficiency (%) | 76 (Sim) | - | 34 | 66 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, C.-S.; Monebi, A.M.; Bayarsaikhan, D.; Xu, S.; Ahn, B.-C.; Lee, I.-S. High-Performance Charge Pump Regulator with Integrated CMOS Voltage Sensing Control Circuit. Energies 2023, 16, 4577. https://doi.org/10.3390/en16124577

Lee C-S, Monebi AM, Bayarsaikhan D, Xu S, Ahn B-C, Lee I-S. High-Performance Charge Pump Regulator with Integrated CMOS Voltage Sensing Control Circuit. Energies. 2023; 16(12):4577. https://doi.org/10.3390/en16124577

Chicago/Turabian StyleLee, Chan-Soo, Ayodeji Matthew Monebi, Dansran Bayarsaikhan, Songyuan Xu, Bierng-Chearl Ahn, and In-Sung Lee. 2023. "High-Performance Charge Pump Regulator with Integrated CMOS Voltage Sensing Control Circuit" Energies 16, no. 12: 4577. https://doi.org/10.3390/en16124577

APA StyleLee, C.-S., Monebi, A. M., Bayarsaikhan, D., Xu, S., Ahn, B.-C., & Lee, I.-S. (2023). High-Performance Charge Pump Regulator with Integrated CMOS Voltage Sensing Control Circuit. Energies, 16(12), 4577. https://doi.org/10.3390/en16124577