Analysis of a Single-Phase Transformerless Bidirectional PFC

Abstract

1. Introduction

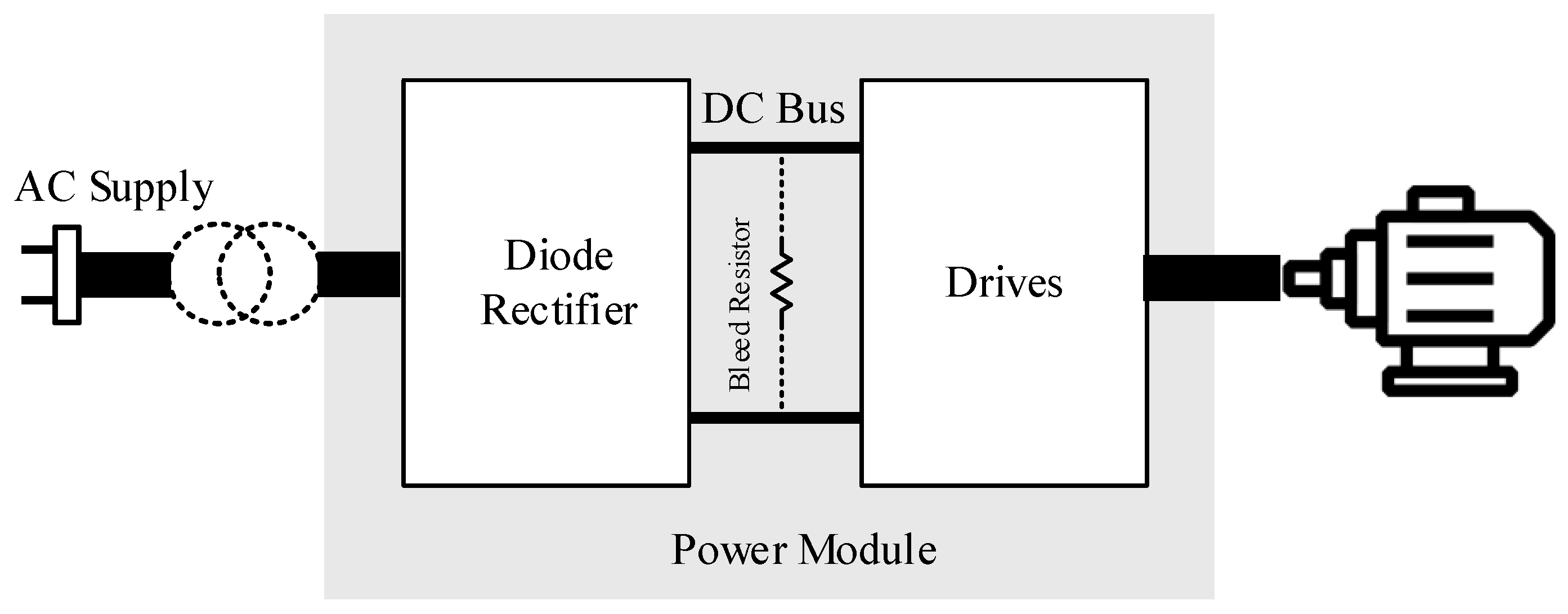

- (1)

- The power flow in the diode rectifier is unidirectional, the regenerative power, generated when the motors decelerate, must be consumed on the bleed resistor, which is installed at the DC bus. Therefore, the total energy efficiency of traditional configuration is very low, and results in the high temperature of the bleed resistor.

- (2)

- The line transformer is always added to supplement the low grid voltage, due to the fact that the DC voltage converted by the diode rectifier is not high enough for the normal operation of the drive for the motor. One additional line transformer must be added to boost the voltage. However, the line transformer is heavy, bulky, and expensive.

- (3)

- The stray capacitor, existing in the long cables to connect the drive with the motor, passes the common-mode leakage current through the ground terminal in the absence of the line transformer. The common-mode leakage current needs to meet certain standards to protect the equipment and humans [10,11,12]; for example, the rms value of the leakage current should be limited to 300 mA. Therefore, a single-phase bidirectional and transformerless PFC with common-mode leakage current suppression technologies needs to be used for low-power servo motor application.

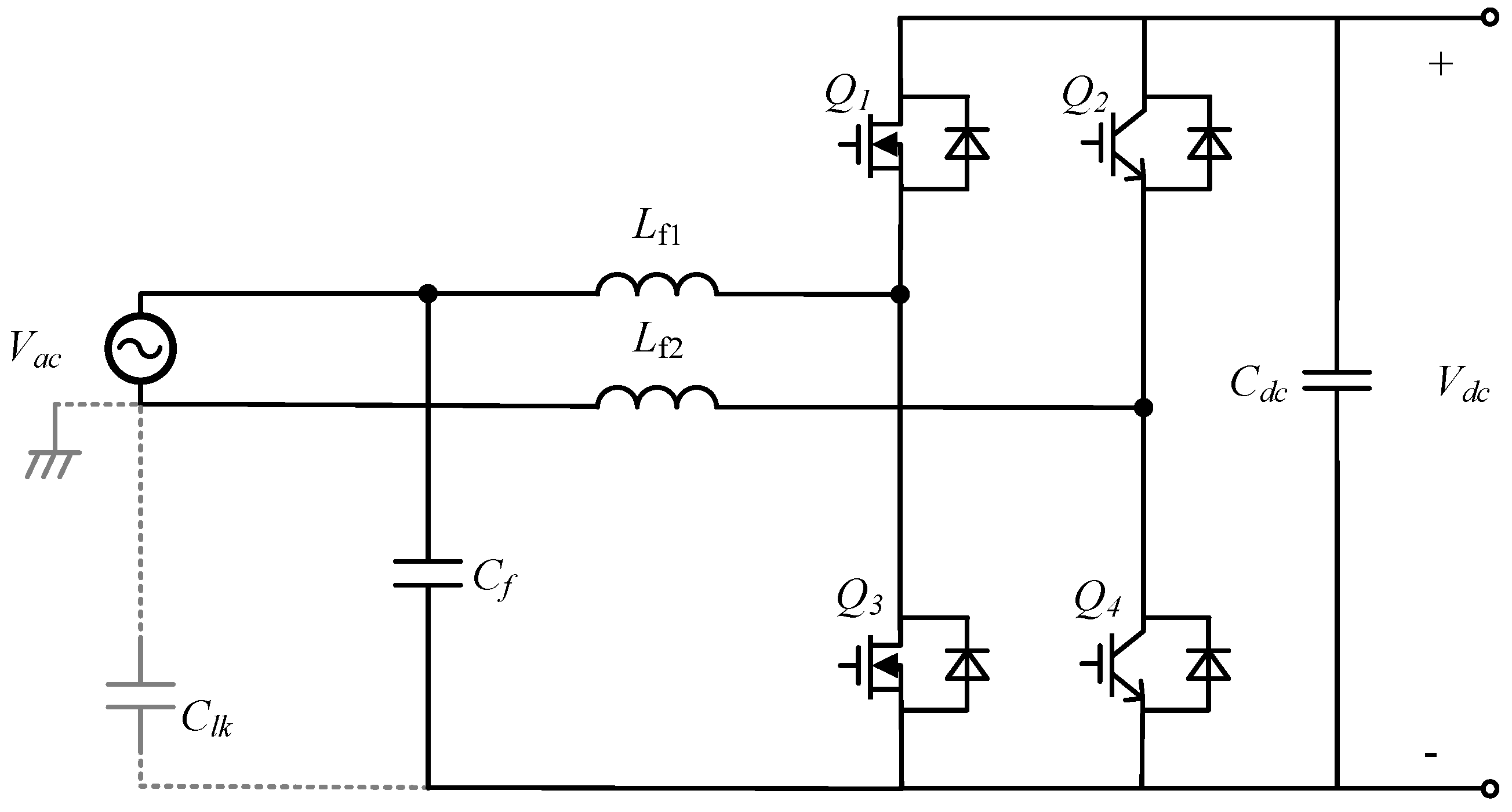

2. Analysis of Operating Principle

2.1. Operation Pattern

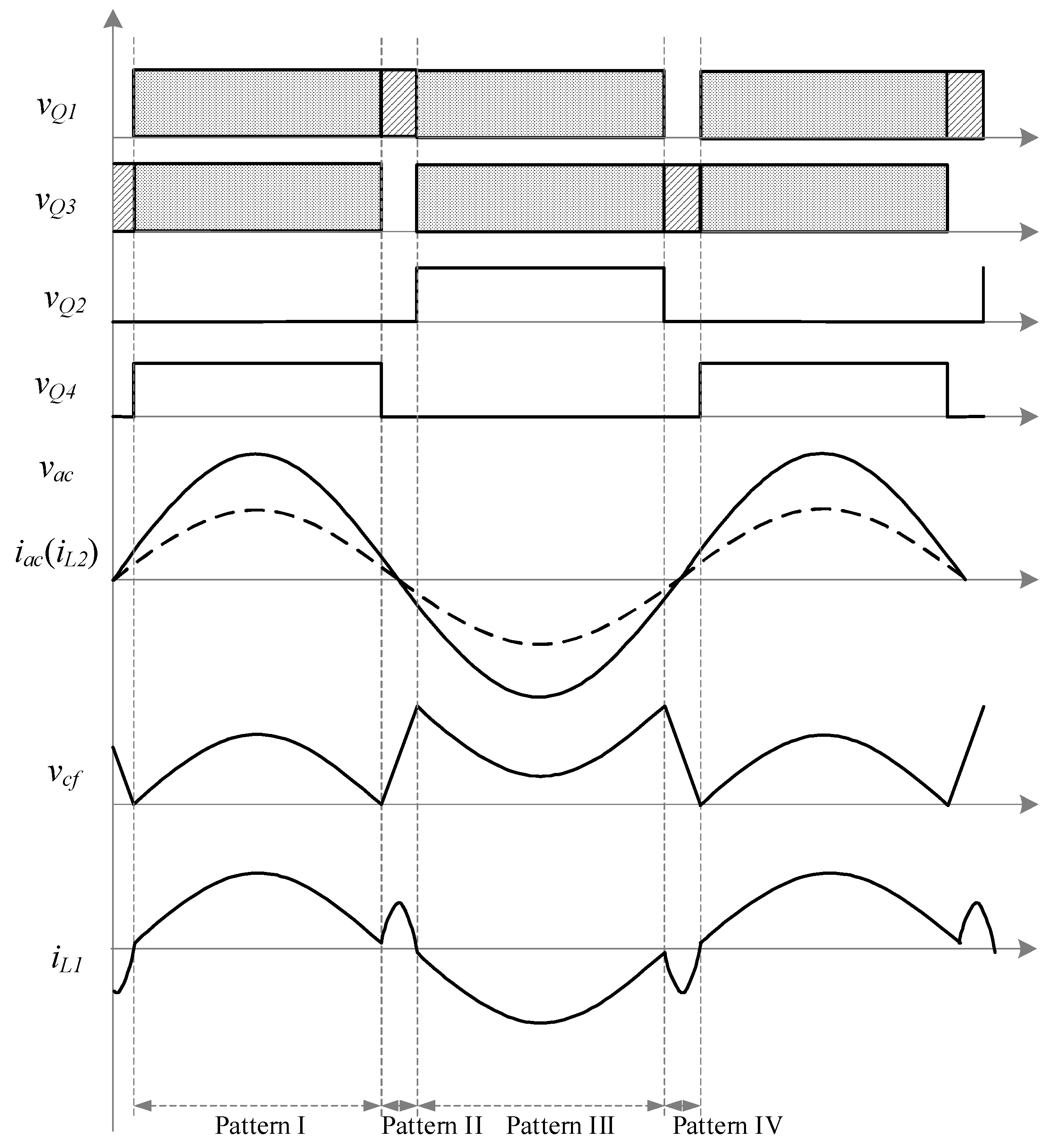

- (1)

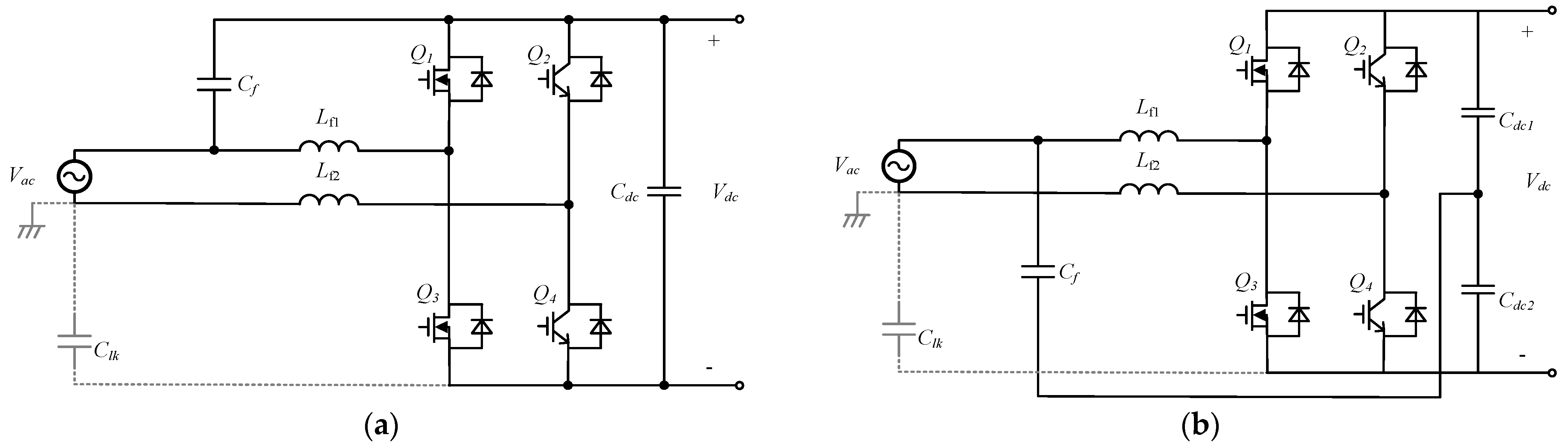

- Pattern I: Switches Q1 and Q3 are switching complementarily with high frequency, and switch Q4 is constantly in the ON state when the grid voltage is in the positive half cycle. The switching state of Pattern I is shown in Figure 4a. It can be observed that the middle voltage of the high-frequency leg is high-frequency switching voltage with magnitude changing between Vdc and zero, which creates large high-frequency current ripple. Due to the capacitor Cf, connecting the ac line terminal and the negative terminal of the DC-side, the LCL filter is configured with the inductors Lf1 and Lf2, which act as the converter-side inductor and the grid-side inductor, respectively. The equivalent circuit of this pattern is shown in Figure 5a. As a result, a significant reduction in the inductor current ripple will be realized. In addition, it can be observed that the stray Clk is in parallel with the capacitor Cf when the grid is assumed to be short-circuit because it can be regarded as a constant voltage source in the high-frequency analysis. The impedance in the capacitor Cf path is lower. Capacitor Cf couples the voltage between the terminal of the grid-side and the negative terminal of the DC-side, which clamps the voltage difference, and the ripple voltage on the capacitor Cf is small. Therefore, the common-mode leakage current flow of the stray capacitor Clk is minimized.

- (2)

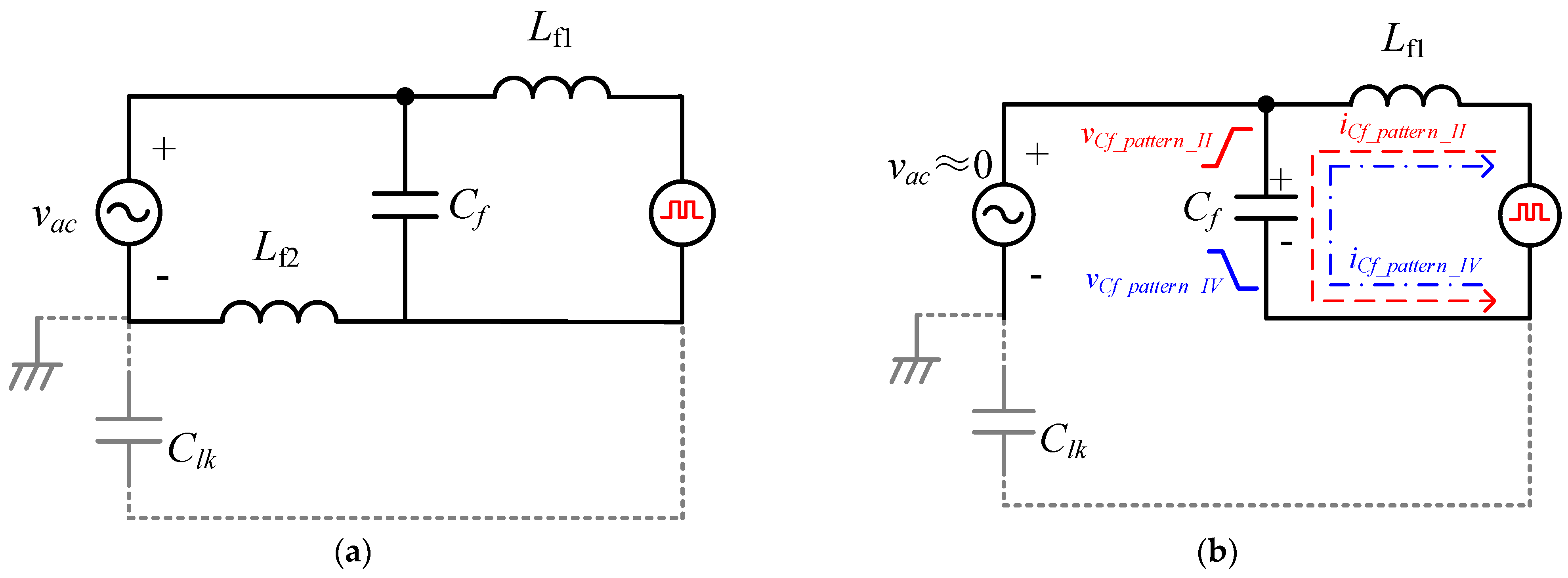

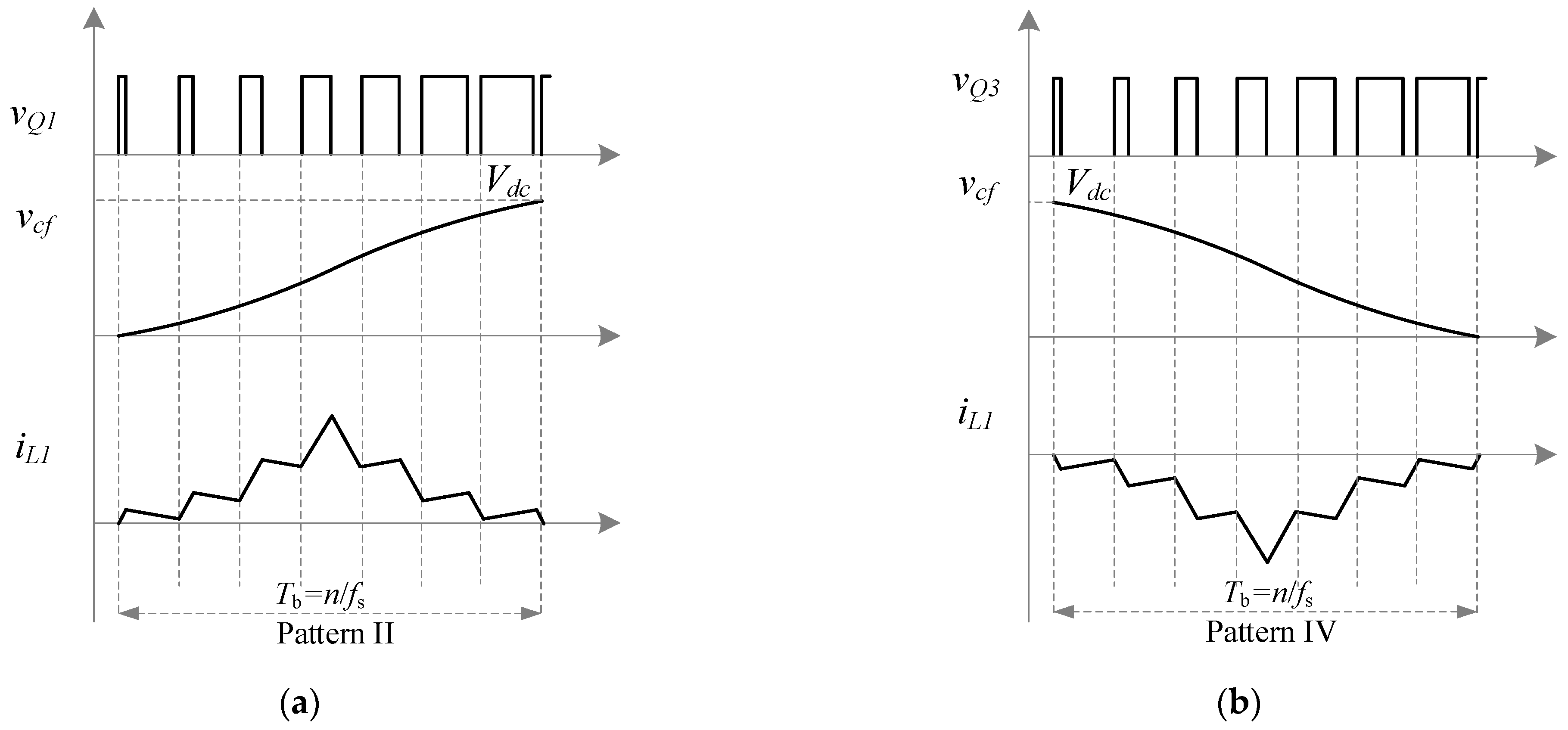

- Pattern II: Switches Q2 and Q4 are in the OFF state, switch Q1 switches ON or OFF with high frequency when the grid voltage zero-crossing point transitions from positive to negative. Switch Q3 acts as the synchronous switch of D3. The switching state of Pattern II is shown in Figure 4b. The reason for this pattern is that the middle voltage of the low-frequency leg changes rapidly from zero to Vdc if switches Q2 and Q4 switchover fast, while the voltages on capacitor Cf and stray capacitor Clk are approximately zero, the voltage difference on which will lead to a large spike on the inductor current and leakage current, which is unwanted. In this pattern, a similar buck converter is formed by DC voltage Vdc, switch Q1, diode D3 (synchronous switch Q3), inductor Lf1, capacitor Cf and stray capacitor Clk. The equivalent circuit of this pattern is shown in Figure 5b. The voltages on capacitor Cf and stray capacitor Clk will be charged up slowly to suppress the appearance of the current spike.

- (3)

- Pattern III: Switches Q1 and Q3 are switching complementarily with high frequency, and switch Q2 is constantly in the ON state when the grid voltage in the negative half cycle. The switching state of Pattern III is shown in Figure 4c. Although the inductor Lf2 is changed to connect the positive terminal of the DC-side, the LCL filter is formed by capacitor Cf, inductors Lf1 and Lf2, which achieves the low inductor current ripple. The equivalent circuit of this pattern is also shown in Figure 5a. Additionally, capacitor Cf and stray capacitor Clk are in parallel, which achieves low common-mode leakage current.

- (4)

- Pattern IV: Switches Q2 and Q4 are in the OFF state, switch Q3 switches ON or OFF with high frequency when the grid voltage zero-crossing point transitions from negative to positive. Switch Q1 acts the synchronous switch of D1. The switching state of Pattern IV is shown in Figure 4d. If switches Q2 and Q4 switchover fast, the middle voltage of the low-frequency leg changes rapidly from Vdc to zero, while the voltages on capacitor Cf and stray capacitor Clk are approximately Vdc, the voltage difference on which will also lead to a large spike on the inductor current and leakage current. In this pattern, a similar boost converter is formed by capacitor Cf and stray capacitor Clk, inductor Lf1, switch Q3, diode D1 (synchronous switch Q1), and DC voltage Vdc. The equivalent circuit of this pattern is shown in Figure 5b. The voltages on capacitor Cf and stray capacitor Clk will be discharged slowly to suppress the appearance of the current spike.

2.2. Control Scheme

3. Characteristics Analysis

3.1. Duty Cycle

3.2. Current Ripple and Voltage Ripple of LCL Filter in Pattern I and Pattern III

3.3. Duty Cycle Fundamental Current of Inductor L1 in Pattern II and Pattern IV

3.4. Current Ripple and Voltage Ripple of LCL Filter in Pattern I and Pattern III

4. System Implementation

4.1. Topology Variants

4.2. System Implementation

4.3. Selection of Filter Components

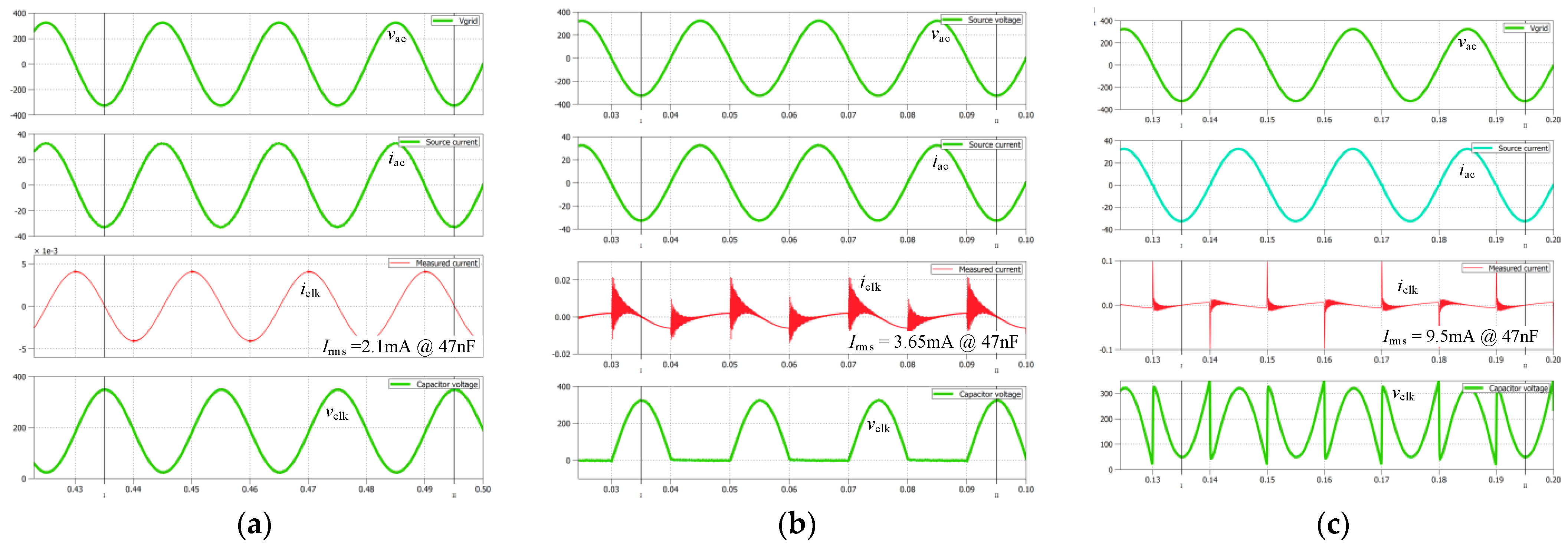

4.4. Simulation Verification

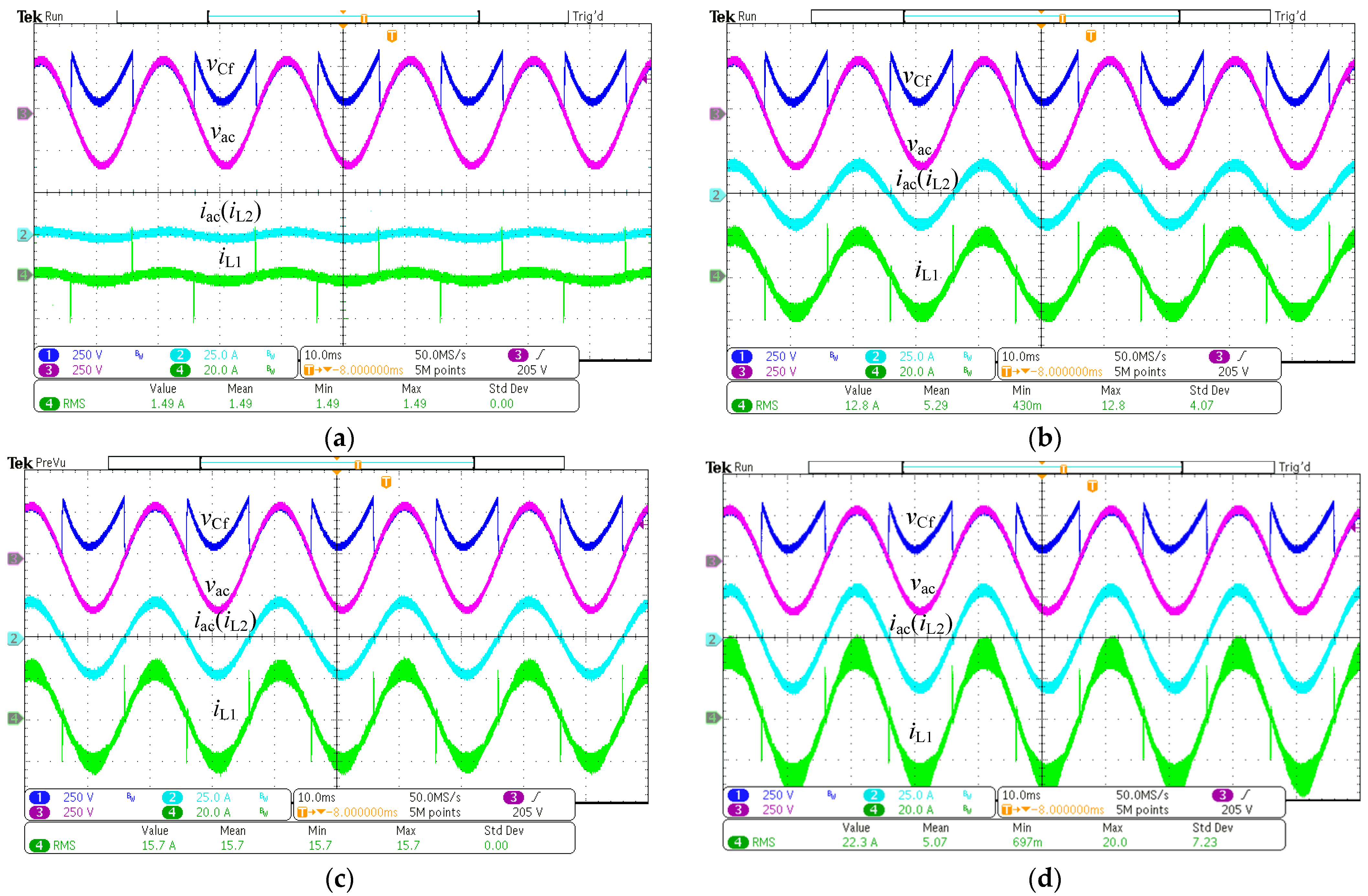

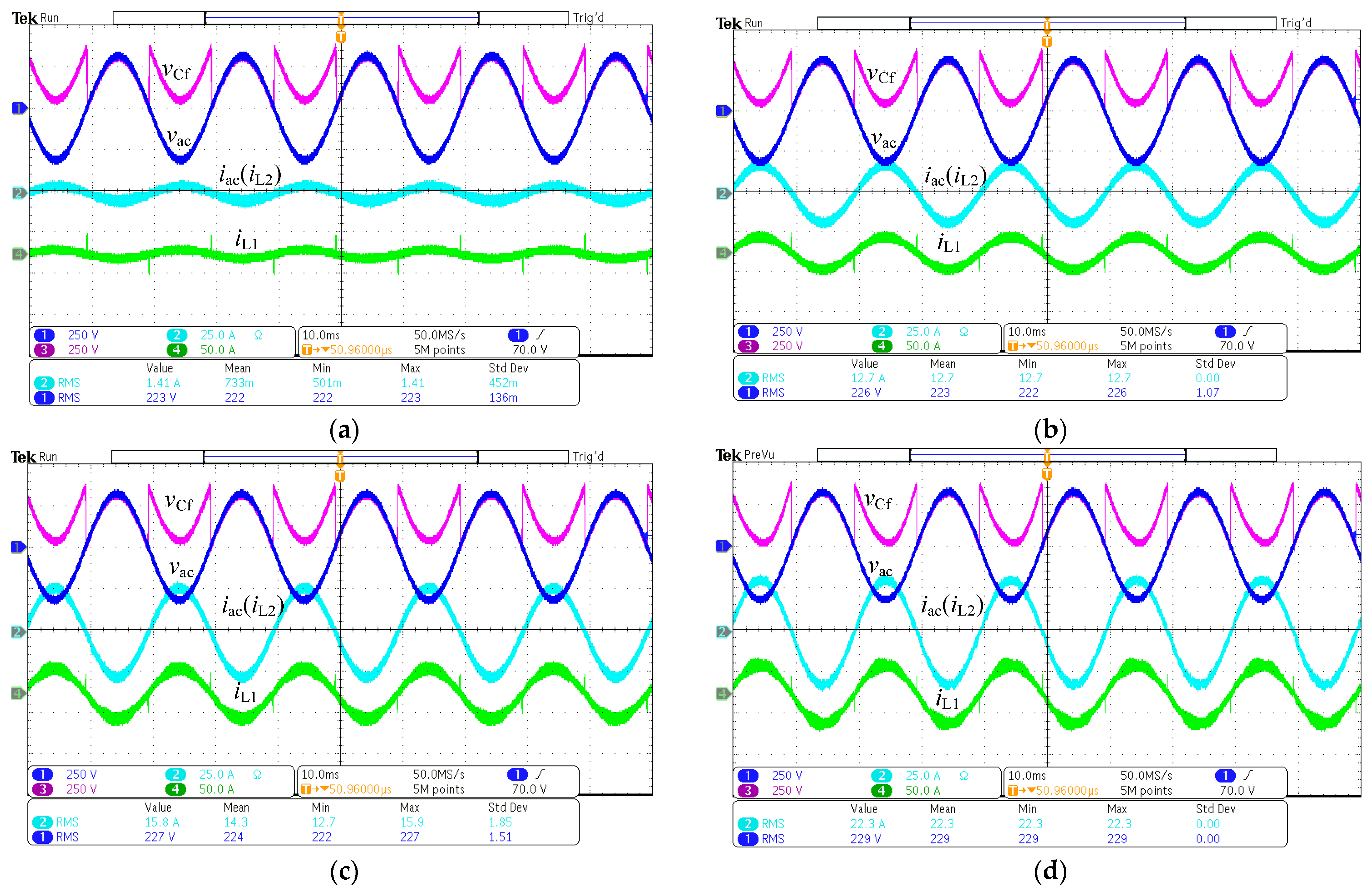

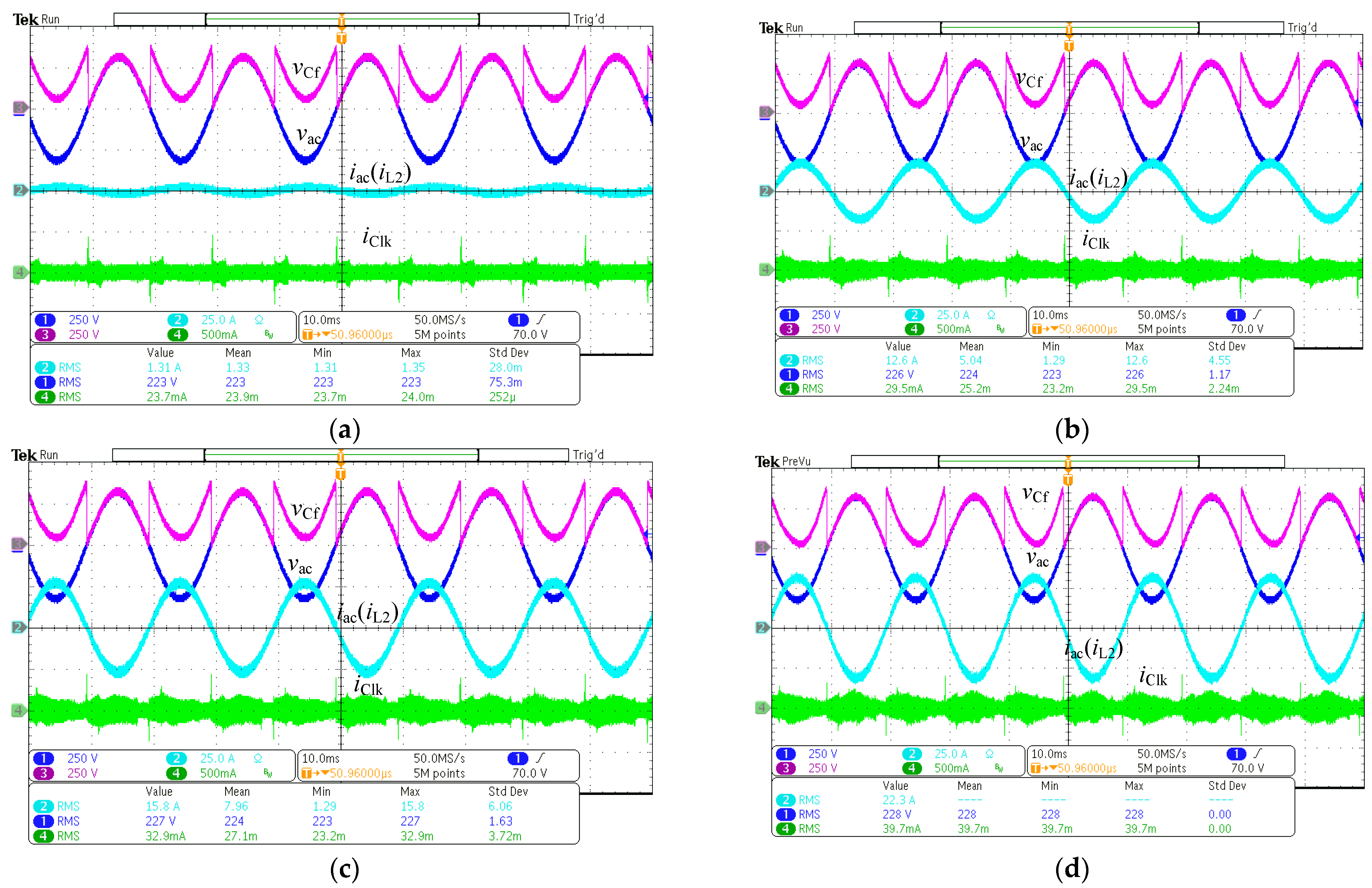

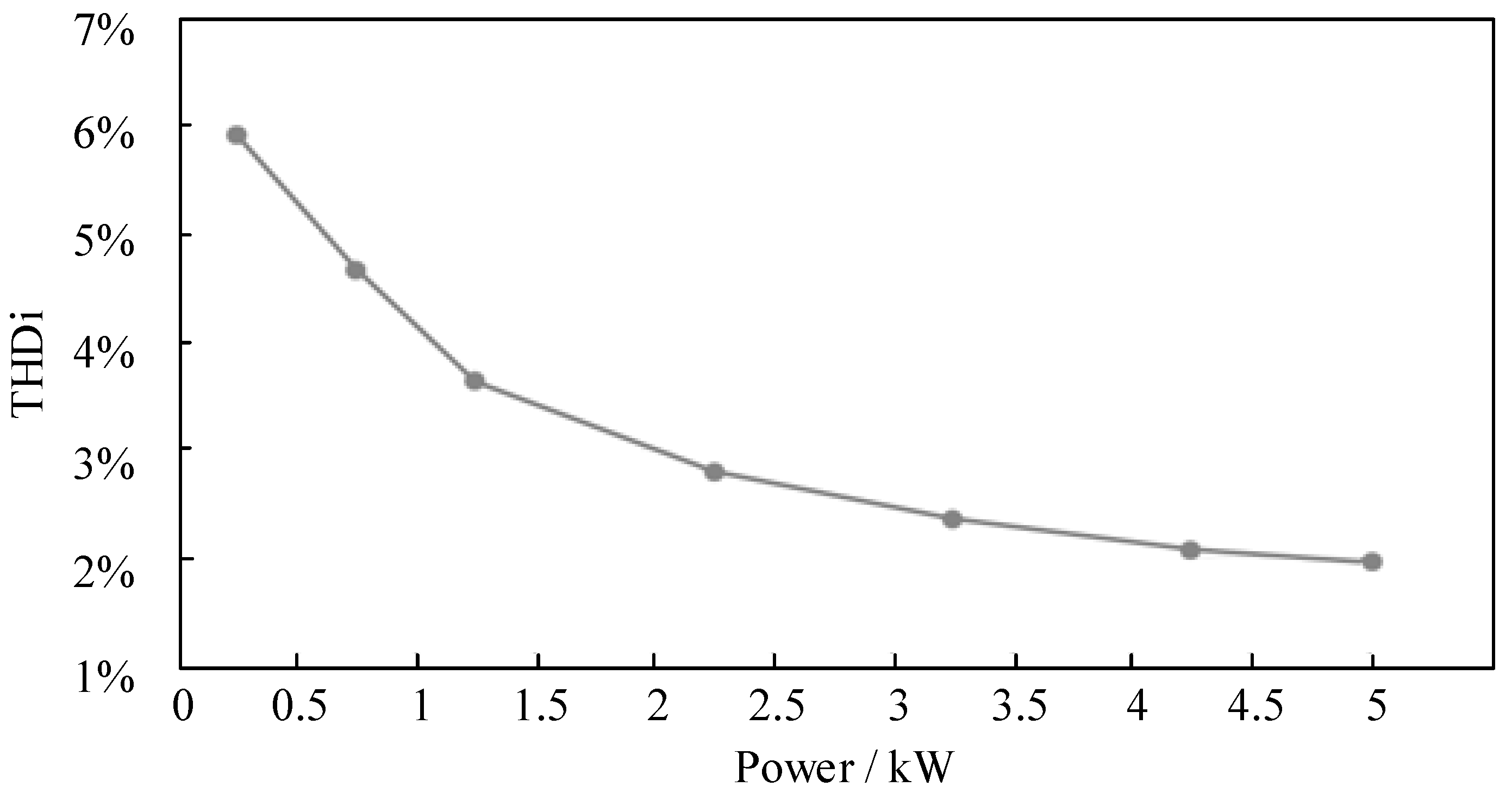

5. Experimental Verification

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Chen, F.; Burgos, R.; Boroyevich, D. A Bidirectional High-Efficiency Transformerless Converter with Common-Mode Decoupling for the Interconnection of AC and DC Grids. IEEE Trans. Power Electron. 2019, 34, 1317–1333. [Google Scholar] [CrossRef]

- Singh, S.M.; Gaurav, T.; Singh, H. PFC Cuk Converter Fed PMBLDC Motor for Ceiling Fan. In Proceedings of the 2021 International Conference on Communication, Control and Information Sciences (ICCISc), Idukki, India, 16–18 June 2021; pp. 1–5. [Google Scholar]

- Liu, J.; Tian, H.; Liang, G.; Zeng, J. A bridgeless electrolytic capacitor-free LED driver based on series-resonant converter with constant frequency control. IEEE Trans. Power Electron. 2019, 34, 2712–2725. [Google Scholar] [CrossRef]

- Strothmann, B.; Schafmeister, F.; Bocker, J. Common-Mode-Free Bidirectional Three-Phase PFC-Rectifier for Non-Isolated EV Charger. In Proceedings of the 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), Phoenix, AZ, USA, 14–17 June 2021; pp. 2783–2790. [Google Scholar]

- Fernandes, L.G.; Badin, A.A.; Cortez, D.F.; Gules, R.; Romaneli, E.F.R.; Assef, A. Transformerless UPS System Based on the Half-Bridge Hybrid Switched-Capacitor Operating as AC–DC and DC–DC Converter. IEEE Trans. Ind. Electron. 2021, 68, 2173–2183. [Google Scholar] [CrossRef]

- Siu, K.K.M.; Ho, C.N.M. A critical review of Bridgeless PFC boost rectifiers with common-mode voltage mitigation. In Proceedings of the IECON 2016—42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, Italy, 23–26 October 2016; pp. 3654–3659. [Google Scholar]

- Sun, Y.; Liu, Y.; Su, M.; Xiong, W.; Yang, J. Review of active power decoupling topologies in single-phase systems. IEEE Trans. Power Electron. 2016, 31, 4778–4794. [Google Scholar] [CrossRef]

- Tian, H.; Chen, M.; Liang, G.; Xiao, X. Single-Phase Rectifier with Reduced Common-Mode Current, Auto-PFC, and Power Decoupling Ability. IEEE Trans. Power Electron. 2022, 37, 6873–6882. [Google Scholar] [CrossRef]

- Siu, K.K.M.; Ho, C.N.M.; Li, R.T.H. A Four-Quadrant Single-Phase Grid-Connected Converter with Only Two High-Frequency Switches. IEEE Trans. Ind. Electron. 2020, 67, 1899–1909. [Google Scholar] [CrossRef]

- DIN VDE V 0126-1-1; Automatic Disconnection Device between a Generator and the Public Low Voltage Grid. VDE: Berlin, Germany, 2006.

- IEC Standard 61008-1-2010; Residual Current Operated Circuit-Breakers without Integral Overcurrent Protection for Household and Similar Uses (RCCBs)—Part 1: General Rules. IEC: Geneva, Switzerland, 2010.

- IEC Standard 62109-1-2007; Safety of Power Converters for Use in Photovoltaic Power Systems—Part 1: General Requirement. IEC: Geneva, Switzerland, 2007.

- Vosoughi, N.; Hosseini, S.H.; Sabahi, M. A New Single-Phase Transformerless Grid-Connected Inverter with Boosting Ability and Common Ground Feature. IEEE Trans. Ind. Electron. 2020, 67, 9313–9325. [Google Scholar] [CrossRef]

- Peng, F.; Zhou, G.; Xu, N.; Gao, S. Zero Leakage Current Single-Phase Quasi-Single-Stage Transformerless PV Inverter with Unipolar SPWM. IEEE Trans. Power Electron. 2022, 37, 13755–13766. [Google Scholar] [CrossRef]

- Xiao, H.F.; Lan, K.; Zhang, L. A quasi-unipolar SPWM full-bridge transformerless PV grid-connected inverter with constant common-mode voltage. IEEE Trans. Power Electron. 2015, 30, 3122–3132. [Google Scholar] [CrossRef]

- Do, N.; Huang, B.; Nguyen, T.; Wu, J.; Liu, Y.; Chiu, H. An Efficiency-Optimized Totem-pole Bridgeless Power Factor Correction Regulator using GaN HEMTs. In Proceedings of the 2020 International Symposium on Computer, Consumer and Control (IS3C), Taichung City, Taiwan, 13–16 November 2020; pp. 351–355. [Google Scholar]

- Yang, B.; Li, W.; Gu, Y.; Cui, W.; He, X. Improved transformerless inverter with common-mode leakage current elimination for a photovoltaic grid-connected power system. IEEE Trans. Power Electron. 2012, 27, 752–762. [Google Scholar] [CrossRef]

- Fan, J.; Yeung, R.; Chung, H. Optimized hybrid PWM scheme for mitigating zero-crossing distortion in totem-pole bridgeless PFC. IEEE Trans. Power Electron. 2019, 34, 928–942. [Google Scholar] [CrossRef]

- Victor, M.; Greizer, F.; Bremicker, S.; Hubler, U. Method of Converting a Direct Current Voltage from a Source of Direct Current Voltage, more Specifically from a Photovoltaic Source of Direct Current Voltage, into a Alternating Current Voltage. U.S. Patent US7411802 B2, 12 August 2008. [Google Scholar]

- Freddy, T.K.S.; Lee, J.; Moon, H.-C.; Lee, K.-B.; Rahim, N.A. Modulation technique for single-phase transformerless photovoltaic inverters with reactive power capability. IEEE Trans. Ind. Electron. 2017, 64, 6989–6999. [Google Scholar] [CrossRef]

- Liu, B.; Su, M.; Yang, J.; Song, D.; He, D.; Song, S. Combined Reactive Power Injection Modulation and Grid Current Distortion Improvement Approach for H6 Transformer-Less Photovoltaic Inverter. IEEE Trans. Energy Convers. 2017, 32, 1456–1467. [Google Scholar] [CrossRef]

- Rahman, M.M.; Hossain, M.S.; Talukder, M.S.I.; Uddin, M.N. Transformerless Six-Switch (H6)-Based Single-Phase Inverter for Grid-Connected Photovoltaic System with Reduced Leakage Current. IEEE Trans. Ind. Appl. 2021, 58, 974–985. [Google Scholar] [CrossRef]

- Tang, Z.; Su, M.; Sun, Y.; Cheng, B.; Yang, Y.; Blaabjerg, F.; Wang, L. Hybrid UP-PWM Scheme for HERIC Inverter to Improve Power Quality and Efficiency. IEEE Trans. Power Electron. 2019, 34, 4292–4303. [Google Scholar] [CrossRef]

- Schmidt, H.; Siedle, C.; Ketterer, J. DC/AC Converter to Convert Direct Electric Voltage into Alternating Voltage or into Alternating Current. U.S. Patent US7046534 B2, 16 May 2006. [Google Scholar]

- Ho, C.N.M.; Li, R.T.-H.; Siu, K.K.-M. Active Virtual Ground—Bridgeless PFC Topology. IEEE Trans. Power Electron. 2017, 32, 6206–6218. [Google Scholar] [CrossRef]

- Ho, R.; Li, C.; Chen, E. Active virtual ground—Single-phase transformerless grid-connected voltage source inverter topology. IEEE Trans. Power Electron. 2018, 33, 1335–1346. [Google Scholar]

- Wang, S.; Kong, P.; Lee, F.C. Common mode noise reduction for boost converters using general balance technique. IEEE Trans. Power Electron. 2007, 22, 1410–1416. [Google Scholar] [CrossRef]

- Zhu, X.; Wang, H.; Zhang, W.; Wang, H.; Deng, X.; Yue, X. A Single-Phase Five-Level Transformer-Less PV Inverter for Leakage Current Reduction. IEEE Trans. Ind. Electron. 2022, 69, 3546–3555. [Google Scholar] [CrossRef]

- Xie, L.; Yuan, X. Common-Mode Current Reduction at DC and AC Sides in Inverter Systems by Passive Cancellation. IEEE Trans. Power Electron. 2021, 36, 9069–9079. [Google Scholar] [CrossRef]

| Parameters | Values |

|---|---|

| DC voltage | 370 V |

| Grid voltage | 230 V |

| Grid frequency | 50 Hz |

| Power | 5 kW |

| Switching frequency | 60 kHz |

| Blank Time of Pattern II or IV | 120 μs |

| Stray Capacitor | 47 nF |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liang, M.; Jia, P.; Guo, T. Analysis of a Single-Phase Transformerless Bidirectional PFC. Energies 2022, 15, 8329. https://doi.org/10.3390/en15228329

Liang M, Jia P, Guo T. Analysis of a Single-Phase Transformerless Bidirectional PFC. Energies. 2022; 15(22):8329. https://doi.org/10.3390/en15228329

Chicago/Turabian StyleLiang, Mei, Pengyu Jia, and Tengfei Guo. 2022. "Analysis of a Single-Phase Transformerless Bidirectional PFC" Energies 15, no. 22: 8329. https://doi.org/10.3390/en15228329

APA StyleLiang, M., Jia, P., & Guo, T. (2022). Analysis of a Single-Phase Transformerless Bidirectional PFC. Energies, 15(22), 8329. https://doi.org/10.3390/en15228329