Development and Control of a Switched Capacitor Multilevel Inverter

Abstract

:1. Introduction

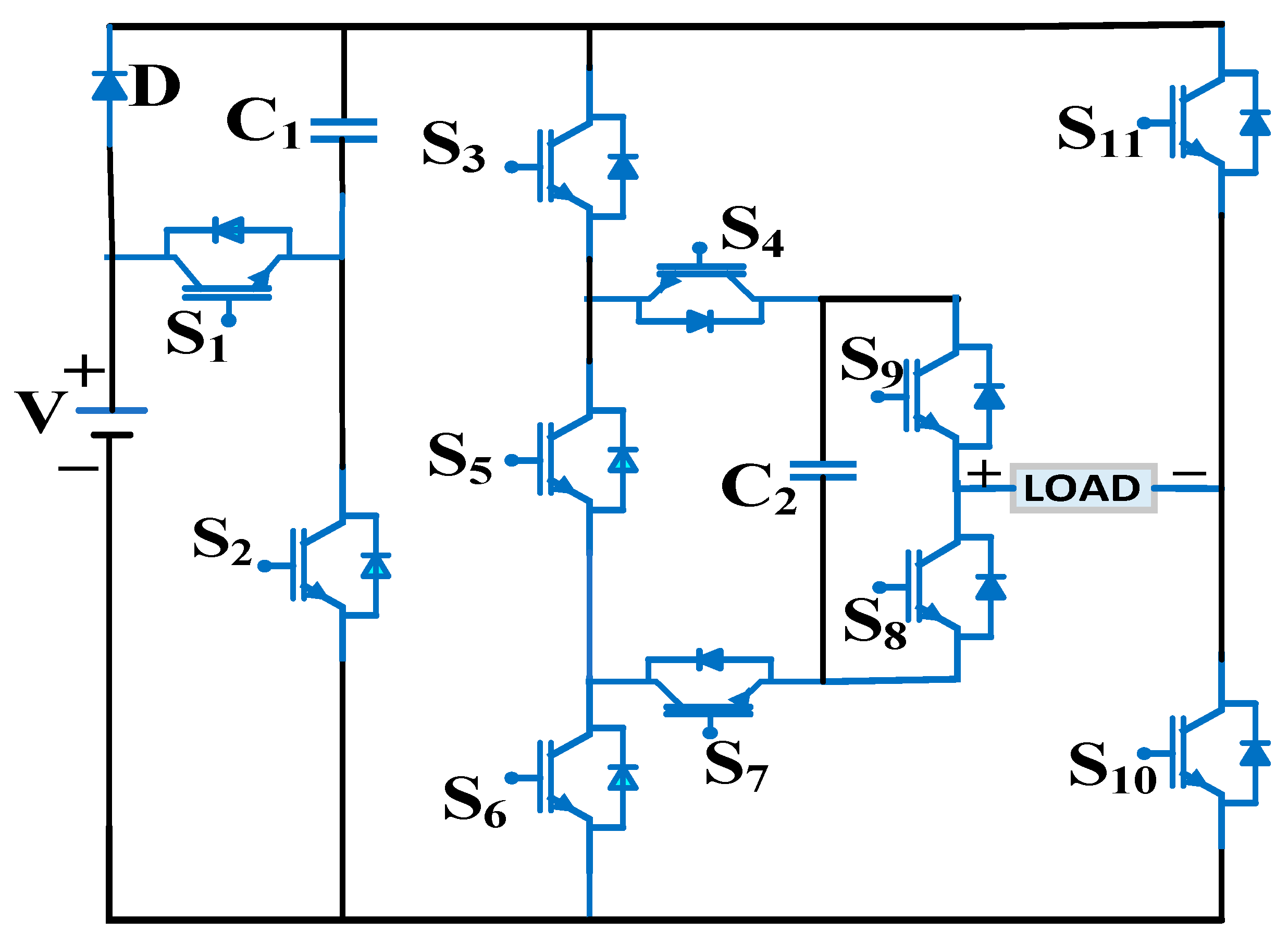

2. Specifics of Proposed Topology

2.1. Configuration of Proposed Topology

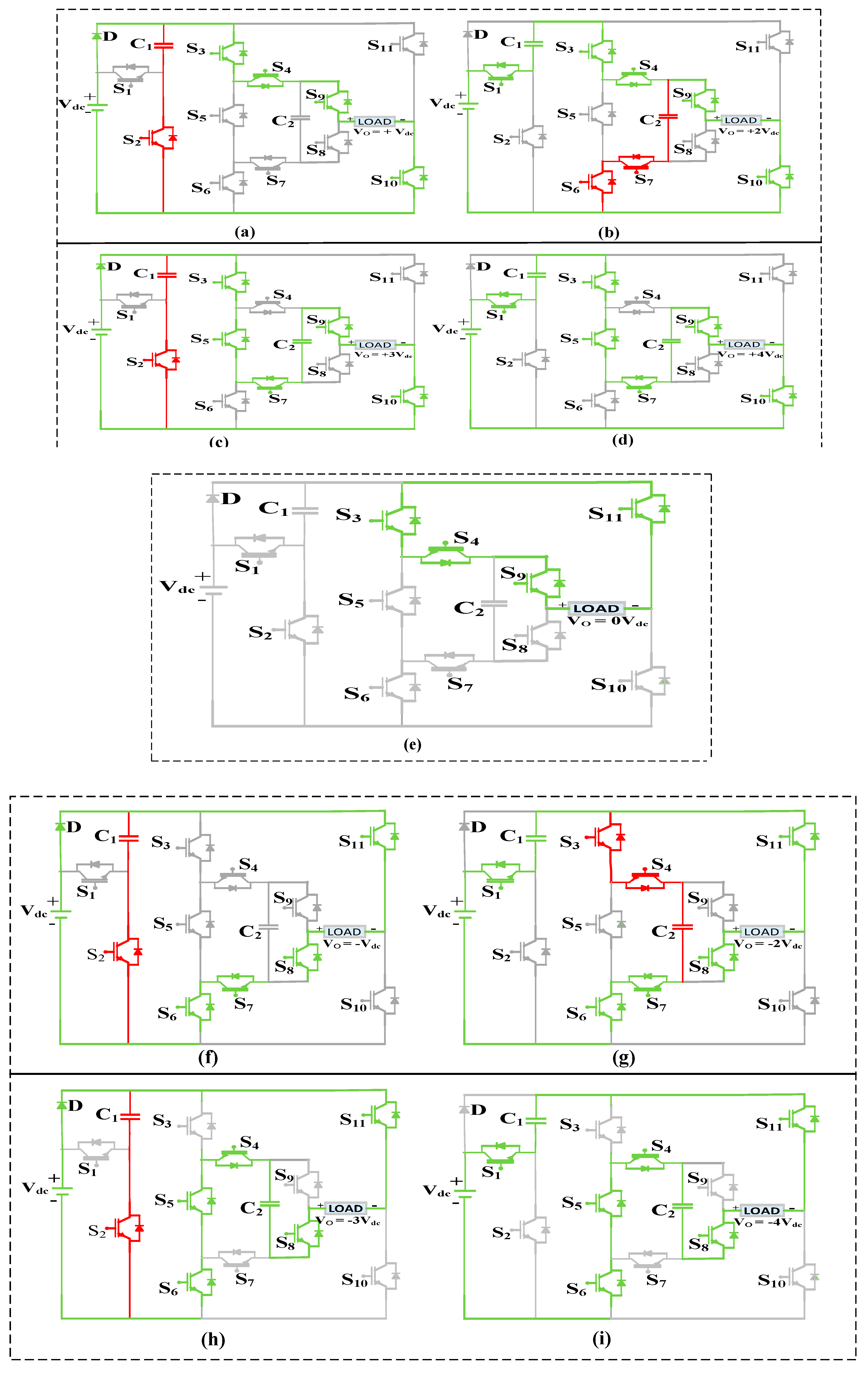

- Level 1: +Vdc output level is produced in this mode. , , , and switches are in the ON state in Figure 2a, while every other switch are in the OFF state. Powered by stored energy in C1, switch is ON.

- Level 2: In this mode, an output level of +2 Vdc is produced. The , , , , and switches are ON, while all other switches are OFF, as illustrated in Figure 2b. As the voltage source and capacitors C1 and C2 become parallel, switches and are turned ON to access the energy storage in C2. There is a 2 Vdc charge on the capacitor C2. The voltage source provides the load with the necessary energy via the capacitor C1 in series.

- Level 3: The output level of this mode is +3 Vdc. As seen in Figure 2c, the , , , , and switches are ON while the other switches are OFF. By switching , the C1’s accumulated energy is turned on. The DC input source is linked in parallel with C1’s capacitor. The load receives the required amount of energy from the voltage source linked in series with C2.

- Level 4: An output level of +4 Vdc is the result. With the exception of the , , , and switches, all other switches are in the OFF state. The load is now connected in series with the capacitors C2, C1, and the SC source, as indicated in Figure 2d, providing the load with the energy it needs.

- Level 5: The output level of this mode is 0 Vdc. As shown in Figure 2e, all switches in this configuration, with the exception of , , , and , are in the off position. The voltage across the load is 0 volts because there isn’t a DC supply.

- Level 6: The output level of this mode is −Vdc. As seen in Figure 2f, the switches , , , and are ON while the other switches are OFF. Switch is ON and powered by energy stored in C1.

- Level 7: The mode’s level of output is −2 Vdc. As seen in Figure 2g, only the , , , , and switches are active while every other switch is off. Switches and are switched ON to access the capacitor C2’s stored energy when it enters parallel with the voltage source and capacitor C1. The capacitor C2 is charged to a voltage of 2 Vdc. The energy for the load is given by the voltage source coupled in series with a capacitor.

- Level 8: This mode produces an output level of −3 Vdc. The , , , , and switches are ON, while all other switches are OFF, as illustrated in Figure 2h. The stored energy in C1 is activated via switch . The DC input source is linked in parallel with the C1 capacitor. The load is powered by the voltage source connected in series with C2.

- Level 9: The output level of this mode is −4 Vdc. With the exception of the , , , , , and switches, all other switches are in the OFF state. To provide the load with the energy it requires, the capacitors C2, C1, and the DC source are linked in series with the load. Figure 2i depicts the current trend.

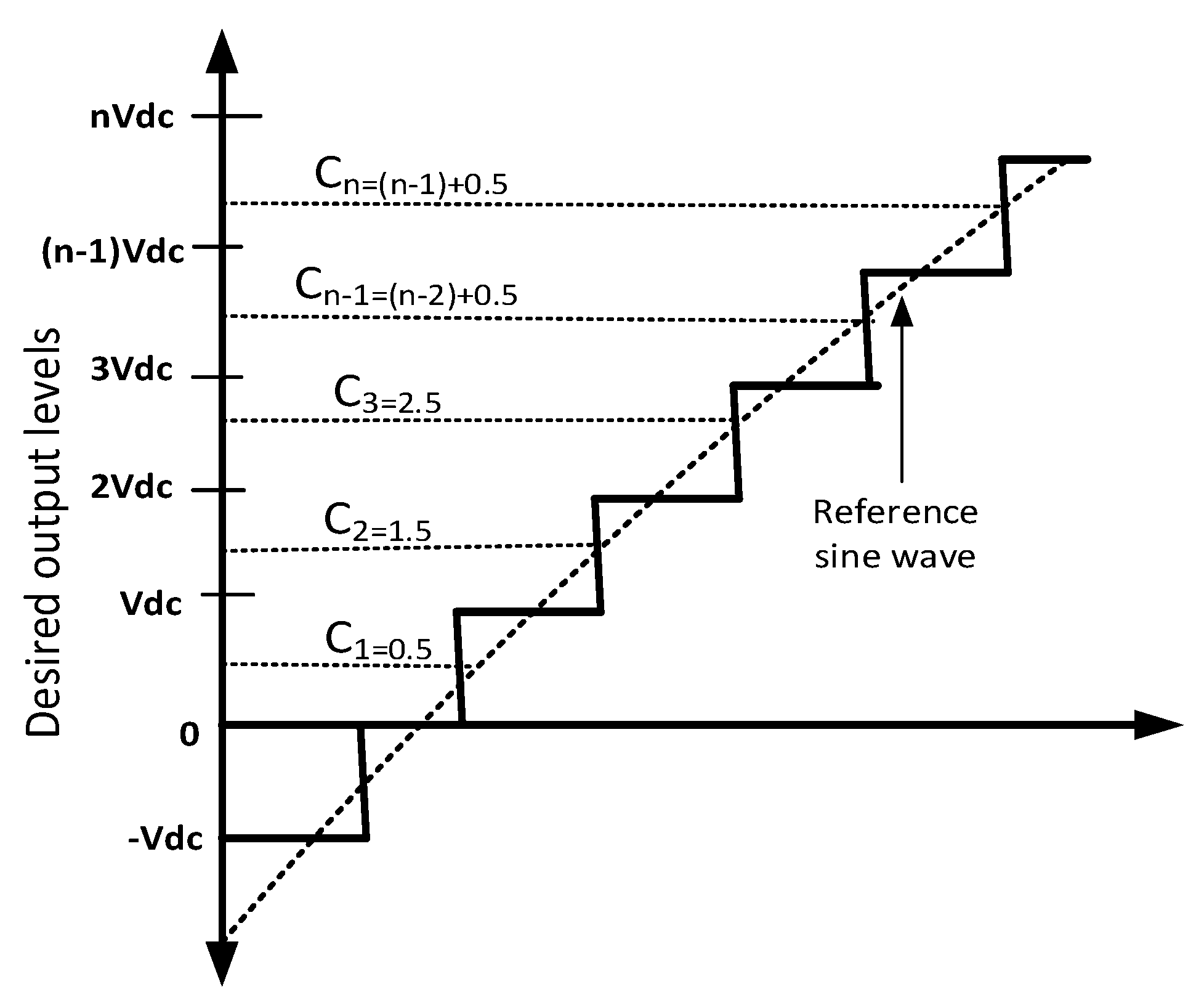

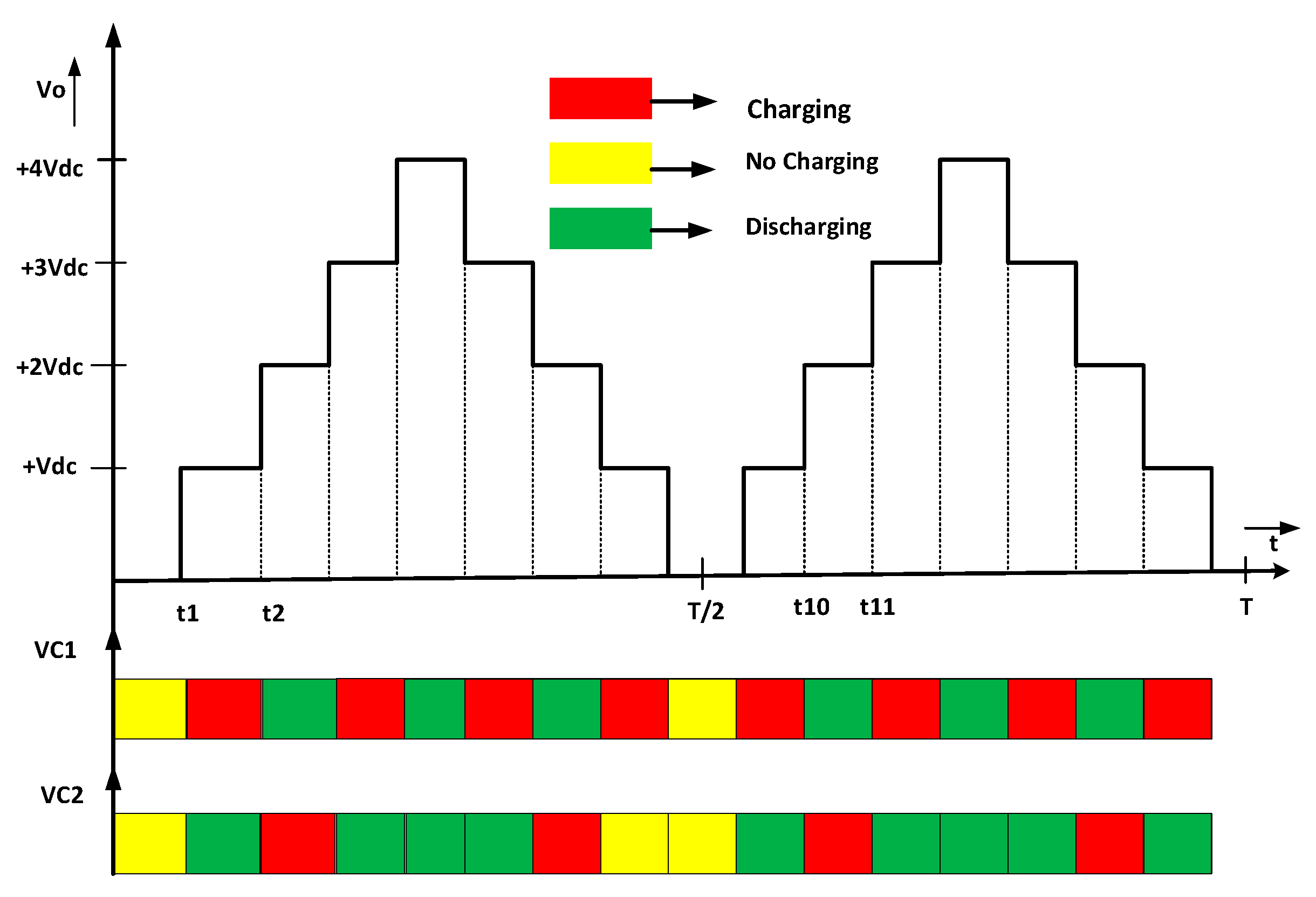

2.2. Nearest Level Control

3. Comparative Analysis

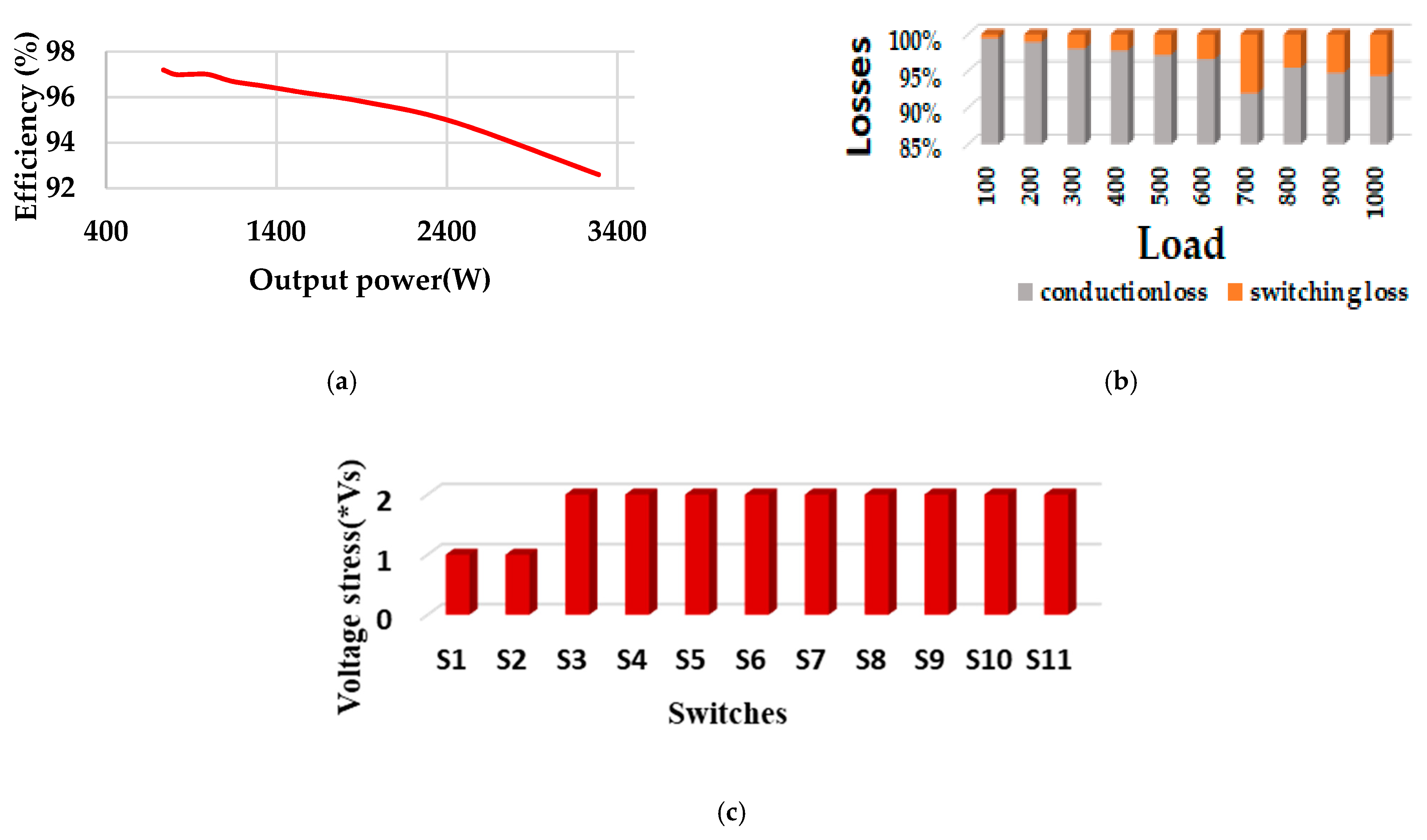

4. Power Loss Analysis

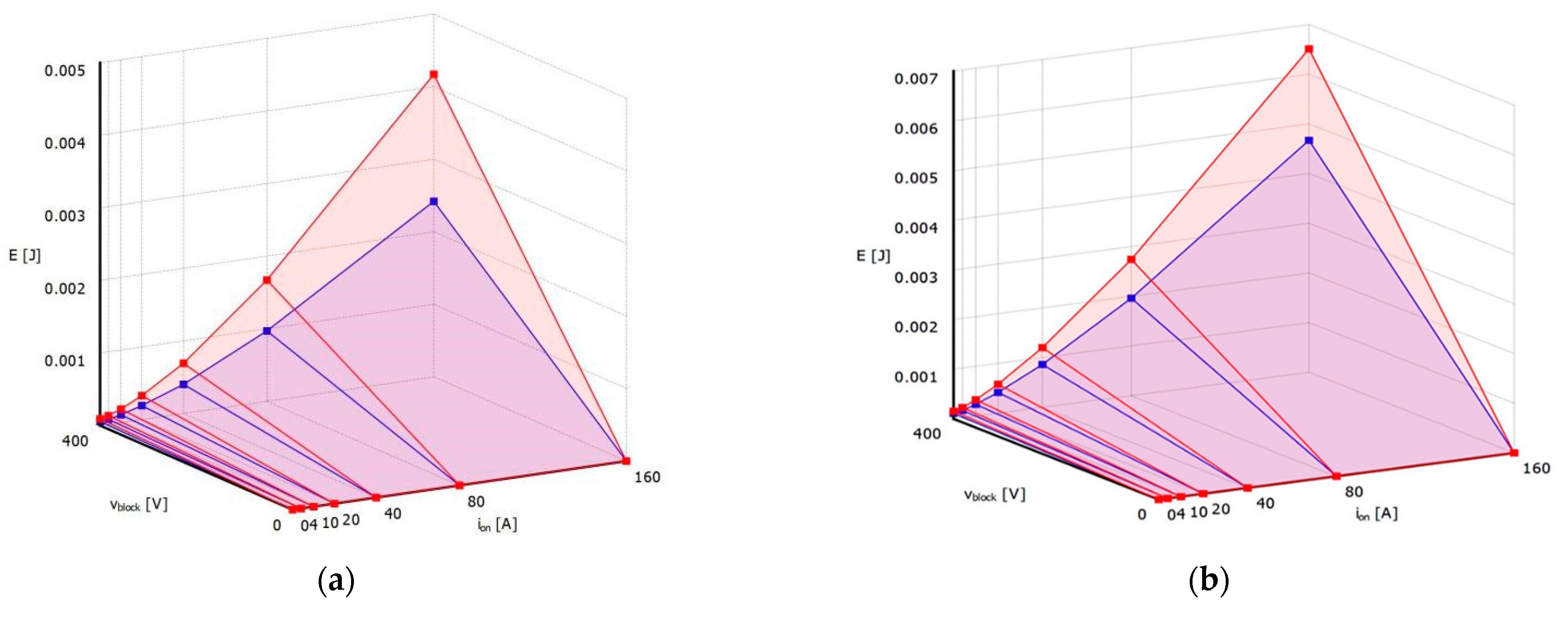

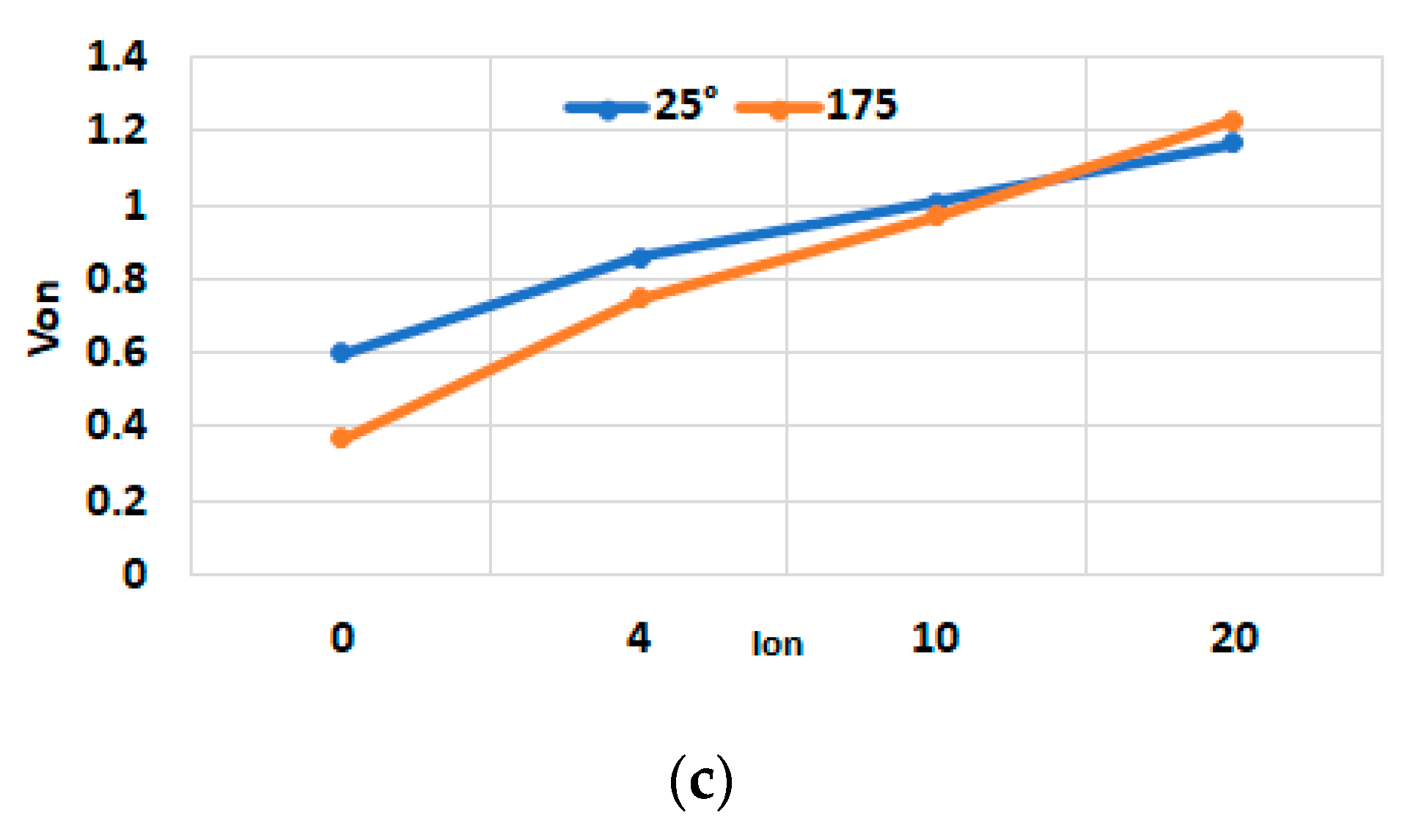

4.1. A-Switching Losses

4.2. B-Conduction Loss

4.3. Capacitor Selection

5. Result and Discussion

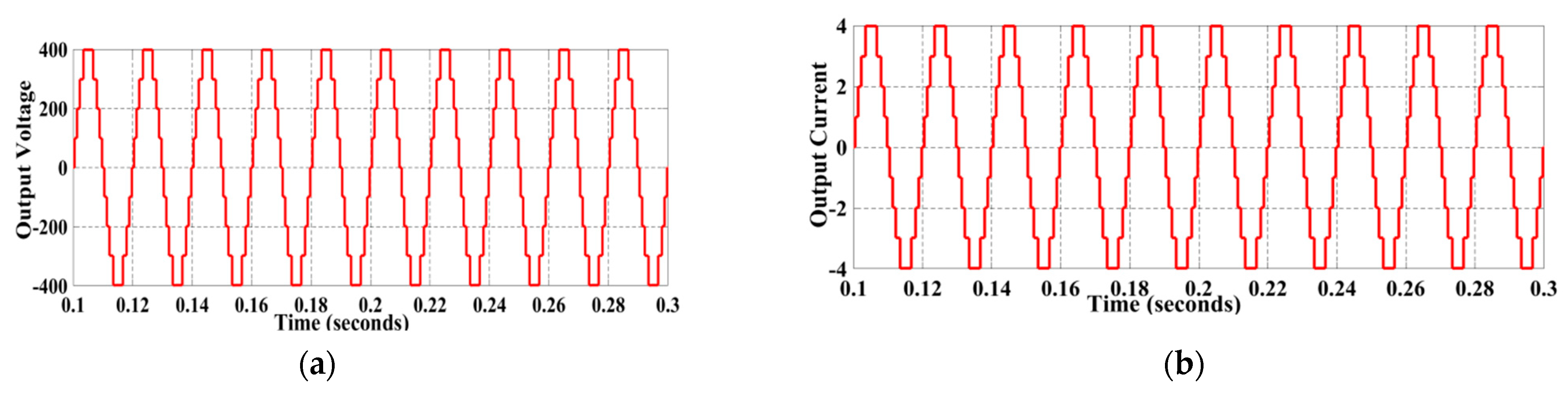

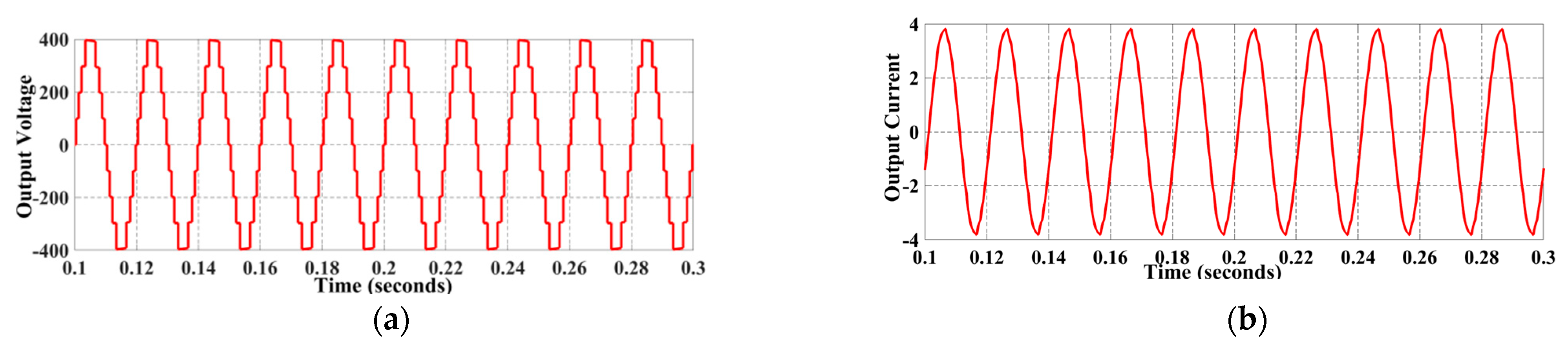

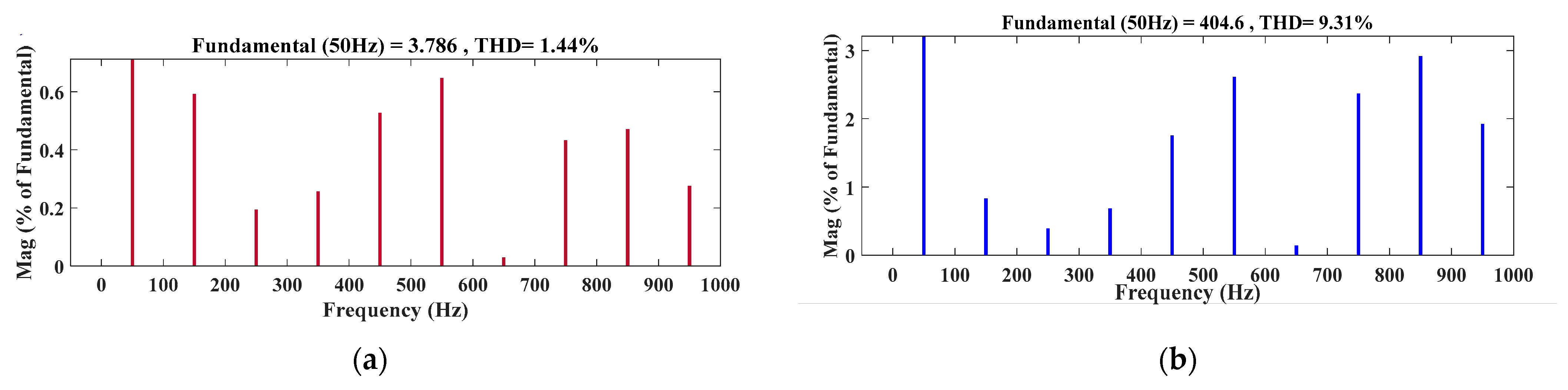

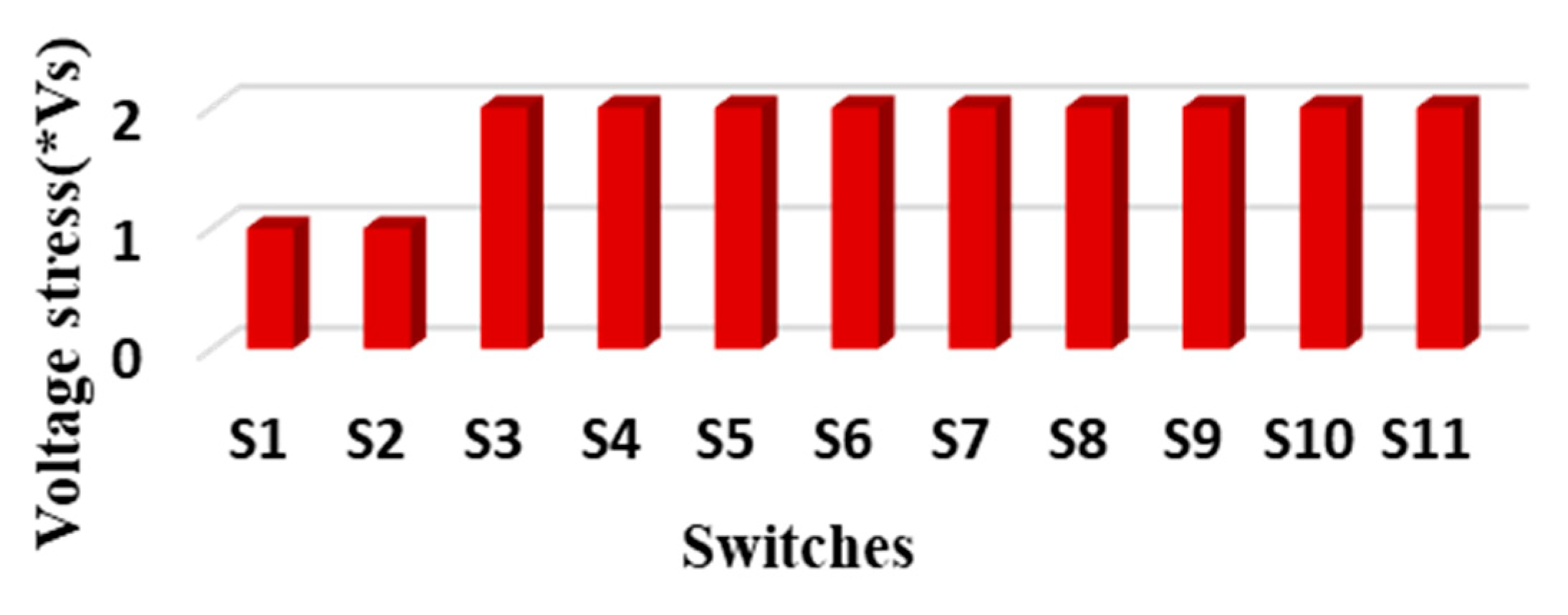

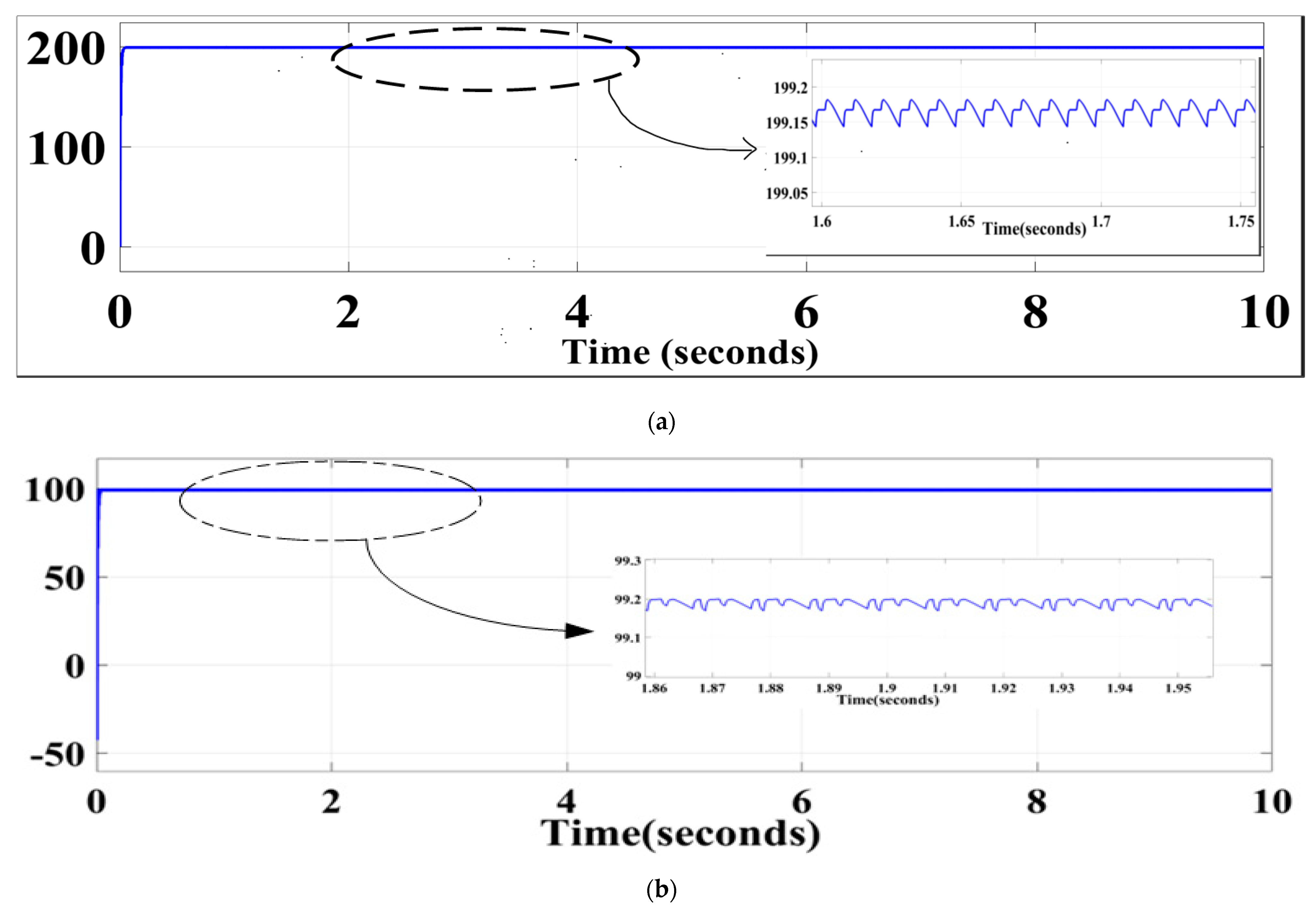

Simulation Result

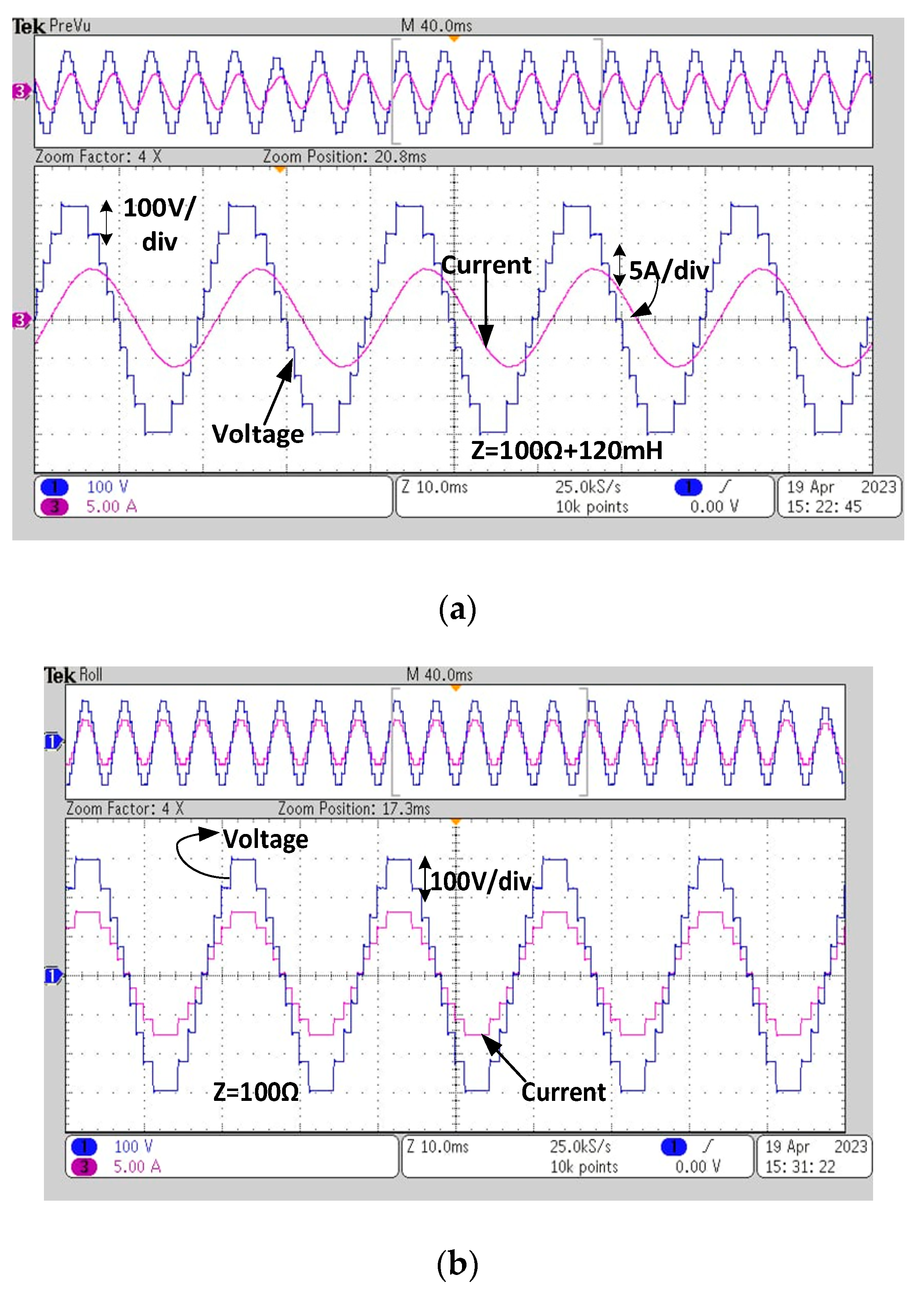

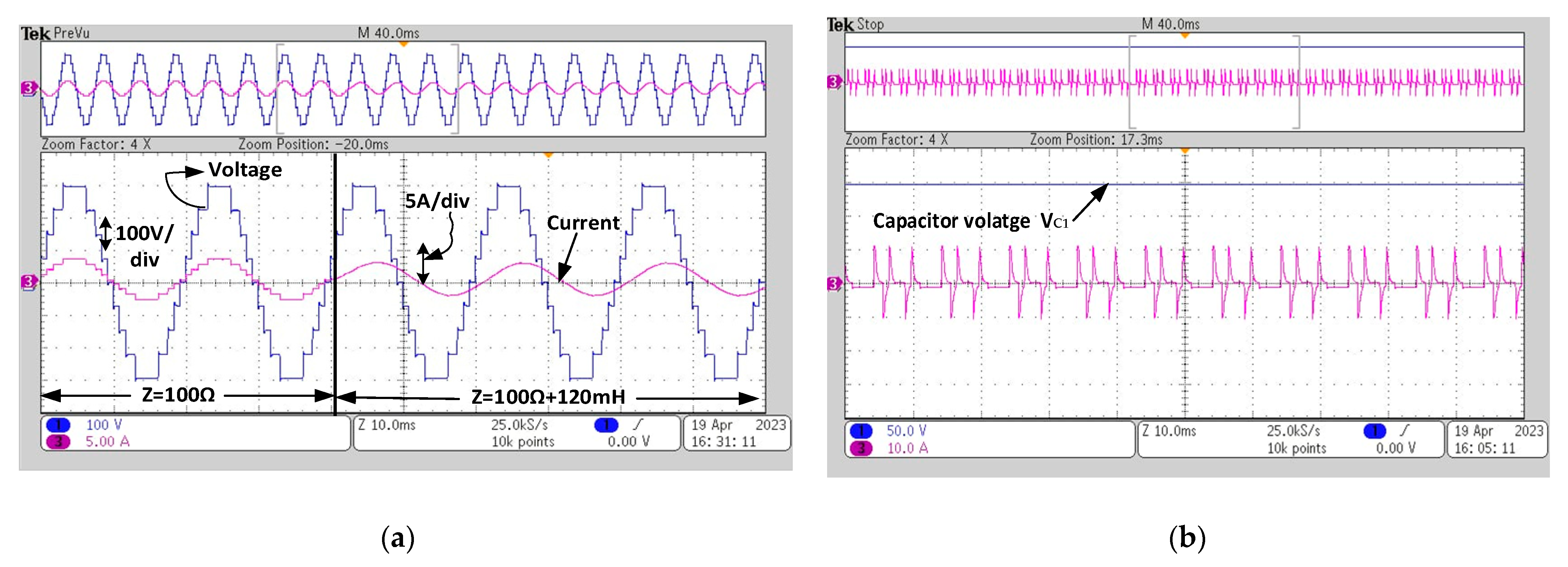

6. Experiment Result

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Emadi, A.; Williamson, S.S.; Khaligh, A. Power electronics intensive solutions for advanced electric, hybrid electric, and fuel cell vehicular power systems. IEEE Trans. Power Electron. 2006, 21, 567–577. [Google Scholar] [CrossRef]

- Jahan, H.K.; Abapour, M.; Zare, K. Switched-capacitor-based single-source cascaded H-bridge multilevel inverter featuring boosting ability. IEEE Trans. Power Electron. 2019, 34, 1113–1124. [Google Scholar] [CrossRef]

- Kumari, M.; Siddique, M.D.; Sarwar, A.; Mekhilef, S.; Tariq, M. A twice boost nine-level switched-capacitor multilevel (2B-9L-SCMLI) inverter with self-voltage balancing capability. Int. J. Circuit Theory Appl. 2021, 49, 2578–2592. [Google Scholar] [CrossRef]

- Khoun-Jahan, H.; Shotorbani, A.M.; Abapour, M.; Zare, K.; Hosseini, S.H.; Blaabjerg, F.; Yang, Y. Switched capacitor based cascaded half-bridge multilevel inverter with voltage boosting feature. In CPSS Transactions on Power Electronics and Applications; CPSS: Shenzhen, China, 2021; Volume 6, pp. 63–73. [Google Scholar] [CrossRef]

- Panda, K.P.; Babu, N.; Bisoyi, S.K.; Panda, G. Reduced Switch Quadruple Boost Switched-Capacitor based Multilevel Inverter. In Proceedings of the 2020 3rd International Conference on Energy, Power and Environment: Towards Clean Energy Technologies, Shillong, India, 5–7 March 2021; pp. 1–6. [Google Scholar] [CrossRef]

- Chakraborty, C.; Iu, H.H.C.; Lu, D.D.C. Power converters, control, and energy management for distributed generation. IEEE Trans. Ind. Electron. 2015, 62, 4466–4470. [Google Scholar] [CrossRef]

- Hussan, M.R.; Sarwar, A.; Khan, I.; Tariq, M.; Tayyab, M.; Alhosaini, W. An eleven-level switched-capacitor inverter with boosting capability. Electronics 2021, 10, 2262. [Google Scholar] [CrossRef]

- Siddique, M.D.; Mekhilef, S.; Shah, N.M.; Sarwar, A.; Iqbal, A.; Tayyab, M.; Ansari, M.K. Low switching frequency based asymmetrical multilevel inverter topology with reduced switch count. IEEE Access 2019, 7, 86374–86383. [Google Scholar] [CrossRef]

- Barzegarkhoo, R.; Moradzadeh, M.; Blaabjerg, F. A new boost switched-capacitor multilevel converter with reduced circuit devices. IEEE Trans. Power Electron. 2018, 33, 6738–6754. [Google Scholar] [CrossRef]

- Hinago, Y.; Koizumi, H. A switched-capacitor inverter using series/parallel conversion with inductive load. IEEE Trans. Ind. Electron. 2012, 59, 878–887. [Google Scholar] [CrossRef]

- Taghvaie, A.; Adabi, J.; Rezanejad, M. A self-balanced step-up multilevel inverter based on switched capacitor structure. IEEE Trans. Power Electron. 2018, 33, 199–209. [Google Scholar] [CrossRef]

- Barzegarkhoo, R.; Lee, S.S.; Khan, S.A.; Siwakoti, Y.; Lu, D.D.-C. A novel generalized common-ground switched-capacitor multilevel inverter suitable for transformerless grid-connected applications. IEEE Trans. Power Electron. 2021, 36, 10293–10306. [Google Scholar] [CrossRef]

- Dhara, S.; Somasekhar, V.T. A nine-level transformerless boost inverter with leakage current reduction and fractional direct power transfer capability for PV applications. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 10, 7938–7949. [Google Scholar] [CrossRef]

- Jakkula, S.; Jayaram, N.; Pulavarthi, S.V.K.; Shankar, Y.R.; Rajesh, J. A Generalized High Gain Multilevel Inverter for Small Scale Solar Photovoltaic Applications. IEEE Access 2022, 10, 25175–25189. [Google Scholar] [CrossRef]

- Wu, D.; Peng, L. Characteristics of nearest level modulation method with circulating current control for modular multilevel converter. IET Power Electron. 2016, 9, 155–164. [Google Scholar] [CrossRef]

- Zhang, Y.; Li, L. A step-up switched capacitor multilevel inverter with reduced switches tolerating lower stress. In Proceedings of the 2020 15th IEEE Conference on Industrial Electronics and Applications (ICIEA), Kristiansand, Norway, 9–13 November 2020; pp. 811–816. [Google Scholar] [CrossRef]

- Thota, P.R.; Jeevananthan, S. A New Switched Capacitor Nine-Level Inverter with Quadruple Voltage Boosting and Capacitor Voltage Balancing Capabilities. In Proceedings of the 2020 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Jaipur, India, 16–19 December 2020; pp. 1–5. [Google Scholar] [CrossRef]

- Siddique, M.D.; Iqbal, A.; Riyaz, A. Single-Phase 9L Switched-Capacitor Boost Multilevel Inverter (9L-SC-BMLI) Topology. In Proceedings of the 2020 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Jaipur, India, 23 September 2022; pp. 1–5. [Google Scholar] [CrossRef]

- Siddique, M.D.; Mekhilef, S.; Shah, N.M.; Ali, J.S.M.; Meraj, M.; Iqbal, A.; Al-Hitmi, M.A. A New Single Phase Single Switched-Capacitor Based Nine-Level Boost Inverter Topology with Reduced Switch Count and Voltage Stress. IEEE Access 2019, 7, 174178–174188. [Google Scholar] [CrossRef]

- Sarwar, M.I.; Sarwar, A.; Farooqui, S.A.; Tariq, M.; Fahad, M.; Beig, A.R.; Alamr, B. A Hybrid Nearest Level Combined with PWM Control Strategy: Analysis and Implementation on Cascaded H-Bridge Multilevel Inverter and its Fault Tolerant Topology. IEEE Access 2021, 9, 44266–44282. [Google Scholar] [CrossRef]

| Levels | S1 | S2 | S3 | S4 | S5 | S6 | S7 | S8 | S9 | S10 | S11 | C1 | C2 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| +Vdc | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | C | - |

| +2 Vdc | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | D | C |

| +3 Vdc | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | C | D |

| +4 Vdc | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | D | D |

| 0 Vdc | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | - | - |

| −Vdc | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | C | - |

| −2 Vdc | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | D | C |

| −3 Vdc | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | C | D |

| −4 Vdc | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | D | D |

| Ref. | N | Nsw | Nd | Nc | TSV | Gain | C.F |

|---|---|---|---|---|---|---|---|

| [10] | 9 | 10 | 12 | 2 | 6 | 2 | 24 |

| [11] | 9 | 13 | 0 | 3 | 6.25 | 4 | 30.56 |

| [12] | 9 | 19 | 3 | 3 | 4.75 | 4 | 45.18 |

| [13] | 9 | 14 | 0 | 4 | 6 | 4 | 22 |

| [14] | 9 | 12 | 2 | 4 | 7.5 | 3 | 22.75 |

| [15] | 9 | 15 | 0 | 4 | 6 | 4 | 22 |

| [P] | 9 | 11 | 1 | 2 | 5 | 4 | 17.5 |

| Parameter | Values |

|---|---|

| Input voltage source | 100 V |

| Resistive Load | 100 ohm, 500 ohm |

| Capacitors (C1 = C2) | 4600 µF |

| Inductive Load | 120 mH, 360 mH |

| Input & output frequency | 50 Hz, 50 Hz |

| Peak output voltage | 400 V |

| Peak output current | 3.786 A |

| TSV(p.u) | 5 |

| Cost Factor(C.F) | 17.5 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mustafa, S.; Sarwar, A.; Tariq, M.; Ahmad, S.; Mahmoud, H.A. Development and Control of a Switched Capacitor Multilevel Inverter. Energies 2023, 16, 4269. https://doi.org/10.3390/en16114269

Mustafa S, Sarwar A, Tariq M, Ahmad S, Mahmoud HA. Development and Control of a Switched Capacitor Multilevel Inverter. Energies. 2023; 16(11):4269. https://doi.org/10.3390/en16114269

Chicago/Turabian StyleMustafa, Safwan, Adil Sarwar, Mohd Tariq, Shafiq Ahmad, and Haitham A. Mahmoud. 2023. "Development and Control of a Switched Capacitor Multilevel Inverter" Energies 16, no. 11: 4269. https://doi.org/10.3390/en16114269

APA StyleMustafa, S., Sarwar, A., Tariq, M., Ahmad, S., & Mahmoud, H. A. (2023). Development and Control of a Switched Capacitor Multilevel Inverter. Energies, 16(11), 4269. https://doi.org/10.3390/en16114269