Online Failure Diagnostic in Full-Bridge Module for Optimum Setup of an IGBT-Based Multilevel Inverter

Abstract

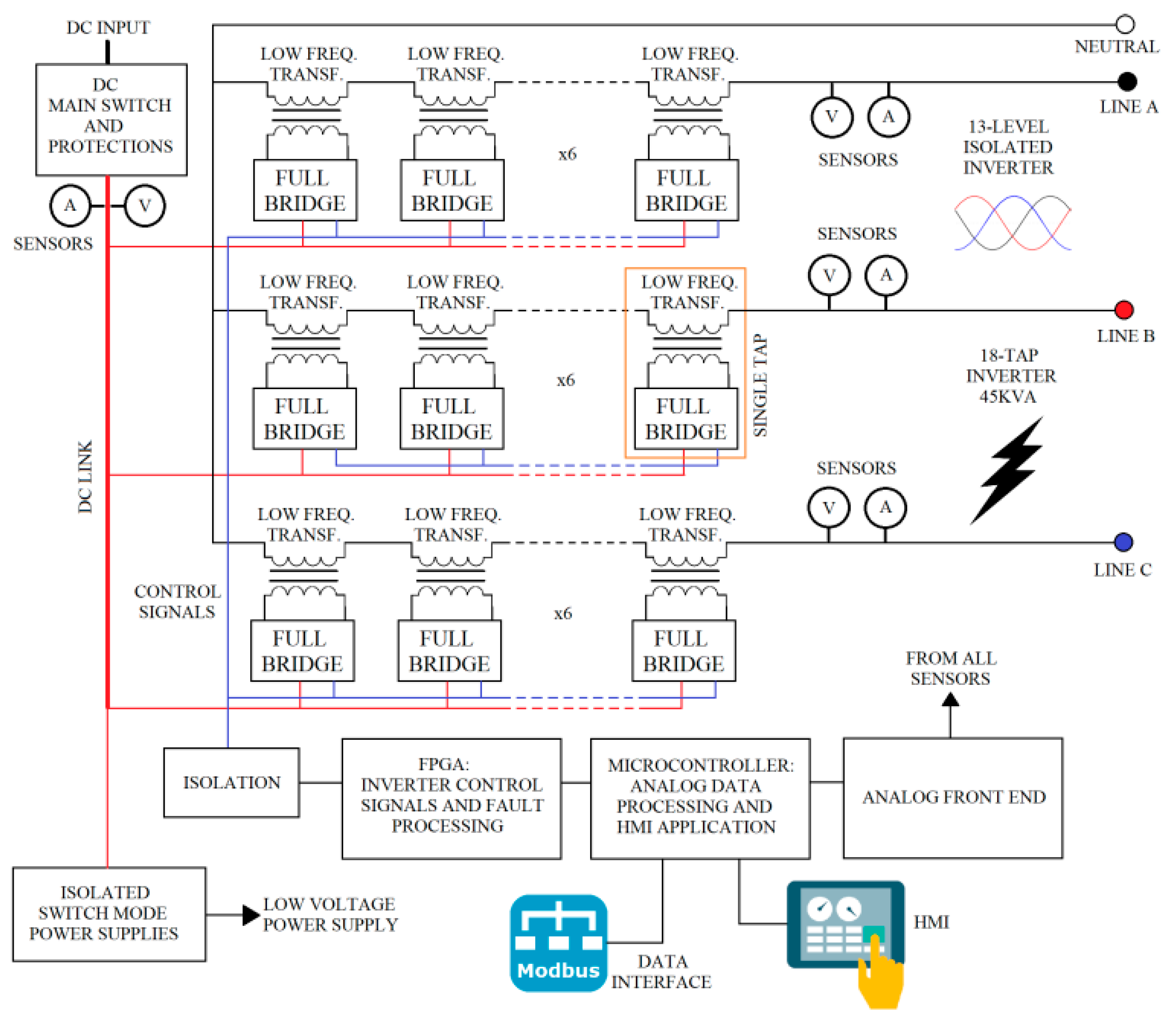

:1. Introduction

2. Failure Mechanisms and Operation of a Full-Bridge Module

- The cross-conduction mechanism emerges during the switching intervals while two IGBTs of the same arm are active. It means an IGBT turns on while the opposite IGBT has not yet turned off. Higher IGBT turn-off times and the driver propagation delays originate from this phenomenon. The cross-conduction is directly related to the switching losses; the higher the cross-conduction, the higher the loss. Furthermore, excessive cross-conduction produces high collector current spikes during transitions that gradually degrade the switching device. IGBT degradation leads to failures such as bonding-wire cracking and detachment, die stresses, and in some cases thermal breakdown.

- In high-inductance switching applications, managing the inductor-stored energy properly is a challenge nowadays. This stored energy becomes a high voltage spike that appears during the IGBT turn-off transition, causing an inductive load avalanche failure. The avalanche mechanism deals with the energy in a different way than a short-circuit does. In a short-circuit event, the IGBT is active, whereas in the avalanche event, the IGBT is gate-emitter voltage (VGE) unbiased.

- The second turn-on is a failure mechanism originated by the IGBT’s Miller capacitance combined with a high dv/dt at the collector node and leads to a type I short-circuit failure. This mechanism occurs when the high voltage at the collector node induces a voltage spike in the gate node during the IGBT turn-off transition. If the voltage spike reaches the IGBT plateau level, the device will turn on again. In addition, the induced voltage in the gate node may increase enough to reach the plateau level, turning on the IGBT, see Figure 2.

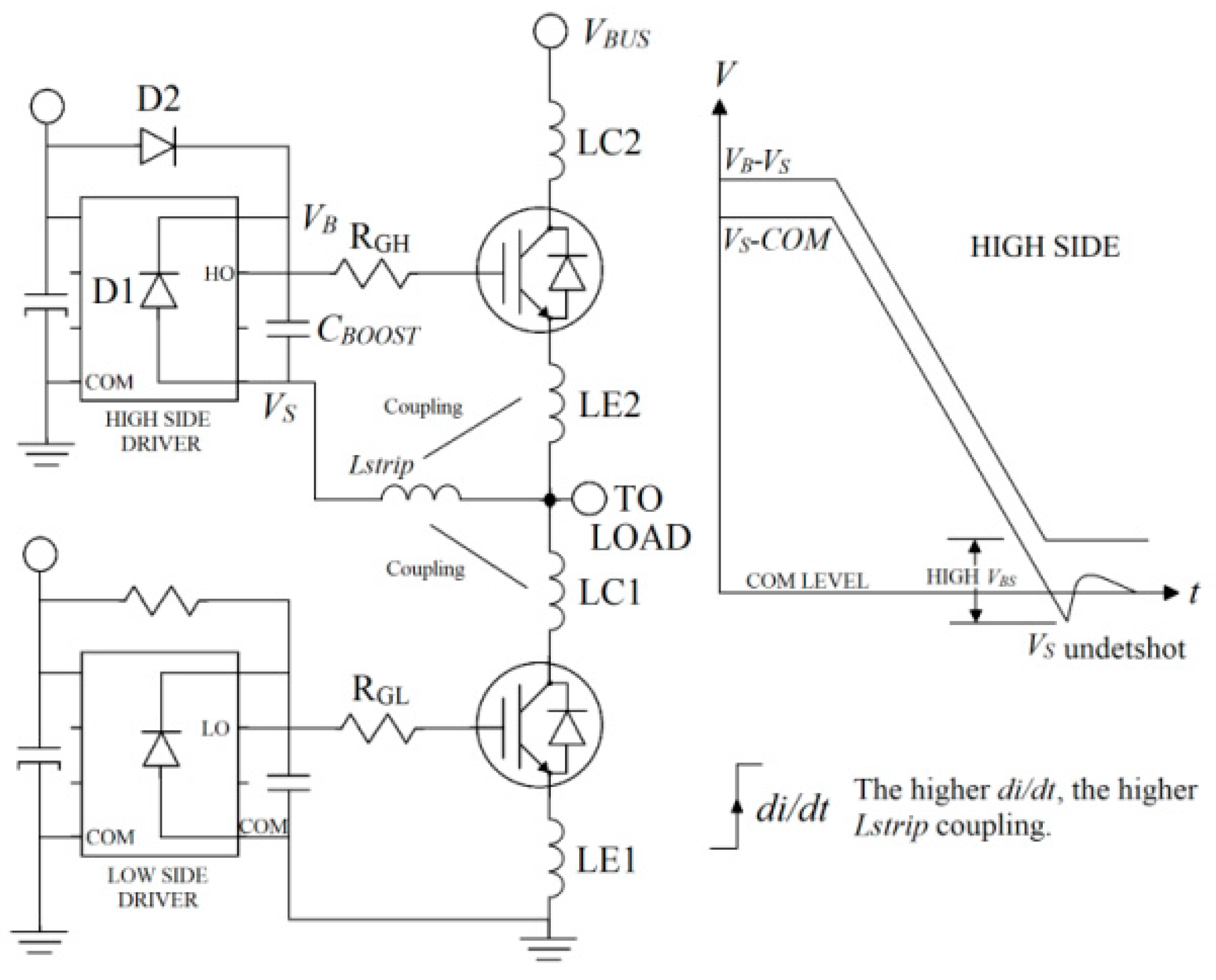

- The VS-undershoot failure mechanism is an under-voltage spike that appears at the driver’s VS terminal, which is used for IGBT switching. When a high di/dt transition occurs, it is generated by the stored energy in the parasitic inductances of the collector and emitter IGBT terminals of the PCB tracks (Lstray). Therefore, VS-undershoot directly affects the high-side IGBT driver, as seen in Figure 3.

- Thermal runaway is a failure mechanism that occurs when a rising temperature causes a further increase in temperature in each IGBT in the full-bridge module. Therefore, uncontrolled temperature-positive feedback leads the IGBT to a destructive scenario.

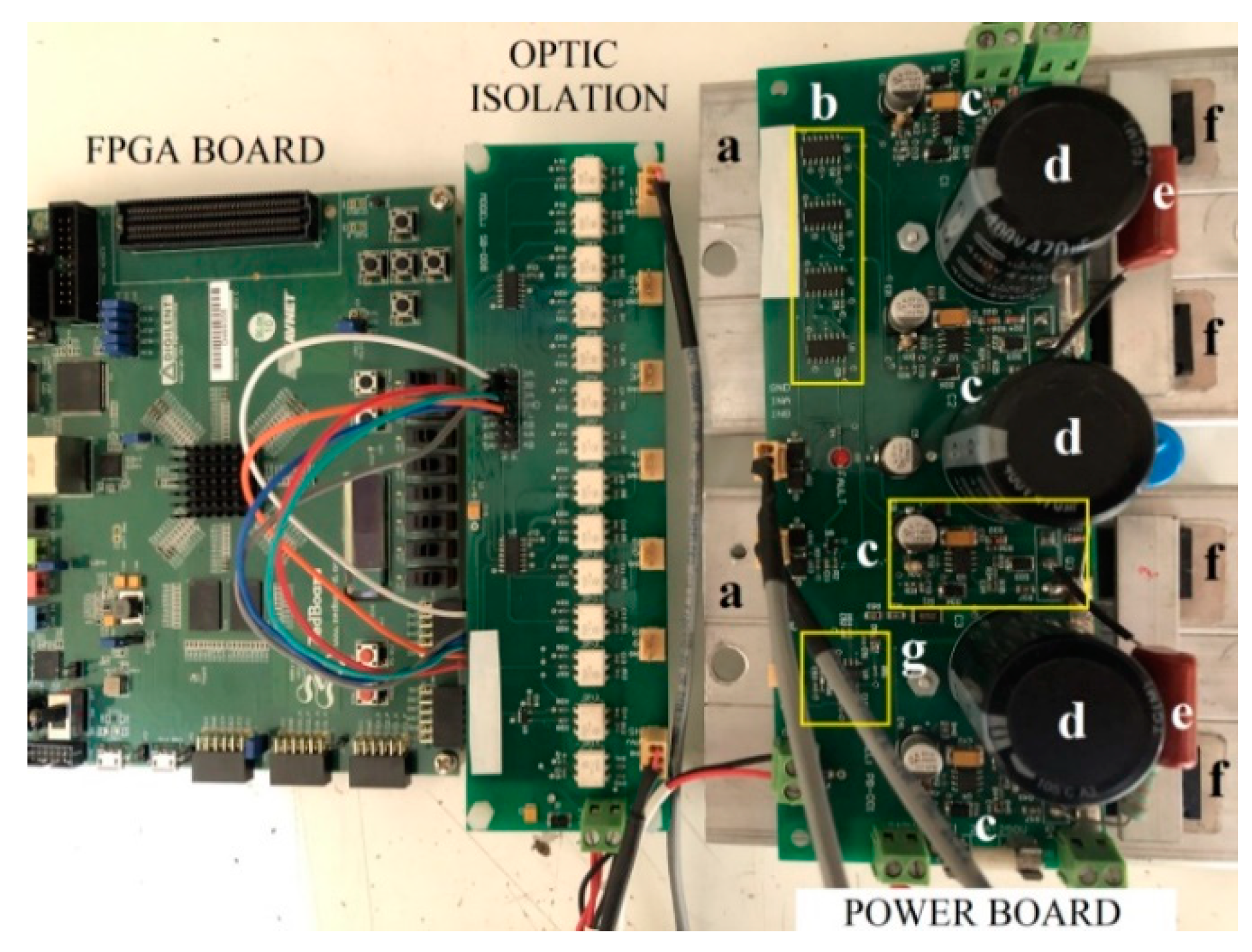

3. Online Diagnostic of the Failure Mechanisms

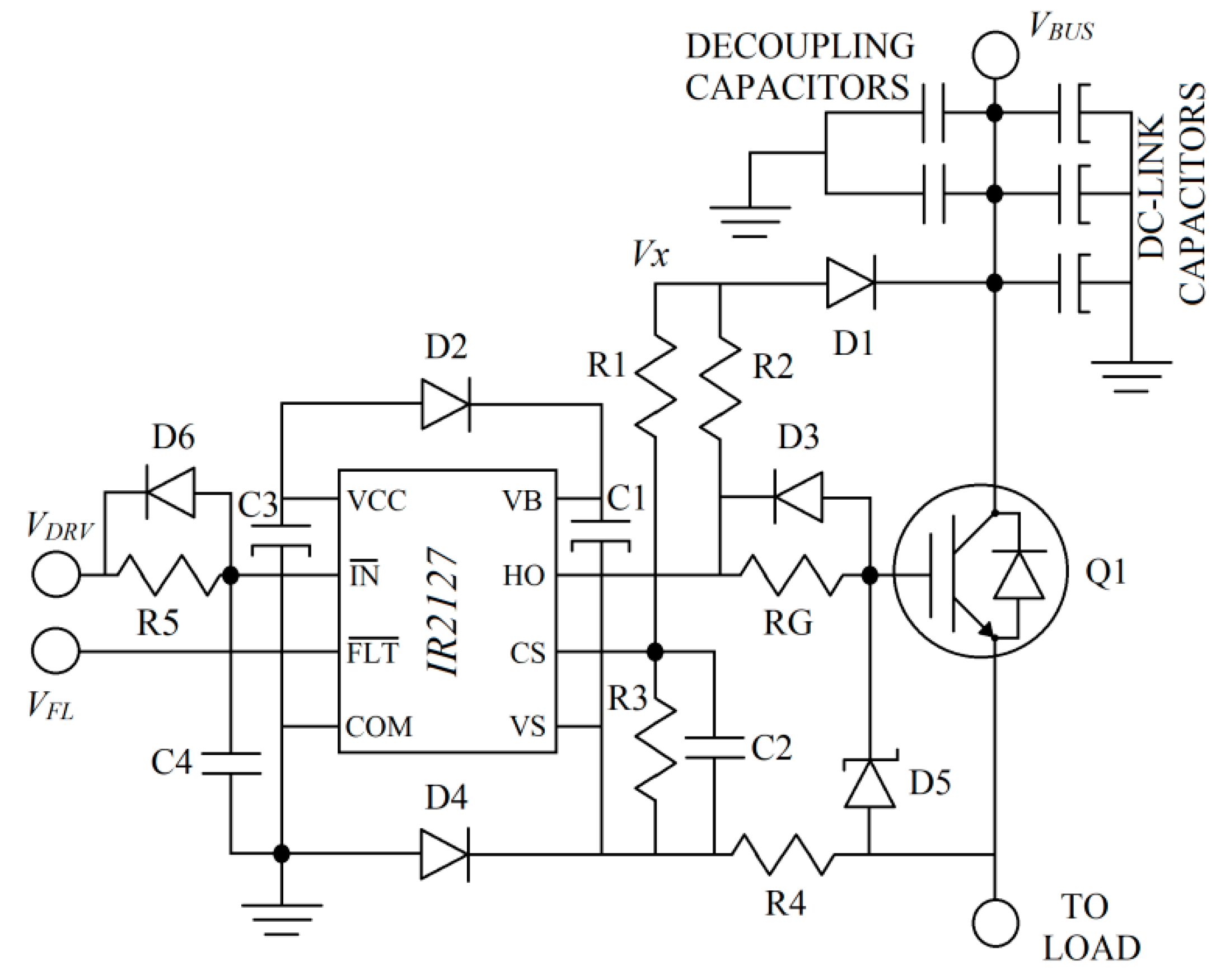

- R1, R2, R3, and C2 values established the driver shutdown delay to prevent an unstable failure condition during the IGBT turn-on time. Therefore, the minimum shutdown delay was the IGBT turn-on time, and the maximum was the IGBT short-circuit withstanding time minus the driver shutdown propagation delay. The optimum shutdown delay should be slightly higher than the IGBT turn-on time.

- The RG value predominantly sets the gate impedance, which should be as low as possible to reduce the probability of the second turn-on phenomenon. However, the RG also creates a delay path to increase the IGBT turn-on time, preventing cross-conduction failure. Moreover, it slightly increases dv/dt, reducing the harmful effects of the Miller capacitance. The optimum RG value is the one that equals the IGBT turn-on and turn-off times.

- The boost capacitor C1 stores the energy to keep the high-side IGBT active when needed. Its value is essential, especially in low-frequency applications. C1 also plays an essential role in setting the driver’s output impedance during the high logical state. In Section 3.3, detailed information on the C1 optimum value calculation is presented.

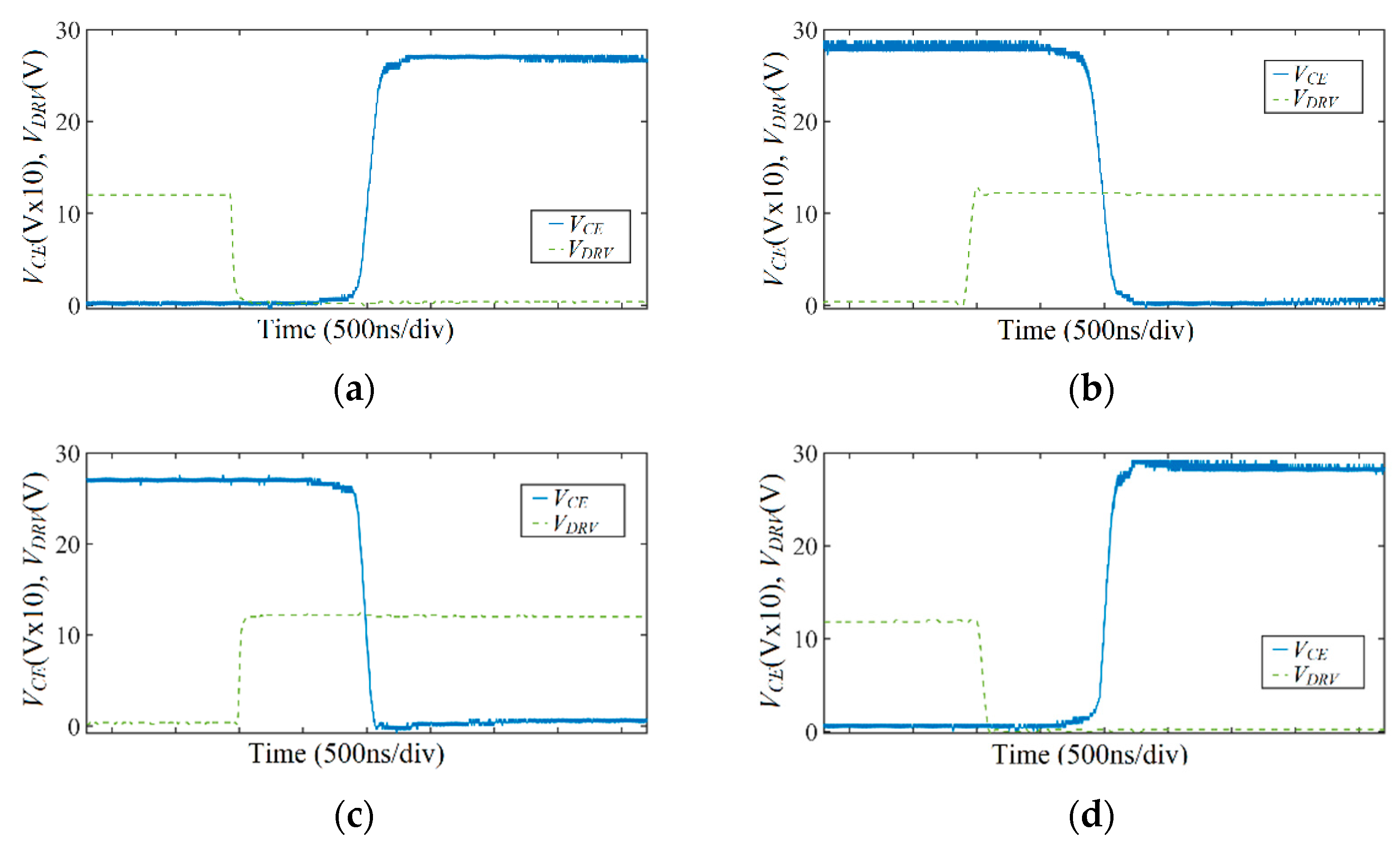

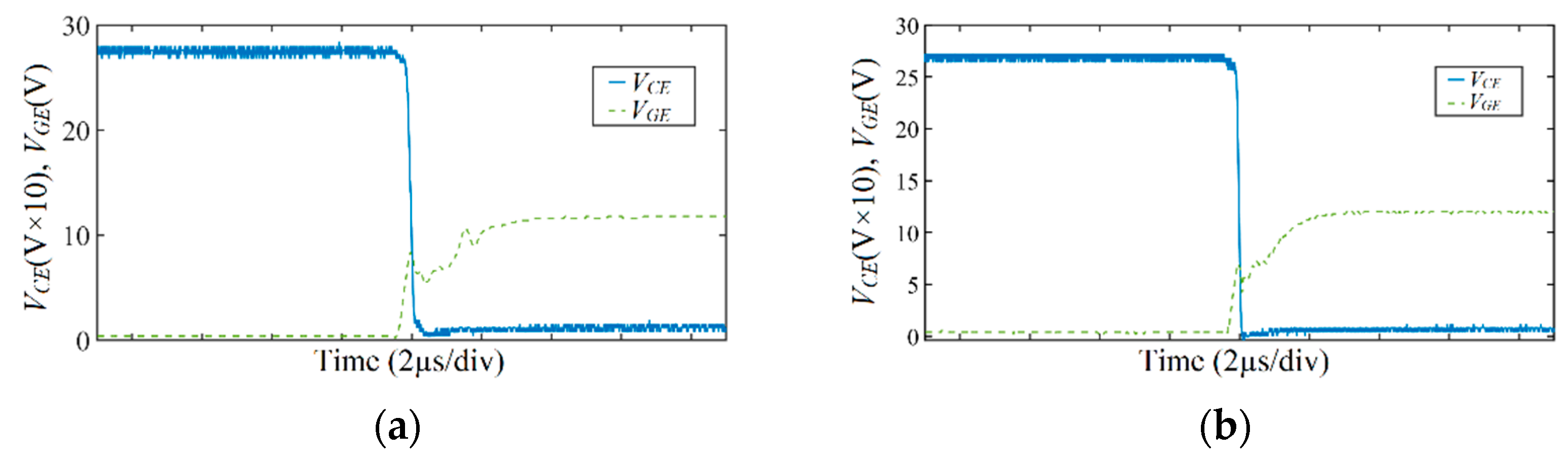

3.1. Cross-Conduction

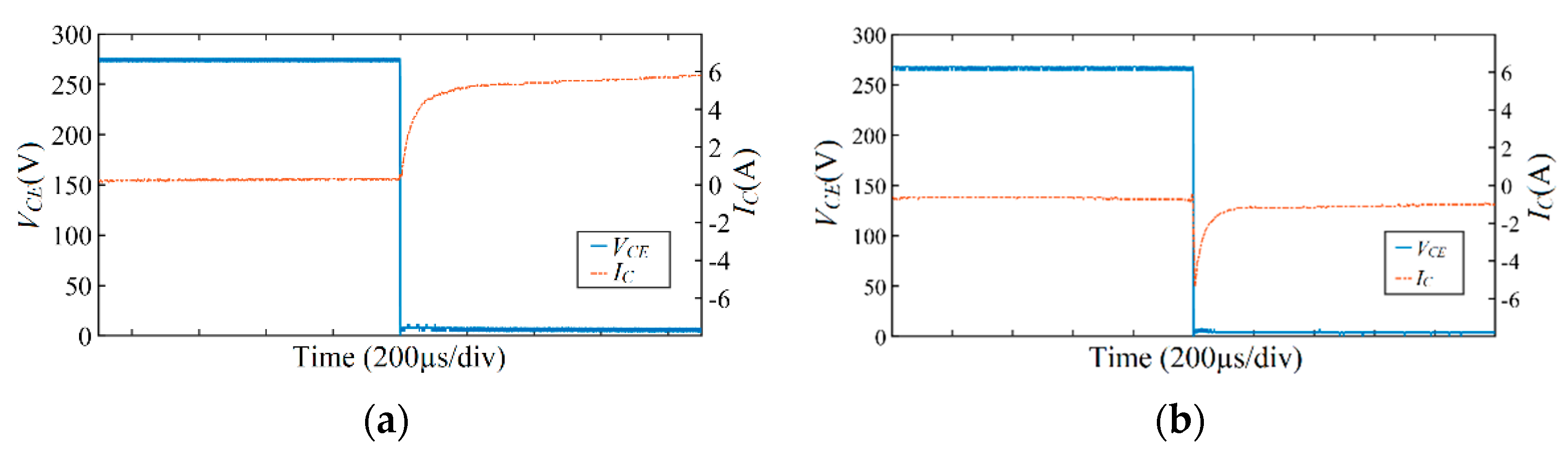

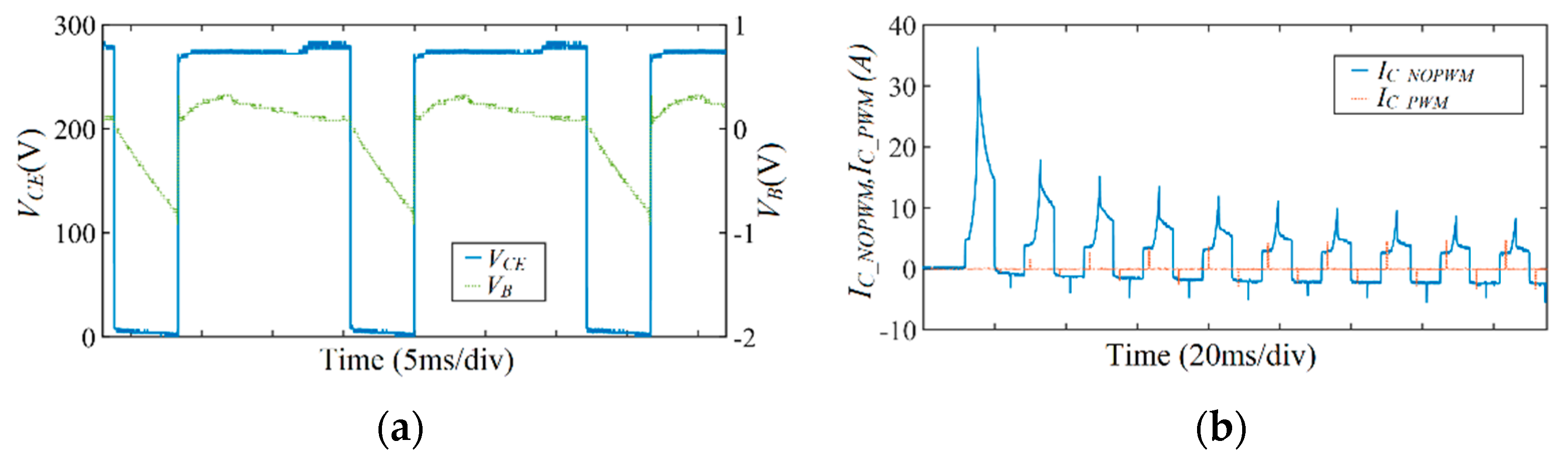

3.2. Inductive Avalanche

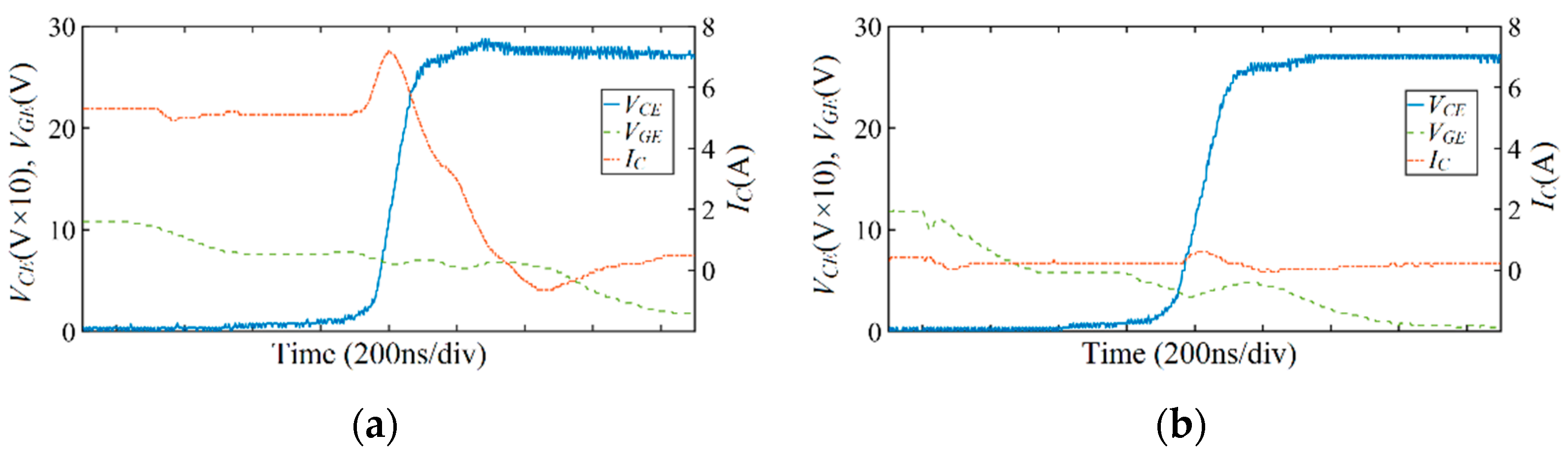

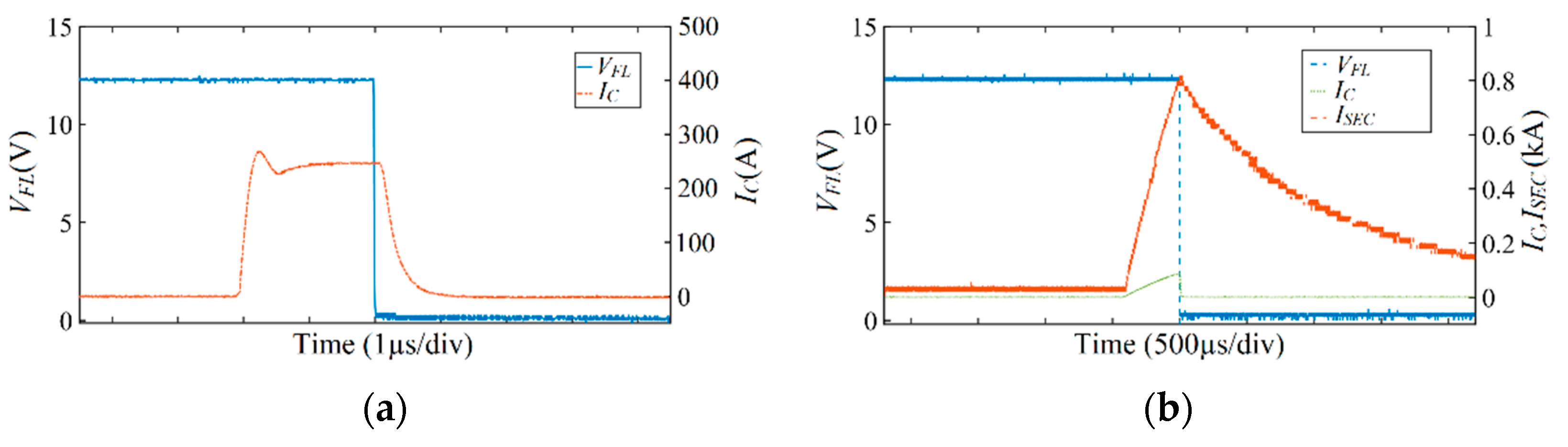

3.3. Second Turn-On

3.4. VS-Undershoot

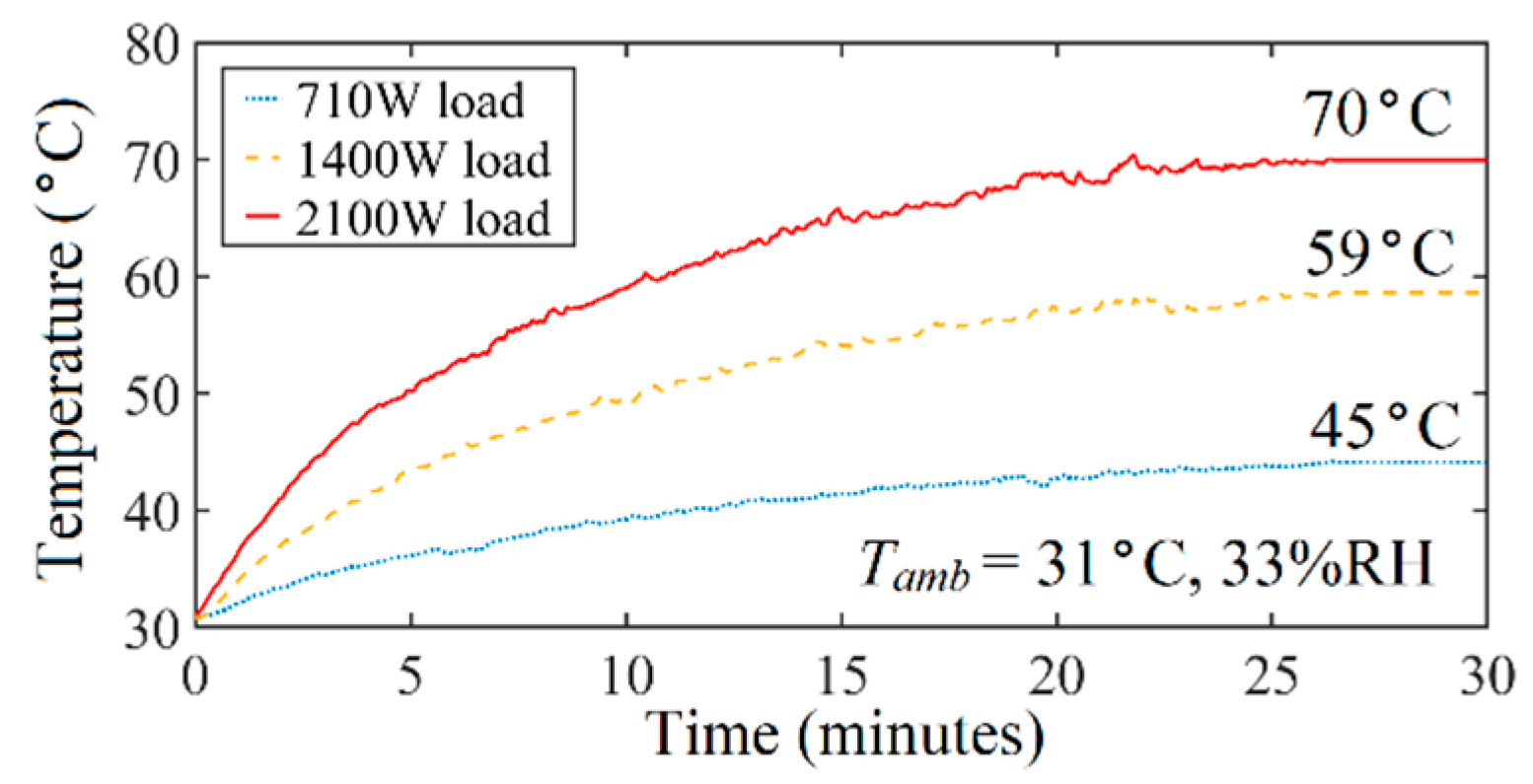

3.5. Thermal Runaway

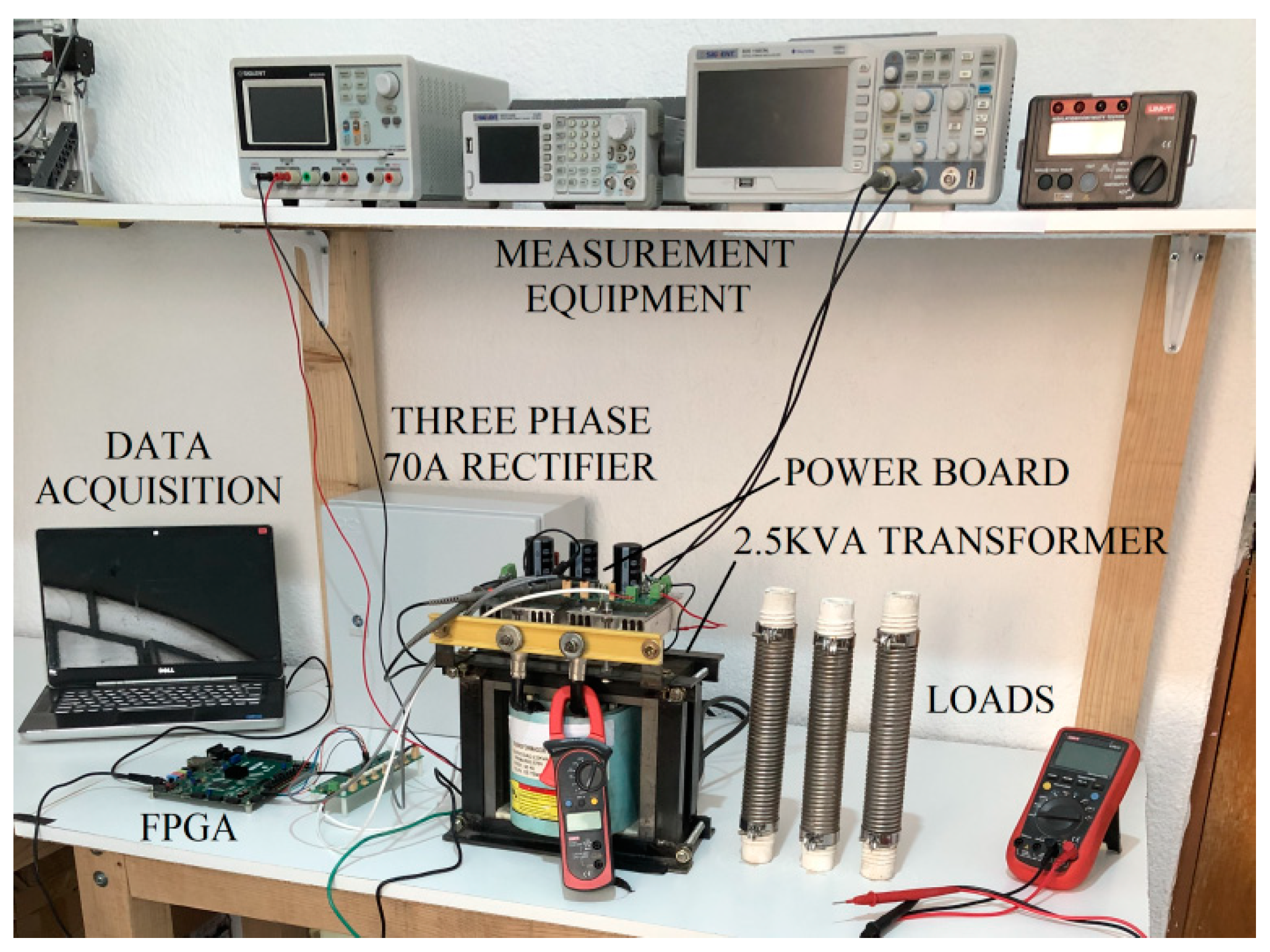

4. Discussion

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Hassan, A.; Yang, X.; Chen, W.; Houran, M.A. A State of the Art of the Multilevel Inverters with Reduced Count Components. Electronics 2020, 9, 1924. [Google Scholar] [CrossRef]

- Daher, S.; Schmid, J.; Antunes, F.L.M. Multilevel Inverter Topologies for Stand-Alone PV Systems. IEEE Trans. Ind. Electron. 2008, 55, 2703–2712. [Google Scholar] [CrossRef]

- Bukhari, S.S.H.; Atiq, S.; Kwon, B.-I. Elimination of the Inrush Current Phenomenon Associated with Single-Phase Offline UPS Systems. Energies 2016, 9, 96. [Google Scholar] [CrossRef] [Green Version]

- Dodge, J.; Hess, J. IGBT Tutorial. Application Note APT0201. 2002. Available online: www.academia.edu/9345985/ApplicationNoteAPT0201RevIGBTTutorial (accessed on 1 April 2022).

- Verdugo, C.; Candela, J.I.; Rodriguez, P. Energy Balancing with Wide Range Operation in the Isolated Multi-Modular Converter. IEEE Power Energy Soc. Section. 2020, 8, 84479–84489. [Google Scholar] [CrossRef]

- Gandomi, A.A.; Saeidabadi, S.; Hossein, S.; Babaei, E.; Gandomi, Y.A. Flexible Transformer Based Multilevel Inverter Topologies. IET Power Electron. 2018, 12, 578–587. [Google Scholar] [CrossRef]

- Behara, S.; Sandeep, N.; Yaragatti, U.R. Design and Implementation of Transformer-Based Multilevel Inverter Topology With Reduced Components. IEEE Trans. Ind. Appl. 2018, 54, 4632–4639. [Google Scholar] [CrossRef]

- Salehahari, S.; Babaei, E.; Hossein, S.; Ajami, A. Transformer-Based Multilevel Inverter: Analysis, design and implementation. IET Power Electron. 2018, 12, 1–10. [Google Scholar] [CrossRef]

- Panda, A.; Suresh, Y. Performance of Cascaded Multilevel Inverter by Employing Single and Three-Phase Transformers. IET Power Electron. 2012, 5, 1694–1705. [Google Scholar] [CrossRef]

- Choi, U.-M.; Blaabjerg, F.; Lee, K.-B. Study and Handling Methods of Power IGBT Module Failures in Power Electronic Converter Systems. IEEE Trans. Power Electron. 2014, 30, 2517–2533. [Google Scholar] [CrossRef]

- ON Semiconductor. Current Sensing Power MOSFETs. AND8093/D. 2017. Available online: www.onsemi.com/pub/Collateral/AND8093-D.PDF (accessed on 1 April 2022).

- Meng, Z.; Yang, Y.; Gao, Y.; Ai, S.; Fang, Z.; Wen, Y.; Wu, L. A Novel IC Measurement Without Blanking Time for Short-Circuit Protection of High-Power IPM. IEEE Access 2020, 8, 64475–64485. [Google Scholar] [CrossRef]

- Shu, L.; Zhang, J.; Shao, S. Crosstalk Analysis and Suppression for a Closed-Loop Active IGBT Gate Driver. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 7, 1931–1940. [Google Scholar] [CrossRef]

- Groeger, J.; Schindler, A.; Wicht, B.; Norling, K. Optimized dv/dt, di/dt Sensing for a Digitally Controlled Slope Shaping Gate Driver. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017. [Google Scholar] [CrossRef]

- Li, X.; Xu, D.; Zhu, H.; Cheng, X.; Yu, Y.; Ng, W.T. Indirect IGBT Over-Current Detection Technique Via Gate Voltage Monitoring and Analysis. IEEE Trans. Power Electron. 2018, 34, 3615–3622. [Google Scholar] [CrossRef]

- Hain, S.; Bakran, M. The Benefit of Using an IGBT with a High Desaturation Current. In Proceedings of the 2017 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017. [Google Scholar]

- Chen, M.; Xu, D.; Zhang, X.; Zhu, N.; Wu, J.; Rajashekara, K. An Improved IGBT Short-Circuit Protection Method with Self-Adaptive Blanking Circuit Based on VCE Measurement. IEEE Trans. Power Electron. 2018, 33, 6126–6136. [Google Scholar] [CrossRef]

- Yin, S.; Wu, Y.; Liu, Y.; Pan, X. Comparative Design of Gate Drivers with Short-Circuit Protection Scheme for SiC MOSFET and Si IGBT. Energies 2019, 12, 4546. [Google Scholar] [CrossRef] [Green Version]

- Krone, T.; Xu, C.; Mertens, A. Fast and Easily Implementable Detection Circuits for Short Circuits of Power Semiconductors. IEEE Trans. Ind. Appl. 2016, 53, 2871–2879. [Google Scholar] [CrossRef]

- Chokhawala, R.; Catt, J.; Kiraly, L. A discussion on IGBT short-circuit behavior and fault protection schemes. IEEE Trans. Ind. Appl. 1995, 31, 256–263. [Google Scholar] [CrossRef]

- Adams, J. Using the Current Sensing IR212X Gate Drive ICs. Application Note AN-1014. Available online: www.all-electronics.de/migrated/document/411pdf-an-1014 (accessed on 5 May 2022).

- International Rectifier. IR2127; Data Sheet. 2004. Available online: https://www.infineon.com/dgdl/Infineon-ir2127-DS-v01_00-EN.pdf?fileId=5546d462533600a4015355c868861696 (accessed on 8 May 2022).

- ON Semiconductor. NGTB50N120FL2W. 2015. Available online: www.onsemi.com/pdf/datasheet/ngtb50n120fl2w-d.pdf (accessed on 12 May 2022).

- Shen, C.; Hefner, A.R., Jr.; Berning, D.W.; Bernstein, J.B. Failure Dynamics of the IGBT During Turn-Off for Unclamped Inductive Loading Conditions. IEEE Trans. Ind. Appl. 2000, 36, 614–624. [Google Scholar] [CrossRef]

- Insulated Gate Bipolar Transistor Failure Analysis in Overvoltage Condition. In Proceedings of the ICREPQ International Conference; European Association for the Development of Renewable Energies, Environment and Power Quality: Santiago de Compostela, Spain. 2012. Available online: www.icrepq.com/icrepq’12/392-kok.pdf (accessed on 15 February 2022).

- ON Semiconductor. AND9052/D. 2011. Available online: www.onsemi.com/pub/Collateral/AND9052-D.PDF (accessed on 4 March 2022).

- Hofstotter, N.; Beckedahl, P. Limits and Hints How to Turn off IGBTs with Unipolar Supply; Application Note AN1401; Semikron Tech., Corp.: Nuremberg, Germany, 2015; Available online: www.semikron.com/downloads/Application-NoteEN2015-06-03Rev-02.pdf (accessed on 10 January 2022).

- Marello, A.; Ruggineti, A.; Grasso, M. Using Monolithic High Voltage Gate Drivers. DT04-04. Available online: www.yumpu.com/en/document/view/3183746/international-rectifier (accessed on 20 March 2022).

- Chey, C.; Parry, J. Managing Transients in Control IC Driven Power Stages. DT97-3. Available online: www.blog.avislab.com/uploads/2014/05/dt97-3.pdf (accessed on 20 March 2022).

- Hu, Z.; Du, M.; Wei, K.; Hurley, W.G. An Adaptive Thermal Equivalent Circuit Model for Estimating the Junction Temperature of IGBTs. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 7, 392–403. [Google Scholar] [CrossRef]

- Otsuki, M.; Onozawa, Y.; Kanemaru, H.; Seki, Y.; Matsumoto, T. A study on the short-circuit capability of field-stop igbts. IEEE Trans. Electron. Devices 2003, 50, 1525–1531. [Google Scholar] [CrossRef]

- Vujacic, M.; Hammami, M.; Srndovic, M.; Grandi, G. Analysis of dc-Link Voltage Switching Ripple in Three-Phase PWM Inverters. Energies 2018, 11, 471. [Google Scholar] [CrossRef] [Green Version]

| Specifications | Values |

|---|---|

| Input voltage (DC link) | 230–280 V (240 V nominal) |

| Output voltage (square wave) | 230–280 V peak (variable duty cycle) |

| IGBT switching frequency | 60 Hz (low switching loss) |

| Output THD | <8% |

| Shor circuit current limit | 300 A |

| Overload (15 min) | 150% |

| Power PCB board size (L × W) | 180 × 70 mm |

| Device Symbol | MFG Part | Description |

|---|---|---|

| R1 | RC0603FR-075K6L | Thick Film Resistor 5.6 kΩ-1% |

| R2 | CRCW060310K0JNEAC | Thick Film Resistor 0.1 W 10 kΩ 5% |

| R3 | CRCW0603200RFKEAC | Thick Film Resistor 0.1 W 200 Ω-1% |

| R4, RG | CR1206-FX-10R0ELF | Thick Film Resistors 10 Ω-1% |

| R5 | CR0603-JW-392ELF | Thick Film Resistor 3.9 kΩ-5% |

| C1 | TAJC476M016RNJ | Tantalum capacitor SMT, 47 µF, 16 V |

| C2 | CC0603KRX7R9BB103 | Multilayer Ceramic Capacitor MLCC-SMD/SMT 10 nF 50 V X7R 10% |

| C3, C4 | CC0603ZRY5V9BB104 | Multilayer Ceramic Capacitors MLCC-SMD/SMT 0.1 µF 50 V 20–80% |

| D1, D2, D4 | ES1J | Super-Fast Diode SMA 600 V 1A |

| D3, D6 | MM4148-T | Diode-General Purpose, Power, Switching RECT-SWIT 0075V 00.15 A |

| D5 | ZMM5245B | Zener Diode 0.5 W 15 V 5% |

| DC-LINK | B43504A9567M000 | CAP ALUM 560 µF 20% 400 V SNAP |

| DECOUPLING | ECW-F4205JL | CAP FILM 2 µF 5% 400VDC AXIAL |

| Q1 | NGTB50N120FL2WG | 1200 V/50 A FAST IGBT FSII |

| Feature | Juan Carlos Iglesias-Rojas, et al. | Zhaoliang Meng, et al. [12] | Johannes Groeger, et al. [14] | Min Chen, et al. [17] | Shan Yin, et al. [18] |

|---|---|---|---|---|---|

| Method | Online monitoring + SC tolerant IGBT | Integrated shunt method | dv/dt and di/dt sensing | Self-adaptive blanking circuit | Improved VCE desaturation |

| Complexity | Low | Medium | High | High | Medium |

| Mature technology (reliability) | Yes | No | No | No | Yes |

| Blanking time | 2 µs | 380 ns | Not reported | 500 ns | 910 ns |

| Economic impact | Low Field Stop II IGBT | Medium Shunts Detection circuits | High High-speed ADCProcessor device | High Complex blanking circuit | Medium Special IC driver |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Iglesias-Rojas, J.C.; Velázquez-Lozada, E.; Baca-Arroyo, R. Online Failure Diagnostic in Full-Bridge Module for Optimum Setup of an IGBT-Based Multilevel Inverter. Energies 2022, 15, 5203. https://doi.org/10.3390/en15145203

Iglesias-Rojas JC, Velázquez-Lozada E, Baca-Arroyo R. Online Failure Diagnostic in Full-Bridge Module for Optimum Setup of an IGBT-Based Multilevel Inverter. Energies. 2022; 15(14):5203. https://doi.org/10.3390/en15145203

Chicago/Turabian StyleIglesias-Rojas, Juan Carlos, Erick Velázquez-Lozada, and Roberto Baca-Arroyo. 2022. "Online Failure Diagnostic in Full-Bridge Module for Optimum Setup of an IGBT-Based Multilevel Inverter" Energies 15, no. 14: 5203. https://doi.org/10.3390/en15145203

APA StyleIglesias-Rojas, J. C., Velázquez-Lozada, E., & Baca-Arroyo, R. (2022). Online Failure Diagnostic in Full-Bridge Module for Optimum Setup of an IGBT-Based Multilevel Inverter. Energies, 15(14), 5203. https://doi.org/10.3390/en15145203