Analysis of the Practical Implementation of Flicker Measurement Coprocessor for AMI Meters †

Abstract

1. Introduction

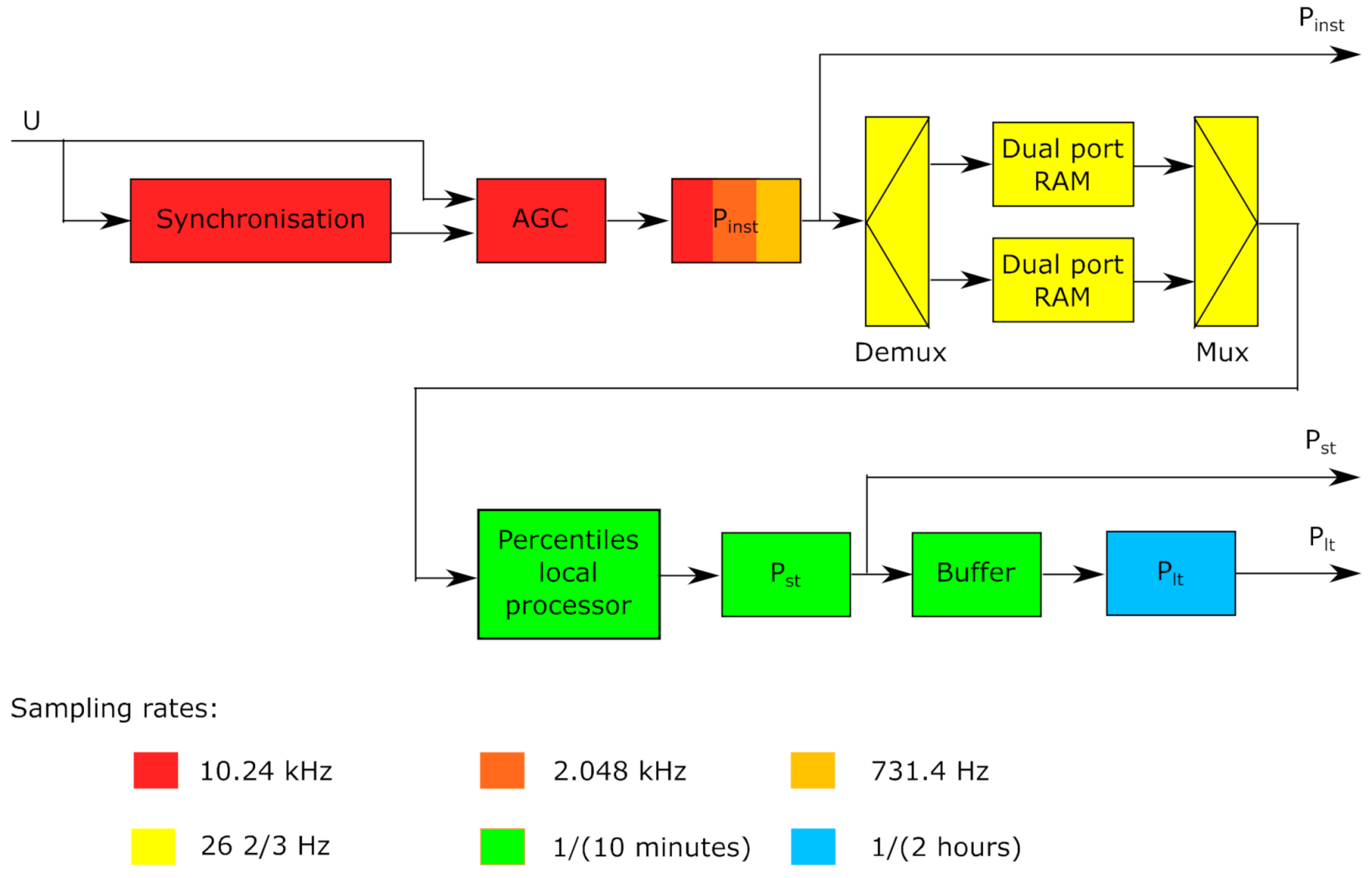

2. Algorithm of Flickermeter and Implementation Issues

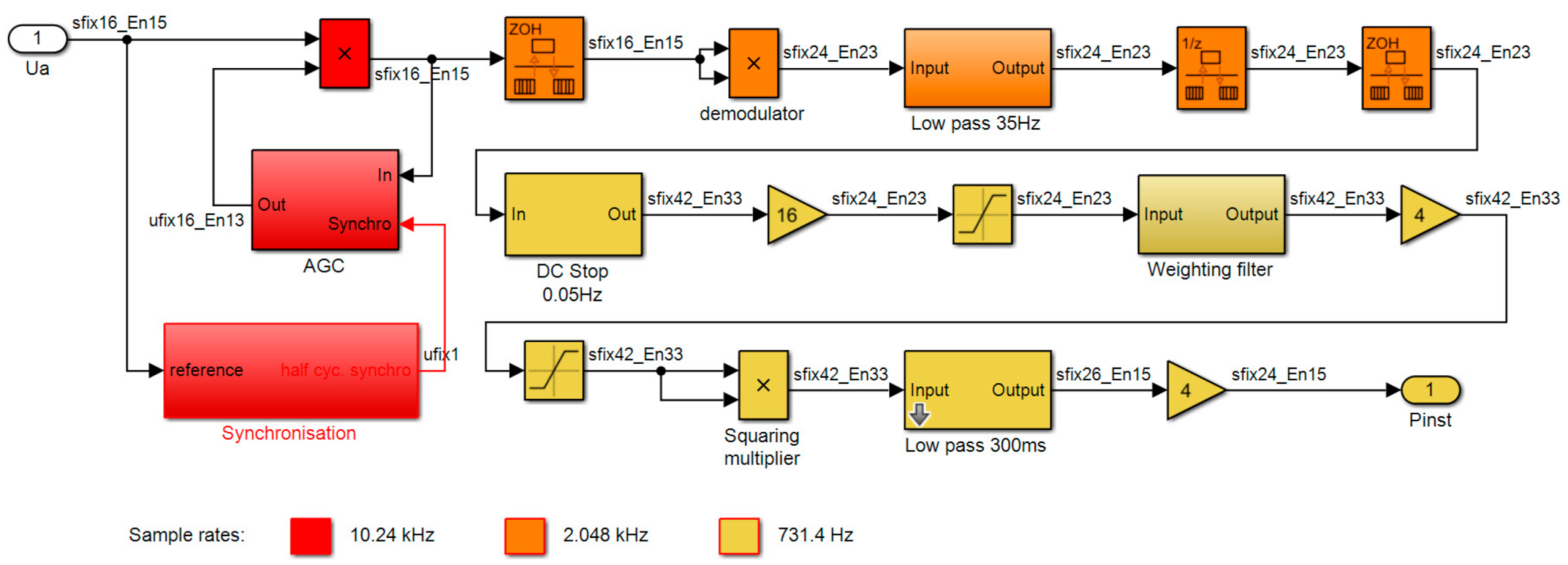

- Input gain control block—the block operates as a signal conditioning unit and provides scaling to the reference value. The reference is the half-period RMS value processed by the 1st order digital filter with a 27.3 s time constant. In the digital implementation, this block provides only scaling, which can be performed by automatic gain control (AGC).

- Square multiplier block—this block, together with the high pass filter in the next block, operate as a demodulator. The FPGA implementation requires the implementation of the integer multiplier.

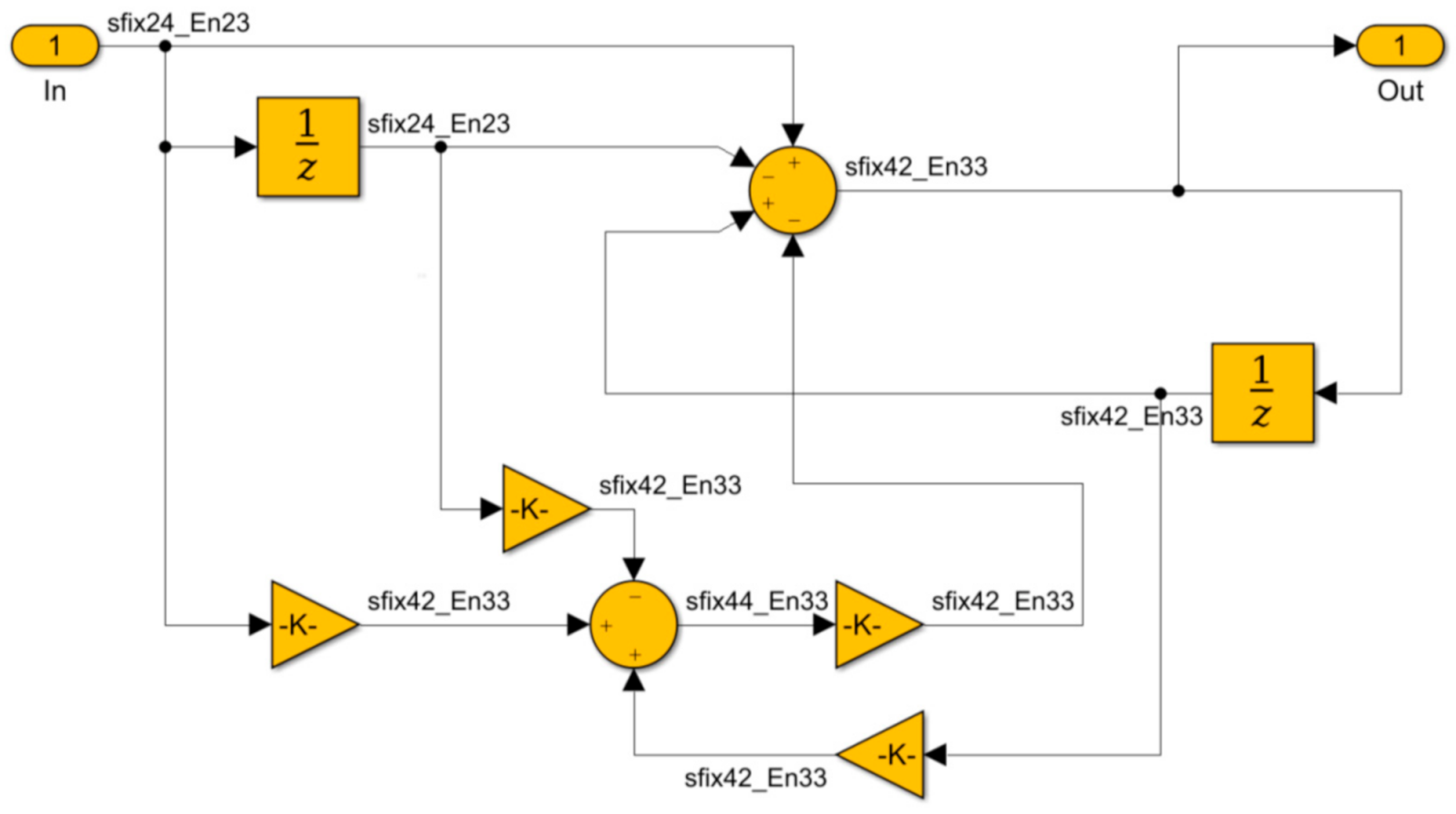

- High pass and weighting filters—this block consist of three filters. The first is a high pass filter, which eliminates the DC component of the voltage. The standard suggests that the filter should be of first-order with −3 dB attenuation at 0.05 Hz cut-off frequency. The second filter is a low pass one, and the standard requires a 6th-order Butterworth filter with an attenuation of −3 dB at 35 Hz (for 230 V system). The last filter is a so-called weighting filter. It simulates the spectral nature of the human visual system. The filter is defined by the transfer function:where the parameters k, λ, ωi (i = 1…4) are given in the standard and vary for 230 V and 110 V systems. Digital implementation of the filters requires the utilisation of filter design tools in order to evaluate fixed-point parameters. It is possible to use a standard FPGA implementation of IIR filters.

- Squaring and smoothing—this block performs two functions: it simulates the eye-brain visual channel through a squaring operation and emulates the brain’s memory effect. Such functions can be achieved through the sliding mean operator; however, the standard suggests utilising a 1st-order filter with 300 ms time constant. The output of this block is an instantaneous flicker Pinst. FPGA implementation requires the utilisation of fixed-point squaring and filtering as described above.

- Statistical analysis—it is the only block that utilises typical digital data processing to obtain short-term Pst and long-term Plt flicker coefficients. The computation is based on the percentile evaluation according to the formula:where:and Px is the x-th percentile of the Pinst values logged during a specified time interval, where x is 0.1, 0.7, 1, 1.5, 2.2, 3, 4, 6, 8, 10, 13, 17, 30, 50, and 80, respectively. The interval can vary from 1 to 15 min; however, the IEC 61000-4-30 standard assumes 10 min for a typical flicker severity evaluation. The evaluation of Plt is performed using 12 samples of Pst. Hence the long-term flicker describes the flicker severity for the last two hours according to the formula:where Plt is the long-term flicker coefficient, Pst,i is the i-th consecutive value of the short-term coefficient, N = 12 is the number of Pst levels taken to compute the Plt coefficient. Due to the sequential nature of the computation, this block is the most difficult to implement in an FPGA.

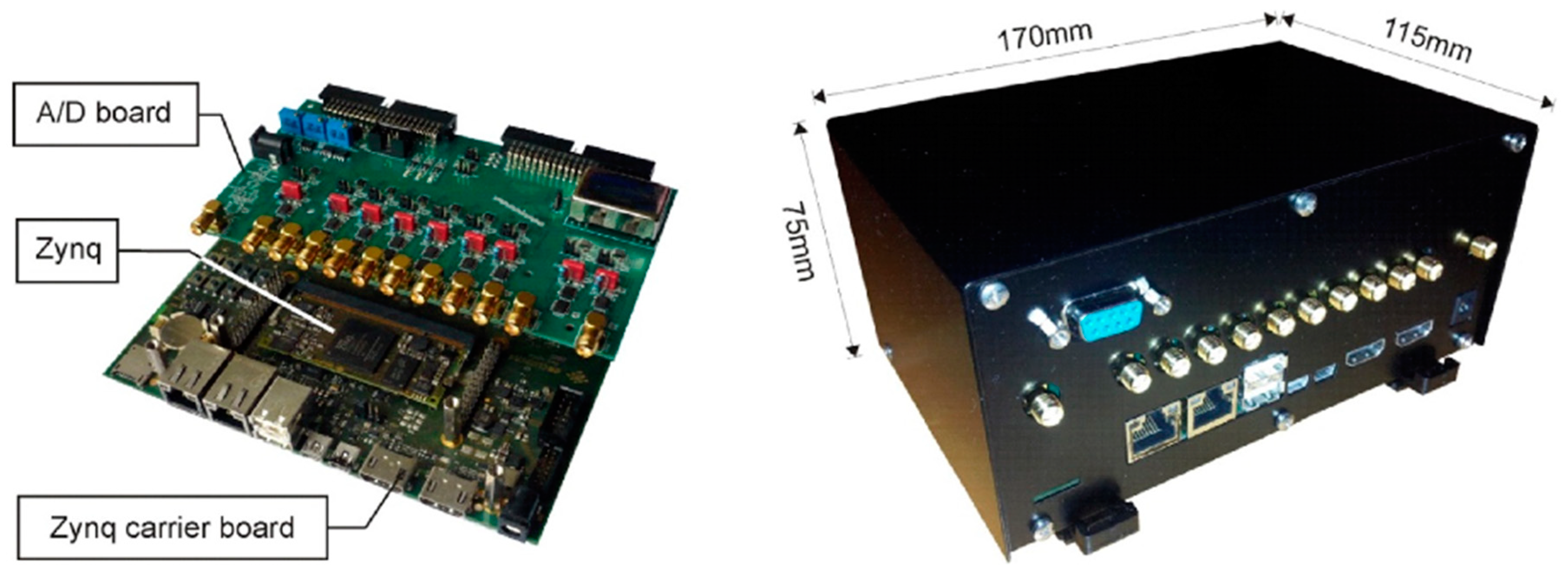

3. Rapid Implementation and Hardware Platform

- To generate C-code finally executed in real-time by a microprocessor, or

- To generate HDL code applied for building an IP module dedicated to an FPGA.

3.1. Data Flow

3.2. Pinst Fixed-Point Algorithm

3.3. Rapid Prototyping

3.4. Hardware Platform

4. Simulation Test Respective to the IEC 61000-4-15 and IEC 61000-4-30

- Sinusoidal/rectangular voltage changes;

- Rectangular voltage changes and performance testing;

- Combined frequency and voltage changes;

- Distorted voltage with multiple zero crossings;

- Bandwidth test using harmonic and interharmonic sideband modulation;

- Phase jumps;

- Rectangular voltage changes with a duty ratio; and

- Measuring range.

4.1. Sinusoidal/Rectangular Voltage Changes

4.2. Rectangular Voltage Changes and Performance Testing

4.3. Combined Frequency and Voltage Changes

4.4. Distorted Voltage with Multiple Zero Crossings

4.5. Harmonics with Sideband

4.6. Phase Jumps

4.7. Rectangular Voltage Changes with a Duty Ratio

4.8. Pst measuring Range

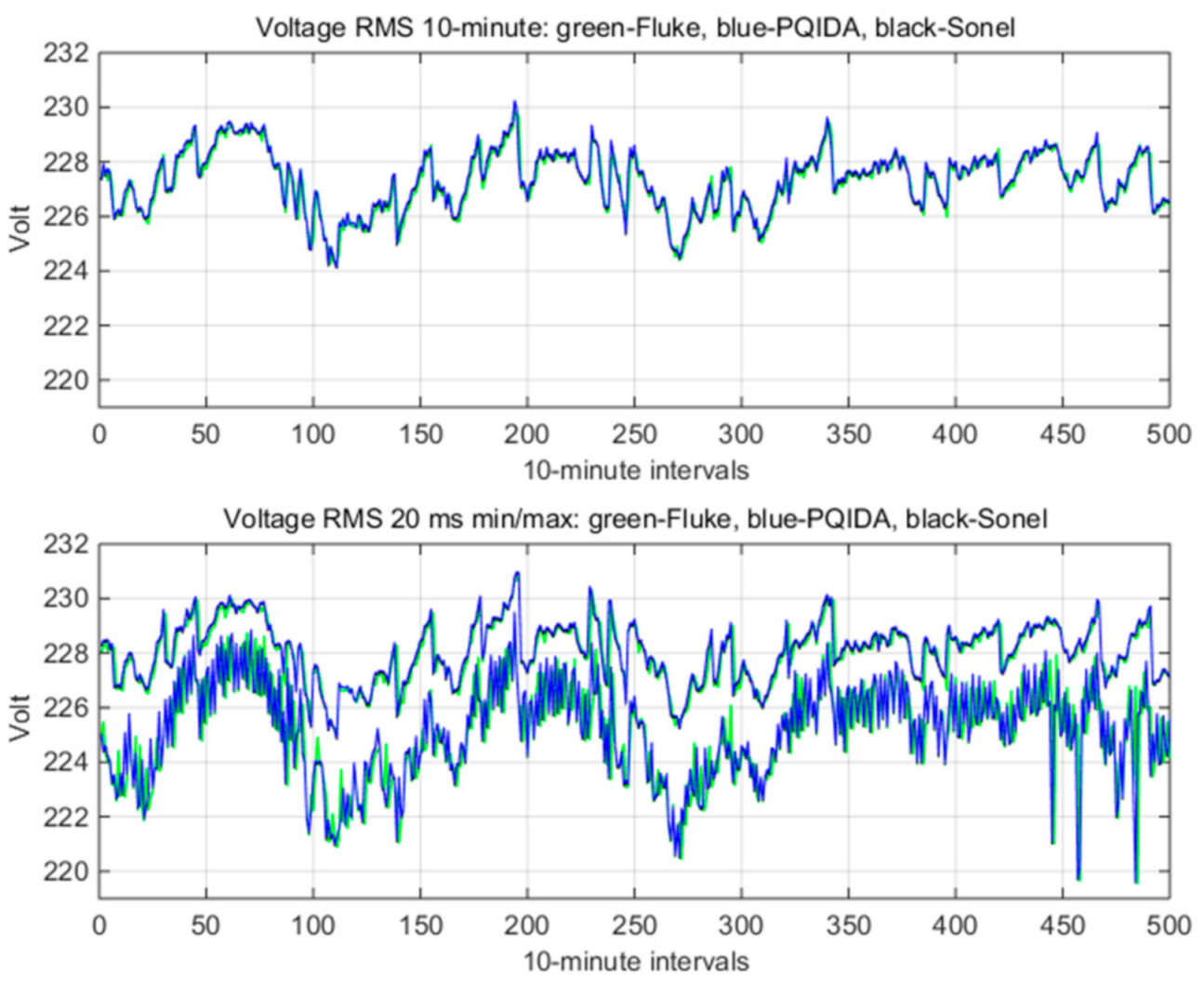

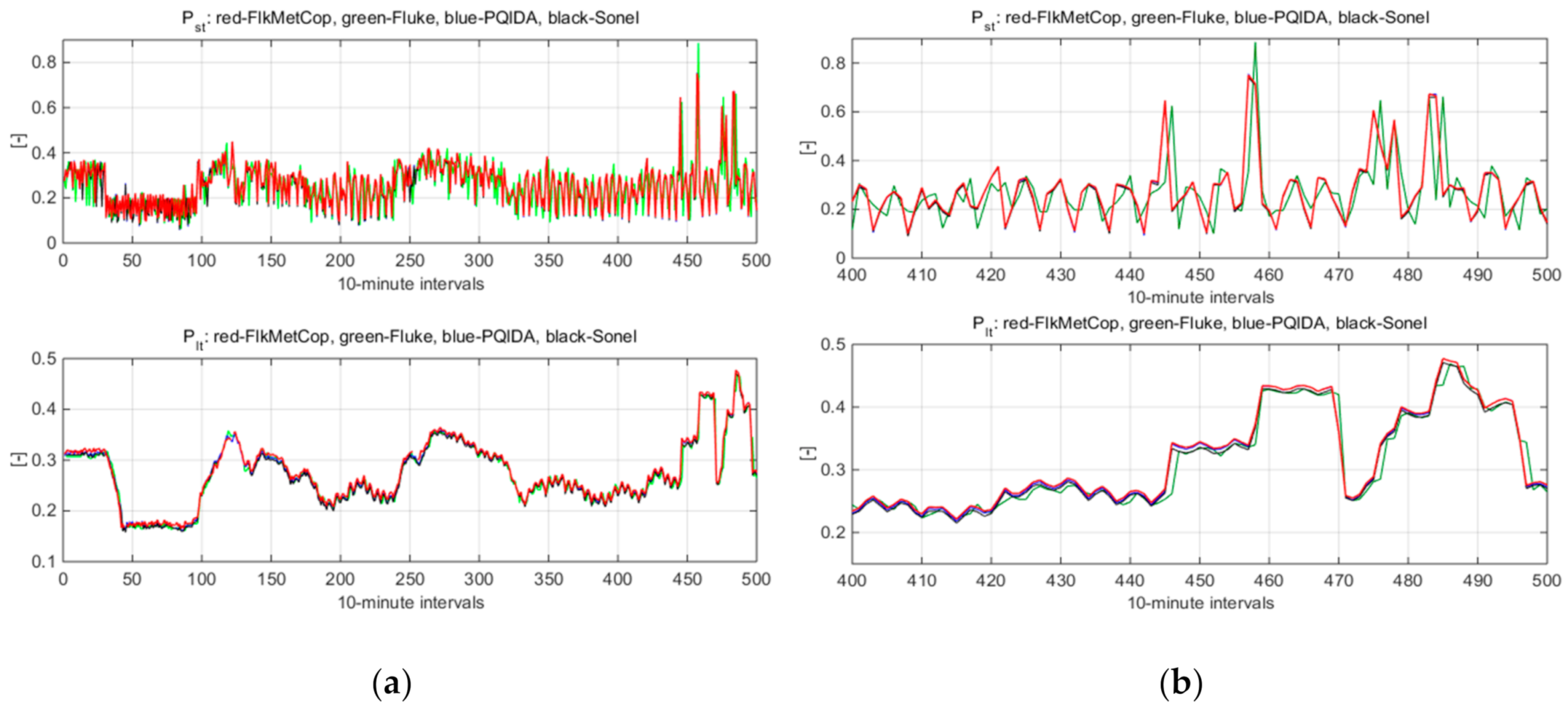

5. Field Tests

6. Discussion and Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Kołek, K.; Firlit, A.; Piatek, K.; Chmielowiec, K. Flicker Measurement Coprocessor for AMI Meters. In Proceedings of the 2020 12th International Conference and Exhibition on Electrical Power Quality and Utilisation EPQU, Kraków, Poland, 14–15 September 2020. [Google Scholar] [CrossRef]

- Lumbreras, D.; Gálvez, E.; Collado, A.; Zaragoza, J. Trends in Power Quality, Harmonic Mitigation and Standards for Light and Heavy Industries: A Review. Energies 2020, 13, 5792. [Google Scholar] [CrossRef]

- IEC International Electrotechnical Commission. IEC 61000-4-30 (edition 1.0: 2003, COR1/2006; edition 2.0: 2008; edition 3.0: 2015, COR1:2016). In Electromagnetic compatibility (EMC)—Part 4–30: Testing and Measurement Techniques—Power Quality Measurement Methods; IEC International Electrotechnical Commission: Geneva, Switzerland, 2016. [Google Scholar]

- Brundrett, G.W. Human sensitivity to flicker. Lighting Res. Technol. 1974, 6, 127–143. [Google Scholar] [CrossRef]

- Fregosi, D.; White, L.; Green, E.; Bhattacharya, S.; Watterson, J. Digital Flickermeter design and implementation based on IEC Standard. IEEE Energy Convers. Congr. Expo. 2010, 4521–4526. [Google Scholar] [CrossRef]

- Kowacs, P.A.; Piovesan, E.J.; Werneck, L.C.; Fameli, H.; Zani, A.C.; Da Silva, H.P. Critical flicker frequency in migraine. A controlled study in patients without prophylactic therapy. Cephalalgia 2005, 25, 339–343. [Google Scholar] [CrossRef] [PubMed]

- Bodington, D.; Bierman, A.; Narendran, N. A flicker perception metric. Lighting Res. Technol. 2015, 48, 624–641. [Google Scholar] [CrossRef]

- Gil-de-Castro, A.; Moreno-Munoz, A.; Larsson, A.; de la Rosa, J.; Bollen, M. LED street lighting: A power quality comparison among street light technologies. Lighting Res. Technol. 2012, 45, 710–728. [Google Scholar] [CrossRef]

- IEC International Electrotechnical Commission. IEC 61000-4-15 (edition 1.0: 1997, AMD1/2003; edition 1.1: 1997+AMD1/2003 CSV; edition 2.0: 2010, COR1:2012—Corrigendum 1, ISH1:2017—Interpretation Sheet 1. In Electromagnetic Compatibility (EMC)—Part 4–15: Testing and Measurement Techniques—Flickermeter—Functional and Design Specifications; IEC International Electrotechnical Commission: Geneva, Switzerland, 2017. [Google Scholar]

- Wiczynski, G. Inaccuracy of Short-Term Light Flicker Pst Indicator Measuring with a Flickermeter. IEEE Trans. Power Deliv. 2012, 27, 842–848. [Google Scholar] [CrossRef]

- Chmielowiec, K. Flicker effect of different types of light sources. In Proceedings of the 11th International Conference on Electrical Power Quality and Utilisation (EPQU), Lisbon, Portugal, 17–19 October 2011; pp. 1–6. [Google Scholar] [CrossRef]

- Drapela, J.; Langella, R.; Testa, A.; Grappè, J. A real life light flicker case-study with LED lamps. In Proceedings of the 18th International Conference on Harmonics and Quality of Power (ICHQP), Ljubljana, Slovenia, 13–16 May 2018; pp. 1–6. [Google Scholar] [CrossRef]

- Hanzelka, Z.; Chmielowiec, K.; Firlit, A.; Swiątek, B. New challenges for voltage quality studies. Prz. Elektrotechniczny 2013, 89, 17–25. [Google Scholar]

- CENELEC European Committee for Electrotechnical Standardization. EN 50160 Voltage Characteristics of Electricity Supplied by Public Electricity Networks (Edition: 2010, A2:2019, A3:2019); CENELEC European Committee for Electrotechnical Standardization: Brussels, Belgium, 2019. [Google Scholar]

- Drapela, J. A time domain based flickermeter with response to high frequency interharmonics. In Proceedings of the 2008 13th International Conference on Harmonics and Quality of Power ICHQP, Wollongong, Australia, 28 September–1 October 2008. [Google Scholar] [CrossRef]

- White, L.; Bhattacharya, S. A Discrete Matlab-Simulink Flickermeter Model for Power Quality Studies. IEEE Trans. Instrum. Meas. 2010, 59, 527–533. [Google Scholar] [CrossRef]

- Ruiz, J.; Lazkano, A.; Aramendi, E.; Leturiondo, L. Analysis of sensitivity to the main parameters involved in the digital implementation of the UIE flickermeter. In Proceedings of the 2000 10th Mediterranean Electrotechnical Conference. Information Technology and Electrotechnology for the Mediterranean Countries, Lemesos, Cyprus, 29–31 May 2000; Volume 2, pp. 823–826. [Google Scholar] [CrossRef]

- Hooshyar, A.; El-Saadany, E. Development of a Flickermeter to Measure Non-Incandescent Lamps Flicker. IEEE Trans. Power Deliv. 2013, 28, 2103–2115. [Google Scholar] [CrossRef]

- Bucci, G.; Fiorucci, E.; Landi, C. A Digital Instrument for Light Flicker Effect Evaluation. IEEE Trans. Instrum. Meas. 2018, 57, 76–84. [Google Scholar] [CrossRef]

- Chen, M.; Lu, C.; Lin, C. Implementation of a integrated algorithm for voltage variation and flicker measurements. In Proceedings of the 2010 IEEE Instrumentation & Measurement Technology Conference Proceedings, Austin, TX, USA, 3–6 May 2010; pp. 1467–1471. [Google Scholar] [CrossRef]

- Caldara, S.; Nuccio, S.; Spataro, C. Digital techniques for flicker measurement: Algorithms and implementations analysis. In Proceedings of the 1999 16th IEEE Instrumentation and Measurement Technology Conference, Venice, Italy, 24–26 May 1999; Volume 2, pp. 656–661, IMTC/99, (Cat. No.99CH36309). [Google Scholar] [CrossRef]

- Stepan, P.; Bubla, V.; Kukacka, L.; Kraus, J. Implementation of flicker meter in power quality analyzers. In Proceedings of the PCIM Europe 2015 International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 19–21 May 2015; pp. 1–8. [Google Scholar]

- Budovsky, I.; Hammond, G. Precision Measurement of Power Harmonics and Flicker. IEEE Trans. Instrum. Meas. 2005, 54, 483–487. [Google Scholar] [CrossRef]

- Eldery, M.; El-Saadany, E.; Salama, M. A Simple Energy Operator Computational Method for Voltage Flicker Assessment. IEEE Trans. Power Deliv. 2006, 21, 1743–1750. [Google Scholar] [CrossRef]

- Kołek, K.; Piątek, K. Rapid algorithm prototyping and implementation for power quality measurement. EURASIP J. Adv. Signal Process. 2015, 19. [Google Scholar] [CrossRef]

- Colnago, G.; Macedo, J.; de Freitas Vieira, J. Implementation of a light Flickermeter in a low cost embedded system. IET Sci. Meas. Technol. 2015, 9, 522–531. [Google Scholar] [CrossRef]

- Huoy, S.; Jamuar, S.; Sidek, R.; Marhaban, M. Digital Signal Processing Based Waveform Generator for Flickermeter Calibration Test System. In Proceedings of the 2006 4th Student Conference on Research and Development, Shah Alam, Malaysia, 27–28 June 2006; pp. 108–111. [Google Scholar] [CrossRef]

- Lin, T.; Tsuji, M.; Yamada, E. Wavelet approach to power quality monitoring. In Proceedings of the IECON’01. In Proceedings of the 27th Annual Conference of the IEEE Industrial Electronics Society, (Cat. No.37243), Denver, CO, USA, 29 November–2 December 2001; Volume 1, pp. 670–675. [Google Scholar] [CrossRef]

- El-Gawad, A. Suggested flicker monitoring system based on wavelet transform. In Proceedings of the 2013 22nd International Conference and Exhibition on Electricity Distribution CIRED 2013, Stockholm, Sweden, 10–13 June 2013. [Google Scholar] [CrossRef]

- Li, Z.; Shen, J.; Wei, P.; Li, T. A Voltage Fluctuation and Flicker Monitoring System Based on Wavelet Transform. In Proceedings of the 2008 Workshop on Power Electronics and Intelligent Transportation System, Guangzhou, China, 2–3 August 2008; pp. 310–314. [Google Scholar] [CrossRef]

- Szlosek, M.; Swiatek, B.; Hanzelka, Z. Application of neural networks to voltage fluctuations measurement—Neural networks flickermeter. In Proceedings of the 2008 International School on Nonsinusoidal Currents and Compensation, Lagow, Poland, 10–13 June 2008. [Google Scholar] [CrossRef]

- Ranganathan, P.; Kavasseri, R. Flickermeter Design: An Improved Method to evaluate Short term Flicker Severity Index (Pst) using Walsh Hadamard Transform (WHT). In Proceedings of the 2010 Asia-Pacific Power and Energy Engineering Conference, Chengdu, China, 28–31 March 2010. [Google Scholar] [CrossRef]

- Legarreta, A.; Figueroa, J. An IEC 61000-4-30 class A—Power quality monitor with a flicker meter based on Hilbert transform. In Proceedings of the 2011 11th International Conference on Electrical Power Quality and Utilisation, Lisbon, Portugal, 17–19 October 2011. [Google Scholar] [CrossRef]

- Yao, W.; Tang, Q.; Teng, Z.; Gao, Y.; Wen, H. Fast S-Transform for Time-Varying Voltage Flicker Analysis. IEEE Trans. Instrum. Meas. 2014, 63, 72–79. [Google Scholar] [CrossRef]

- Wei, K.; Xiangwu, Y.; Lixia, Z. A modified digital measuring method on flickering. In Proceedings of the 2003 Asia-Pacific Conference on Environmental Electromagnetics, CEEM 2003, Hangzhou, China, 4–7 November 2003; pp. 621–625. [Google Scholar] [CrossRef]

- Haitao, G.; Peng, X.; Jin, T.; Shihui, H.; Rugang, W.; Quan, Z. Voltage Flicker Detection Based on Probability Resampling. Energies 2020, 13, 3350. [Google Scholar] [CrossRef]

- Analog Devices Web Site. ADE9000 Data Sheet. High Performance, Multiphase Energy, and Power Quality Monitoring IC. 2020. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/ADE9000.pdf; https://www.analog.com/en/products/ade9000.html (accessed on 31 December 2020).

| LUTs | Registers | Block RAM | DSP Blocks | |

|---|---|---|---|---|

| Zynq 7010 | 6202 35.24% | 1403 3.99% | 25 41.67% | 51 63.75% |

| Zynq 7100 | 6202 1.24% | 1403 0.25% | 25 3.31% | 51 2.52% |

| Artix 7 XC7A200t | 4597 3.42% | 1542 0.57% | 25 3.38% | 71 9.60% |

| Fluctuation Frequency [Hz] | Voltage Fluctuation ∆U/U [%] | Pinst,max | |||

|---|---|---|---|---|---|

| Floating-Point Simulation | Relative Error | HIL Fixed-Point Test | Relative Error | ||

| 0.5 | 2.325 | 0.9987 | −0.13% | 0.9952 | −0.48% |

| 1.5 | 1.067 | 0.9983 | −0.17% | 0.9874 | −1.26% |

| 8.8 | 0.250 | 0.9986 | −0.14% | 1.0339 | 3.39% |

| 20 | 0.704 | 0.9988 | −0.12% | 1.0023 | 0.23% |

| 25 | 1.037 | 0.9972 | −0.28% | 0.9862 | −1.38% |

| 33 1/3 | 2.128 | 0.9976 | −0.24% | 0.9850 | −1.50% |

| Fluctuation Frequency [Hz] | Voltage Fluctuation ∆U/U [%] | Pinst,max | |||

|---|---|---|---|---|---|

| Floating-Point Simulation | Relative Error | HIL Fixed-Point Test | Relative Error | ||

| 0.5 | 0.509 | 0.9991 | −0.09% | 0.9895 | 0.33% |

| 3.5 | 0.342 | 0.9965 | −0.35% | 1.0024 | 0.17% |

| 8.8 | 0.196 | 0.9991 | −0.09% | 1.0347 | −0.09% |

| 18.0 | 0.446 | 0.9968 | −0.32% | 0.9845 | −1.02% |

| 21.5 | 0.592 | 0.9981 | −0.19% | 0.9945 | −0.98% |

| 25.0 | 0.764 | 0.9984 | −0.16% | 0.9840 | −0.46% |

| 28.0 | 0.915 | 0.9991 | −0.09% | 0.9972 | 0.57% |

| 30.5 | 0.847 | 0.9988 | −0.12% | 1.0160 | 0.33% |

| 33 1/3 | 1.671 | 1.0001 | 0.01% | 1.0240 | 0.17% |

| Rectangular Changes Per Minute [CPM] | Voltage Fluctuation ∆U/U [%] | Pst | |||

|---|---|---|---|---|---|

| Floating-Point Simulation | Relative Error | HIL Fixed-Point Test | Relative Error | ||

| 1 | 2.715 | 0.9935 | −0.65% | 1.0033 | 0.33% |

| 2 | 2.191 | 1.0020 | 0.20% | 1.0017 | 0.17% |

| 7 | 1.450 | 0.9988 | −0.12% | 0.9991 | −0.09% |

| 39 | 0.894 | 0.9994 | −0.06% | 0.9898 | −1.02% |

| 110 | 0.722 | 1.0005 | 0.05% | 0.9902 | −0.98% |

| 1620 | 0.407 | 0.9981 | −0.19% | 0.9954 | −0.46% |

| 4000 | 2.343 | 0.9990 | −0.10% | 1.0057 | 0.57% |

| Fluctuation Frequency [Hz] | Voltage Fluctuation ∆U/U [%] | Pinst,max | |||

|---|---|---|---|---|---|

| Floating-Point Simulation | Relative Error | HIL Fixed-Point Test | Relative Error | ||

| 49.75 | 230.000 | 1.0064 | 0.64% | 1.0306 | 3.06% |

| 50.25 | 228.812 | ||||

| fi/fv [Hz] | Uv/U = Ui/U [%] | Pinst,max | |||

|---|---|---|---|---|---|

| Floating-Point Simulation | Relative Error | HIL Fixed-Point Test | Relative Error | ||

| 140/150 | 3.611 | 0.9902 | −0.98% | 0.9392 | −6.08% |

| 190/200 | 0.9941 | −0.59% | 1.0526 | 5.26% | |

| 240/250 | 0.9911 | −0.89% | 0.9496 | −5.04% | |

| 290/300 | 0.9941 | −0.59% | 1.0550 | 5.50% | |

| 340/350 | 0.9913 | −0.87% | 0.9866 | −1.34% | |

| 390/400 | 0.9941 | −0.59% | 1.0315 | 3.15% | |

| 440/450 | 0.9914 | −0.86% | 0.9867 | −1.33% | |

| 490/500 | 0.9945 | −0.55% | 1.0531 | 5.31% | |

| 540/550 | 0.9915 | −0.85% | 0.9961 | −0.39% | |

| Phase Jump Angle Δβ | Required Pst | Pst | |||||

|---|---|---|---|---|---|---|---|

| Floating-Point Simulation | Relative Error | Absolute Error | HIL Fixed-Point Test | Relative Error | Absolute Error | ||

| +30 deg | 0.913 | 0.8710 | −4.60% | −0.042 | 0.9041 | −0.97% | −0.009 |

| −30 deg | 0.913 | 0.9564 | 4.75% | 0.043 | 0.9539 | 4.48% | 0.041 |

| +45 deg | 1.060 | 1.0879 | 2.63% | 0.028 | 1.0582 | −0.17% | −0.002 |

| −45 deg | 1.060 | 1.1020 | 3.96% | 0.042 | 1.0708 | 1.02% | 0.011 |

| Rectangular Changes per Minute [CPM] | HIL Floating-Point Test Relative Errors | ||||

|---|---|---|---|---|---|

| Reference Pst = 0.2 | Reference Pst = 0.5 | Reference Pst = 2 | Reference Pst = 5 | Reference Pst = 10 | |

| 1 | 0.70% | 0.14% | −0.29% | 0.62% | −1.37% |

| 2 | 1.11% | 0.71% | −0.57% | 1.82% | −4.20% |

| 7 | 0.11% | −0.04% | −0.11% | 0.23% | −2.48% |

| 39 | 0.07% | −0.02% | −0.07% | −0.09% | −0.81% |

| 110 | 0.17% | 0.07% | 0.05% | 0.04% | −1.07% |

| 1620 | −0.08% | −0.18% | −0.20% | −0.20% | −0.92% |

| 4000 | 0.00% | −0.08% | −0.13% | −0.36% | −1.26% |

| Rectangular Changes per Minute [CPM] | HIL Fixed-Point Test Relative Errors | ||||

|---|---|---|---|---|---|

| Reference Pst = 0.2 | Reference Pst = 0.5 | Reference Pst = 2 | Reference Pst = 5 | Reference Pst = 10 | |

| 1 | −0.07% | 0.07% | −1.71% | −3.37% | −3.94% |

| 2 | 0.34% | −0.21% | −4.31% | 3.31% | −0.93% |

| 7 | 0.12% | −0.10% | 0.24% | 0.09% | −0.38% |

| 39 | −0.63% | 0.75% | −0.84% | −0.86% | 0.07% |

| 110 | −0.56% | 0.85% | −0.97% | −0.81% | −0.03% |

| 1620 | −0.87% | 0.53% | −1.00% | −0.80% | 0.21% |

| 4000 | 2.20% | −0.73% | 0.62% | 0.45% | 1.19% |

| PQ Analyser | Manufacturer |

|---|---|

| Fluke 1760TR | FLUKE Corporation, Everett, WA, USA |

| PQM−703 | Sonel S.A., Swidnica, Poland |

| PQI-DA | A. Eberle GmbH & Co., Nuremberg, Germany |

| ION7650 | Schneider Electric, Rueil-Malmaison, France |

| Statistical Values | Pst | ||||

|---|---|---|---|---|---|

| Fluke 1760TR | PQI-DA | Sonel | Average Value | Flicker Coprocessor | |

| Max | 0.887 | 0.755 | 0.740 | 0.794 | 0.751 |

| CP99 (99%) | 0.468 | 0.527 | 0.528 | 0.508 | 0.533 |

| CP95 (95%) | 0.380 | 0.380 | 0.370 | 0.377 | 0.382 |

| CP50 (50%) | 0.259 | 0.260 | 0.260 | 0.260 | 0.264 |

| CP05 (5%) | 0.109 | 0.106 | 0.110 | 0.108 | 0.116 |

| Statistical Values | Plt | ||||

|---|---|---|---|---|---|

| Fluke 1760TR | PQI-DA | Sonel | Average Value | Flicker Coprocessor | |

| Max | 0.469 | 0.477 | 0.471 | 0.472 | 0.477 |

| CP99 (99%) | 0.429 | 0.434 | 0.429 | 0.431 | 0.434 |

| CP95 (95%) | 0.354 | 0.358 | 0.353 | 0.355 | 0.360 |

| CP50 (50%) | 0.276 | 0.277 | 0.273 | 0.275 | 0.280 |

| CP05 (5%) | 0.172 | 0.172 | 0.169 | 0.171 | 0.175 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kołek, K.; Firlit, A.; Piątek, K.; Chmielowiec, K. Analysis of the Practical Implementation of Flicker Measurement Coprocessor for AMI Meters. Energies 2021, 14, 1589. https://doi.org/10.3390/en14061589

Kołek K, Firlit A, Piątek K, Chmielowiec K. Analysis of the Practical Implementation of Flicker Measurement Coprocessor for AMI Meters. Energies. 2021; 14(6):1589. https://doi.org/10.3390/en14061589

Chicago/Turabian StyleKołek, Krzysztof, Andrzej Firlit, Krzysztof Piątek, and Krzysztof Chmielowiec. 2021. "Analysis of the Practical Implementation of Flicker Measurement Coprocessor for AMI Meters" Energies 14, no. 6: 1589. https://doi.org/10.3390/en14061589

APA StyleKołek, K., Firlit, A., Piątek, K., & Chmielowiec, K. (2021). Analysis of the Practical Implementation of Flicker Measurement Coprocessor for AMI Meters. Energies, 14(6), 1589. https://doi.org/10.3390/en14061589