A Multilevel Inverter Topology Using Diode Half-Bridge Circuit with Reduced Power Component

Abstract

:1. Introduction

- (1)

- The number of switches is reduced, which further reduces the number of driver circuits and heat sinks.

- (2)

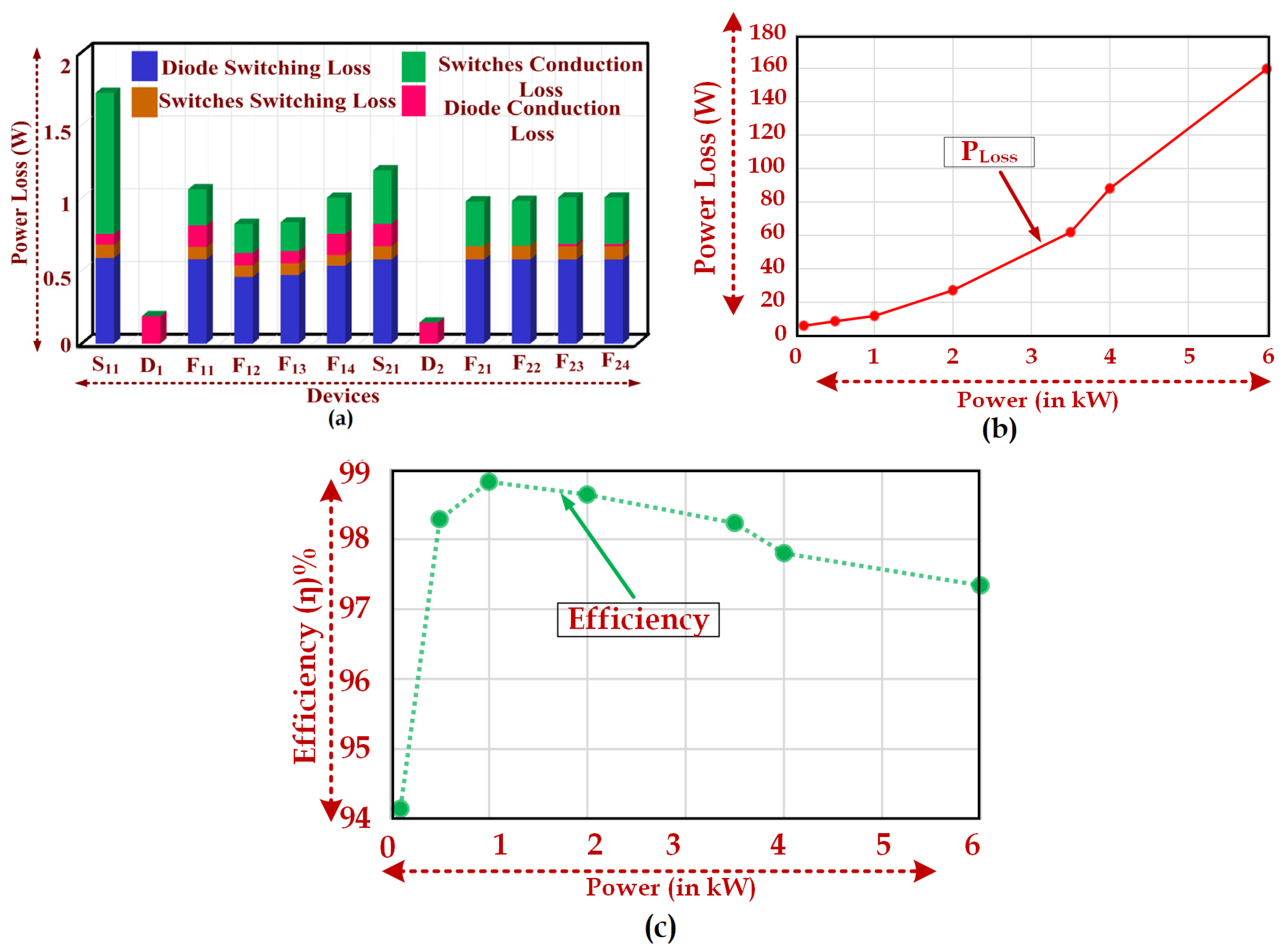

- Due to the reduction of the number of switches, the power loss is minimized.

- (3)

- The number of isolated dc sources is reduced.

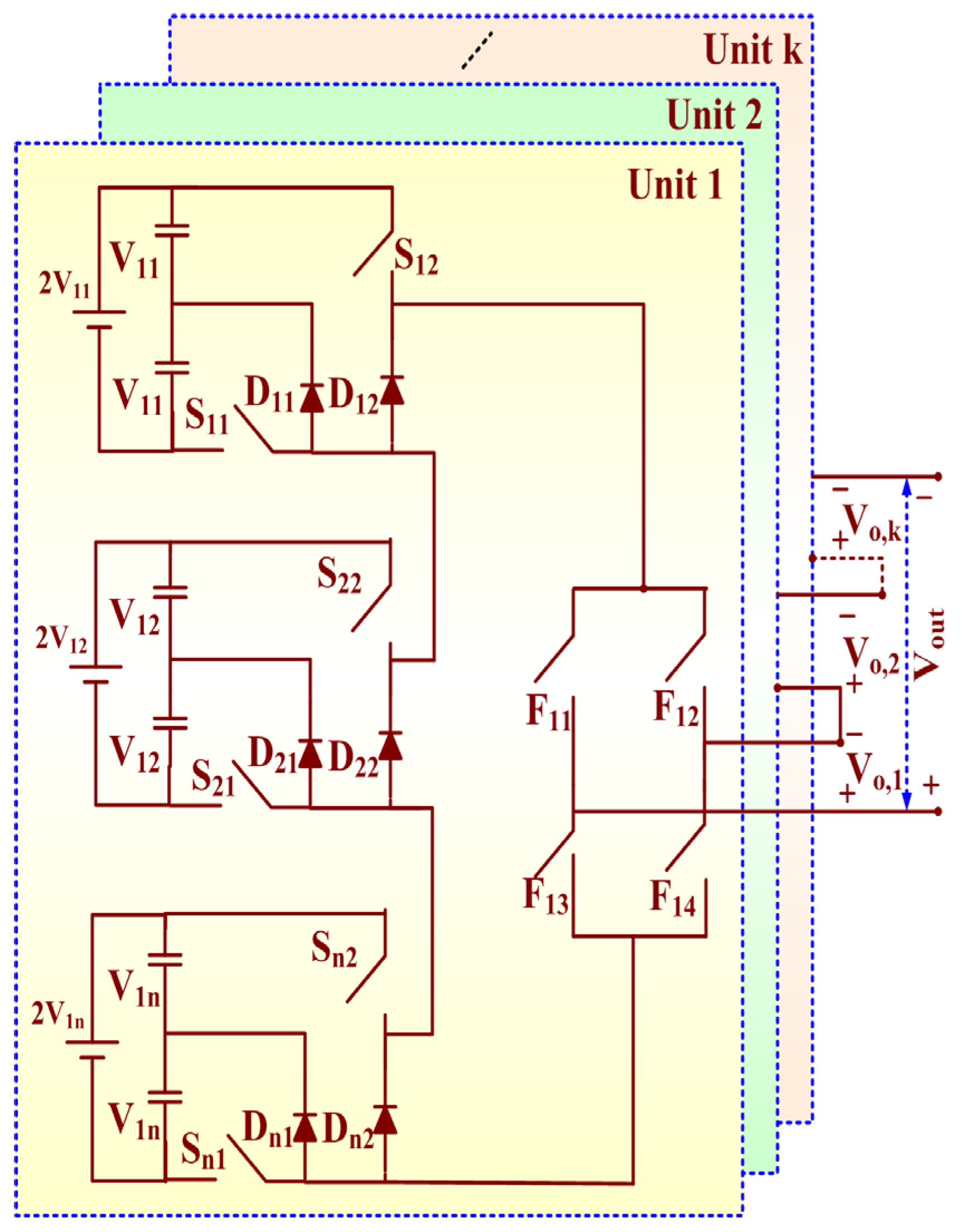

2. Proposed Multilevel Inverter Topology

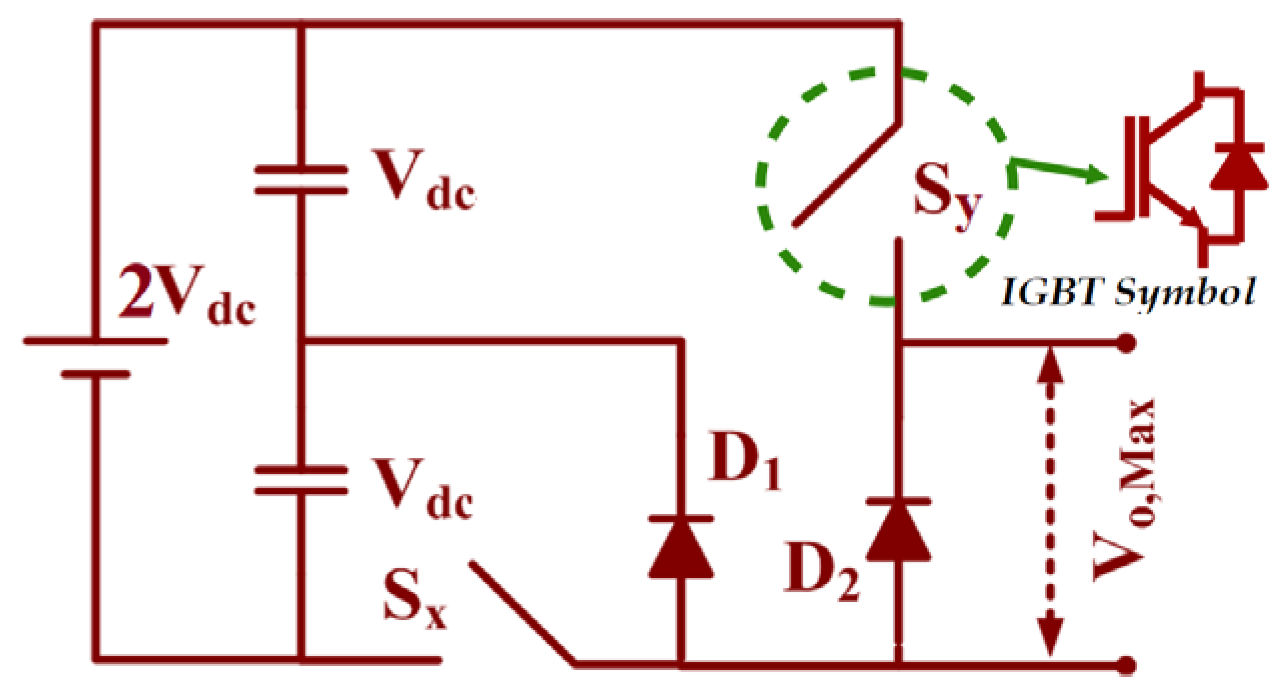

2.1. Symmetric Diode Half-Bridge (SDHB) Multilevel Inverter Topology

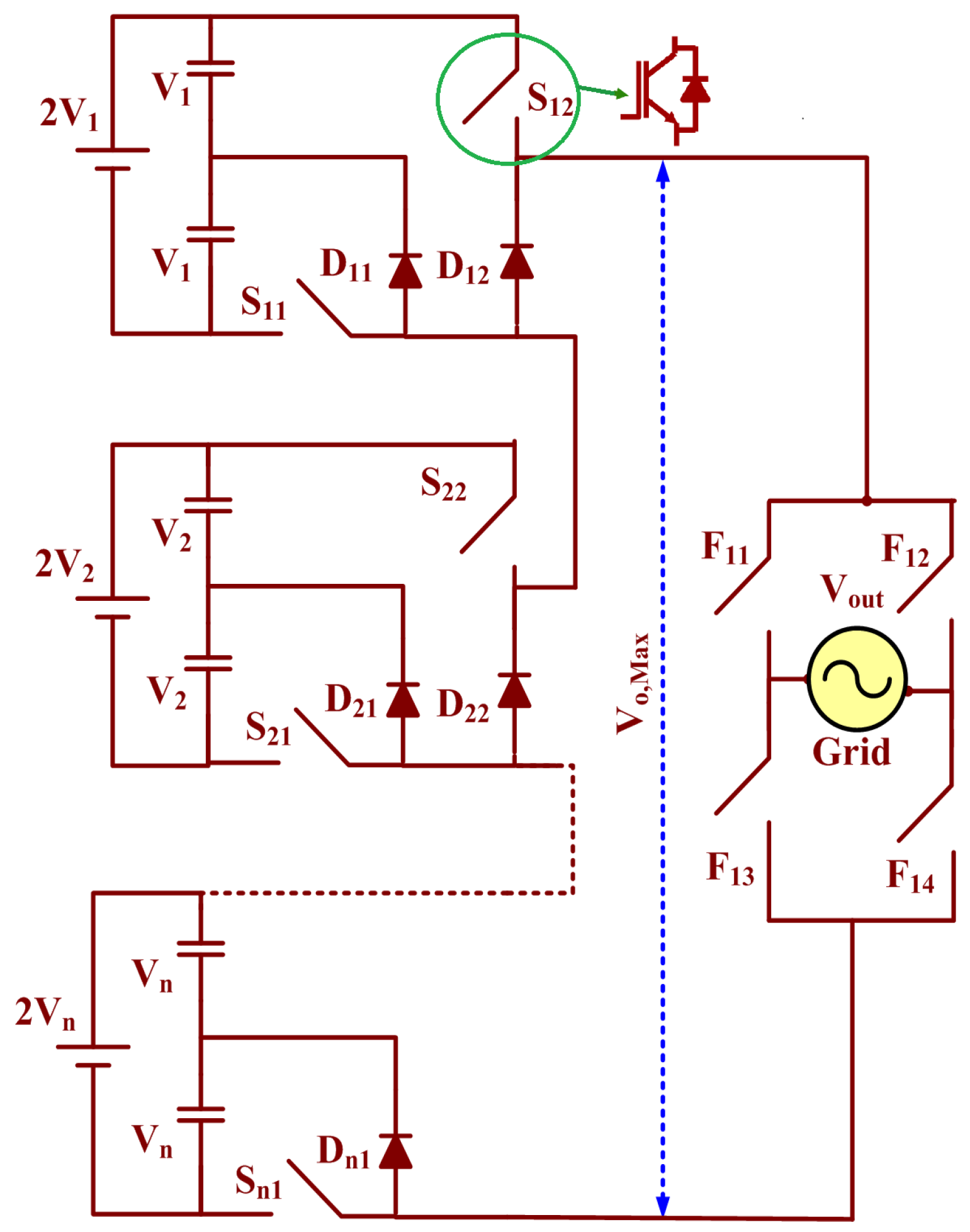

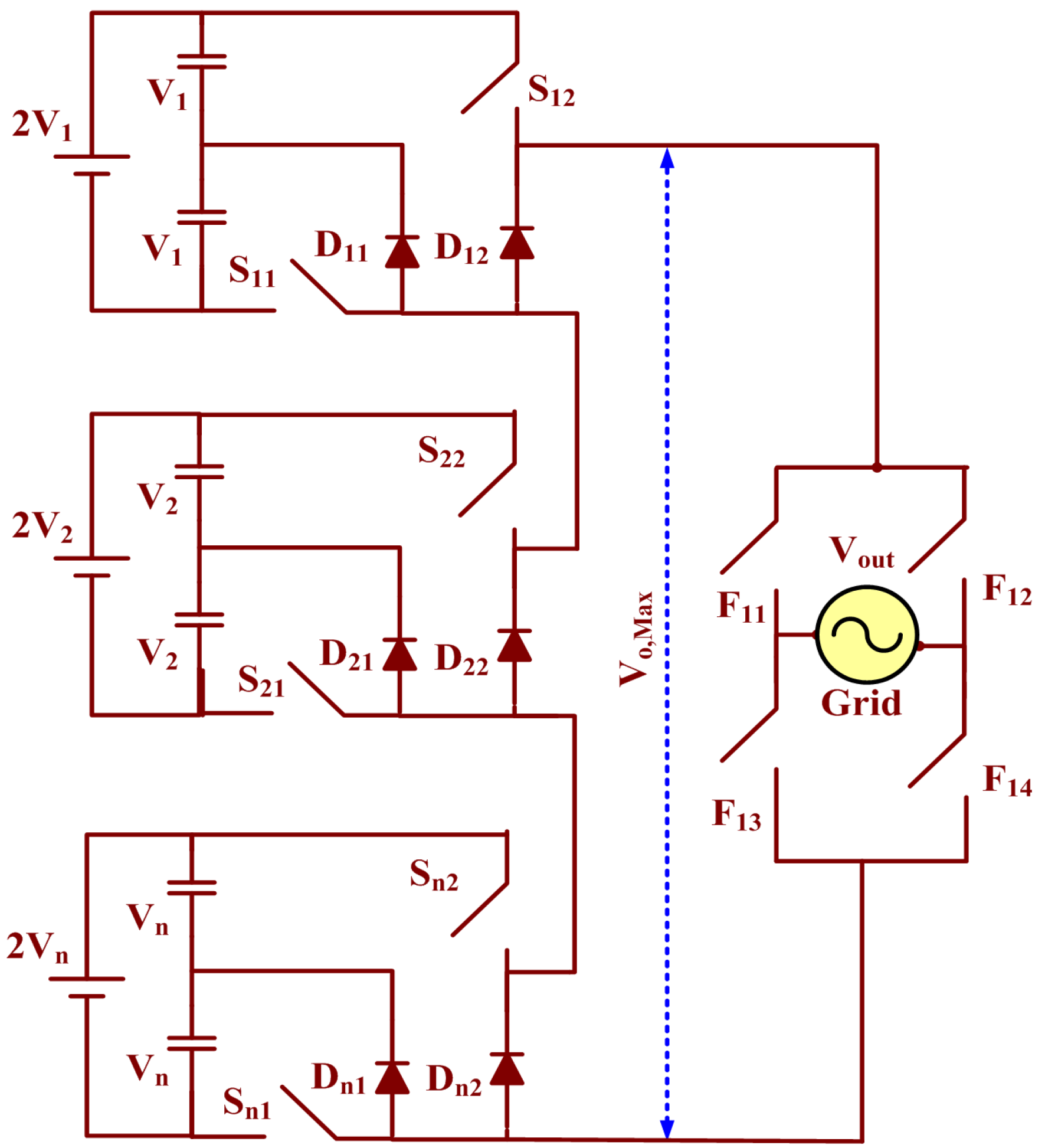

2.2. Asymmetric Diode Half-Bridge (ADHB) Multilevel Inverter Topology

3. Cascaded Asymmetric Diode Half-Bridge Multilevel Converter

3.1. The First Algorithm

3.2. The Second Algorithm

3.3. Total Blocking Voltage

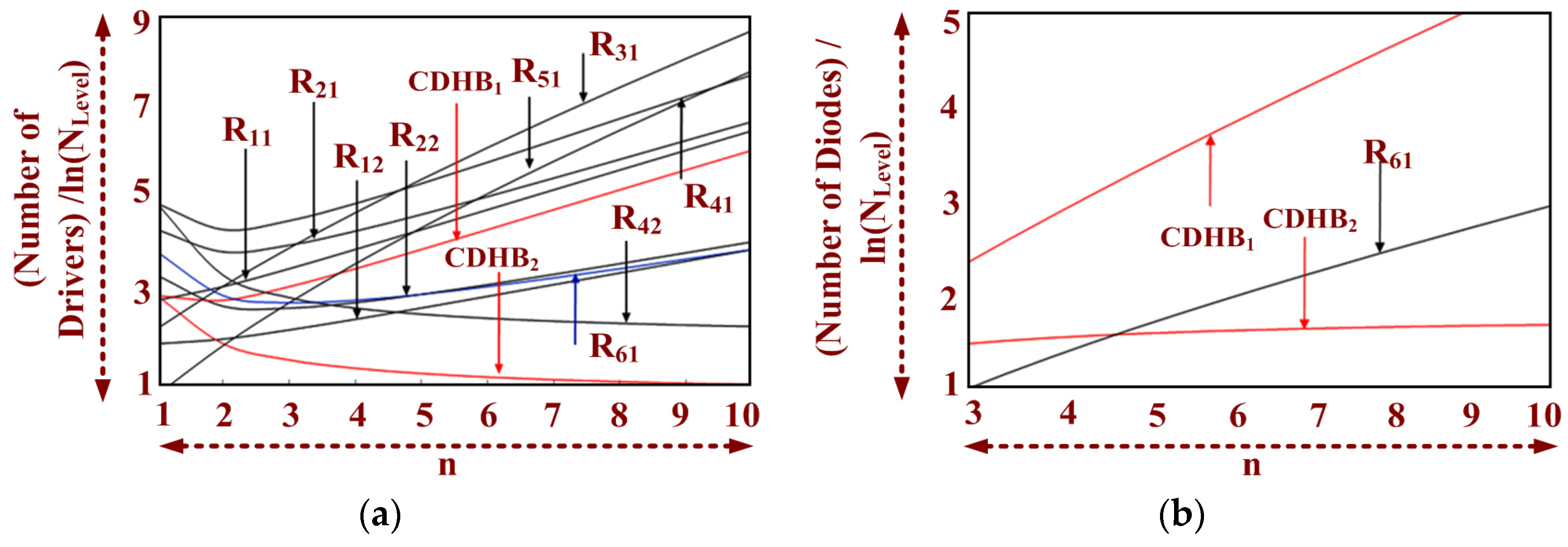

4. Optimal Topology of the Proposed Multilevel Converter

4.1. Number of Voltage Levels with a Constant Number of IGBTs

4.2. Number of IGBTs with a Constant Number of Voltage Levels

4.3. Number of Voltage Levels with a Constant Number of Sources

4.4. Number of Capacitors with a Constant Number of Voltage Levels

4.5. Number of Drivers with a Constant Number of Voltage Levels

4.6. Number of Diodes with a Constant Number of Voltage Levels

4.7. Blocking Voltage Rating with a Constant Number of Voltage Levels

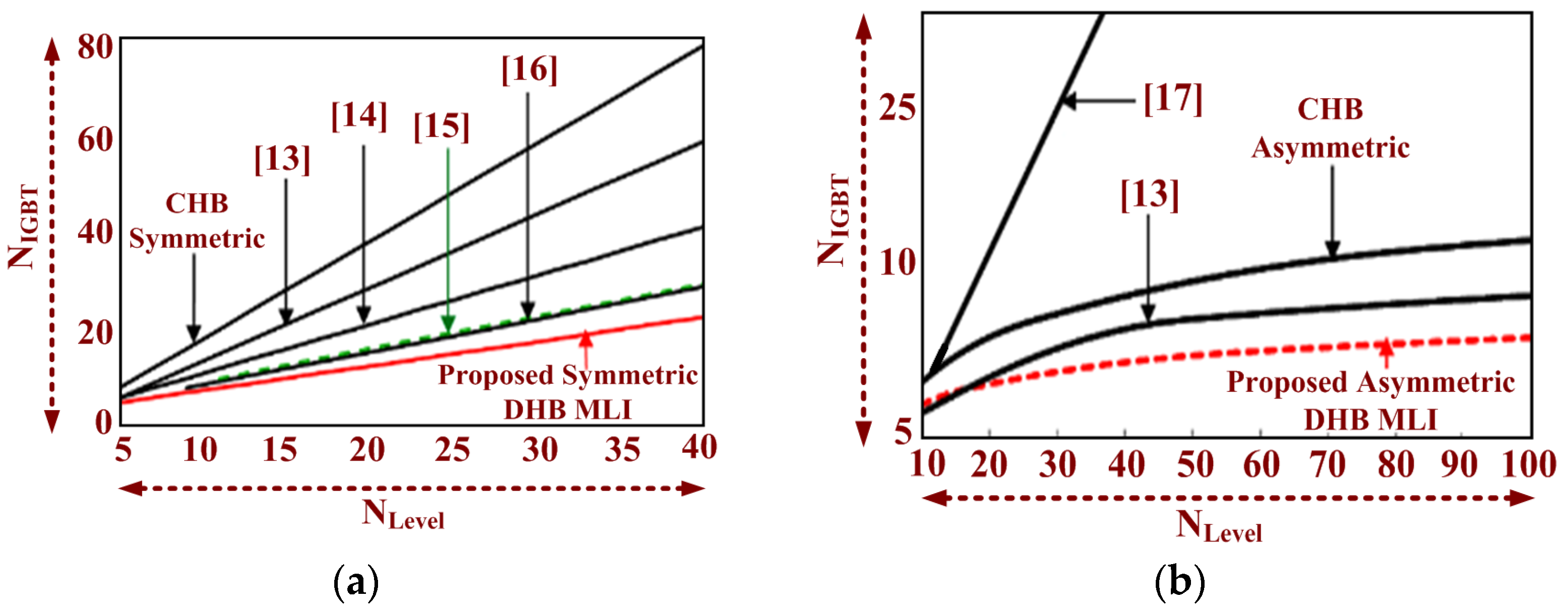

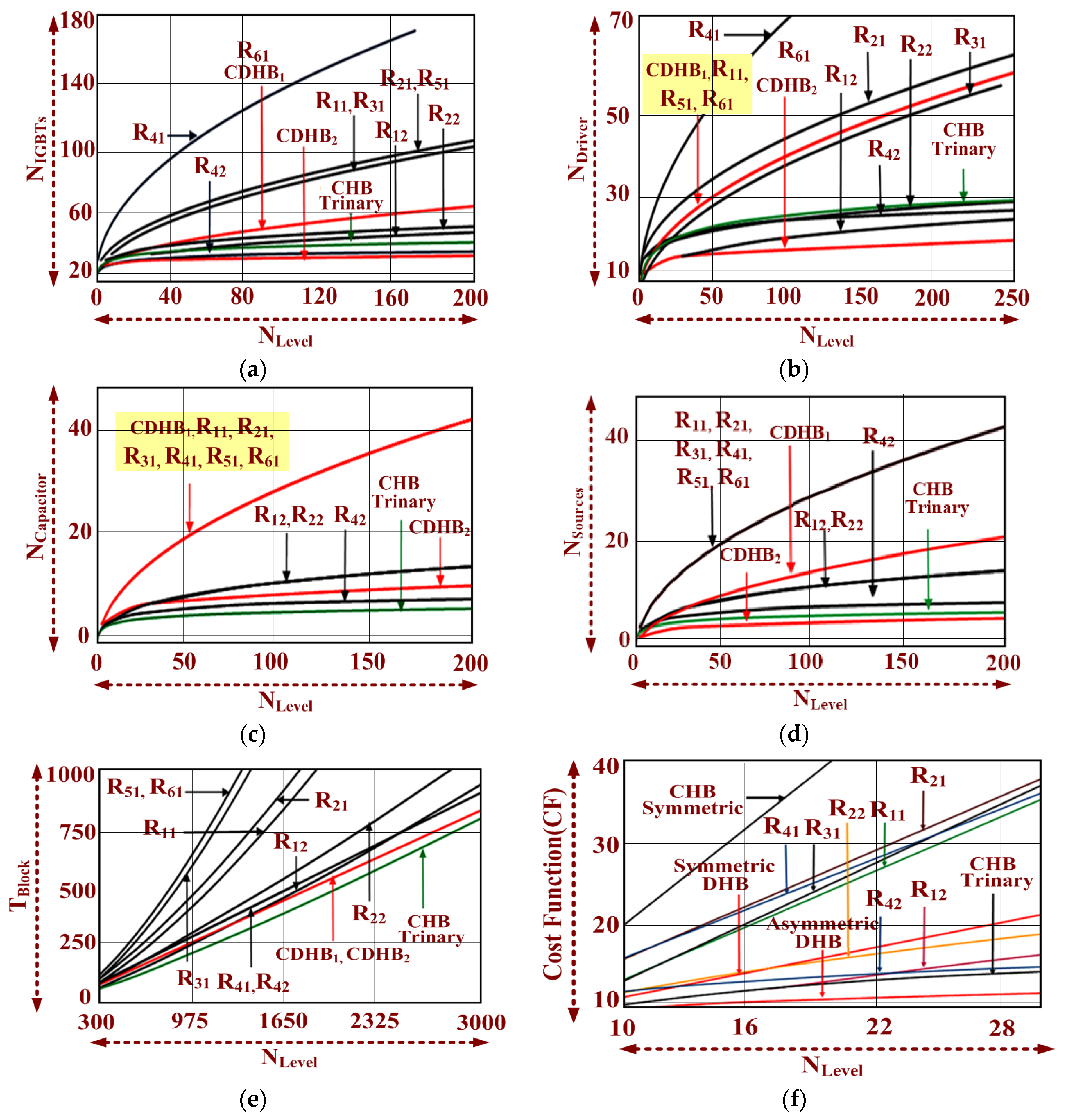

5. Comparative Study with Recent Cascaded Multilevel Inverter Topologies

5.1. The Required Number of IGBTs against the Number of Levels

5.2. The Required Number of Driver Circuits against the Number of Levels

5.3. The Required Number of Dc Sources/Capacitors Number of Levels

5.4. Total Blocking Voltage against the Number of Levels

5.5. Cost

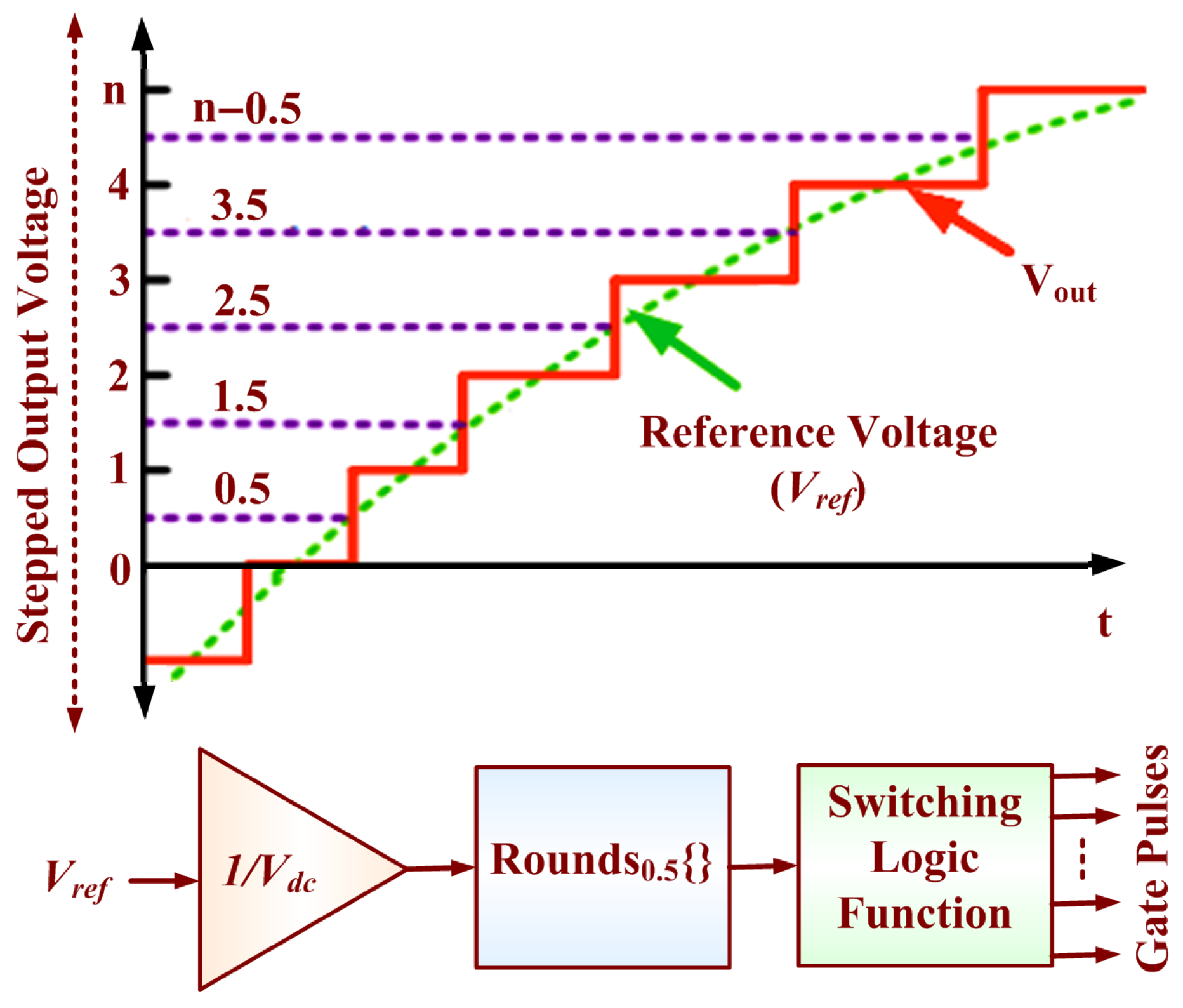

6. Nearest Level Modulation Technique

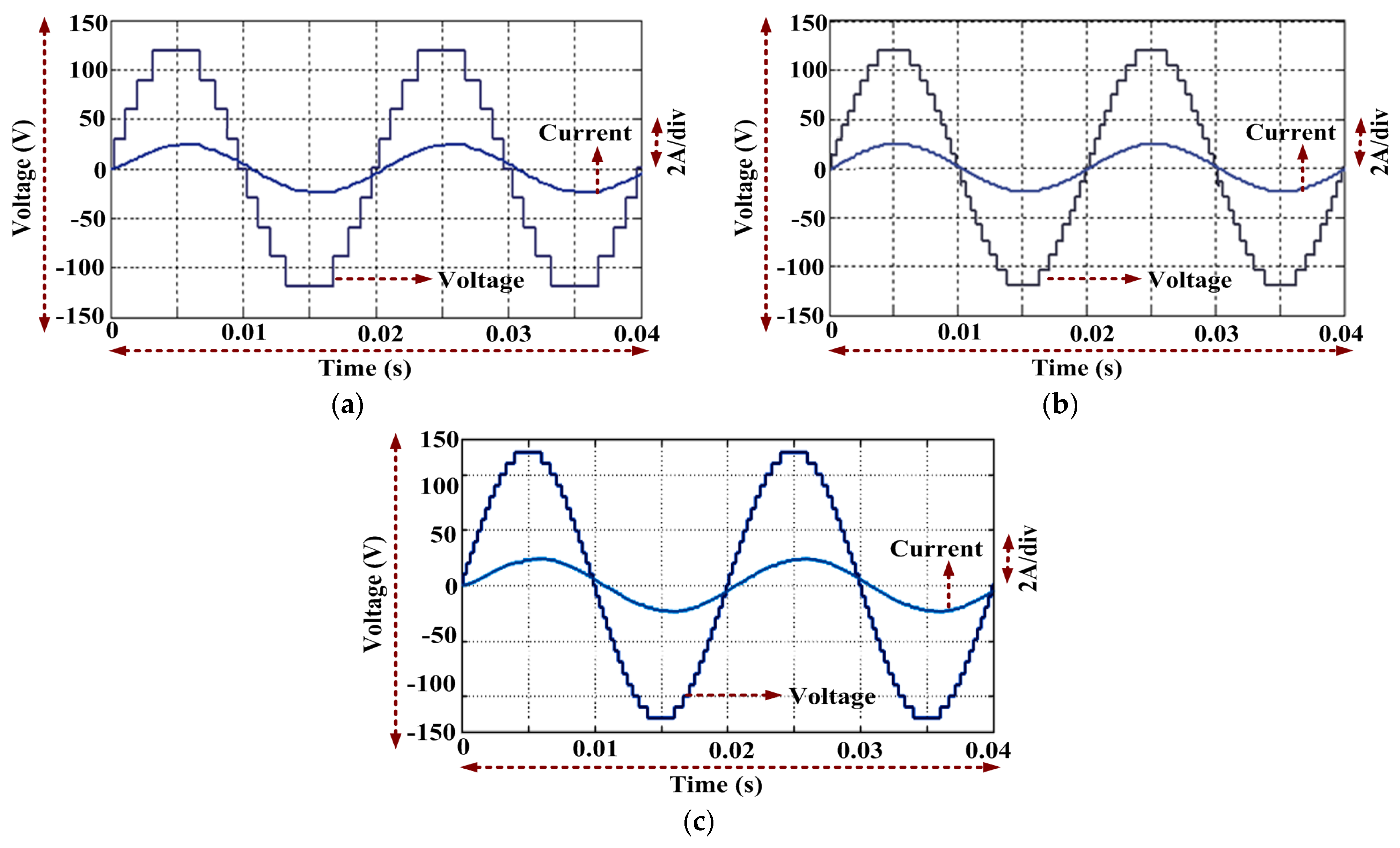

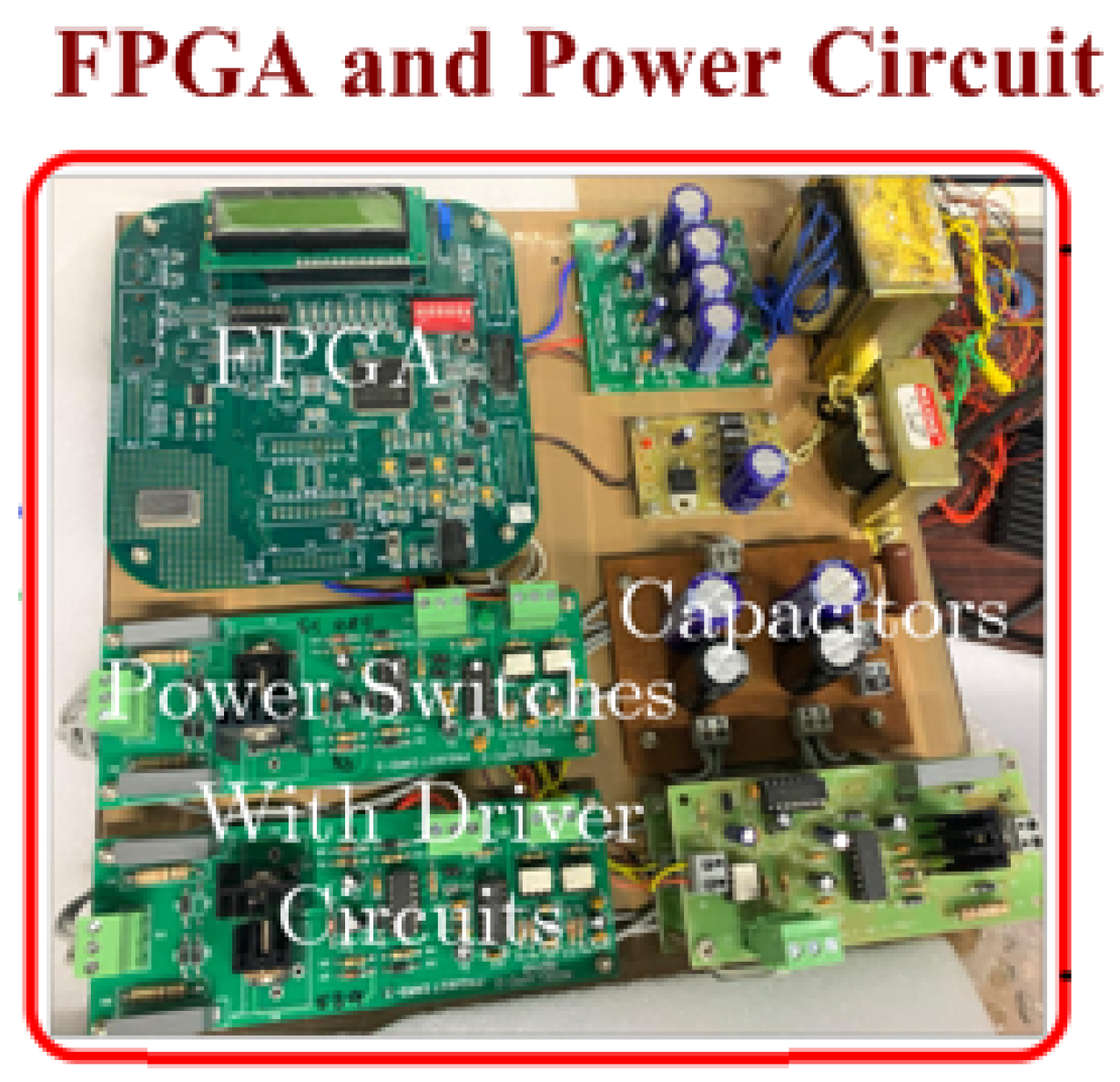

7. Experimental Test Results

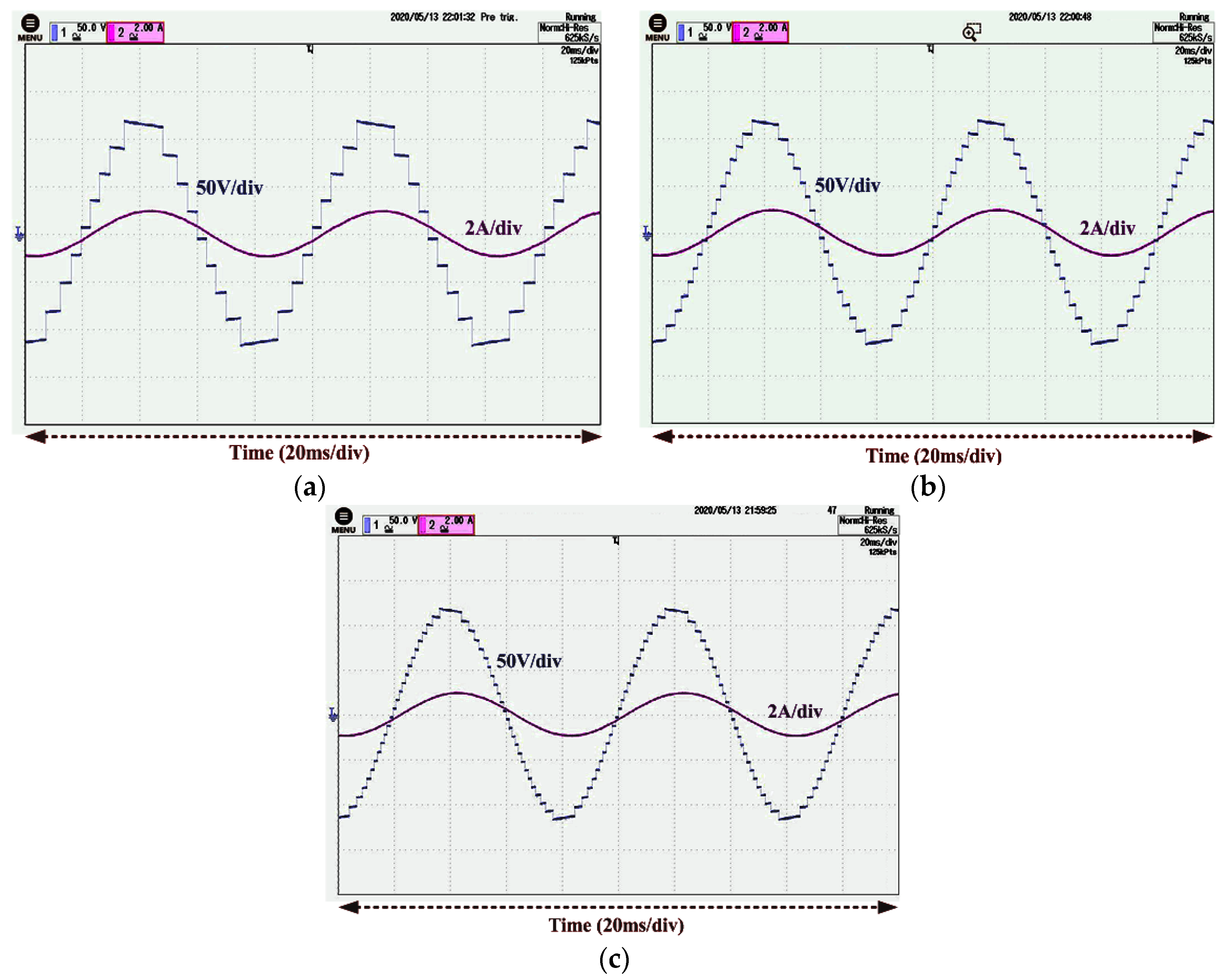

7.1. Symmetric Topology for 9-Level Inverter

7.2. Asymmetric Topology for 17-Level Inverter

7.3. Cascaded Asymmetric Structure for 25-Level Inverter

8. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Sathik, M.A.J.; Vijayakumar, K. An assessment of recent multilevel inverter topologies with reduced power electronics components for renewable applications. Rene. Sustain. Energy Rev. 2018, 82, 3379–3399. [Google Scholar]

- Ali, J.S.M.; Krishnasamy, V. Compact Switched-Capacitor Multilevel Inverter (CSCMLI) with Self-Voltage Balancing and Boosting Ability. IEEE Trans. Power Electron. 2019, 34, 4009–4013. [Google Scholar]

- Ali, J.S.M.; Alishah, R.S.; Krishnasamy, V. A New Generalized Multilevel Converter Topology with Reduced Voltage on Switches, Power losses, and Components. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 1094–1106. [Google Scholar]

- Sathik, J.; Aleem, S.H.E.A.; Kannan, R.; Zobaa, A. A new switched DC-link capacitor-based multi-level converter (SDC 2 MLC). Electr. Power Compon. Syst. 2017, 45, 1001–1015. [Google Scholar] [CrossRef] [Green Version]

- Shukla, A.; Ghosh, A.; Joshi, A. Hysteresis Current Control Operation of Flying Capacitor Multilevel Inverter and Its Application in Shunt Compensation of Distribution Systems. IEEE Trans. Power Deliv. 2007, 22, 396–405. [Google Scholar] [CrossRef] [Green Version]

- Memon, M.A.; Siddique, M.D.; Saad, M.; Mubin, M. Asynchronous Particle Swarm Optimization-Genetic Algorithm (APSO-GA) based Selective Harmonic Elimination in a Cascaded H-Bridge Multilevel Inverter. IEEE Trans. Ind. Electron. 2021. [Google Scholar] [CrossRef]

- Wu, S.; Qi, L.; Jia, W.; Zhu, Y.; Zhang, X.; Guo, X.; Pan, X. A Modular Multilevel Converter with Integrated Energy Dissipation Equipment for Offshore Wind VSC-HVDC System. IEEE Trans. Sustain. Energy 2021. [Google Scholar] [CrossRef]

- Newton, C.; Sumner, M. Multilevel converters: A real solution to medium high voltage drives? Inst. Electron. Eng. Power Eng. J. 1998, 12, 21–26. [Google Scholar] [CrossRef]

- Lai, J.-S.; Peng, F.Z. Multilevel converters—A new breed of power converters. IEEE Trans. Ind. Appl. 1996, 32, 509–517. [Google Scholar]

- Patil, K.V.; Mathur, R.M.; Jiang, J.; Hosseini, S.H. Distribution system compensation using a new binary multilevel voltage source inverter. IEEE Trans. Power Deliv. 1999, 14, 459–464. [Google Scholar] [CrossRef]

- Ali, J.S.M.; Alishah, R.S.; Sandeep, N.; Hosseini, S.H.; Babaei, E.; Vijayakumar, K.; Yaragatti, U.R. A New Generalized Multilevel Converter Topology Based on Cascaded Connection of Basic Units. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 2498–2512. [Google Scholar]

- Liu, Y.; Luo, F.L. Trinary hybrid 81-level multilevel inverter for motor drive with zero common-mode voltage. IEEE Trans. Ind. Electron. 2008, 55, 1014–1021. [Google Scholar] [CrossRef]

- Mokhberdoran, A.; Ajami, A. Symmetric and asymmetric design and implementation of new cascaded multilevel inverter topology. IEEE Trans. Power Electron. 2014, 29, 6712–6724. [Google Scholar] [CrossRef]

- Kangarlu, M.F.; Babaei, E.; Laali, S. Symmetric multilevel inverter with reduced components based on non-insulated DC voltage sources. IET Power Electron. 2012, 5, 571–581. [Google Scholar] [CrossRef]

- Oskuee, M.R.J.; Karimi, M.; Ravadanegh, S.N.; Gharehpetian, G.B. An Innovative Scheme of Symmetric Multilevel Voltage Source Inverter with Lower Number of Circuit Devices. IEEE Trans. Ind. Electron. 2015, 62, 6965–6973. [Google Scholar] [CrossRef]

- Oskuee, M.R.J.; Salary, E.; Najafi-Ravadanegh, S. Creative design of symmetric multilevel converter to enhance the circuit’s performance. IET Power Electron. 2015, 8, 96–102. [Google Scholar] [CrossRef]

- Samadaei, E.; Gholamian, S.A.; Sheikholeslami, A.; Adabi, J. An envelope type (E-Type) module: Asymmetric multilevel inverters with reduced components. IEEE Trans. Ind. Electron. 2016, 63, 7148–7156. [Google Scholar] [CrossRef]

- Alishah, R.S.; Hosseini, S.H.; Babaei, E.; Sabahi, M. Optimal design of new cascaded switch-ladder multilevel inverter structure. IEEE Trans. Ind. Electron. 2017, 64, 2072–2080. [Google Scholar] [CrossRef]

- Alishah, R.S.; Hosseini, S.H.; Babaei, E.; Sabahi, M. A new general multilevel converter topology based on cascaded connection of submultilevel units with reduced switching components, DC sources, and blocked voltage by switches. IEEE Trans. Ind. Electron. 2016, 63, 7157–7164. [Google Scholar] [CrossRef]

- Alishah, R.S.; Nazarpour, D.; Hosseini, S.H.; Sabahi, M. Reduction of power electronic elements in multilevel converters using a new cascade structure. IEEE Trans. Ind. Electron. 2015, 62, 256–269. [Google Scholar] [CrossRef]

- Ebrahimi, J.; Babaei, E.; Gharehpetian, G.B. A new topology of cascaded multilevel converters with reduced number of components for high-voltage applications. IEEE Trans. Power Electron. 2011, 26, 3109–3118. [Google Scholar] [CrossRef]

- Ebrahimi, J.; Babaei, E.; Gharehpetian, G.B. A new multilevel converter topology with reduced number of power electronic components. IEEE Trans. Ind. Electron. 2012, 59, 655–667. [Google Scholar] [CrossRef]

- Samanbakhsh, R.; Taheri, A. Reduction of power electronic components in multilevel converters using new switched capacitor-diode structure. IEEE Trans. Ind. Electron. 2016, 63, 7204–7214. [Google Scholar] [CrossRef]

- Prabaharan, N.; Salam, Z.; Cecati, C.; Palanisamy, K. Design and implementation of new multilevel inverter topology for trinary sequence using unipolar pulse width modulation. IEEE Trans. Ind. Electron. 2020, 67, 3573–3582. [Google Scholar] [CrossRef]

- Rosas-Caro, J.C.; Ramirez, J.M.; Peng, F.Z.; Valderrabano, A. A DC–DC multilevel boost converter. IET Power Electron. 2010, 3, 129–137. [Google Scholar] [CrossRef]

- Taheri, A.; Rasulkhani, A.; Ren, H.-P. An Asymmetric Switched Capacitor Multilevel Inverter with Component Reduction. IEEE Access 2019, 7, 127166–127176. [Google Scholar] [CrossRef]

- Zaid, M.M.; Ro, J.-S. Switch Ladder Modified H-Bridge Multilevel Inverter with Novel Pulse Width Modulation Technique. IEEE Access 2019, 7, 102073–102086. [Google Scholar] [CrossRef]

- Siddique, M.D.; Mekhilef, S.; Shah, N.M.; Sarwar, A.; Iqbal, A.; Tayyab, M.; Ansari, M.K. Low Switching Frequency Based Asymmetrical Multilevel Inverter Topology with Reduced Switch Count. IEEE Access 2019, 7, 86374–86383. [Google Scholar] [CrossRef]

- Dhanamjayulu, C.; Meikandasivam, S. Implementation and Comparison of Symmetric and Asymmetric Multilevel Inverters for Dynamic Loads. IEEE Access 2018, 6, 738–746. [Google Scholar] [CrossRef]

- Almakhles, D.J.; Ali, J.S.M.; Padmanaban, S.; Bhaskar, M.S.; Subramaniam, U.; Sakthivel, R. An Original Hybrid Multilevel DC-AC Converter Using Single-Double Source Unit for Medium Voltage Applications: Hardware Implementation and Investigation. IEEE Access 2020, 8, 71291–71301. [Google Scholar] [CrossRef]

- Meraj, S.T.; Hasan, K.; Masaoud, A. A Novel Configuration of Cross-Switched T-Type (CT-Type) Multilevel Inverter. IEEE Trans. Power Electron. 2019, 35, 3688–3696. [Google Scholar] [CrossRef]

- Panda, K.P.; Bana, P.R.; Panda, G. FPA Optimized Selective Harmonic Elimination in Symmetric–Asymmetric Reduced Switch Cascaded Multilevel Inverter. IEEE Trans. Ind. Appl. 2020, 56, 2862–2870. [Google Scholar] [CrossRef]

- Ali, S.; Ling, Z.; Tian, K.; Huang, Z. Recent Advancements in Submodule Topologies and Applications of MMC. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 3407–3435. [Google Scholar] [CrossRef]

- Deng, F.; Lü, Y.; Liu, C.; Heng, Q.; Yu, Q.; Zhao, J. Overview on submodule topologies, modeling, modulation, control schemes, fault diagnosis, and tolerant control strategies of modular multilevel converters. Chin. J. Electr. Eng. 2020, 6, 1–21. [Google Scholar] [CrossRef]

- Wang, K.; Zhou, L.; Deng, Y.; Lu, Y.; Wang, C.; Xu, F. Application range analysis and implementation of the logic-processed CPS-PWM scheme based mmc capacitor voltage balancing strategy. CPSS Trans. Power Electron. Appl. 2019, 4, 1–9. [Google Scholar] [CrossRef]

- Joshi, S.D.; Ghat, M.B.; Shukla, A.; Chandorkar, M.C. Improved Balancing and Sensing of Submodule Capacitor Voltages in Modular Multilevel Converter. IEEE Trans. Ind. Appl. 2021, 57, 537–548. [Google Scholar] [CrossRef]

- Zhao, J.; Kong, C.; Liu, T.; Li, R. Research on an Auto-Optimized Capacitor Voltage Balancing Control Strategy of MMC SM for Renewable Energy HVDC Transmission System. Electronics 2019, 8, 104. [Google Scholar] [CrossRef] [Green Version]

- Lara, J.; Masisi, L.; Hernandez, C.; Arjona, M.A.; Chandra, A. Novel Single-Phase Grid-Tied NPC Five-Level Converter with an Inherent DC-Link Voltage Balancing Strategy for Power Quality Improvement. Energies 2021, 14, 2644. [Google Scholar] [CrossRef]

| State | Sx | D1 | Sy | Voltage (Vo,max) |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | Vdc |

| 2 | 1 | 0 | 1 | 2Vdc |

| State | ON/OFF State Switches | Output Voltage | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| S11 | S21 | S31 | … | S12 | S22 | … | Sn1 | F11 | F13 | ||

| 0 | 0 | 0 | 0 | … | 0 | 0 | … | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | … | 0 | 0 | … | 0 | 1 | 1 | +Vn |

| 2 | 0 | 0 | 0 | … | 0 | 0 | … | 1 | 1 | 1 | +2Vn |

| … | … | … | … | … | … | … | … | … | … | … | … |

| n − 1 | 0 | 1 | 1 | … | 1 | 1 | … | 1 | 1 | 1 | 2 |

| n | 1 | 1 | 1 | … | 1 | 1 | … | 1 | 1 | 1 | 2 |

| State | ON/OFF State Switches | Output Voltage | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| S11 | S21 | S31 | … | S12 | S22 | … | Sn1 | F11 | F13 | ||

| 0 | 0 | 0 | 0 | … | 0 | 0 | … | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | … | 1 | 0 | … | 0 | 1 | 1 | +Vn |

| 2 | 1 | 0 | 0 | … | 1 | 0 | … | 0 | 1 | 1 | +2Vn |

| 3 | 0 | 0 | 0 | 0 | 1 | … | 0 | 1 | 1 | +3Vn | |

| … | … | … | … | … | … | … | … | … | … | … | … |

| n − 1 | 0 | 1 | 1 | … | 1 | 1 | … | 1 | 1 | 1 | 2 |

| n | 1 | 1 | 1 | … | 1 | 1 | … | 1 | 1 | 1 | 2 |

| Topologies | NLevel | NSwitches | NDiode | NDriver | MBlock | TBlock | Efficiency (%) | Voltage THD (%) |

|---|---|---|---|---|---|---|---|---|

| Proposed | 9 | 7 | 3 | 7 | 4Vdc | 20Vdc | 94.50% | 9.07% |

| 17 | 8 | 4 | 8 | 8 Vdc | 44Vdc | 94.76% | 4.76% | |

| 25 | 10 | 4 | 10 | 10Vdc | 66Vdc | 95.10% | 3.10% | |

| [12] | 17 | 10 | - | 10 | 8Vdc | 36Vdc | 93.91% | 6.17% |

| [27] | 25 | 10 | 16 | 10 | 12Vdc | 70Vdc | 99.7% | 3.25% |

| [28] | 17 | 8 | 8 | 8 | 8Vdc | 36Vdc | 98.5% | 6.8% |

| [29] | 25 | 14 | - | 11 | 12Vdc | 76Vdc | NA | NA |

| [30] | 17 | 10 | 8 | 10 | 8Vdc | 36Vdc | 96.7% | 5.41% |

| Description | Symmetric | Asymmetric | Cascaded | |

|---|---|---|---|---|

| VBlock in volts | 120 | 120 | 100 | |

| Number of switches | 8 | 8 | 10 | |

| Number of driver circuit | 8 | 8 | 10 | |

| Variety of dc source | 1 | 2 | 2 | |

| Nsource/Ncapacitors | 2/4 | 2/4 | 2/4 | |

| Number of levels | 9 | 17 | 25 | |

| Voltage THD (%) | Experimental | 9.07% | 4.76% | 3.10% |

| Simulation | 8.78% | 4.69% | 2.97% | |

| Number | Nswitch | VBlock (V) | NLevel | TBlock (V) | Nsource/Ncapacitor | NSub | η (%) |

|---|---|---|---|---|---|---|---|

| 1 | 6 | 2 | 5 | 11 | 1/2 | 1 | 88.12 |

| 2 | 8 | 4 | 9 | 22 | 2/4 | 1 | 88.9 |

| 3 | 8 | 8 | 17 | 44 | 2/4 | 1 | 89.46 |

| 4 | 12 | 10 | 25 | 66 | 2/4 | 2 | 89.97 |

| 5 | 14 | 34 | 85 | 231 | 3/6 | 2 | 90.11 |

| 6 | 14 | 40 | 85 | 231 | 3/6 | 2 | 90.37 |

| 7 | 18 | 50 | 125 | 341 | 3/6 | 3 | 90.23 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sathik, J.; Aleem, S.H.E.A.; Shalchi Alishah, R.; Almakhles, D.; Bertilsson, K.; Bhaskar, M.S.; Fernandez Savier, G.; Dhandapani, K. A Multilevel Inverter Topology Using Diode Half-Bridge Circuit with Reduced Power Component. Energies 2021, 14, 7249. https://doi.org/10.3390/en14217249

Sathik J, Aleem SHEA, Shalchi Alishah R, Almakhles D, Bertilsson K, Bhaskar MS, Fernandez Savier G, Dhandapani K. A Multilevel Inverter Topology Using Diode Half-Bridge Circuit with Reduced Power Component. Energies. 2021; 14(21):7249. https://doi.org/10.3390/en14217249

Chicago/Turabian StyleSathik, Jagabar, Shady H. E. Abdel Aleem, Rasoul Shalchi Alishah, Dhafer Almakhles, Kent Bertilsson, Mahajan Sagar Bhaskar, George Fernandez Savier, and Karthikeyan Dhandapani. 2021. "A Multilevel Inverter Topology Using Diode Half-Bridge Circuit with Reduced Power Component" Energies 14, no. 21: 7249. https://doi.org/10.3390/en14217249

APA StyleSathik, J., Aleem, S. H. E. A., Shalchi Alishah, R., Almakhles, D., Bertilsson, K., Bhaskar, M. S., Fernandez Savier, G., & Dhandapani, K. (2021). A Multilevel Inverter Topology Using Diode Half-Bridge Circuit with Reduced Power Component. Energies, 14(21), 7249. https://doi.org/10.3390/en14217249