Enhanced Boost Factor for Three-Level Quasi-Switched Boost T-Type Inverter

Abstract

:1. Introduction

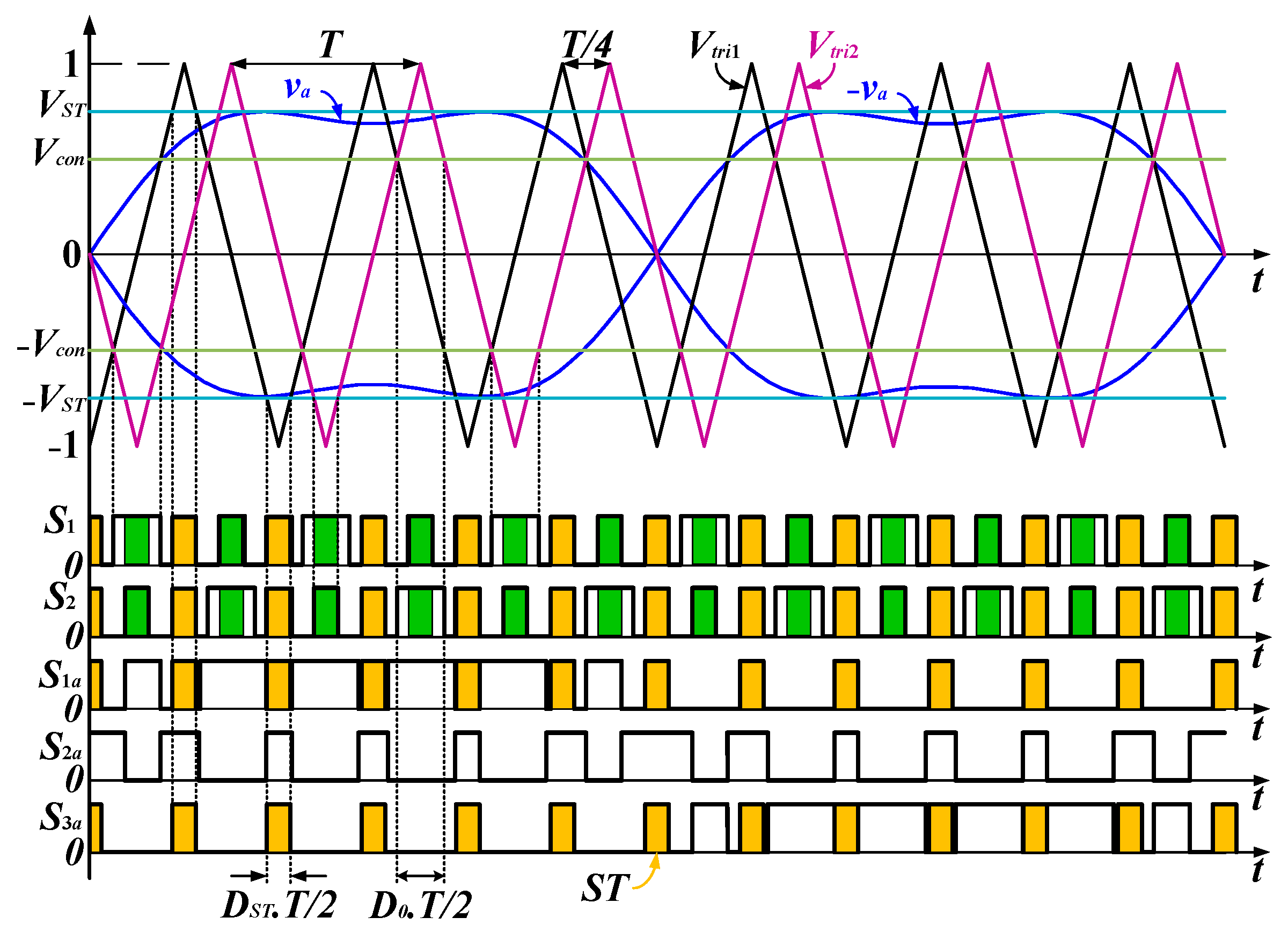

2. Proposed PWM Scheme for 3L-qSBT2I

2.1. PWM Signal Generation

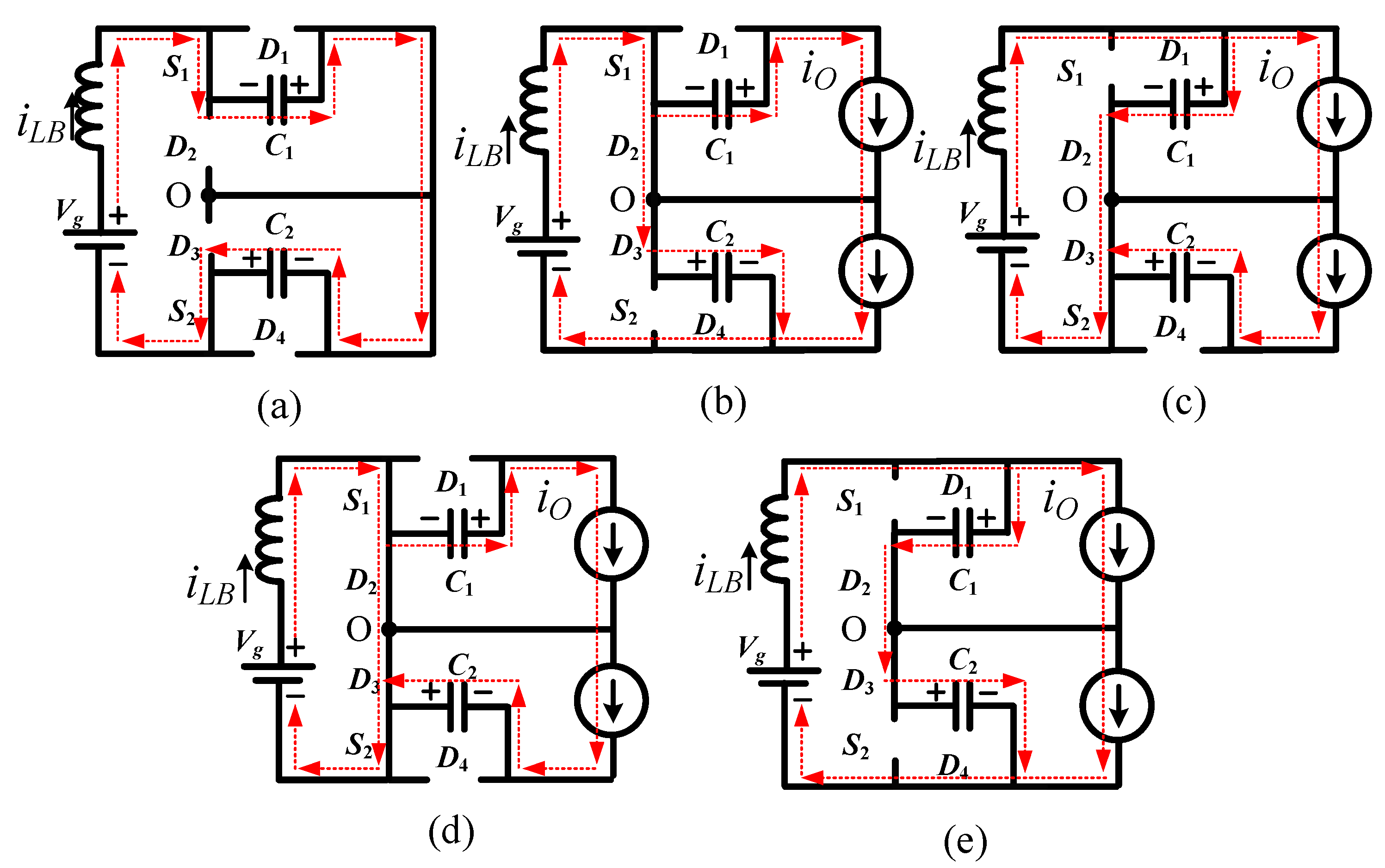

2.2. Operating Modes

2.3. Steady-State Analysis

2.4. Parameter Selection

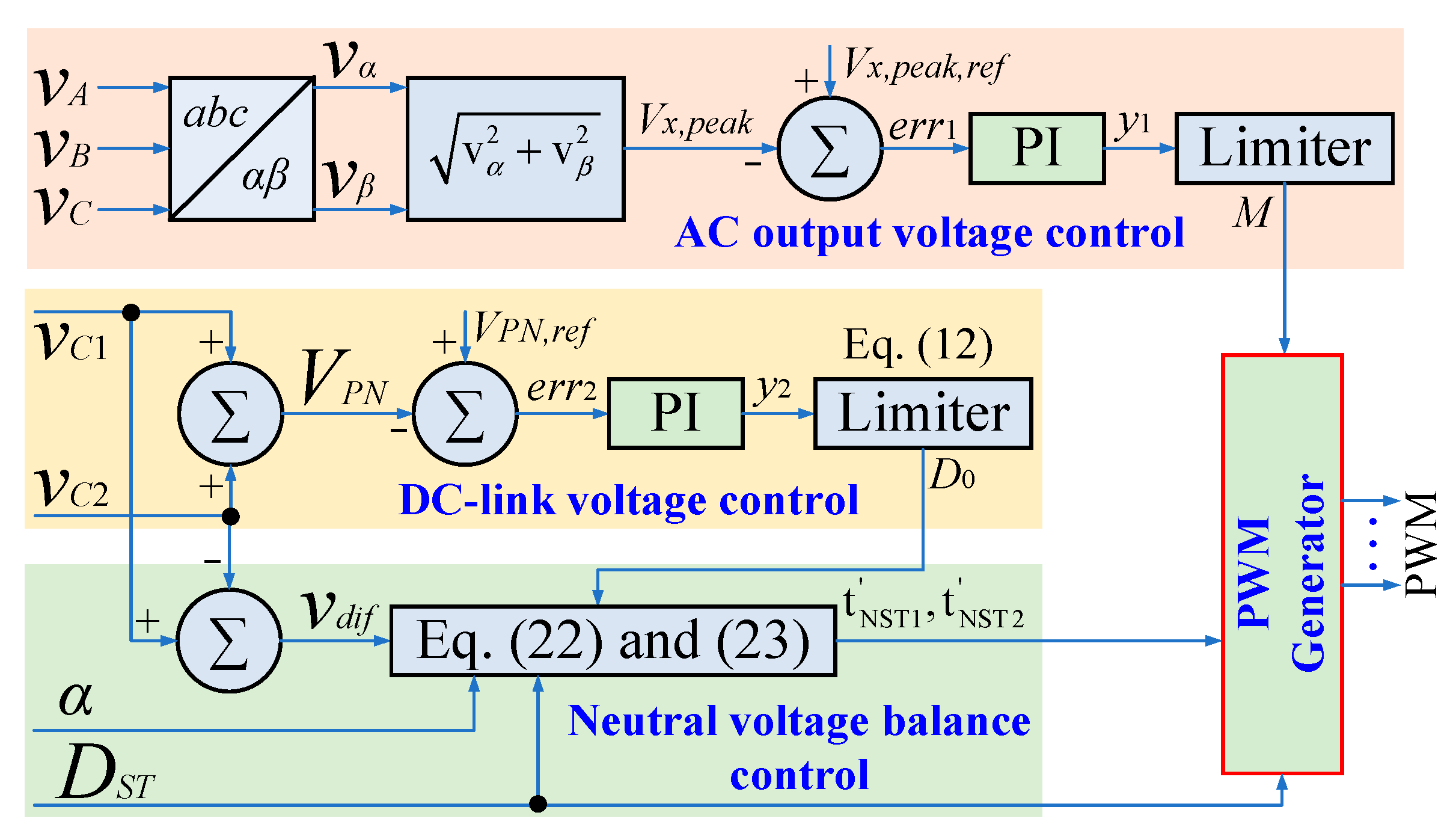

3. Proposed Capacitor Voltage Balance Scheme and DC-Link Voltage Control

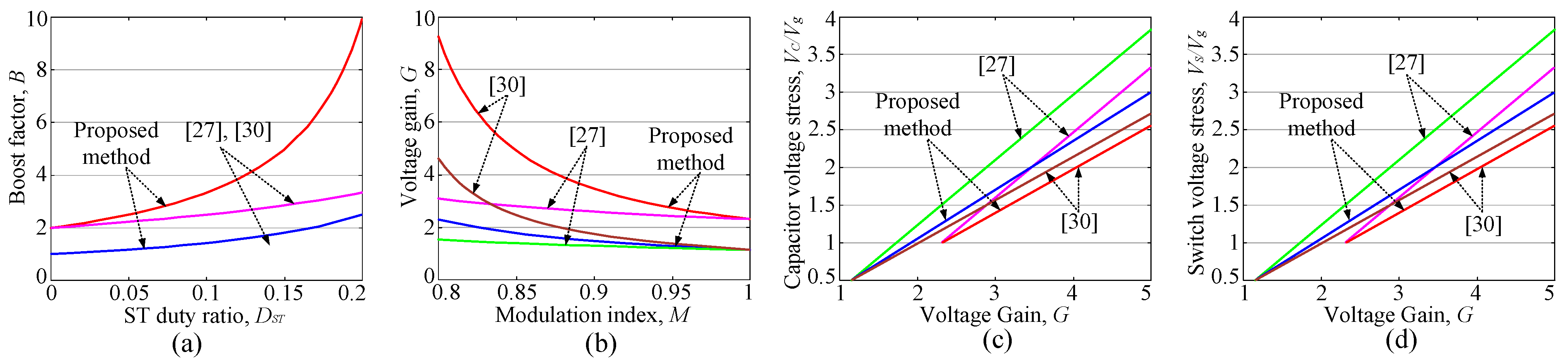

4. Comparative Study

5. Simulation and Experimental Verifications

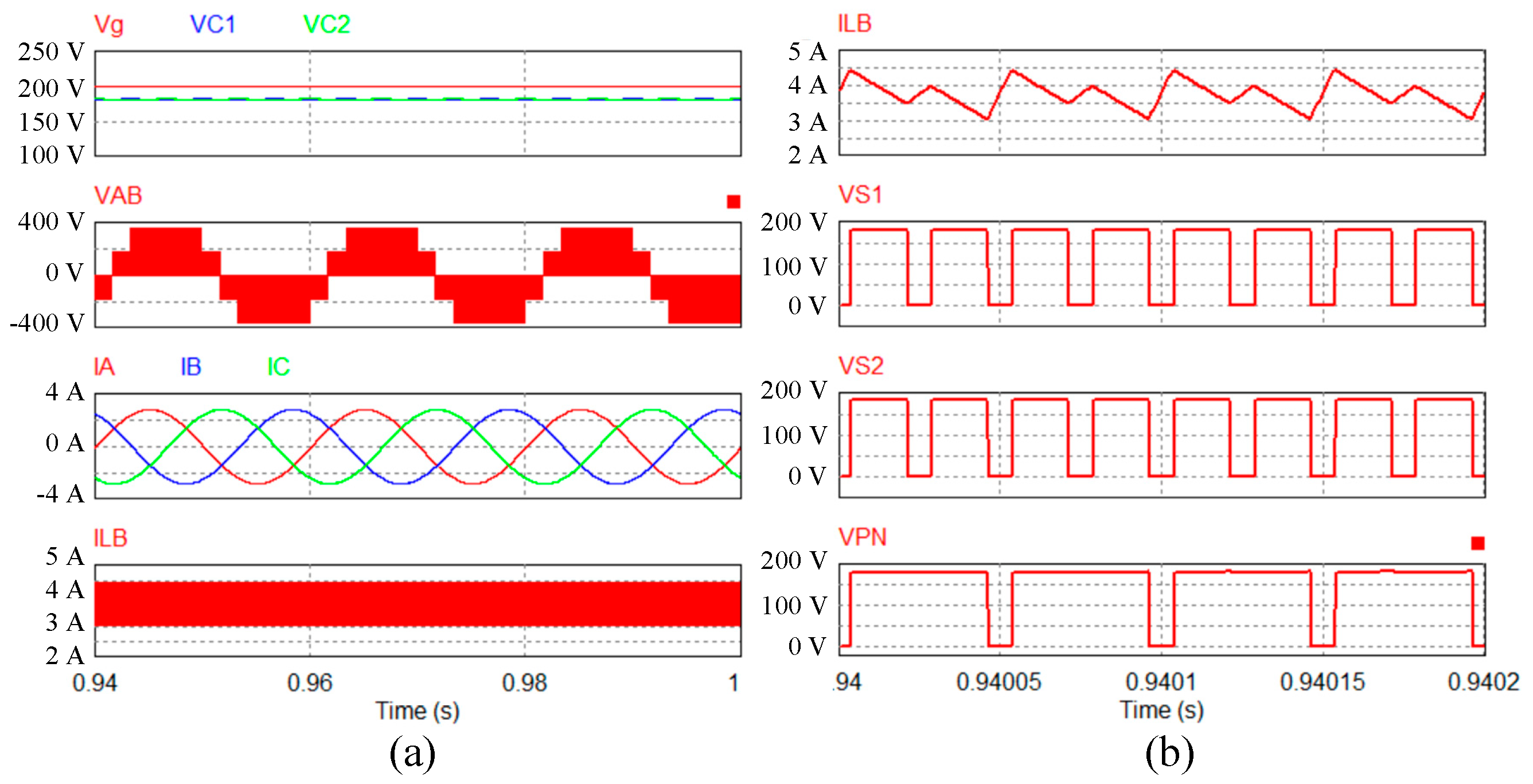

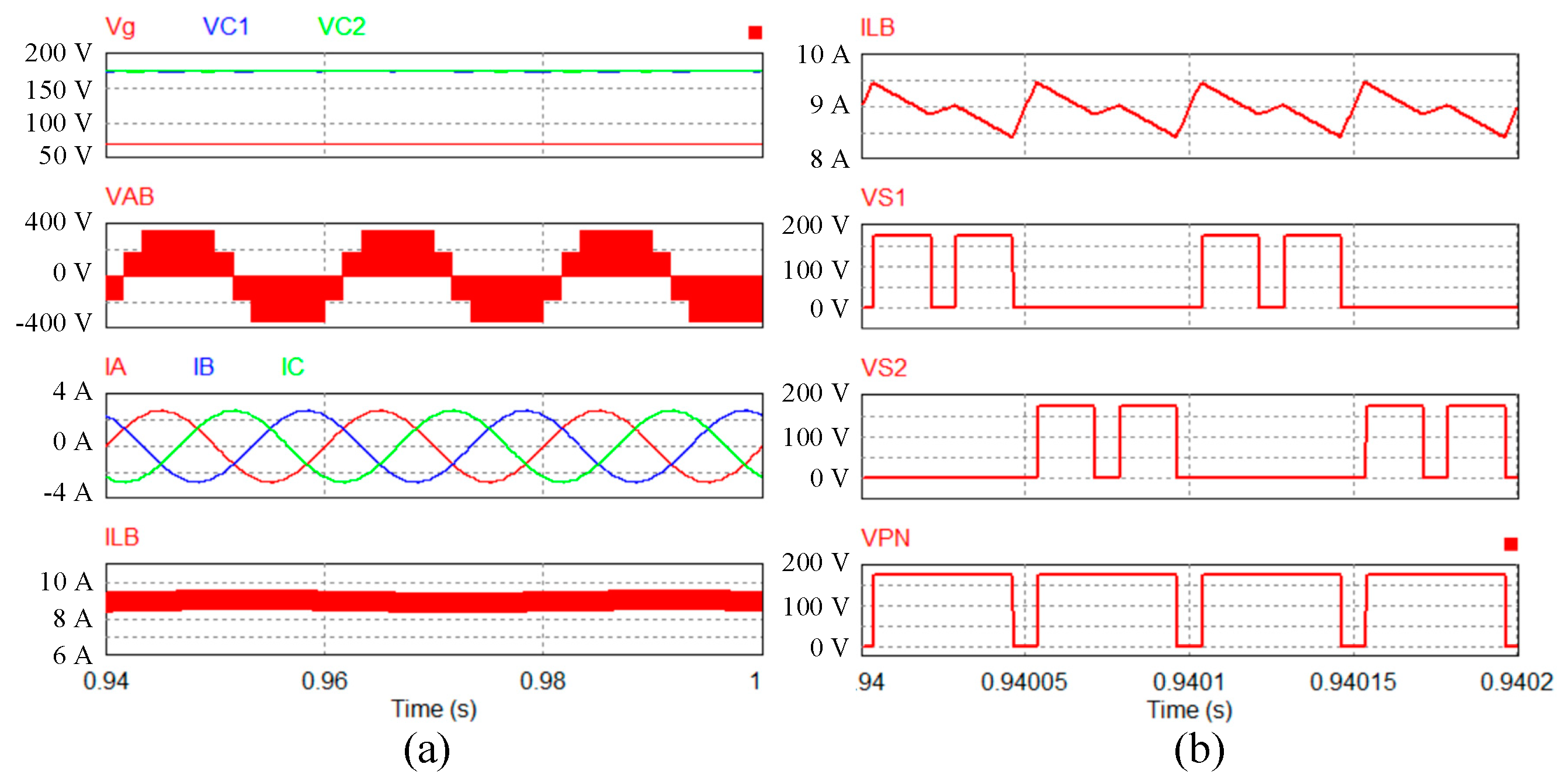

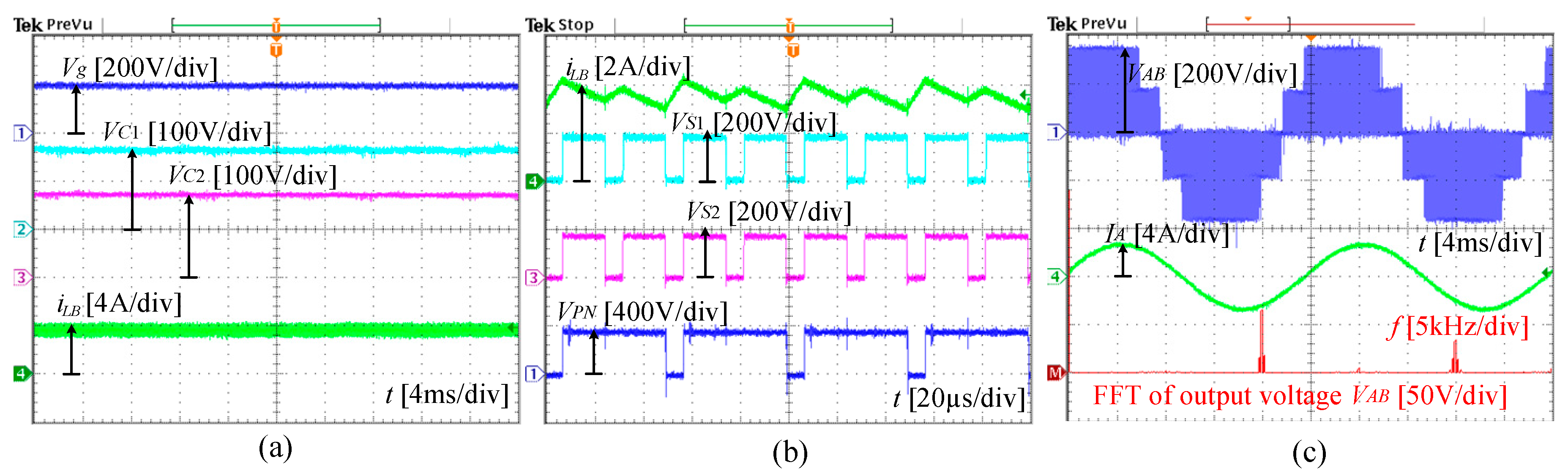

5.1. Simulation Results

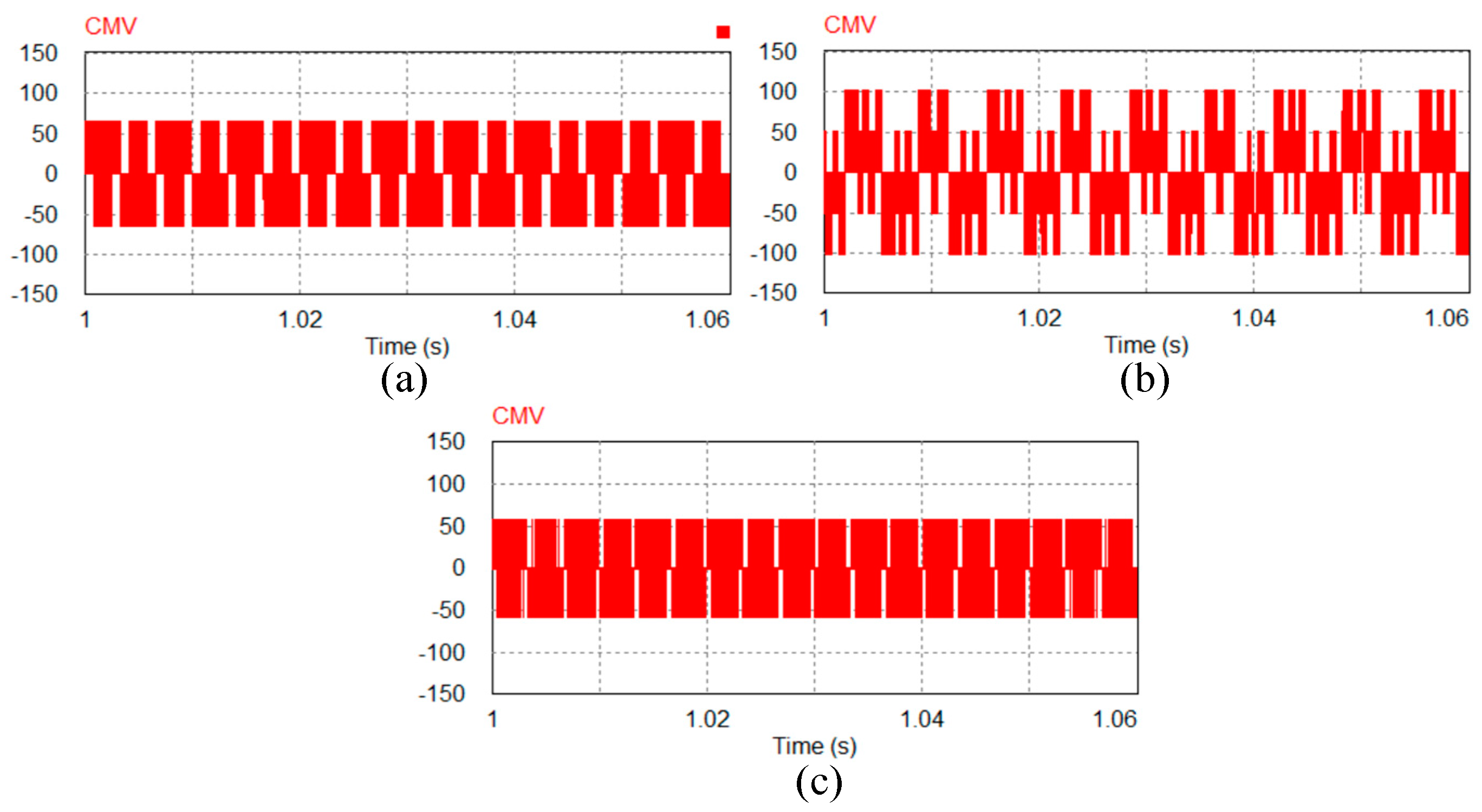

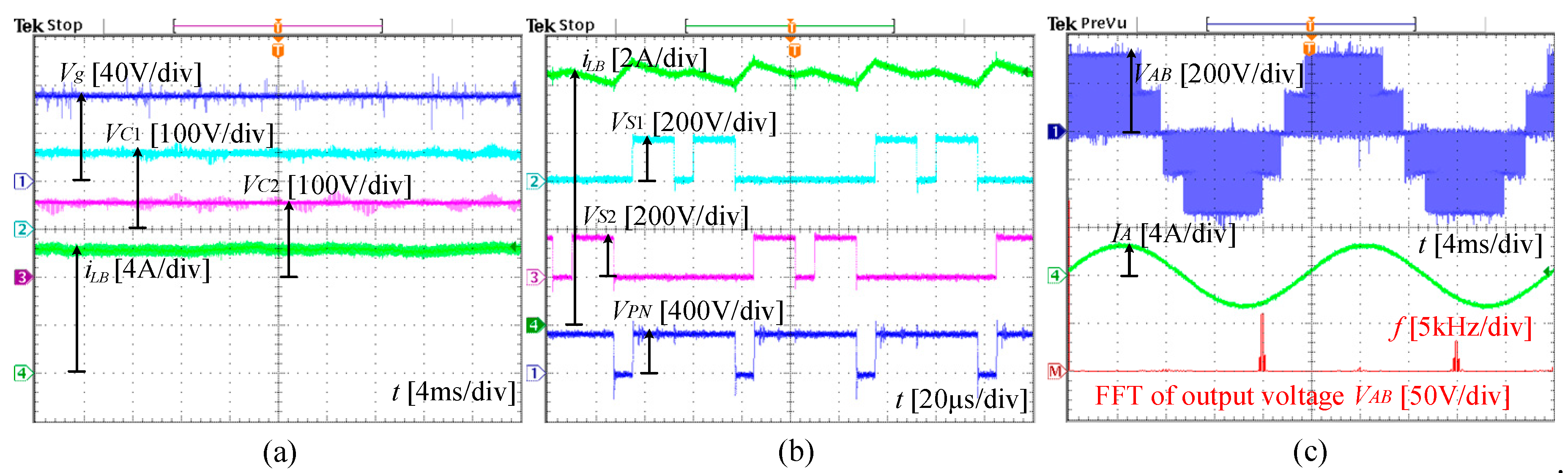

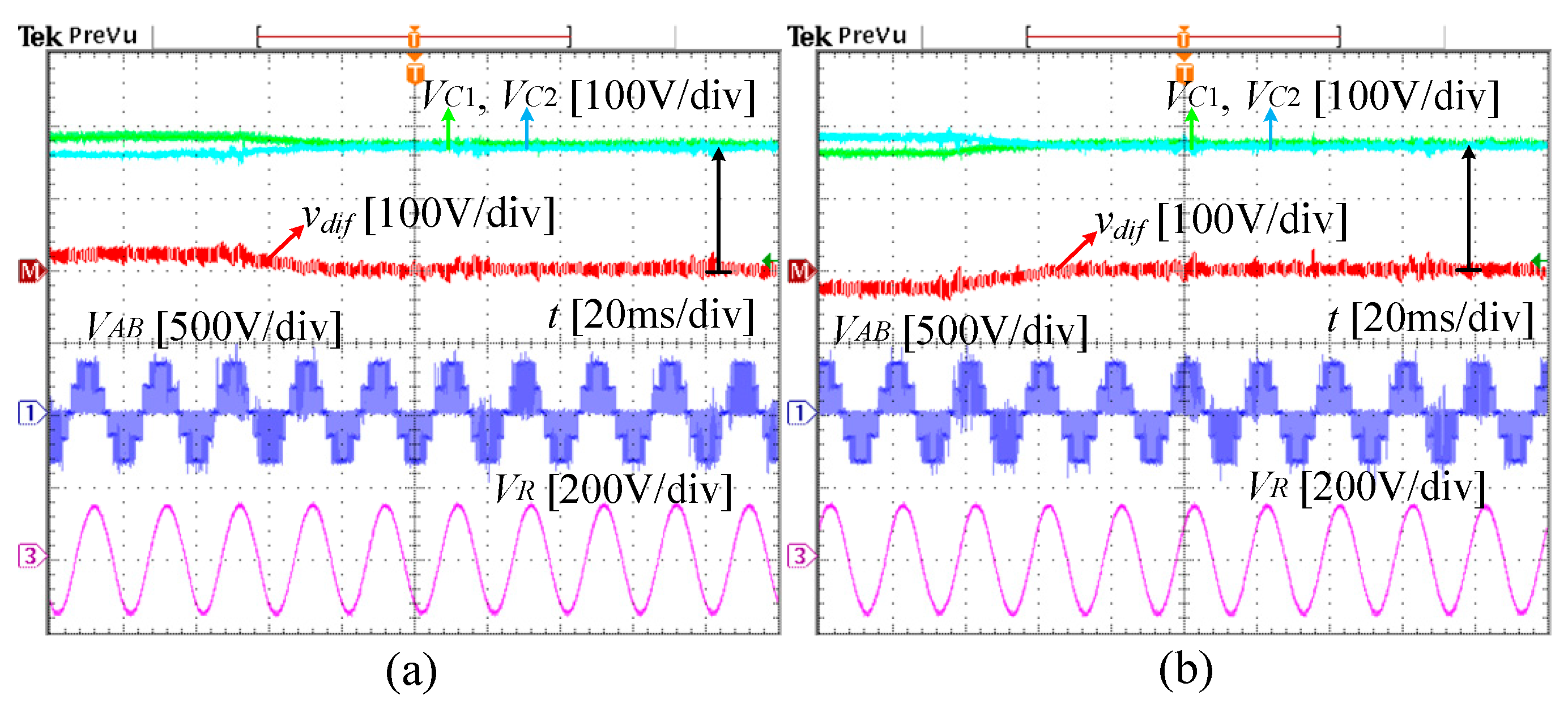

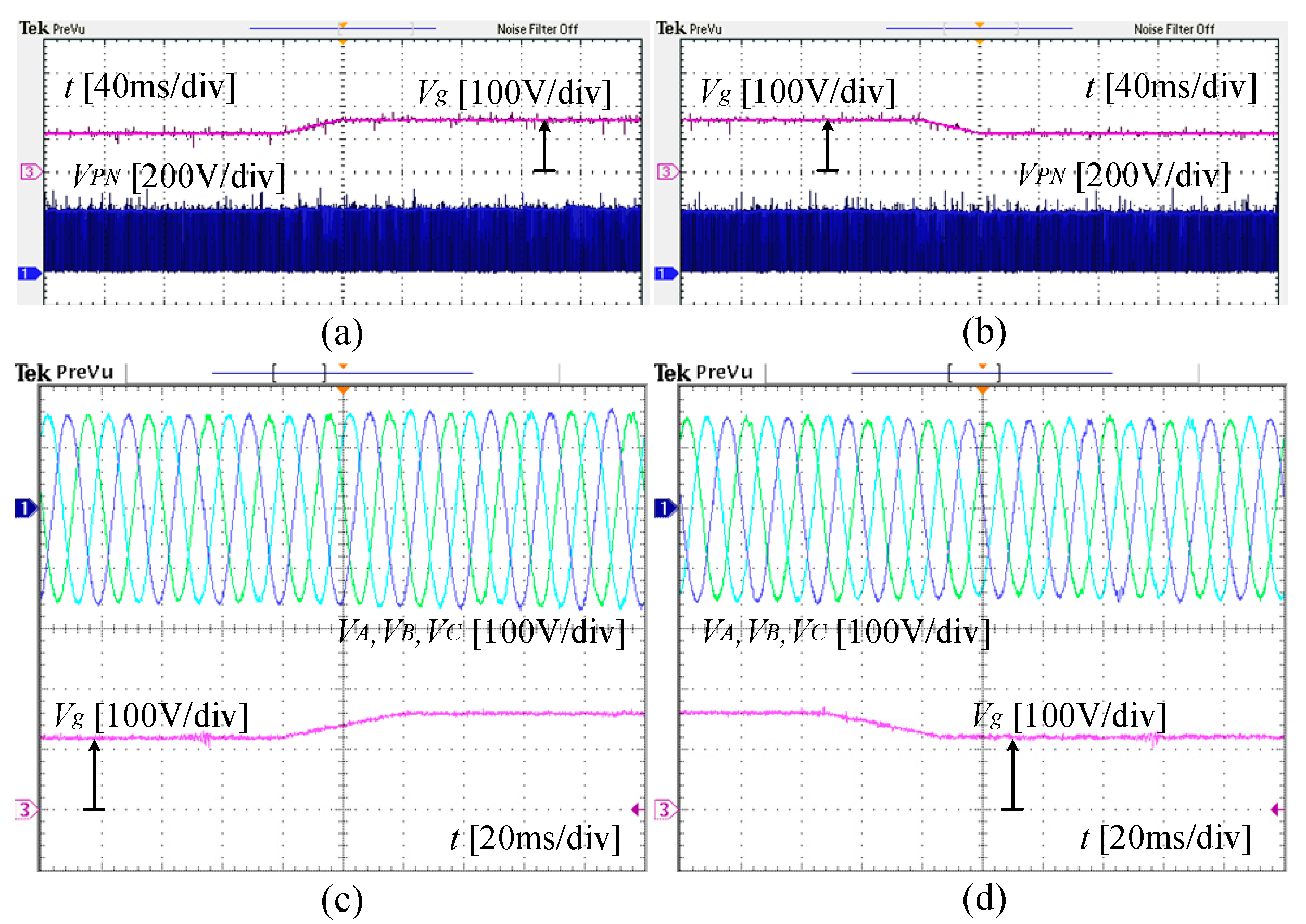

5.2. Experimental Results

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Zhang, Z.; Zhang, J.; Shao, S. A Novel Trapezoidal Wave Control Method for a Single-Phase Grid-Tied T-Type Inverter. IEEE Trans. Power Electron. 2021, 36, 4711–4722. [Google Scholar] [CrossRef]

- Wang, Z.; Wu, Y.; Mahmud, M.H.; Zhao, Z.; Zhao, Y.; Mantooth, H.A. Design and Implementation of a Highly Efficient Three-Level T-Type Converter for Low-Voltage Applications. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 578–588. [Google Scholar] [CrossRef]

- Nemade, R.V.; Pandit, J.K.; Aware, M.V. Reconfiguration of T-Type Inverter for Direct Torque Controlled Induction Motor Drives under Open-Switch Faults. IEEE Trans. Ind. Appl. 2017, 53, 2936–2947. [Google Scholar] [CrossRef]

- Li, X.; Xing, X.; Zhang, C.; Chen, A.; Qin, C.; Zhang, G. Simultaneous Common-Mode Resonance Circulating Current and Leakage Current Suppression for Transformerless Three-Level T-Type PV Inverter System. IEEE Trans. Ind. Electron. 2019, 66, 4457–4467. [Google Scholar] [CrossRef]

- Xing, X.; Zhang, C.; Chen, A.; Geng, H.; Qin, C. Deadbeat Control Strategy for Circulating Current Suppression in Multiparalleled Three-Level Inverters. IEEE Trans. Ind. Electron. 2018, 65, 6239–6249. [Google Scholar] [CrossRef]

- Roncero-Clemente, C.; Romero-Cadaval, E.; Ruiz-Cortés, M.; Husev, O. Carrier Level-Shifted Based Control Method for the PWM 3L-T-Type qZS Inverter with Capacitor Imbalance Compensation. IEEE Trans. Ind. Electron. 2018, 65, 8297–8306. [Google Scholar] [CrossRef]

- Ding, X.; Hao, Y.; Li, K.; Li, H.; Wei, Z.; Wu, W. Extensible Z-Source Inverter Architecture: Modular Construction and Analysis. IEEE Trans. Power Electron. 2021, 36, 1742–1763. [Google Scholar] [CrossRef]

- Peng, F.Z. Z-source inverter. IEEE Trans. Ind. Appl. 2003, 39, 504–510. [Google Scholar] [CrossRef]

- Mahmoudi, H.; Aleenejad, M.; Ahmadi, R. Modulated Model Predictive Control for a Z-Source-Based Permanent Magnet Synchronous Motor Drive System. IEEE Trans. Ind. Electron. 2018, 65, 8307–8319. [Google Scholar] [CrossRef]

- Singh, S.A.; Carli, G.; Azeez, N.A.; Williamson, S.S. Modeling, Design, Control, and Implementation of a Modified Z-Source Integrated PV/Grid/EV DC Charger/Inverter. IEEE Trans. Ind. Electron. 2018, 65, 5213–5220. [Google Scholar] [CrossRef]

- Birundha, S.; Saravanan, V. Design and development of Z source cascaded seven level inverter for solar photovoltaic system. In Proceedings of the 2015 International Conference on Computation of Power, Energy, Information and Communication (ICCPEIC), Melmaruvathur, Chennai, India, 22–23 April 2015; pp. 87–92. [Google Scholar]

- Loh, P.C.; Gao, F.; Blaabjerg, F.; Feng, S.Y.C.; Soon, K.N.J. Pulsewidth-Modulated Z-Source Neutral-Point-Clamped Inverter. IEEE Trans. Ind. Appl. 2007, 43, 1295–1308. [Google Scholar] [CrossRef]

- Loh, P.C.; Lim, S.W.; Gao, F.; Blaabjerg, F. Three-Level Z-Source Inverters Using a Single LC Impedance Network. IEEE Trans. Ind. Electron. 2007, 22, 706–711. [Google Scholar] [CrossRef]

- Annam, S.K.; Pongiannan, R.K.; Yadaiah, N. A Hysteresis Space Vector PWM for PV Tied Z-Source NPC-MLI with DC-Link Neutral Point Balancing. IEEE Access 2021, 9, 54420–54434. [Google Scholar] [CrossRef]

- Effah, F.B.; Wheeler, P.; Clare, J.; Watson, A. Space-Vector-Modulated Three-Level Inverters with a Single Z-Source Network. IEEE Trans. Ind. Electron. 2013, 28, 2806–2815. [Google Scholar] [CrossRef] [Green Version]

- Xing, X.; Zhang, C.; Chen, A.; He, J.; Wang, W.; Du, C. Space-Vector-Modulated Method for Boosting and Neutral Voltage Balancing in Z-Source Three-Level T-Type Inverter. IEEE Trans. Ind. Appl. 2016, 52, 1621–1631. [Google Scholar] [CrossRef]

- Stepenko, S.; Husev, O.; Vinnikov, D.; Fesenko, A.; Clemente, C.R.; Pimentel, S.P.; Santasheva, E. Experimental Comparison of Two-Level Full-SiC and Three-Level Si–SiC Quasi-Z-Source Inverters for PV Applications. Energies 2019, 12, 2509. [Google Scholar] [CrossRef] [Green Version]

- Stepenko, S.; Husev, O.; Vinnikov, D.; Fesenko, A.; Matiushkin, O. Feasibility Study of Interleaving Approach for Quasi-Z-Source Inverter. Electronics 2020, 9, 277. [Google Scholar] [CrossRef] [Green Version]

- Pires, V.F.; Cordeiro, A.; Foito, D.; Martins, J.F. Quasi-z-Source Inverter with a T-Type Converter in Normal and Failure Mode. IEEE Trans. Power Electron. 2016, 31, 7462–7470. [Google Scholar] [CrossRef]

- Wang, T.; Wang, X.; He, Y.; Chen, X.; Ruan, X.; Zhang, Z. An Improved Quasi-Z-Source Three-Level T-Type Inverter and Its Modulation Scheme. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, 15–19 March 2020; pp. 412–416. [Google Scholar]

- Qin, C.; Zhang, C.; Chen, A.; Xing, X.; Zhang, G. A Space Vector Modulation Scheme of the Quasi-Z-Source Three-Level T-Type Inverter for Common-Mode Voltage Reduction. IEEE Trans. Ind. Electron. 2018, 65, 8340–8350. [Google Scholar] [CrossRef]

- Qin, C.; Zhang, C.; Xing, X.; Li, X.; Chen, A.; Zhang, G. Simultaneous Common-Mode Voltage Reduction and Neutral-Point Voltage Balance Scheme for the Quasi-Z-Source Three-Level T-Type Inverter. IEEE Trans. Ind. Electron. 2020, 67, 1956–1967. [Google Scholar] [CrossRef]

- Nguyen, M.K.; Lim, Y.C.; Park, S.J. A Comparison between Single-Phase Quasi- Z-Source and Quasi-Switched Boost Inverters. IEEE Trans. Ind. Electron. 2015, 62, 6336–6344. [Google Scholar] [CrossRef]

- Tran, V.T.; Do, D.T.; Do, V.D.; Nguyen, M.K. A Three-Level DC-Link Quasi-Switch Boost T-Type Inverter with Voltage Stress Reduction. Energies 2020, 13, 3727. [Google Scholar] [CrossRef]

- Sahoo, M.; Keerthipati, S. A Three-Level LC-Switching-Based Voltage Boost NPC Inverter. IEEE Trans. Ind. Electron. 2017, 64, 2876–2883. [Google Scholar] [CrossRef]

- Sahoo, M.; Kumar, S. A single source fed three level voltage boost NPC inverter with reduced LC count. In Proceedings of the IECON 2016-42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, Italy, 23–26 October 2016; pp. 3190–3195. [Google Scholar]

- Do, D.T.; Nguyen, M.K. Three-Level Quasi-Switched Boost T-Type Inverter: Analysis, PWM Control, and Verification. IEEE Trans. Ind. Electron. 2018, 65, 8320–8329. [Google Scholar] [CrossRef]

- Do, D.T.; Nguyen, M.K.; Ngo, V.T.; Quach, T.H.; Tran, V.T. Common Mode Voltage Elimination for Quasi-Switch Boost T-Type Inverter Based on SVM Technique. Electronics 2020, 9, 76. [Google Scholar] [CrossRef] [Green Version]

- Do, D.T.; Nguyen, M.K.; Quach, T.H.; Tran, V.T.; Blaabjerg, F.; Vilathgamuwa, D.M. A PWM Scheme for a Fault-Tolerant Three-Level Quasi-Switched Boost T-Type Inverter. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 8, 3029–3040. [Google Scholar] [CrossRef] [Green Version]

- Tran, V.T.; Nguyen, M.K.; Do, D.T.; Vinnikov, D. An SVM Scheme for Three-Level Quasi-Switched Boost T-Type Inverter with Enhance Voltage Gain and Capacitor Voltage Balance. IEEE Trans. Power Electron. 2021, in press. [Google Scholar] [CrossRef]

| Mode | ON Switches | ON Diodes | VXO |

|---|---|---|---|

| NST mode 1 | S1 | D2, D3, D4 | +VPN/2, 0 or −VPN/2 |

| NST mode 2 | S2 | D1, D2, D3 | +VPN/2, 0 or −VPN/2 |

| NST mode 3 | S1, S2 | D2, D3 | +VPN/2, 0 or −VPN/2 |

| NST mode 4 | S1X | D1, D2, D3, D4 | +VPN/2 |

| S2X | 0 | ||

| S3X | −VPN/2 | ||

| ST mode | S1, S2, S1X, S2X, S3X | 0 |

| Strategy in [27] | Strategy in [30] | Proposed Method | |

|---|---|---|---|

| Max ST duty ratio, DST | 1 − M | 2(1 − M) | 1 − M |

| Boost factor, B | 2/(3 − 2DST − D0) | 2/(3 − 2DST − D0) | 2/(3 − 5DST − D0) |

| Voltage gain, G | 1.15·MB | 1.15·MB | 1.15·MB |

| Capacitor voltage rating, Vc/Vdc | 1/(3 − 2DST − D0) | 1/(3 − 2DST − D0) | 1/(3 − 5DST − D0) |

| Diode voltage rating, VD/Vdc | 1/(3 − 2DST − D0) | 1/(3 − 2DST − D0) | 1/(3 − 5DST − D0) |

| Switch voltage rating, VS/Vdc | 1/(3 – 2DST – D0) | 1/(3 – 2DST – D0) | 1/(3 − 5DST − D0) |

| Parameter/Components | Values | |

|---|---|---|

| Input voltage | Vg | 70 V ÷ 200 V |

| Output load voltage | Vx,RMS | 110 VRMS |

| Output frequency | fo | 50 Hz |

| Switching frequency | fs | 10 kHz |

| Extra duty ratio | D0 | 0.15 ÷ 0.85 |

| ST duty ratio | DST | 0.15 |

| Modulation index | M | 0.76 |

| Boost inductors | LB | 3 mH/20 A |

| Capacitors | C1 = C2 | 2200 μF/400 V |

| LC filter | Lf and Cf | 3 mH and 10 μF |

| Resistor load | R | 56 Ω |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Do, D.-T.; Tran, V.-T.; Nguyen, M.-K. Enhanced Boost Factor for Three-Level Quasi-Switched Boost T-Type Inverter. Energies 2021, 14, 3920. https://doi.org/10.3390/en14133920

Do D-T, Tran V-T, Nguyen M-K. Enhanced Boost Factor for Three-Level Quasi-Switched Boost T-Type Inverter. Energies. 2021; 14(13):3920. https://doi.org/10.3390/en14133920

Chicago/Turabian StyleDo, Duc-Tri, Vinh-Thanh Tran, and Minh-Khai Nguyen. 2021. "Enhanced Boost Factor for Three-Level Quasi-Switched Boost T-Type Inverter" Energies 14, no. 13: 3920. https://doi.org/10.3390/en14133920

APA StyleDo, D.-T., Tran, V.-T., & Nguyen, M.-K. (2021). Enhanced Boost Factor for Three-Level Quasi-Switched Boost T-Type Inverter. Energies, 14(13), 3920. https://doi.org/10.3390/en14133920