Control Design and Experimental Validation of a HB-NPC as a Shunt Active Power Filter

Abstract

1. Introduction

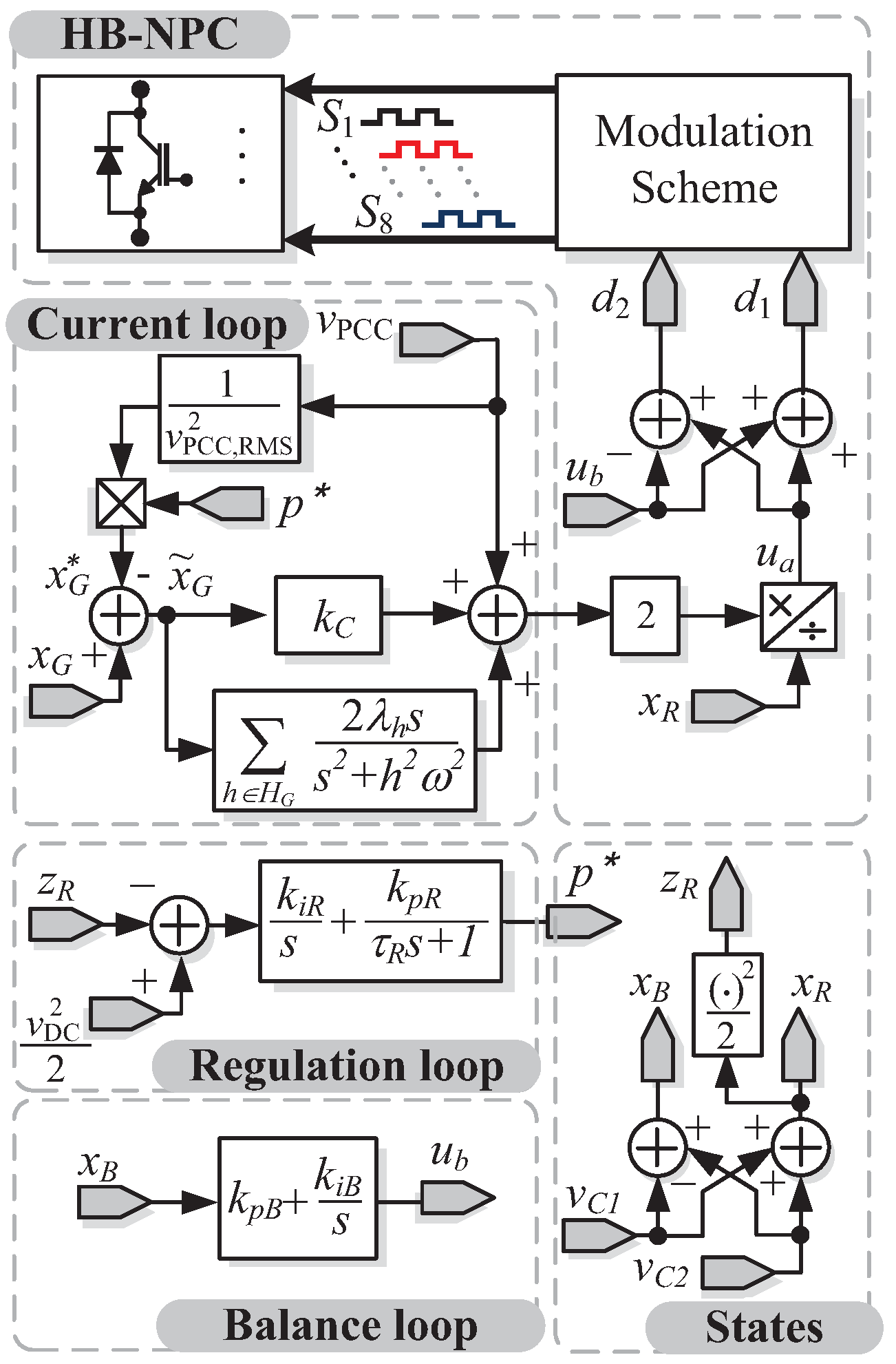

- The design of a multi-loop controller for SAPF based on a five-level HB-NPC topology, which considers a time scale separation between current and voltage dynamics. The last yields three independent control loops, i.e., current tracking loop, voltage regulation loop, and voltage balance loop for PF correction and harmonic mitigation.

- The proposed control scheme does not depend on system parameters’ knowledge; therefore, a robust behavior against grid uncertain parameters, output filter uncertain parameters, current harmonic distortion, and load variations is exhibited.

- According to the best of the authors knowledge, there is no similar work in the literature regarding the experimental validation of the proposed control scheme applied to a five-level HB-NPC topology for an SAPF of 2 kW academic prototype with a constant switching frequency of 7 kHz.

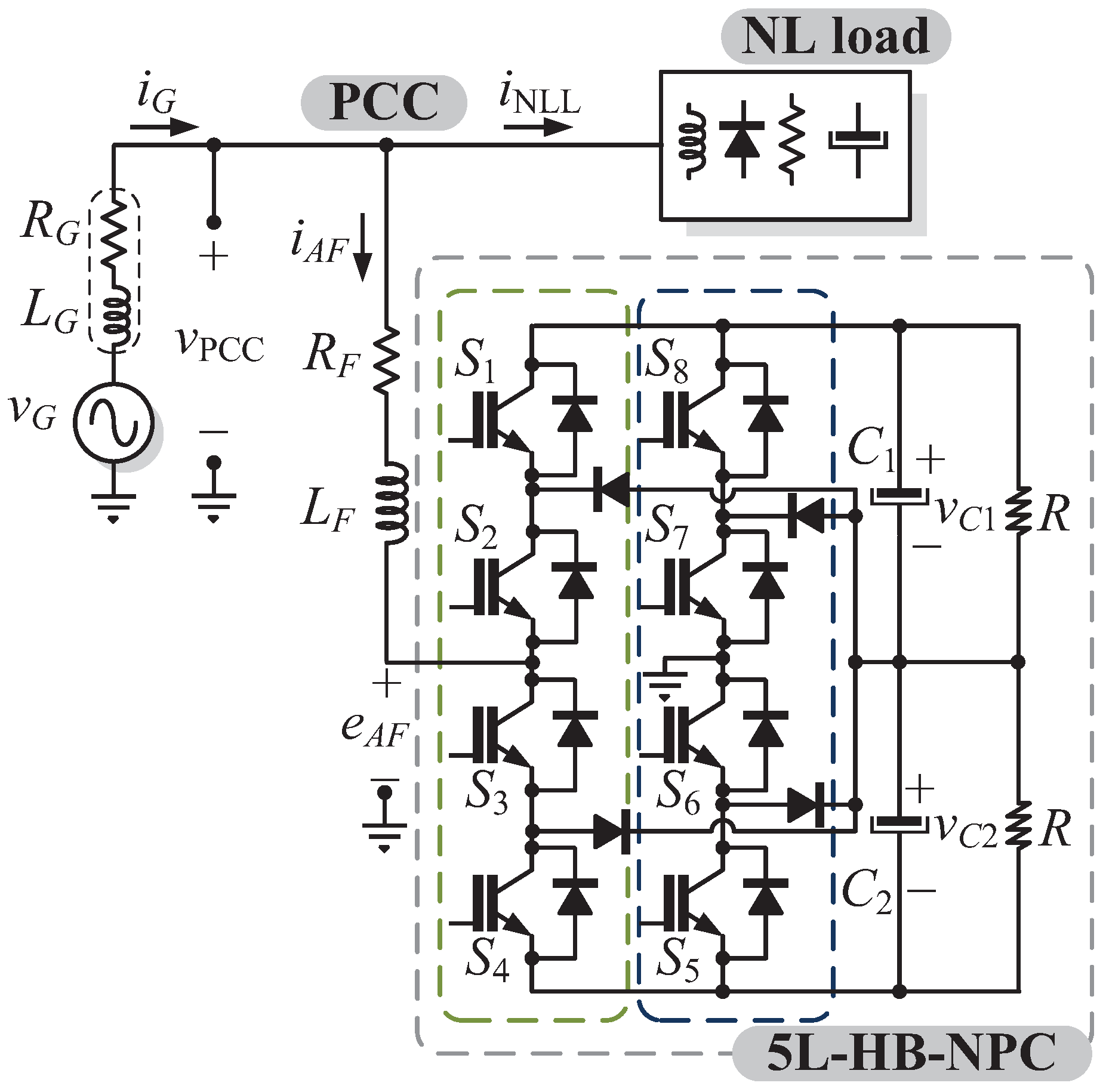

2. System Description

- O1.

- Current tracking objective: An inner (current) control loop is designed to guarantee tracking of the state towards a desired reference , i.e., (Without loss of generality, time dependency is only explicitly used in (11) and (13)–(15). Throughout the paper, time dependency is omitted for simplicity.):where the current reference is calculated as:where is the fundamental component of and its RMS value. In practice, may be polluted by harmonic distortion, and thus, it is preferred to construct the current reference in terms of the fundamental component. Signal can be obtained from an external filter or with a phase-locked loop (PLL) scheme [35]. The term represents the active power reference of the system, which modulates the amplitude of the grid current. The scalar term is obtained from the outer (regulation voltage) control loop, as will be explained later.

- O2.

- Voltage regulation objective: An outer (regulation voltage) loop is designed to maintain (on average) the DC-link voltage regulated to a desired constant value . In particular, this control objective is expressed as:where represents the DC component of and is used to address the average of , which is extracted using the following averaging function:where T represents the fundamental period of the disturbance signal; in this case, a second order harmonic of the fundamental is expected, and thus, can be proposed.As an outcome of this control loop, the power reference is obtained. The regulation objective must guarantee that the DC-Link stores enough energy to allow the appropriate injection of the compensating (reactive and harmonic) current to the PCC.

- O3.

- Voltage balance objective: A balance loop is designed to guarantee that capacitors and , in the DC-bus, achieve the same voltage level. This avoids asymmetries on the reconstructed injected voltage and guarantees a safe operation of the capacitors. Equivalently, the balance objective is reached if the difference of the capacitor voltages goes to zero, that is,

- A1.

- The inductor current dynamics is faster than the voltage dynamics (in the closed loop). Furthermore, the voltage balance dynamics is considered faster than the voltage regulation dynamics (in the closed loop). Hence, the controller design procedure can be divided into three independent loops’ design (one loop for each dynamics). This is commonly referred to as the decoupling assumption and is based on the singular perturbation theory and analysis [36], i.e., a time scale separation.

- A2.

- The fundamental frequency of the grid voltage is a known constant.

- A3.

- The , as well as the are periodic signals (may be perturbed by harmonic disturbances) with a fundamental frequency , and thus, they can be described by Fourier series as follows:where and are the vectors of unknown harmonic coefficients. Normally, for single-phase systems, such a harmonic distortion is only comprised of odd harmonics, i.e., harmonics in the set .

- A4.

- The system parameters , C, and R are considered positive unknown constants or may vary slowly due to the aging effect.

3. Controller Design

3.1. Current Tracking Loop

3.2. Regulation and Balance Control Loops

3.2.1. Voltage Balance Control Loop

3.2.2. Voltage Regulation Control Loop

3.3. Tuning Guidelines

3.3.1. Tuning Guidelines: Current Tracking Loop

3.3.2. Tuning Guidelines: Voltage Balance Loop

3.3.3. Tuning Guidelines: Voltage Regulation Loop

4. Numerical and Experimental Results

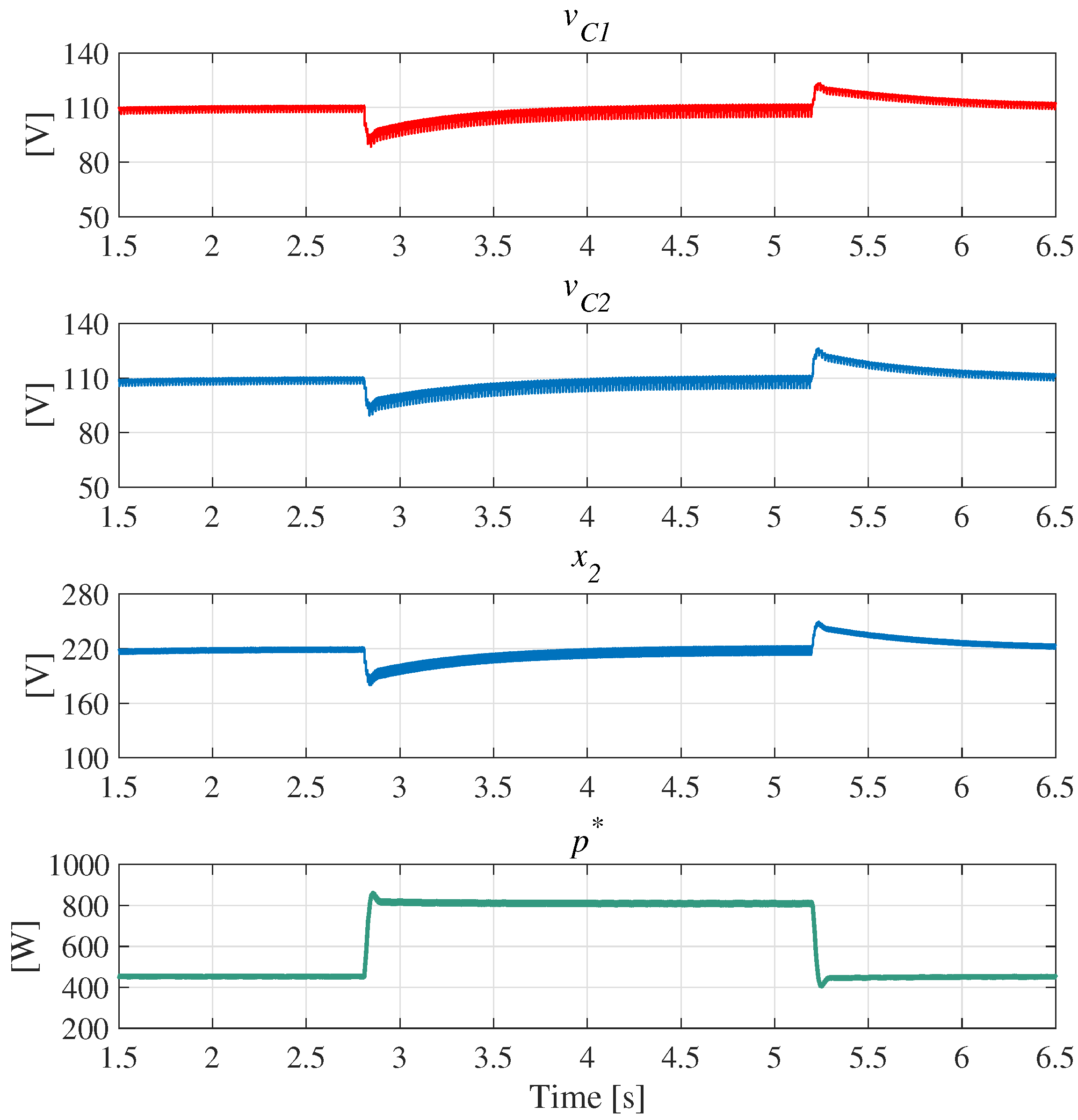

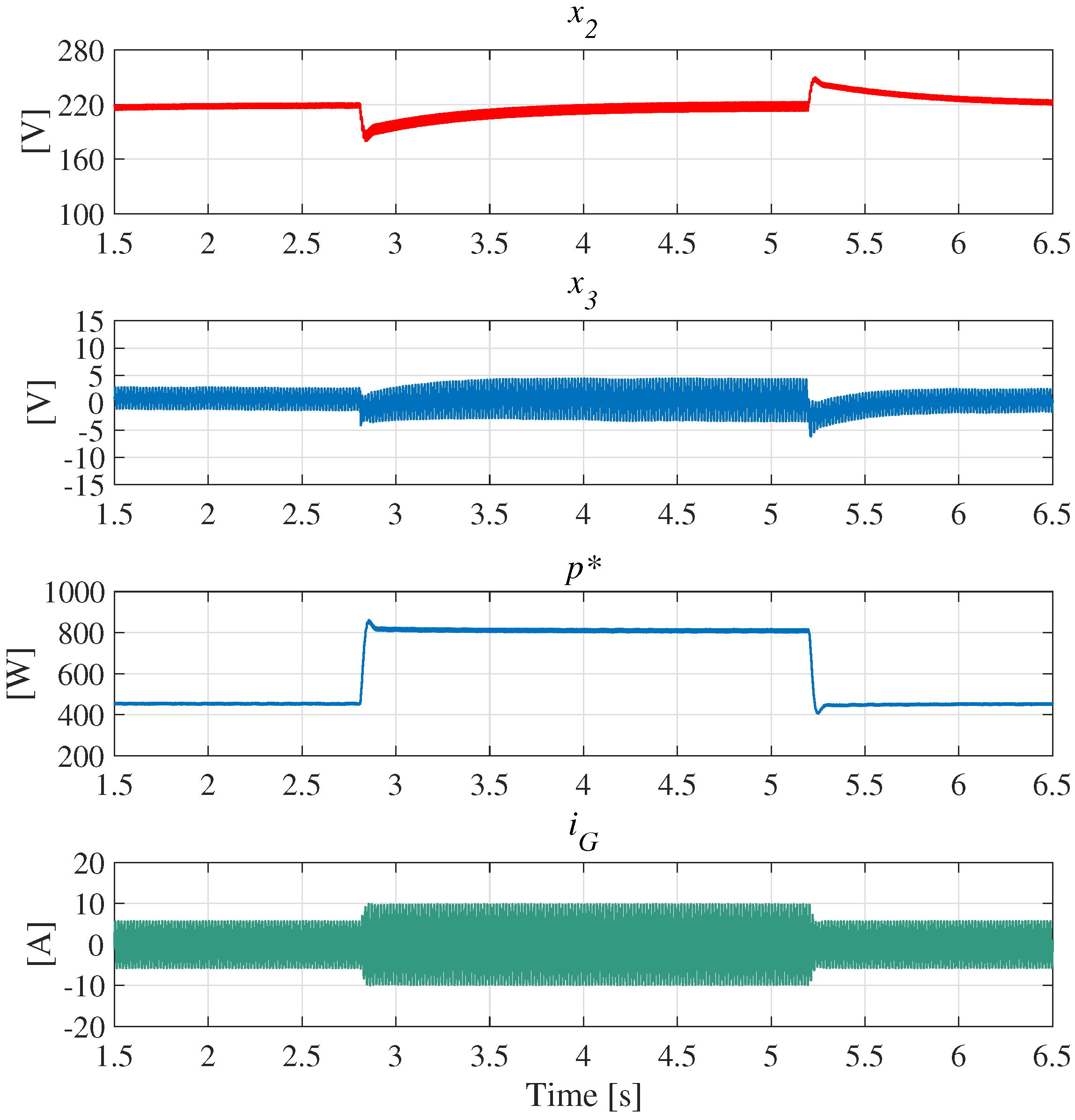

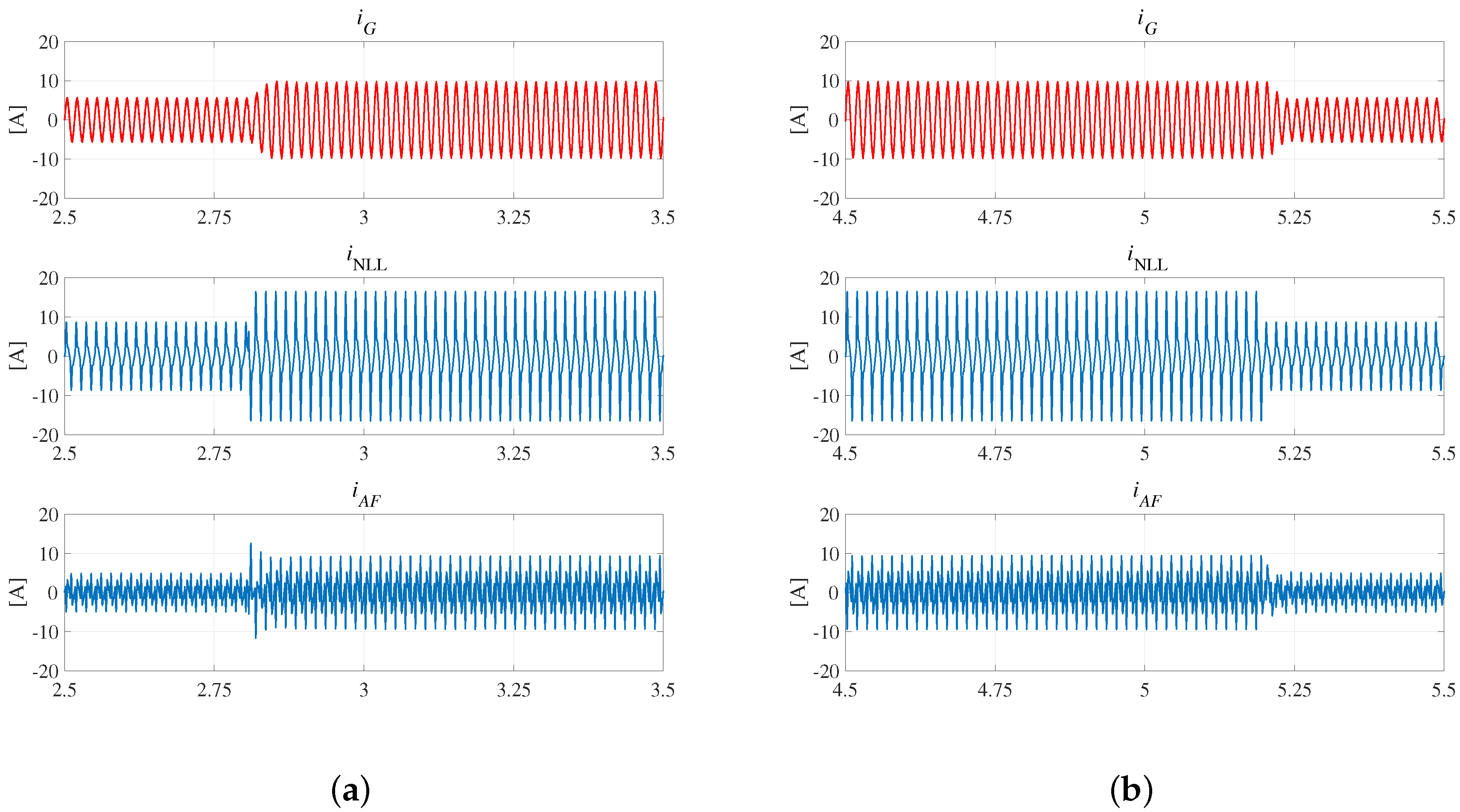

4.1. Numerical Results

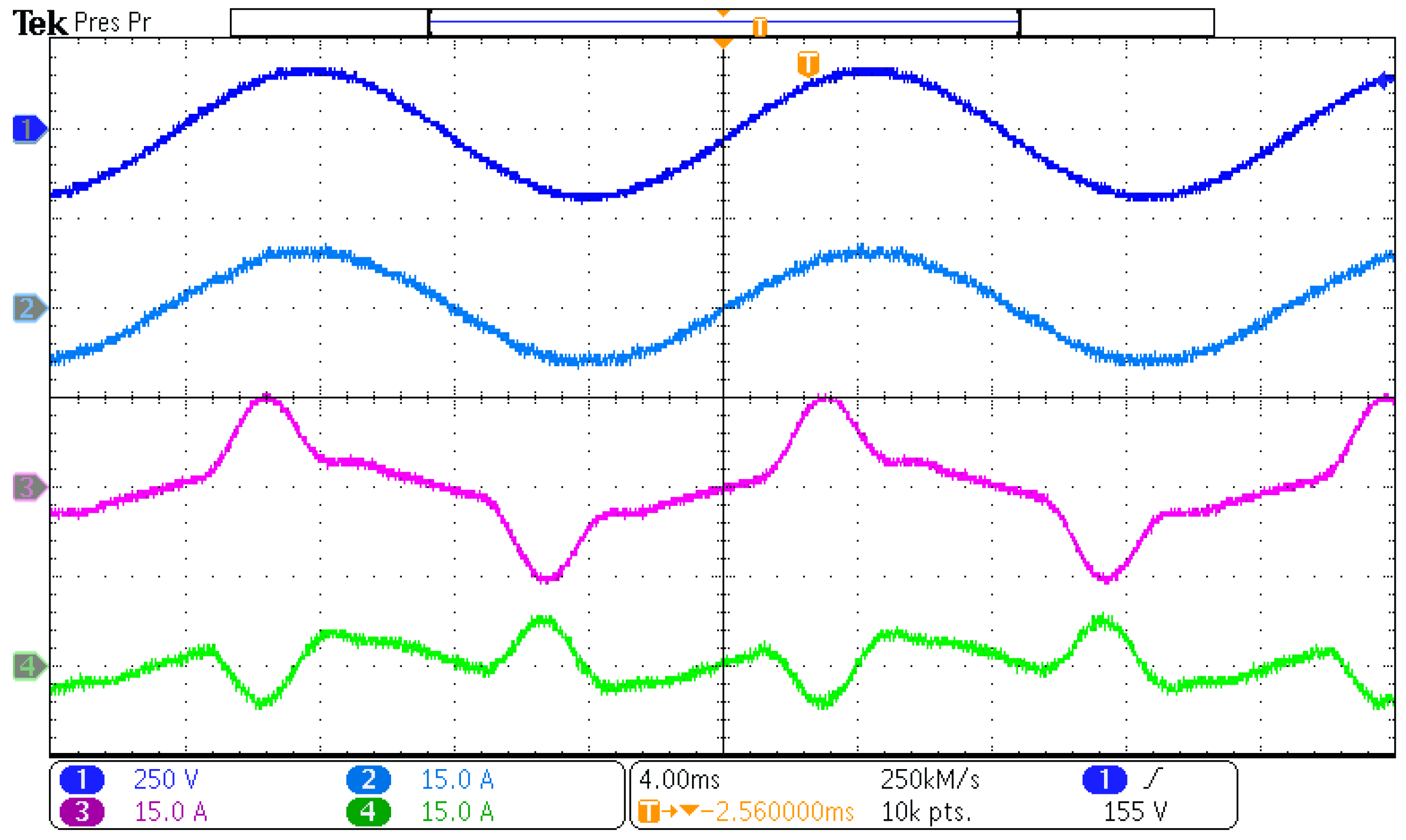

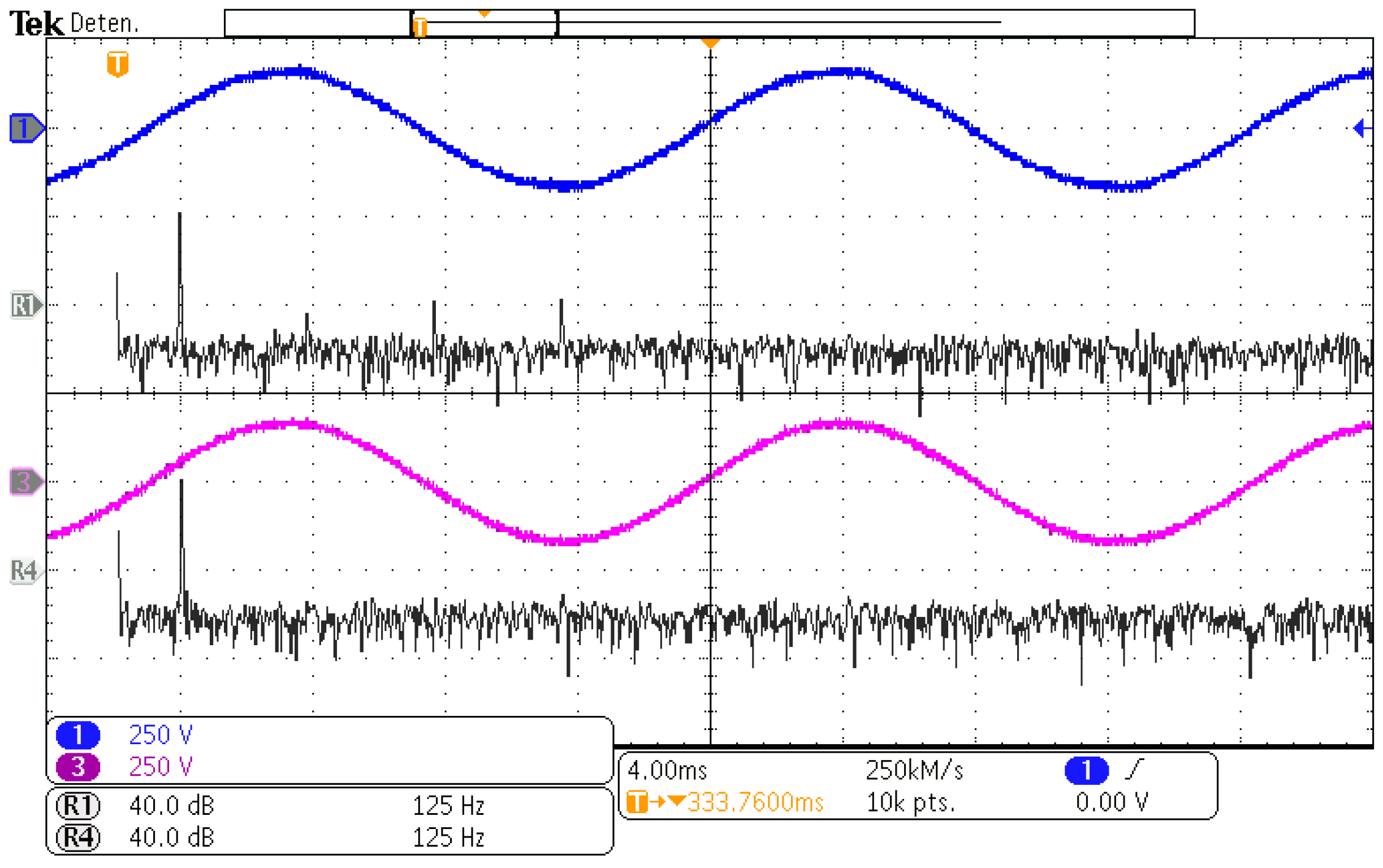

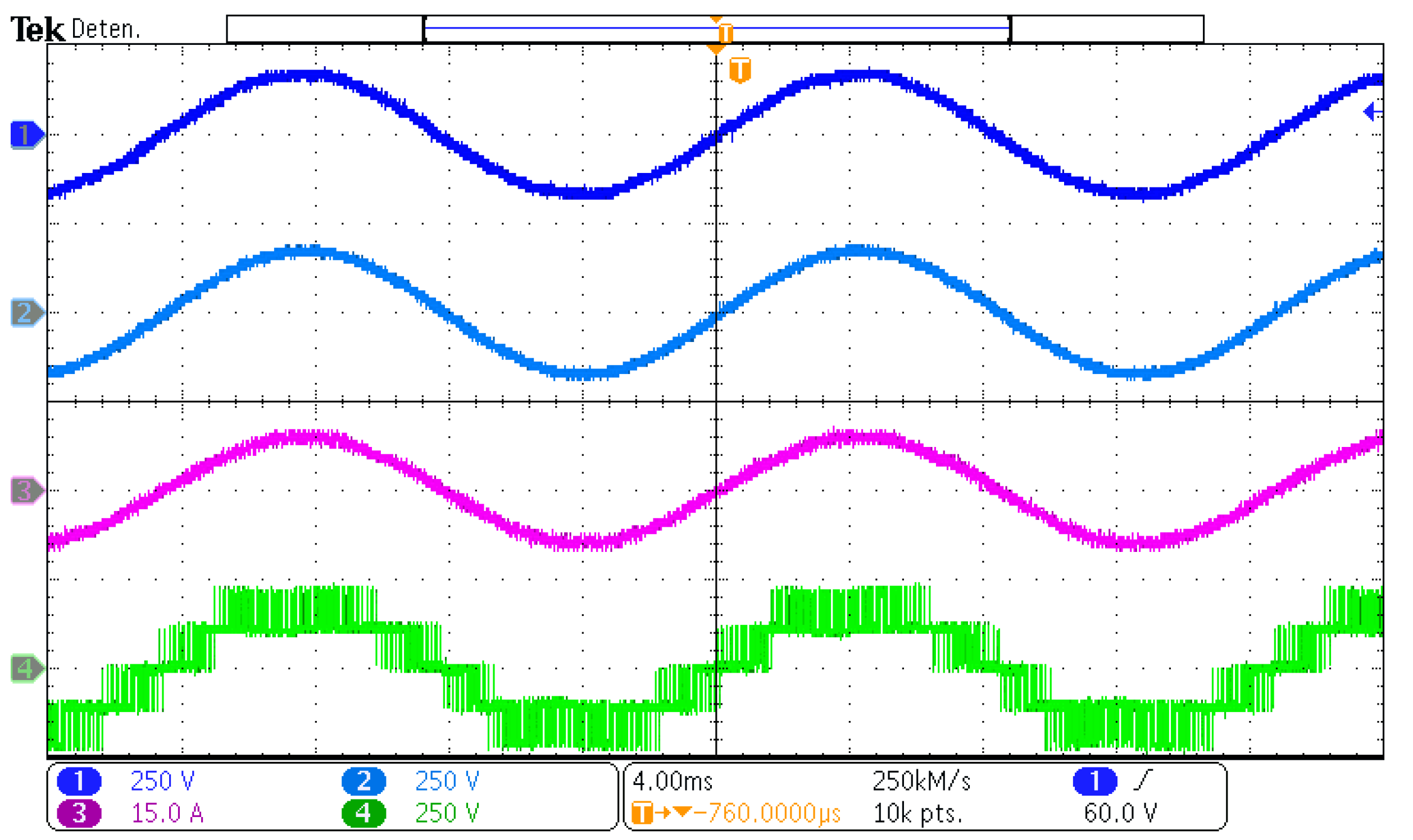

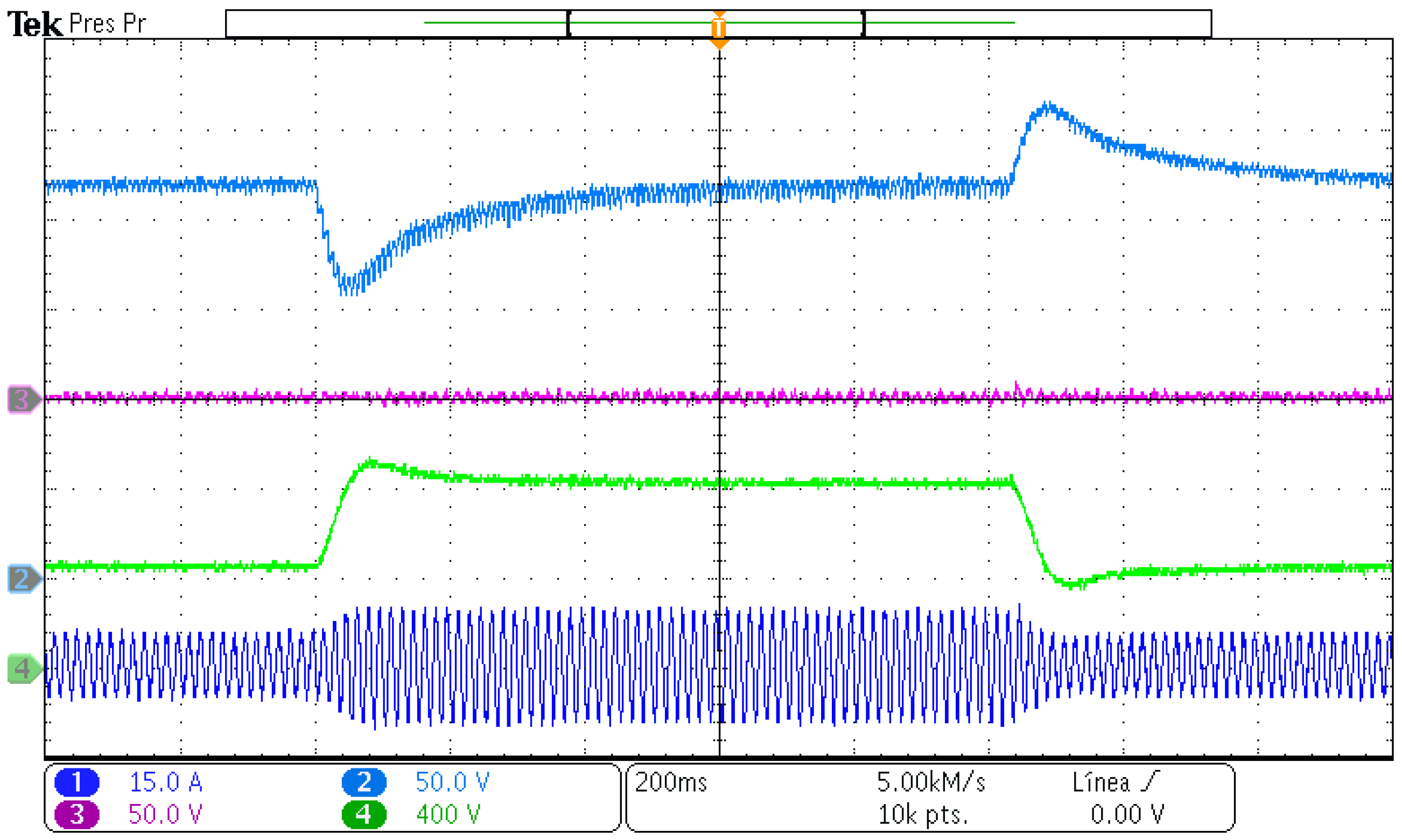

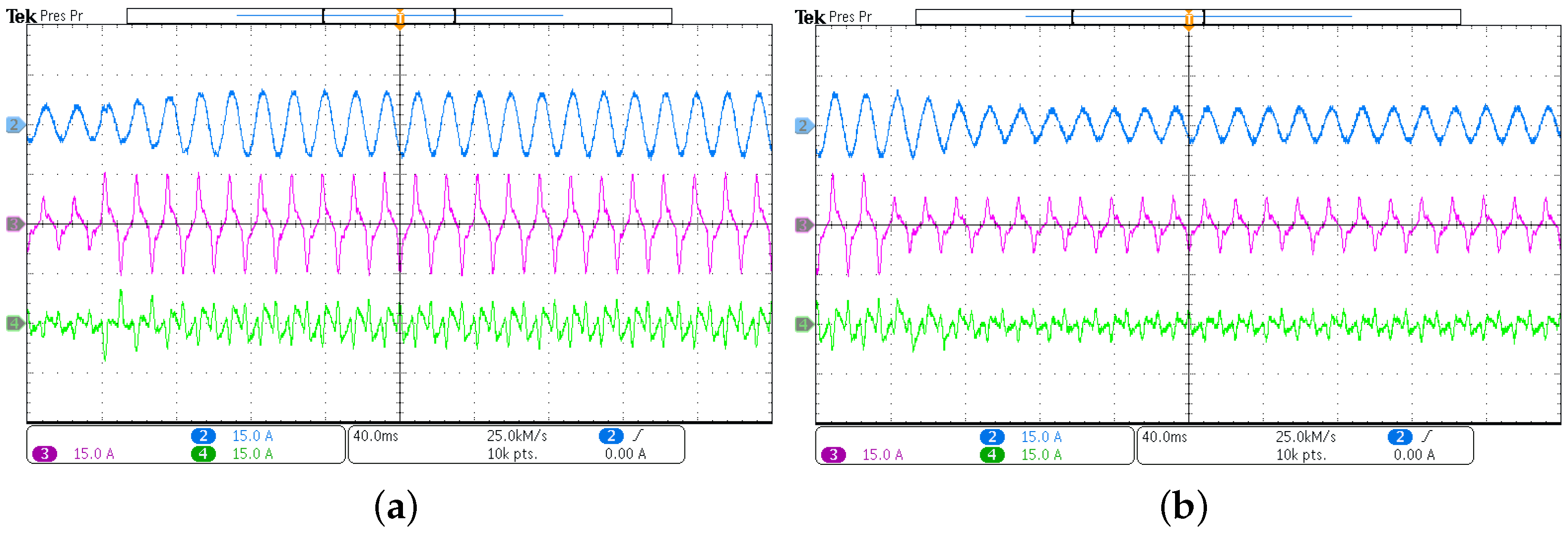

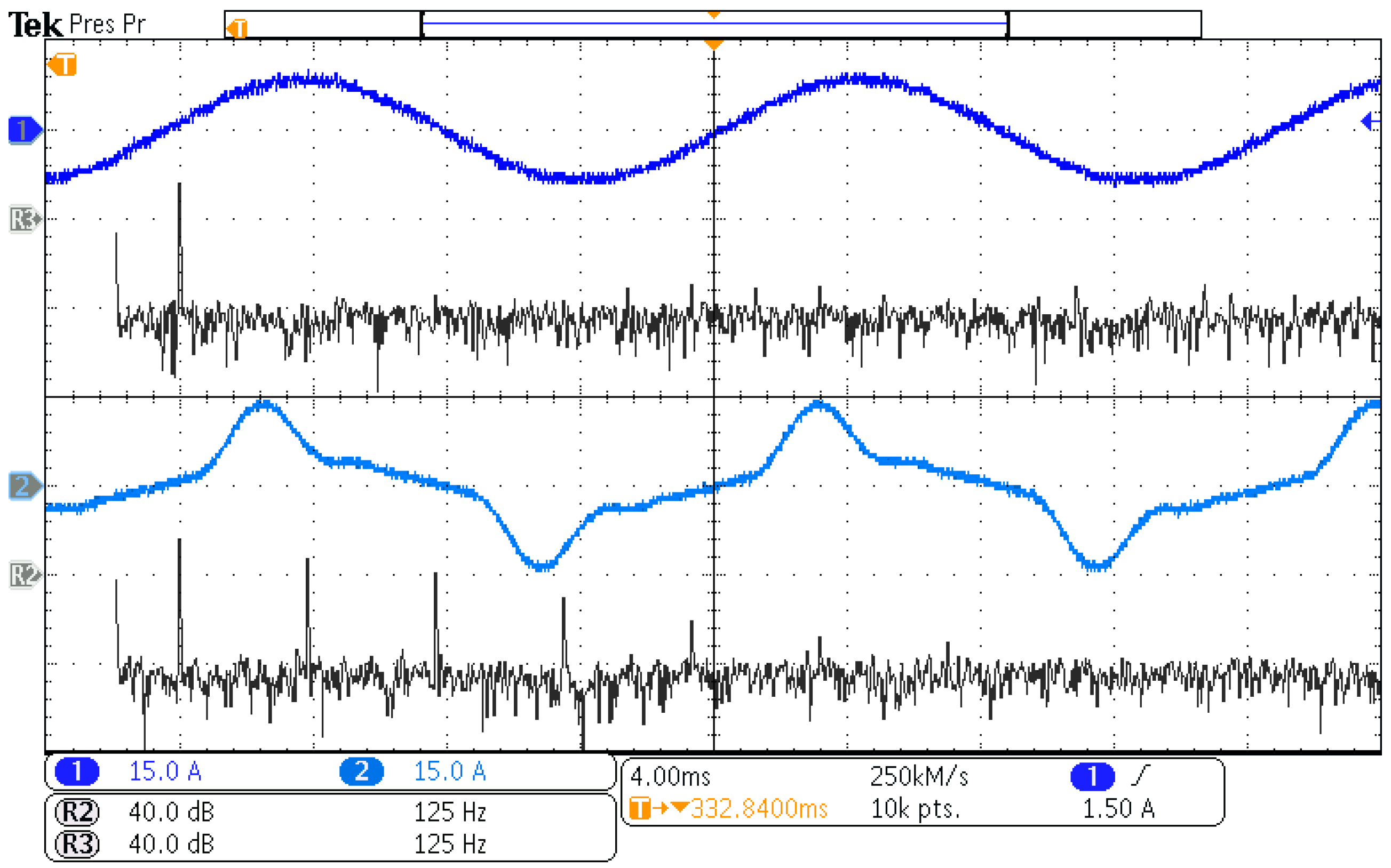

4.2. Experimental Results

5. Concluding Remarks

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| 5L-HB-NPC | Five-level H-bridge neutral point clamped |

| NLL | Nonlinear loads |

| SAPF | Shunt active power filter |

| PF | Power factor |

| VSI | Voltage source inverter |

| PCC | Point of common coupling |

| THD | Total harmonic distortion |

| PLL | Phase locked loop |

| RMS | Root mean square |

| Grid voltage | |

| Grid fundamental frequency | |

| Grid inductance | |

| Grid resistance | |

| Voltage at point of common coupling | |

| , | Grid current |

| Filter inductance | |

| Parasitic filter resistance | |

| DC-link capacitors | |

| ,..., | Converter switches |

| Filter current | |

| Nonlinear load current | |

| VSI output voltage | |

| , | Capacitors’ and voltages, respectively |

| , | Switching functions |

| , | Duty ratios |

| Voltage regulation state variable | |

| Voltage balance state variable | |

| , | Control signals |

| R | Capacitors’ discharge resistance |

| Grid current reference | |

| Active power reference | |

| RMS voltage of | |

| Fundamental component of | |

| Desired constant value for the DC-link | |

| Average value of | |

| T | Fundamental period of averaging function |

| Fundamental frequency of grid voltage | |

| , | Vectors of unknown harmonic coefficients. |

| Fourier trigonometric vector | |

| Grid current error variable | |

| Vanishing part of | |

| Parasitic resistance | |

| Sum of periodic signals | |

| Proportional gain | |

| Harmonic compensation term | |

| Harmonic compensation error | |

| Gain of the h-th oscillator | |

| Demanded load power | |

| , | Proportional and integral gains of the balance loop. |

| Balance loop integral variable | |

| , | Transformation variable and error variable |

| , | Integral and proportional gains of regulation loop |

| Low-pass filter time constant | |

| Regulation loop integral variable and low-pass filter state | |

| Bandwidth of the closed-loop current subsystem | |

| , | Natural oscillation frequency and damping factor of the balance loop |

| , | Natural oscillation frequency and damping factor of the regulation loop |

| Bandwidth of the closed-loop voltage regulation subsystem |

References

- Luo, A.; Xu, Q.; Ma, F.; Chen, Y. Overview of power quality analysis and control technology for the smart grid. J. Mod. Power Syst. Clean Energy 2016, 4, 1–9. [Google Scholar] [CrossRef]

- Hoon, Y.; Radzi, M.A.M.; Hassan, M.K.; Mailah, N.F. Operation of Three-level Inverter-based Shunt Active Power Filter under Non-ideal Grid Voltage Conditions with Dual Fundamental Component Extraction. IEEE Trans. Power Electron. 2017, 33, 7558–7570. [Google Scholar] [CrossRef]

- Guzman, R.; de Vicuña, L.G.; Morales, J.; Castilla, M.; Miret, J. Model-based control for a three-phase shunt active power filter. IEEE Trans. Ind. Electron. 2016, 63, 3998–4007. [Google Scholar] [CrossRef]

- Tareen, W.U.K.; Mekhielf, S. Three-Phase Transformerless Shunt Active Power Filter With Reduced Switch Count for Harmonic Compensation in Grid-Connected Applications. IEEE Trans. Power Electron. 2018, 33, 4868–4881. [Google Scholar] [CrossRef]

- Martinez-Garcia, J.F.; Martinez-Rodriguez, P.R.; Escobar, G.; Vazquez-Guzman, G.; Sosa-Zuñiga, J.M.; Valdez-Fernandez, A.A. Effects of modulation techniques on leakage ground currents in a grid-tied transformerless HB-NPC inverter. IET Renew. Power Gener. 2019, 13, 1250–1260. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Steimer, P.; Lizama, I. A Survey on Neutral-Point-Clamped Inverters. IEEE Trans. Ind. Electron. 2010, 57, 2219–2230. [Google Scholar] [CrossRef]

- Akagi, H.; Isozaki, K. A Hybrid Active Filter for a Three-Phase 12-Pulse Diode Rectifier Used as the Front End of a Medium-Voltage Motor Drive. IEEE Trans. Power Electron. 2012, 27, 69–77. [Google Scholar] [CrossRef]

- Feng, L.; Wang, Y. Modeling and Resonance Control of Modular Three-Level Shunt Active Power Filter. IEEE Trans. Ind. Electron. 2017, 64, 7478–7486. [Google Scholar] [CrossRef]

- Angulo, M.; Ruiz-Caballero, D.A.; Lago, J.; Heldwein, M.L.; Mussa, S.A. Active power filter control strategy with implicit closed-loop current control and resonant controller. IEEE Trans. Ind. Electron. 2013, 60, 2721–2730. [Google Scholar] [CrossRef]

- Antoniewicz, K.; Jasinski, M.; Kazmierkowski, M.P.; Malinowski, M. Model predictive control for three-level four-leg flying capacitor converter operating as shunt active power filter. IEEE Trans. Ind. Electron. 2016, 63, 5255–5262. [Google Scholar]

- Salim, C. Five-level (NPC) shunt active power filter performances evaluation using fuzzy control scheme for harmonic currents compensation. In Proceedings of the 2017 6th International Conference on Systems and Control (ICSC), Batna, Algeria, 7–9 May 2017; pp. 561–566. [Google Scholar]

- Morsli, A.; Tlemçani, A.; Cherchali, N.O.; Boucherit, M.S. Comparison between PI and fuzzy logic type-1 controllers for improvement the power quality by a shunt active power filter five-level NPC topology. In Proceedings of the 2016 8th International Conference on Modelling, Identification and Control (ICMIC), Algiers, Algeria, 15–17 November 2016; pp. 243–248. [Google Scholar]

- Bonala, A.K.; Sandepudi, S.R.; Muddineni, V.P. Improved model predictive current control for single-phase NPC shunt active power filter. In Proceedings of the 2016 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Kerala, India, 14–17 December 2016; pp. 1–6. [Google Scholar]

- Acuna, P.; Morán, L.; Rivera, M.; Aguilera, R.; Burgos, R.; Agelidis, V.G. A single-objective predictive control method for a multivariable single-phase three-level NPC converter-based active power filter. IEEE Trans. Ind. Electron. 2015, 62, 4598–4607. [Google Scholar] [CrossRef]

- Munoz, J.; Espinoza, J.; Baier, C.; Moran, L.; Guzman, J.; Cardenas, V. Decoupled and Modular Harmonic Compensation for Multilevel STATCOMs. IEEE Trans. Ind. Electron. 2014, 61, 2743–2753. [Google Scholar] [CrossRef]

- Rodriguez, J.; Lai, J.S.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Kim, S.H.; Kim, Y.H.; Seo, K.M.; Bang, S.S.; Kim, K.S. Harmonic analysis and output filter design of NPC multi-level inverters. In Proceedings of the 2006 37th IEEE Power Electronics Specialists Conference, Jeju, Korea, 18–22 June 2006; pp. 1–5. [Google Scholar] [CrossRef]

- Nasiri, M.R.; Farhangi, S.; Rodríguez, J. Model Predictive Control of a Multilevel CHB STATCOM in Wind Farm Application Using Diophantine Equations. IEEE Trans. Ind. Electron. 2019, 66, 1213–1223. [Google Scholar] [CrossRef]

- Dash, A.R.; Panda, A.K.; Patel, R.; Penthia, T. Design and implementation of a cascaded transformer coupled multilevel inverter-based shunt active filter under different grid voltage conditions. Int. Trans. Electr. Energy Syst. 2019, 29, 01–20. [Google Scholar] [CrossRef]

- Franquelo, L.G.; Rodriguez, J.; Leon, J.I.; Kouro, S.; Portillo, R.; Prats, M.A.M. The age of multilevel converters arrives. IEEE Ind. Electron. Mag. 2008, 2, 28–39. [Google Scholar] [CrossRef]

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Pérez, M.A.; Leon, J.I. Recent Advances and Industrial Applications of Multilevel Converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Kumar, R.; Bansal, H.O. Real-time implementation of adaptive PV-integrated SAPF to enhance power quality. Int. Trans. Electr. Energy Syst. 2019, 29, 01–22. [Google Scholar] [CrossRef]

- Radzi, M.A.M.; Rahim, N.A. Neural network and bandless hysteresis approach to control switched capacitor active power filter for reduction of harmonics. IEEE Trans. Ind. Electron. 2009, 56, 1477–1484. [Google Scholar] [CrossRef]

- Rodriguez, J.; Cortes, P. Predicitive Control of Power Converters and Electrical Drives; John Wiley & Sons, Ltd.: Hoboken, NJ, USA, 2012. [Google Scholar]

- Luo, A.; Xu, X.; Fang, L.; Fang, H.; Wu, J.; Wu, C. Feedback-feedforward PI-type iterative learning control strategy for hybrid active power filter with injection circuit. IEEE Trans. Ind. Electron. 2010, 57, 3767–3779. [Google Scholar] [CrossRef]

- Mu, X.; Wang, J.; Wu, W.; Blaabjerg, F. A Modified Multifrequency Passivity-Based Control for Shunt Active Power Filter With Model-Parameter-Adaptive Capability. IEEE Trans. Ind. Electron. 2018, 65, 760–769. [Google Scholar] [CrossRef]

- Sertac, B.; Hasan, K. A Sliding-Mode Controlled Single-Phase Grid-Connected Quasi-Z-Source NPC Inverter With Double-Line Frequency Ripple Suppression. IEEE Access 2019, 7, 160004–160016. [Google Scholar] [CrossRef]

- Martinez-Rodriguez, P.R.; Escobar-Valderrama, G.; Sosa-Zuniga, J.M.; Vazquez-Guzman, G.; Mendoza-Mendoza, J.d.J. Analysis and experimental validation of a controller for a single-phase active power filter based on a 3L-NPC topology. Int. Trans. Electr. Energy Syst. 2017, 27, e2385. [Google Scholar] [CrossRef]

- Barrena, J.; Marroyo, L.; Vidal, M.; Apraiz, J. Individual Voltage Balancing Strategy for PWM Cascaded H-Bridge Converter-Based STATCOM. IEEE Trans. Ind. Electron. 2008, 55, 21–29. [Google Scholar] [CrossRef]

- Bosch, S.; Staiger, J.; Steinhart, H. Predictive Current Control for an Active Power Filter With LCL-Filter. IEEE Trans. Ind. Electron. 2018, 65, 4943–4952. [Google Scholar] [CrossRef]

- Tarisciotti, L.; Formentini, A.; Gaeta, A.; Degano, M.; Zanchetta, P.; Rabbeni, R.; Pucci, M. Model Predictive Control for Shunt Active Filters with Fixed Switching Frequency. IEEE Trans. Ind. Appl. 2017, 53, 296–304. [Google Scholar] [CrossRef]

- Escobar, G.; Leyva-Ramos, J.; Carrasco, J.M.; Galvan, E.; Portillo, R.C.; Prats, M.M.; Franquelo, L.G. Modeling of a three level converter used in a synchronous rectifier application. In Proceedings of the 2004 IEEE 35th Annual Power Electronics Specialists Conference (IEEE Cat. No.04CH37551), Aachen, Germany, 20–25 June 2004; pp. 4306–4311. [Google Scholar] [CrossRef]

- Alepuz, S.; Busquets-Monge, S.; Bordonau, J.; Gago, J.; Gonzalez, D.; Balcells, J. Interfacing Renewable Energy Sources to the Utility Grid Using a Three-Level Inverter. IEEE Trans. Ind. Appl. 2006, 53, 1504–1511. [Google Scholar] [CrossRef]

- Valdez-Fernandez, A.; Martinez-Rodriguez, P.; Escobar, G.; Limones-Pozos, C.; Sosa, J. A Model-Based Controller for the Cascade H-Bridge Multilevel Converter Used as a Shunt Active Filter. IEEE Trans. Ind. Electron. 2013, 60, 5019–5028. [Google Scholar] [CrossRef]

- Escobar, G.; Martinez-Rodriguez, P.R.; Ho, C.N.M.; Sosa, J.M. Design of an inverter-side current reference and controller for a single-phase LCL-based grid-connected inverter. Int. Trans. Electr. Energy Syst. 2018, 28, e2476. [Google Scholar] [CrossRef]

- Khalil, H.K. Nonlinear Systems; Prentice Hall: Hoboken, NJ, USA, 2002. [Google Scholar]

- Francis, B.; Wonham, W. The internal Model Principle for Linear Multivariable Regulators. Appl. Math. Optim. 1975, 2, 170–194. [Google Scholar] [CrossRef]

| State | |||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 1 | −1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | + |

| 2 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | |

| 3 | 0 | −1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | |

| 4 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| 5 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 6 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 7 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | |

| 8 | −1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | |

| 9 | −1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | + |

| SAPF | NLL-L | NLL-H | |||

|---|---|---|---|---|---|

| Parameter | Value | Parameter | Value | Parameter | Value |

| 127 V at 60 Hz | |||||

| 3 mH | F | F | |||

| = | 1880 F | ||||

| 7 kHz | 8 mH | 7 mH | |||

| R | 40 k | ||||

| 100 |

| Tracking Loop | Regulation Loop | Balance Loop |

|---|---|---|

| = 20 | = 0.016 | = 0.0008 |

| = 300 | = 0.035 | = 0.01 |

| = 700 | = 60 | |

| = 1450 | = 220 | |

| = 800 | ||

| = 80 | ||

| = 60 | ||

| = 60 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Escobar, G.; Martinez-Rodriguez, P.R.; Iturriaga-Medina, S.; Vazquez-Guzman, G.; Sosa-Zuñiga, J.M.; Langarica-Cordoba, D. Control Design and Experimental Validation of a HB-NPC as a Shunt Active Power Filter. Energies 2020, 13, 1691. https://doi.org/10.3390/en13071691

Escobar G, Martinez-Rodriguez PR, Iturriaga-Medina S, Vazquez-Guzman G, Sosa-Zuñiga JM, Langarica-Cordoba D. Control Design and Experimental Validation of a HB-NPC as a Shunt Active Power Filter. Energies. 2020; 13(7):1691. https://doi.org/10.3390/en13071691

Chicago/Turabian StyleEscobar, Gerardo, Panfilo R. Martinez-Rodriguez, Samuel Iturriaga-Medina, Gerardo Vazquez-Guzman, Jose M. Sosa-Zuñiga, and Diego Langarica-Cordoba. 2020. "Control Design and Experimental Validation of a HB-NPC as a Shunt Active Power Filter" Energies 13, no. 7: 1691. https://doi.org/10.3390/en13071691

APA StyleEscobar, G., Martinez-Rodriguez, P. R., Iturriaga-Medina, S., Vazquez-Guzman, G., Sosa-Zuñiga, J. M., & Langarica-Cordoba, D. (2020). Control Design and Experimental Validation of a HB-NPC as a Shunt Active Power Filter. Energies, 13(7), 1691. https://doi.org/10.3390/en13071691