A Family of Single-Stage, Buck-Boost Inverters for Photovoltaic Applications

Abstract

1. Introduction

2. Single-Stage, Buck-Boost Inverter Family

- (1)

- Generating a grid-level AC output voltage from a relatively low DC input voltage without extra high gain DC-DC converters.

- (2)

- Having a low component count as single-stage topologies consisting of a single magnetic device and three or four switches.

- (3)

- A push-pull or half/full-bridge arrangement of the switches, where the commercial low-cost driver-integrated circuits can be easily used.

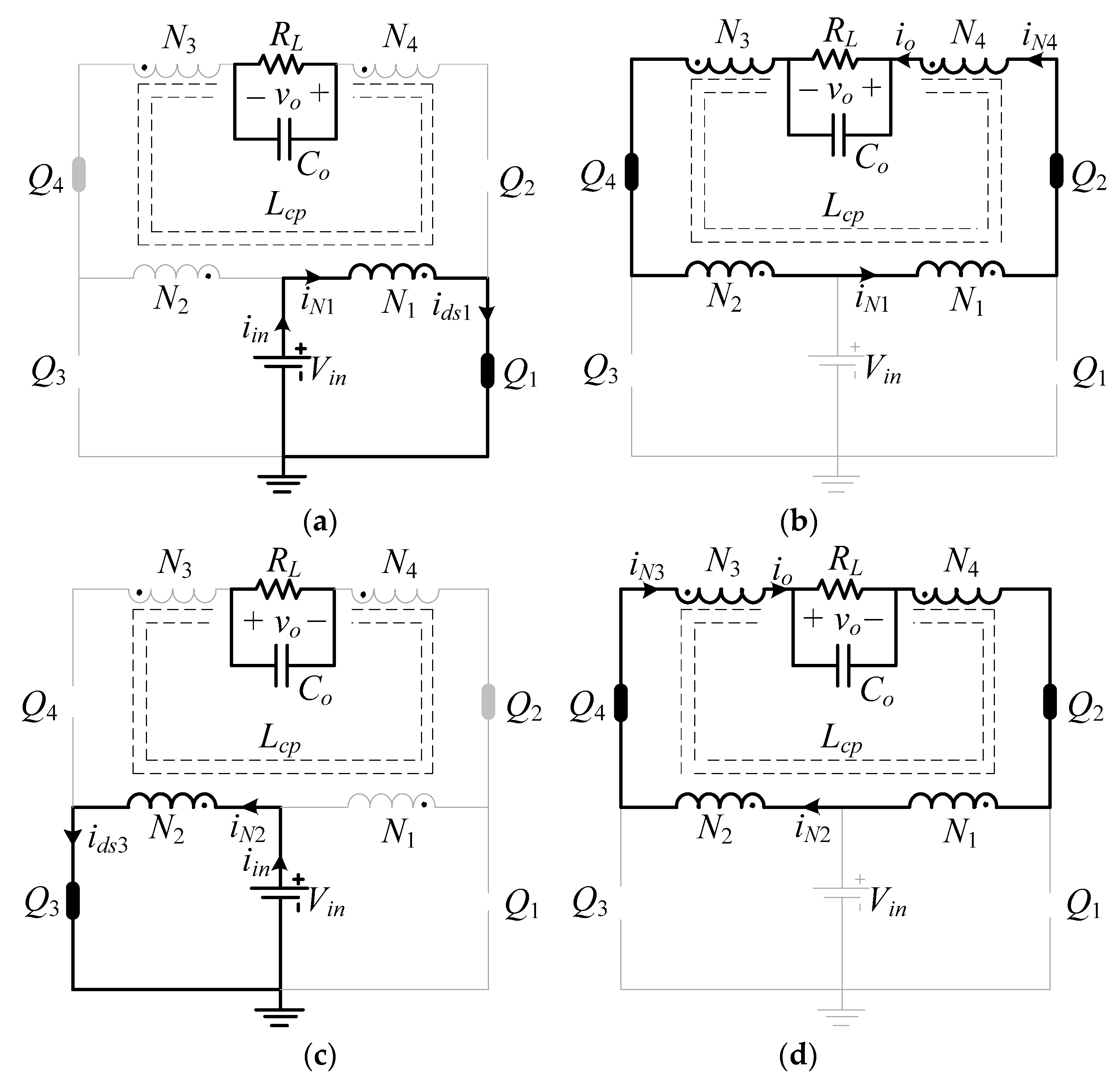

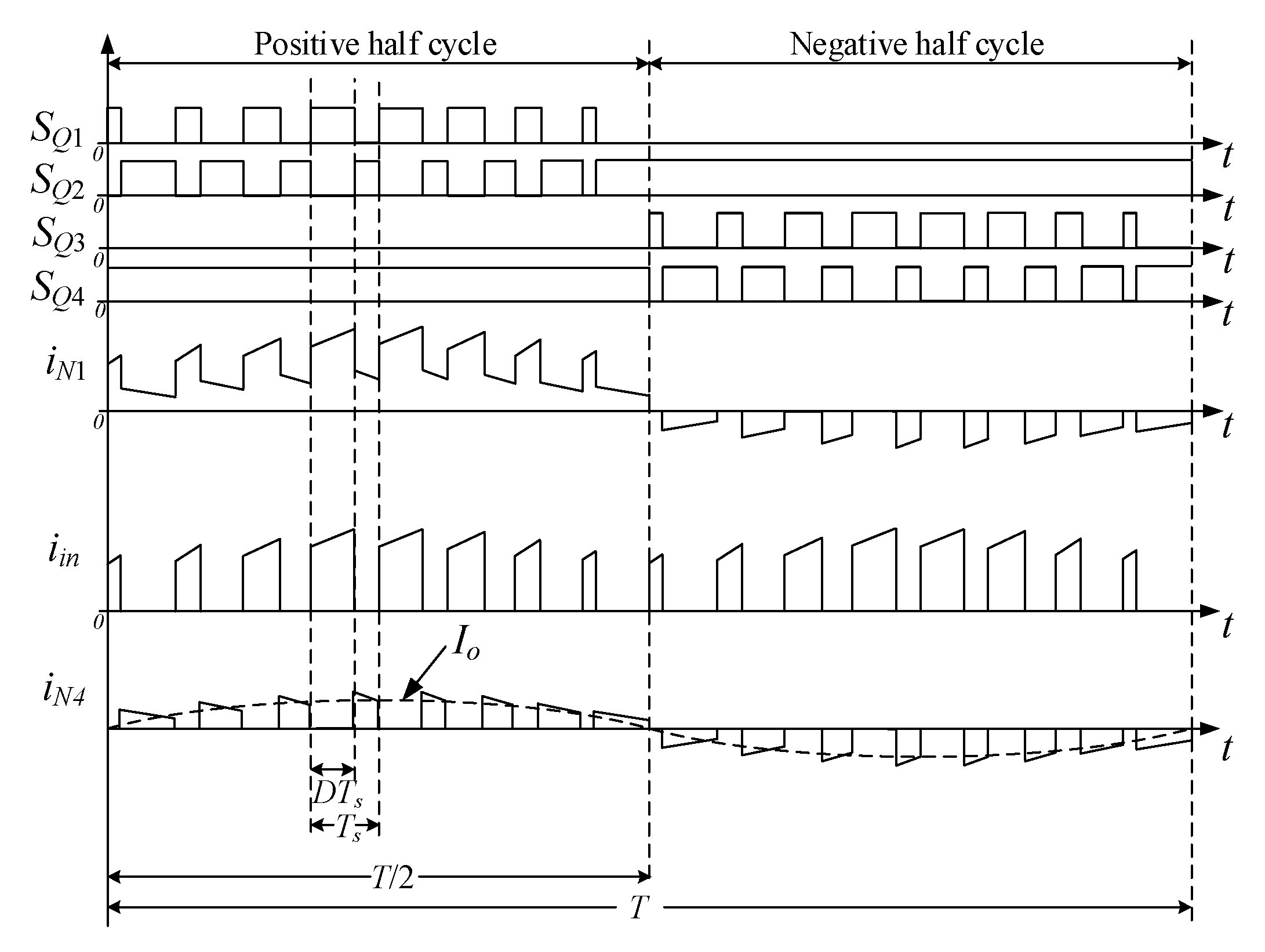

3. Operation Principles of the Proposed SSBBI

4. Analysis and Design Considerations of the Proposed SSBBI

4.1. CCM Voltage Gain

4.2. Turns Ratio and Duty Cycle Constraints

4.3. Voltage and Current Stress

4.3.1. Voltage Stress of Switches

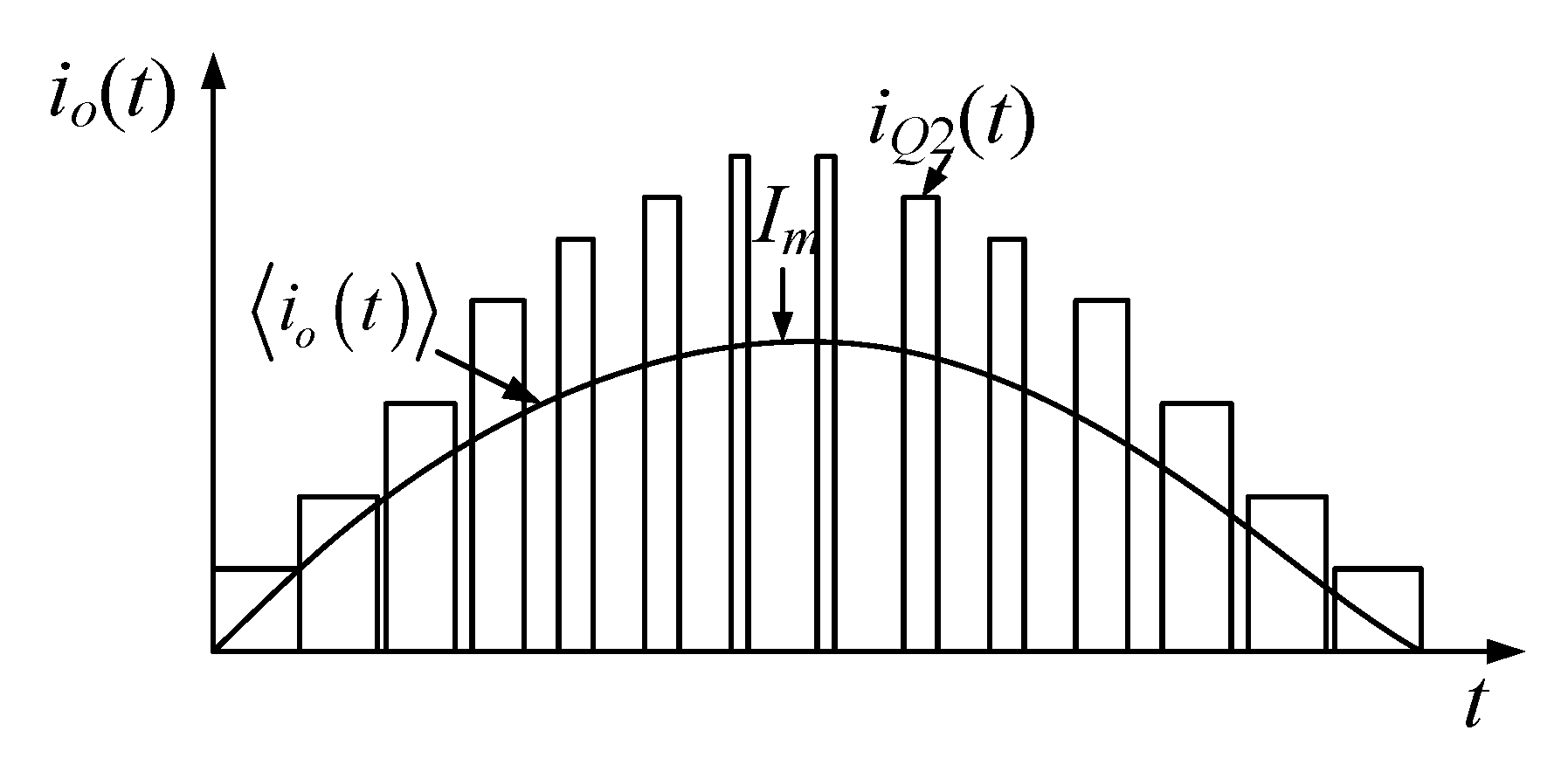

4.3.2. Analysis of Current Stress

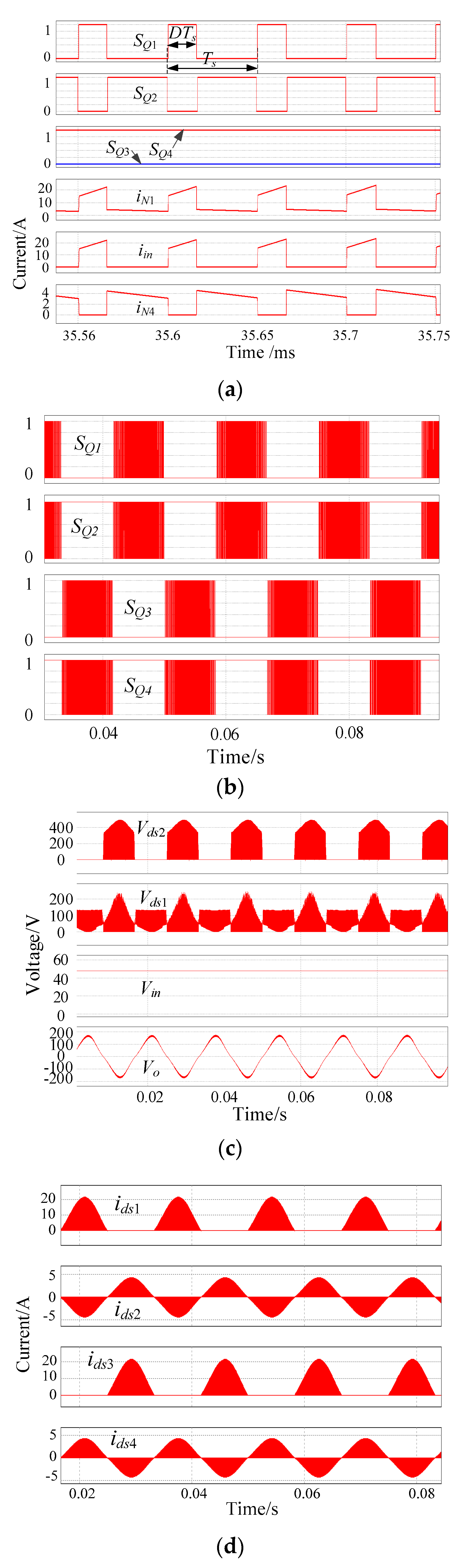

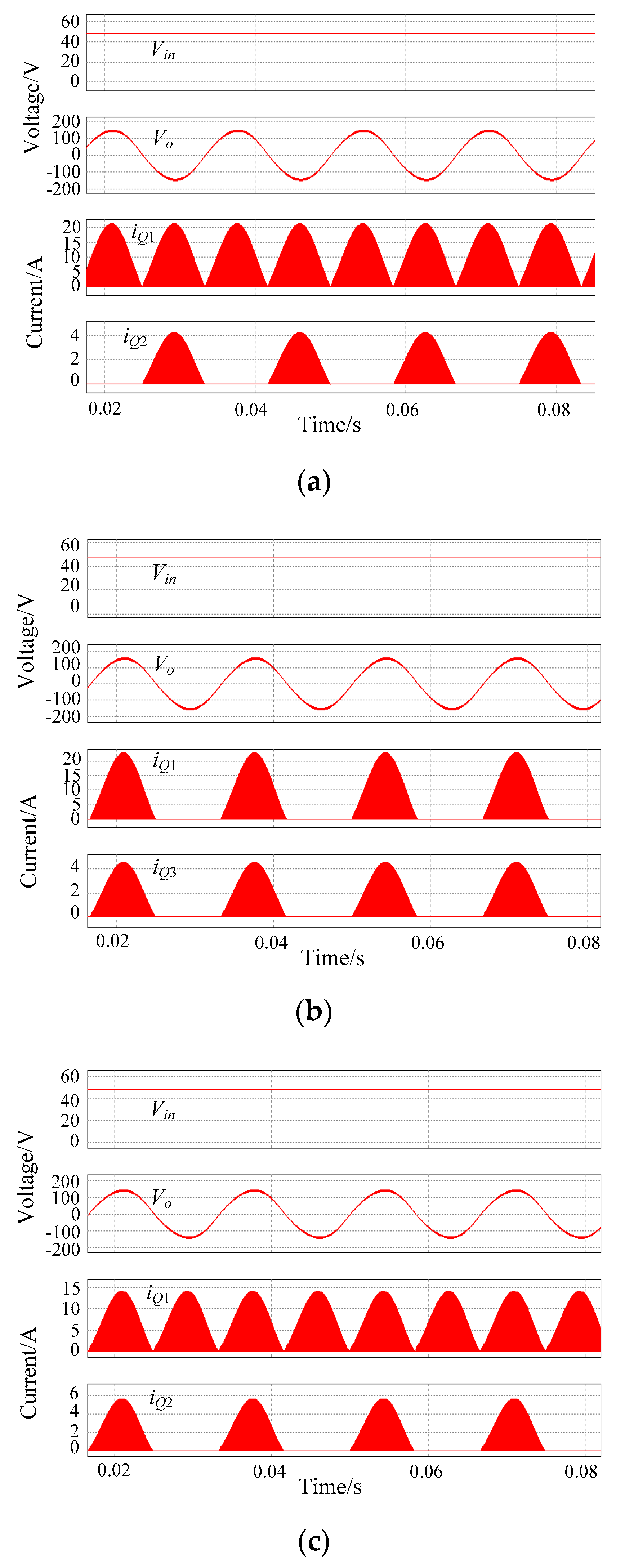

5. Simulation Results and Comparison

5.1. Basic System Operation

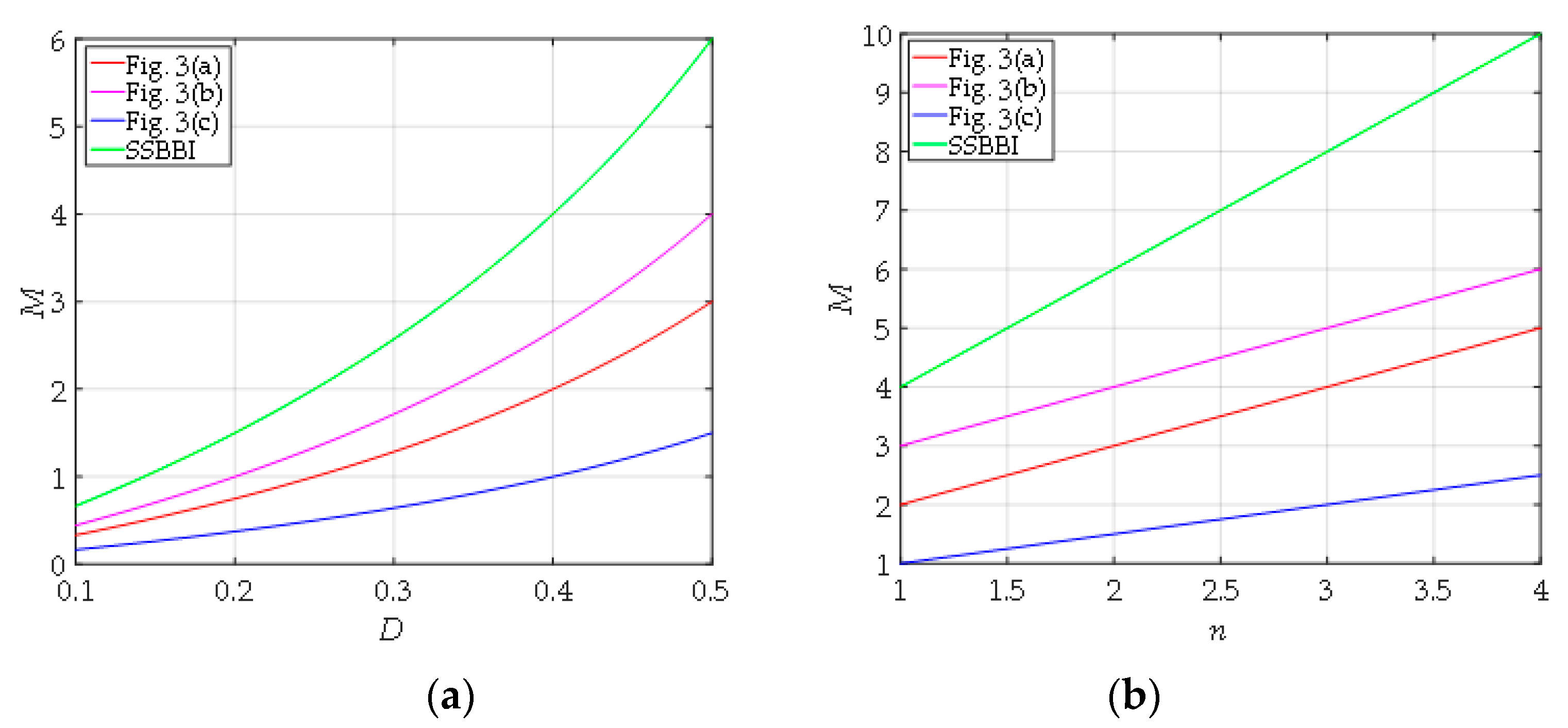

5.2. Comparison of the Proposed Single-Stage, Buck-Boost Inverter Family

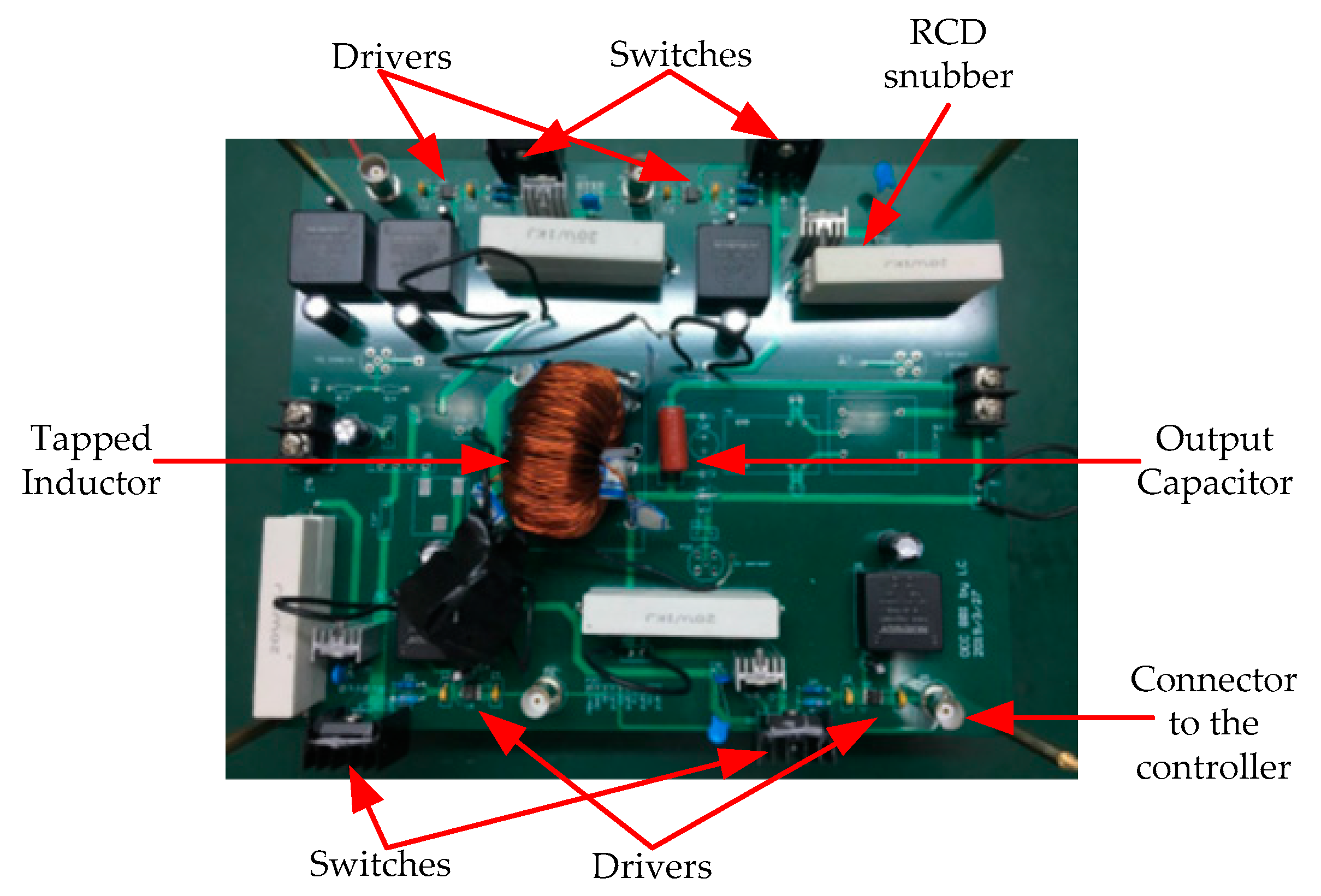

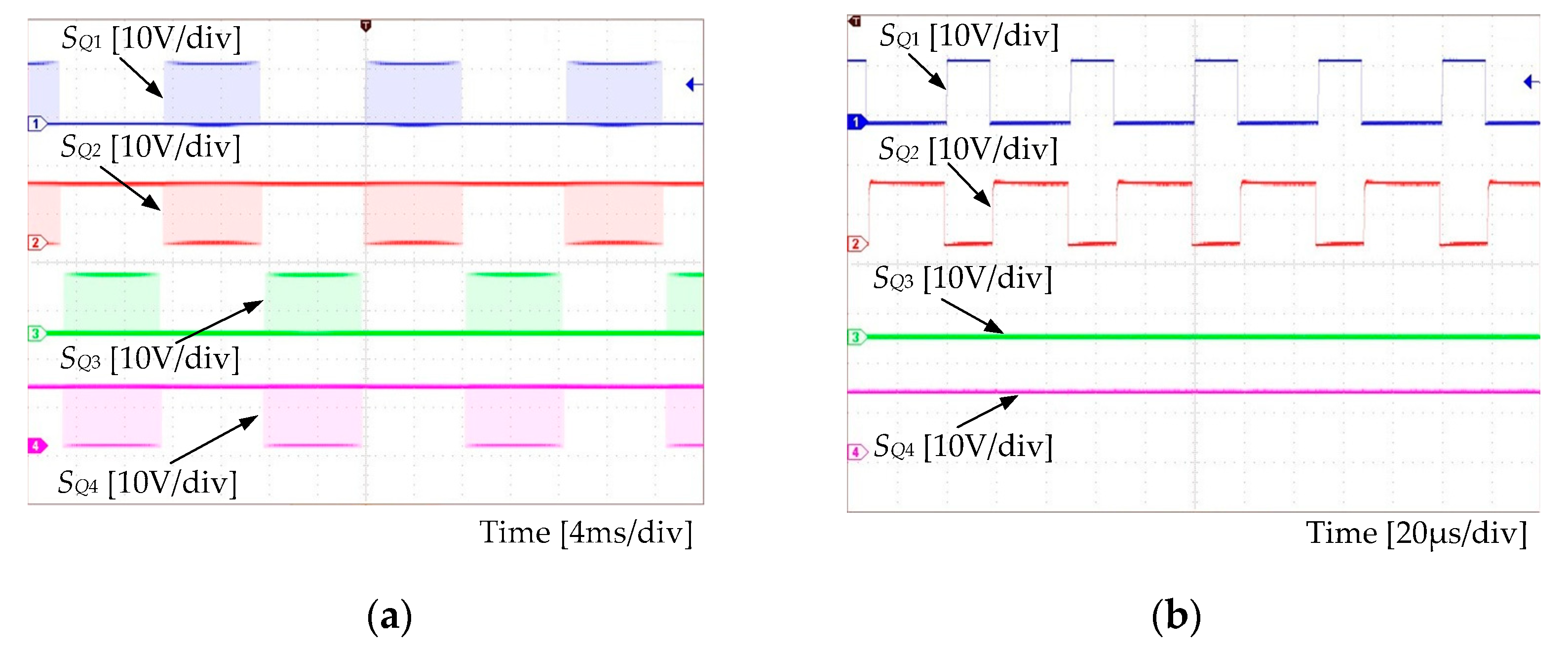

6. Experimental Results and Discussion

6.1. Experimental Results of SSBBI

6.2. Comparison of the SSBBI and the State of the Art

7. Conclusions

Author Contributions

Funding

Conflicts of Interest

Nomenclature

| n | Turns ratio of the tapped inductor |

| N1, N2, N3, N4 | Windings of the tapped inductor |

| Q1, Q2, Q3, Q4, Q5 | Switches (MOSFETs) |

| D1, D2 | Diodes |

| Lcp | Tapped inductor |

| RL | Equivalent load resistance |

| Co | Output capacitor |

| Vin | Input voltage |

| iin | Input current |

| vo | Output voltage |

| io | Output current |

| vds1, vds2, vds3, vds4 | Drain-source voltage of the switches Q1–Q4 |

| ids1, ids2, ids3, ids4 | Currents through the switches Q1–Q4 |

| D | Duty cycle |

| Ts | Switching period |

| iN1, iN2, iN3, iN4 | Currents through the windings |

| SQ1, SQ2, SQ3, SQ4 | Gating signals the switches Q1–Q4 |

| Io | Average output current |

| M | Voltage gain |

| Vomax | Maximum output voltage |

| Dmax | Maximum duty ratio |

| VQ1max, VQ2 max, VQ3 max, VQ4 max | Voltage stress on the switches Q1–Q4 |

| vo(t) | Time-varying output voltage |

| io(t) | Time-varying output current |

| Vm | Peak output voltage |

| Im | Peak output current |

| ω | Angular frequency |

| d(t) | Time-varying duty ratio |

| IQ1max, IQ2max | Maximum current of the switch Q1, Q2 |

| , | Squared RMS current of the switch Q1, Q2 within a switching period |

| , | Squared RMS current of the switch Q1, Q2 |

| IQ1rms, IQ2rms | RMS current of the switch Q1, Q2 |

| fs | Switching frequency |

| Lm | Tapped-inductor magnetizing inductance |

Abbreviations

| DC | Direct current |

| AC | Alternating current |

| PV MIE/MIC | Photovoltaic Module-integrated electronic/converter |

| MPPT | Maximum power point tracking |

| SEPIC | Single ended primary inductor converter |

| PWM MOSFET | Pulse width modulation Metal oxide semiconductor field-effect transistor |

| GaN | Gallium nitride |

| SSBBI | Single-stage, buck-boost inverter |

| CCM | Continuous conduction mode |

| SPWM | Sinusoidal pulse width modulation |

| THD RMS | Total harmonic distortion Root mean square |

| RCD | Resistor-capacitor-diode |

References

- Meneses, D.; Blaabjerg, F.; Garcia, O.; Cobos, J.A. Review and comparison of step-up transformerless topologies for photovoltaic AC-module application. IEEE Trans. Power Electron. 2013, 28, 2649–2663. [Google Scholar] [CrossRef]

- Fang, Y.; Ma, X. A novel PV microinverter with coupled inductors and double-boost topology. IEEE Trans. Power Electron. 2010, 25, 3139–3147. [Google Scholar] [CrossRef]

- Abramovitz, A.; Zhao, B.; Smedley, K.M. High-gain single-stage boosting inverter for photovoltaic applications. IEEE Trans. Power Electron. 2016, 31, 3550–3558. [Google Scholar] [CrossRef]

- Zhang, Y.; Woldegiorgis, A.T.; Chang, L. Design and test of a novel buck-boost inverter with three switching devices. In Proceedings of the 2012 Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 5–9 February 2012. [Google Scholar]

- Chowdhury, A.S.K.; Chakraborty, S.; Salam, K.M.A.; Razzak, M.A. Design of a single-stage grid-connected buck-boost photovoltaic inverter for residential application. In Proceedings of the 2014 Power and Energy Systems: Towards Sustainable Energy, Bangalore, India, 13–15 March 2014. [Google Scholar]

- Kumar, A.; Gautam, V.; Sensarma, P. A SEPIC derived single-stage buck-boost inverter for photovoltaic applications. In Proceedings of the 2014 IEEE International Conference on Industrial Technology (ICIT), Busan, Korea, 26 February–1 March 2014. [Google Scholar]

- Kumar, A.; Sensarma, P. A four-switch single-stage single-phase buck-boost inverter. IEEE Trans. Power Electron. 2017, 32, 5282–5292. [Google Scholar] [CrossRef]

- Kumar, A.; Sensarma, P. New switching strategy for single-mode operation of a single-stage buck-boost inverter. IEEE Trans. Power Electron. 2018, 33, 5927–5936. [Google Scholar] [CrossRef]

- Akbar, F.; Cha, H.; Lee, S.; Nguyen, T. A single-phase transformerless buck-boost inverter for standalone and grid-tied applications with reduced magnetic volume. In Proceedings of the 2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019-ECCE Asia), Busan, Korea, 27–30 May 2019. [Google Scholar]

- Mostaan, A.; Abdelhakim, A.; Soltani, M.; Blaabjerg, F. Single-phase transformer-less buck-boost inverter with zero leakage current for PV systems. In Proceedings of the 2017 43rd Annual Conference of the IEEE Industrial Electronics Society (IECON), Beijing, China, 29 October–1 November 2017. [Google Scholar]

- Muhammedali Shafeeque, K.; Subadhra, P.R. A novel single-stage DC-AC boost inverter for solar power extraction. In Proceedings of the 2013 Annual International Conference on Emerging Research Areas and 2013 International Conference on Microelectronics, Communications and Renewable Energy, Kanjirapally, India, 4–6 June 2013. [Google Scholar]

- Wu, W.; Ji, J.; Blaabjerg, F. Aalborg inverter -a new type of “buck in buck, boost in boost” grid-tied inverter. IEEE Trans. Power Electron. 2015, 30, 4784–4793. [Google Scholar] [CrossRef]

- Xu, S.; Chang, L.; Shao, R.; Mohomad, A.R.H. Power decoupling method for single-phase buck-boost inverter with energy-based control. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017. [Google Scholar]

- Xu, S.; Shao, R.; Chang, L.; Mao, M. Single-phase differential buck-boost inverter with pulse energy modulation and power decoupling control. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 2060–2072. [Google Scholar] [CrossRef]

- Tang, Y.; Dong, X.; He, Y. Active buck-boost inverter. IEEE Trans. Ind. Electron. 2014, 61, 4691–4697. [Google Scholar] [CrossRef]

- Tang, Y.; Xu, F.; Bai, Y.; He, Y. Comparative analysis of two modulation strategies for an active buck-boost inverter. IEEE Trans. Power Electron. 2016, 31, 7963–7971. [Google Scholar] [CrossRef]

- Huang, Q.; Huang, A.Q.; Yu, R.; Liu, P.; Yu, W. High-efficiency and high-density single-phase dual-mode cascaded buck-boost multilevel transformerless PV inverter with GaN AC switches. IEEE Trans. Power Electron. 2019, 34, 7474–7488. [Google Scholar] [CrossRef]

- Khan, A.A.; Cha, H.; Ahmed, H.F.; Kim, J.; Cho, J. A highly reliable and high-efficiency quasi single-stage buck-boost inverter. IEEE Trans. Power Electron. 2017, 32, 4185–4198. [Google Scholar] [CrossRef]

- Khan, A.A.; Cha, H. Dual-buck-structured high-reliability and high-efficiency single-stage buck-boost inverters. IEEE Trans. Ind. Electron. 2018, 65, 3176–3187. [Google Scholar] [CrossRef]

- Ho, C.N.M.; Siu, K.K.M. Manitoba inverter---single-phase single-stage buck-boost VSI topology. IEEE Trans. Power Electron. 2019, 34, 3445–3456. [Google Scholar] [CrossRef]

- Testa, A.; Caro, S.D.; Scimone, T.; Panarello, S. A buck-boost based DC/AC converter for residential PV applications. In Proceedings of the International Symposium on Power Electronics, Electrical Drives, Automation and Motion, Sorrento, Italy, 20–22 June 2012. [Google Scholar]

- Abdel-Rahim, O.; Orabi, M.; Ahmed, M.E. Buck-boost interleaved inverter for a grid-connected photovoltaic system. In Proceedings of the 2010 IEEE International Conference on Power and Energy, Kuala Lumpur, Malaysia, 29 November–1 December 2010. [Google Scholar]

- Tang, Y.; He, Y.; Dong, X. Active buck-boost inverter with coupled inductors. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014. [Google Scholar]

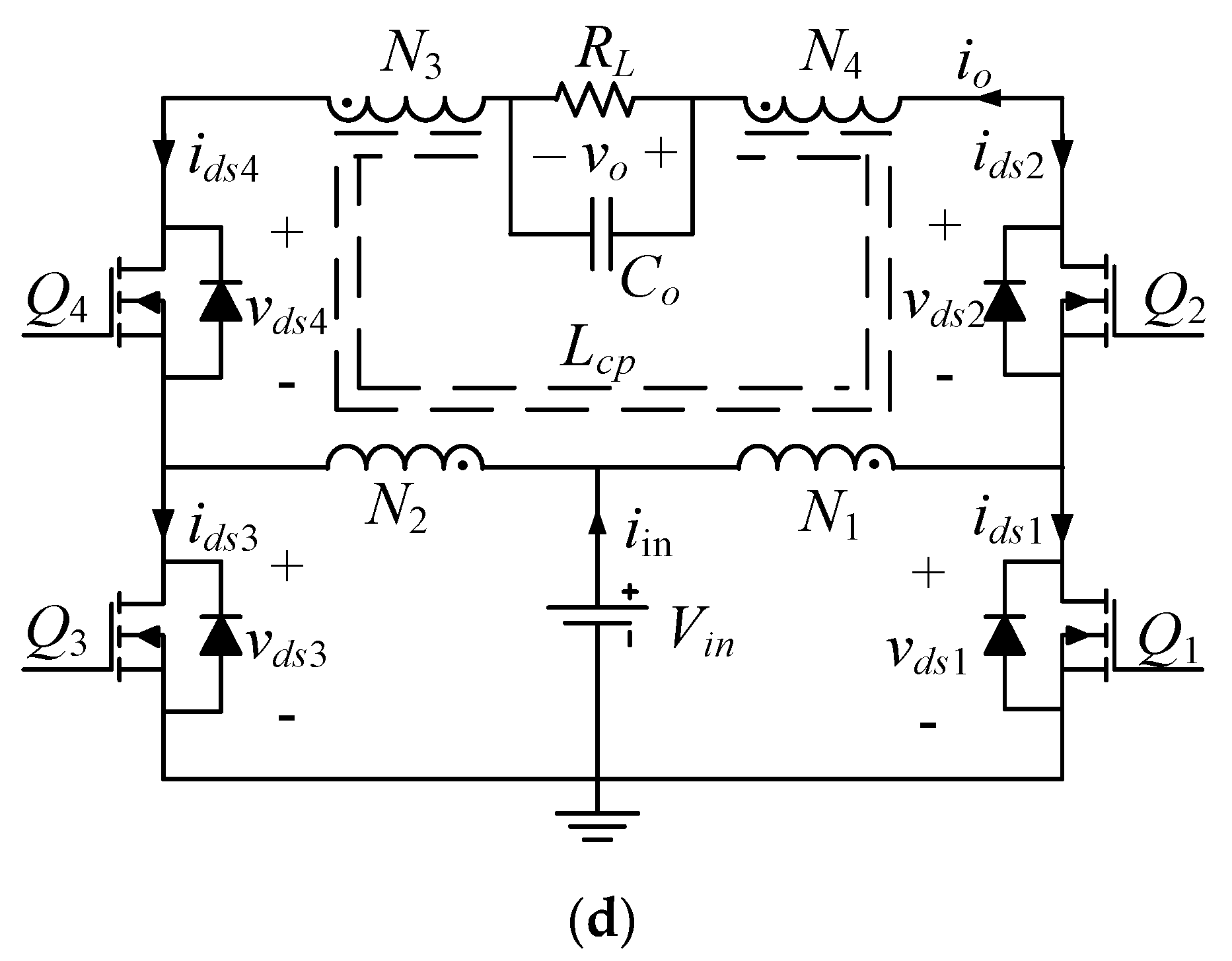

- Husev, O.; Matiushkin, O.; Roncero-Clemente, C.; Blaabjerg, F.; Vinnikov, D. Novel family of single-stage buck-boost inverters on the unfolding circuit. IEEE Trans. Power Electron. 2019, 34, 7662–7676. [Google Scholar] [CrossRef]

- Sreekanth, T.; Lakshminarasamma, N.; Mishra, M.K. Coupled inductor-based single-stage high gain DC-AC buck-boost inverter. IET Power Electron. 2016, 9, 1590–1599. [Google Scholar] [CrossRef]

- Sreekanth, T.; Lakshminarasamma, N.; Mishra, M.K. A single-stage grid-connected high gain buck-boost inverter with maximum power point tracking. IEEE Trans. Energy Convers. 2017, 32, 330–339. [Google Scholar] [CrossRef]

- Zhao, B.; Abramovitz, A.; Smedley, K. Family of bridgeless buck-boost PFC rectifiers. IEEE Trans. Power Electron. 2015, 30, 6524–6527. [Google Scholar] [CrossRef]

- Zhao, B.; Ma, R.; Abramovitz, A.; Smedley, K. Bridgeless buck-boost PFC rectifier with a bi-directional switch. In Proceedings of the 2016 IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, China, 22–26 May 2016. [Google Scholar]

- Zhao, B.; Abramovitz, A.; Ma, R.; Huangfu, Y. High gain single stage buck-boost inverter. In Proceedings of the 2017 20th International Conference on Electrical Machines and Systems (ICEMS), Sydney, Australia, 11–14 August 2017. [Google Scholar]

- Zhao, B.; Abramovitz, A.; Ma, R.; Liang, B. One-cycle-controlled high gain single stage buck-boost inverter for photovoltaic application. In Proceedings of the 43rd Annual Conference of the IEEE Industrial Electronics Society (IECON), Beijing, China, 29 October–1 November 2017. [Google Scholar]

- Design Guide of Inductor. Available online: www.mag-inc.com (accessed on 10 January 2020).

- Abramovitz, A.; Smedley, M.K. Analysis and design of a tapped-inductor buck-boost PFC rectifier with low bus voltage. IEEE Trans. Power Electron. 2011, 26, 2637–2649. [Google Scholar] [CrossRef]

| Ref. | Switches Count | Diodes Count | Inductors Count | Input Voltage | Output Voltage | Output Power | Efficiency |

|---|---|---|---|---|---|---|---|

| [22] | 4 | 8 | 4 | 20 V | 314 V | 100 W | / |

| [23] | 8 | 0 | 1 Tapped | 100–200 V | 110 V | 500 W | >96% |

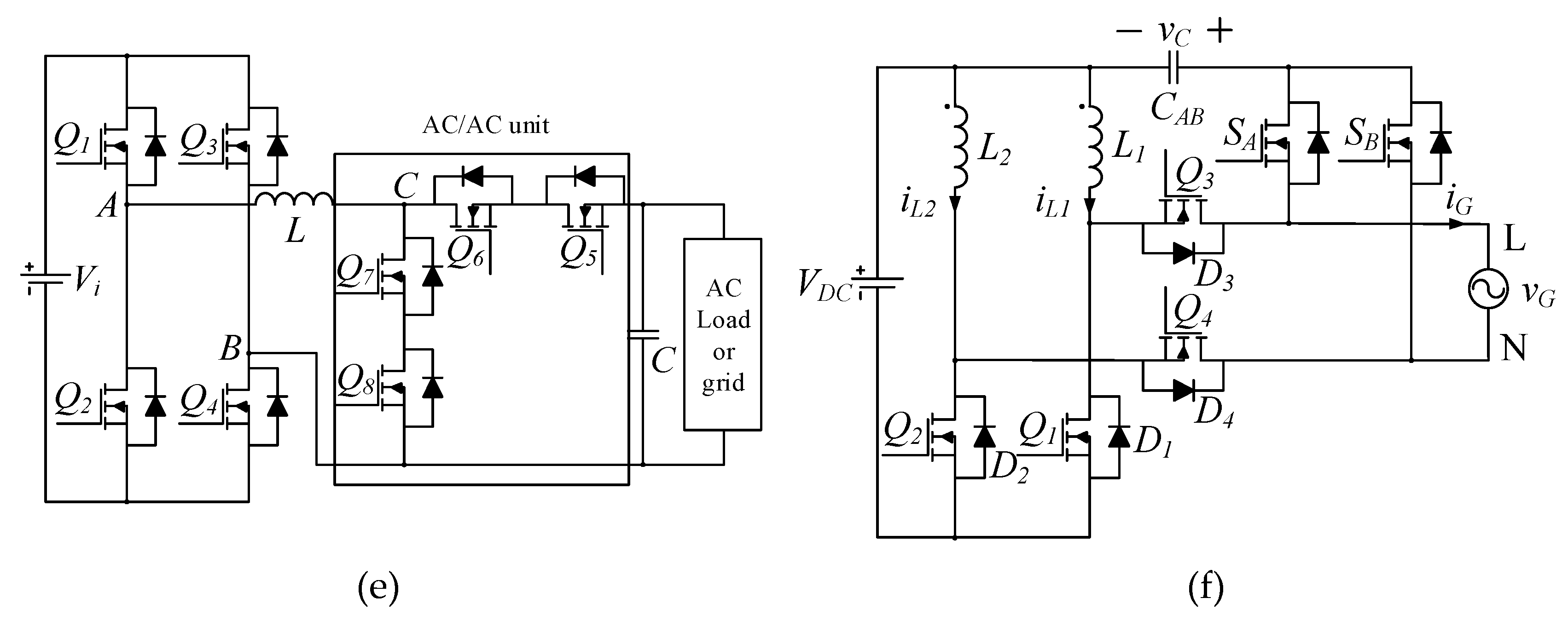

| Figure 2b [24] | 8 | 0 | 1 Tapped | 40 V | 230 V | / | / |

| [25] | 5 | 2 | 1 Tapped | 60 V | 230 V | 100 W | 86% |

| Topologies | Switches | Diodes | Windings | Filter Cap. |

|---|---|---|---|---|

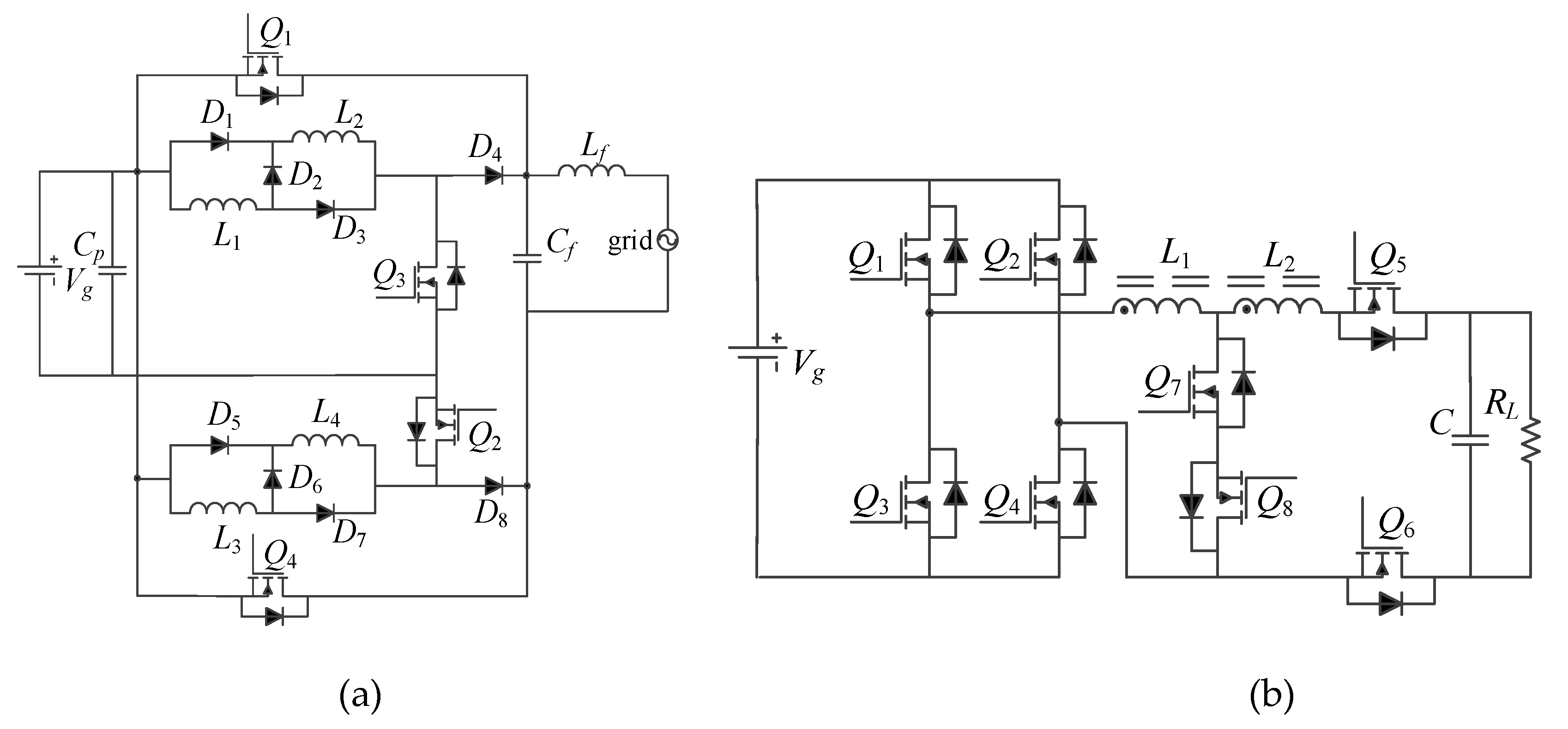

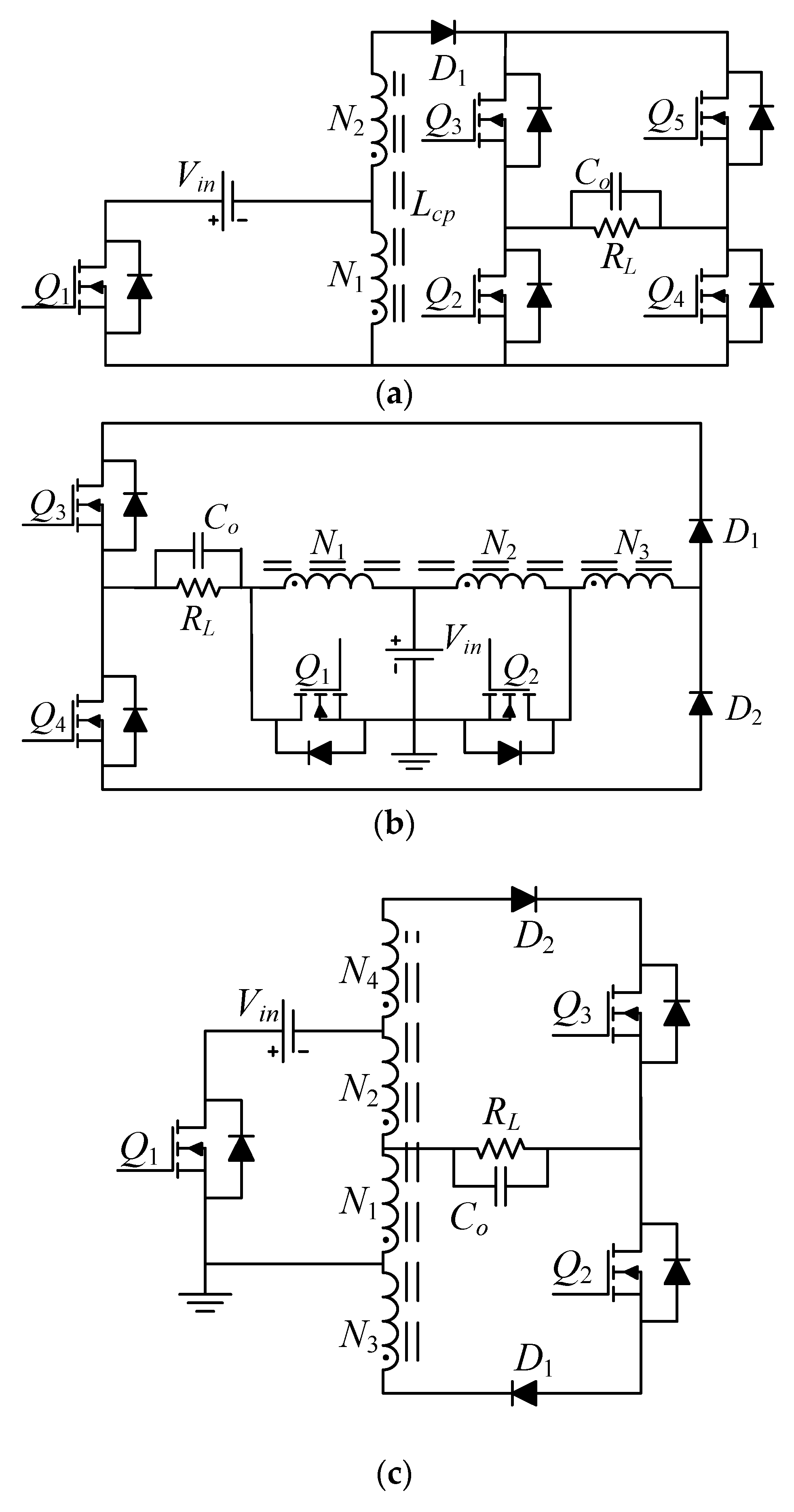

| Figure 3a | 5 | 1 | 2 | 1 |

| Figure 3b | 4 | 2 | 3 | 1 |

| Figure 3c | 3 | 2 | 4 | 1 |

| Figure 3d | 4 | 0 | 4 | 1 |

| Switches | Positive Output Voltage | Negative Output Voltage | ||

|---|---|---|---|---|

| State A | State B | State A’ | State B’ | |

| Q1 | On | Off | Off | Off |

| Q2 | Off | On | On | On |

| Q3 | Off | Off | On | Off |

| Q4 | On | On | Off | On |

| Switches | Voltage Stress | Current Stress | |

|---|---|---|---|

| Peak | RMS | ||

| Q1, Q3 | 2Vin | ||

| Q2, Q4 | 2(n+1)Vin+Vomax | ||

| Topology | Voltage Gain M = vo/Vin |

|---|---|

| Figure 3a | |

| Figure 3b | |

| Figure 3c | |

| SSBBI |

| Topology | Voltage Stress | ||

|---|---|---|---|

| Low Side Switches | High Side Switches | Diodes | |

| Figure 3a | Vomax | (n+1)Vin+Vomax | |

| Figure 3b | 2Vin | (n+2)Vin+Vomax | (n+2)Vin+Vomax |

| Figure 3c | 2Vomax | ||

| SSBBI | 2Vin | 2(n+1)Vin+Vomax | / |

| Topology | Peak Current Stress | ||

|---|---|---|---|

| Low Side Switches | High Side Switches | Diodes | |

| Figure 3a | |||

| Figure 3b | |||

| Figure 3c | |||

| SSBBI | / | ||

| Topology | RMS Current Stress | ||

|---|---|---|---|

| Low Side Switches | High Side Switches | Diodes | |

| Figure 3a | |||

| Figure 3b | |||

| Figure 3c | |||

| SSBBI | / | ||

| Components | Value/Model |

|---|---|

| High side switches | IPW90R340C3 |

| Low side switches | IPW65R125C |

| Driver ICs | 1EDI20N12AF |

| Primary magnetizing inductance | 100 μH |

| Inductor core | 55439A2 |

| Inductor Turns | 30/45 |

| Output capacitor | 2.2 μF |

| Topologies | Switches Count | Diodes Count | Inductors Count | Input Voltage | Output Voltage | Output Power | Efficiency |

|---|---|---|---|---|---|---|---|

| [22] | 4 | 8 | 4 | 20 V | 314 V | 100 W | / |

| [23] | 8 | 0 | 1 Tapped | 100–200 V | 110 V | 500 W | >96% |

| Figure 2b [24] | 8 | 0 | 1 Tapped | 40 V | 230 V | / | / |

| [25] | 5 | 2 | 1 Tapped | 60 V | 230 V | 100 W | 86% |

| SSBBI | 4 | 0 | 1 Tapped | 48 V | 110 V | 100 W | 75% |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhao, B.; Abramovitz, A.; Liu, C.; Yang, Y.; Huangfu, Y. A Family of Single-Stage, Buck-Boost Inverters for Photovoltaic Applications. Energies 2020, 13, 1675. https://doi.org/10.3390/en13071675

Zhao B, Abramovitz A, Liu C, Yang Y, Huangfu Y. A Family of Single-Stage, Buck-Boost Inverters for Photovoltaic Applications. Energies. 2020; 13(7):1675. https://doi.org/10.3390/en13071675

Chicago/Turabian StyleZhao, Ben, Alexander Abramovitz, Chang Liu, Yongheng Yang, and Yigeng Huangfu. 2020. "A Family of Single-Stage, Buck-Boost Inverters for Photovoltaic Applications" Energies 13, no. 7: 1675. https://doi.org/10.3390/en13071675

APA StyleZhao, B., Abramovitz, A., Liu, C., Yang, Y., & Huangfu, Y. (2020). A Family of Single-Stage, Buck-Boost Inverters for Photovoltaic Applications. Energies, 13(7), 1675. https://doi.org/10.3390/en13071675