One Cycle Control of a PWM Rectifier a New Approach

Abstract

1. Introduction

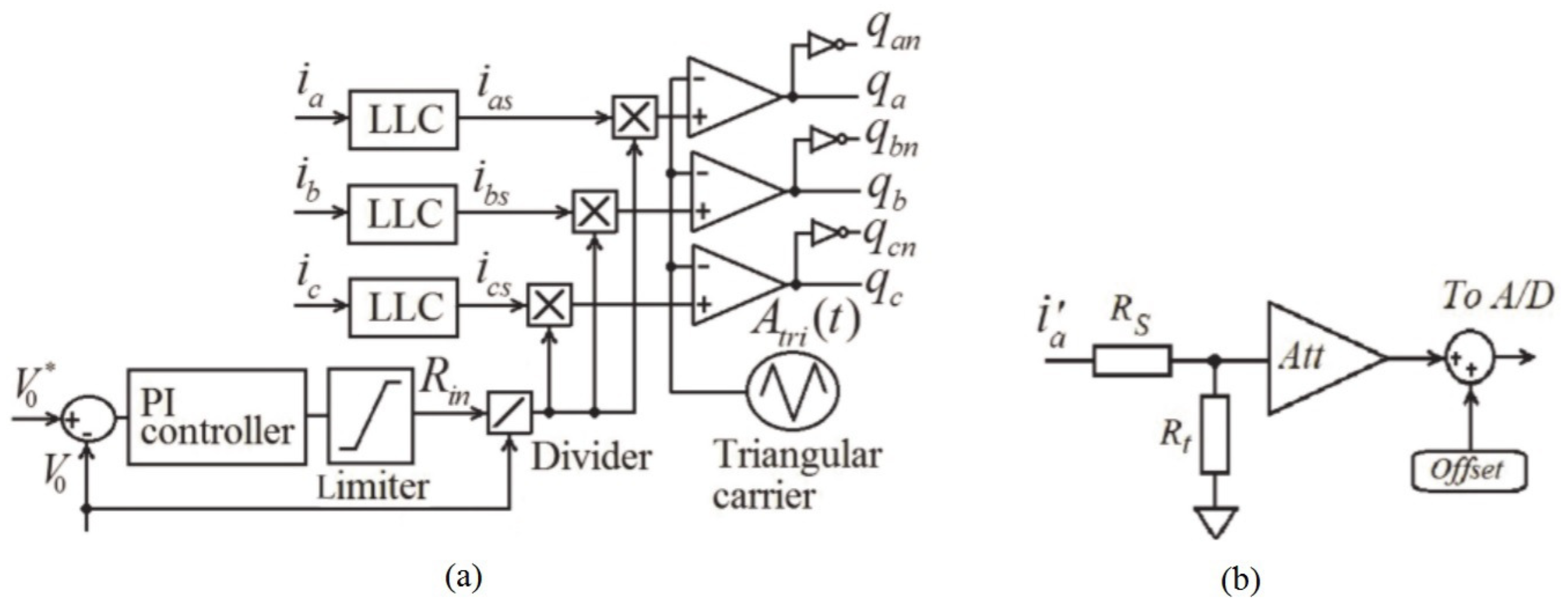

2. Fundamentals of Software-OCC

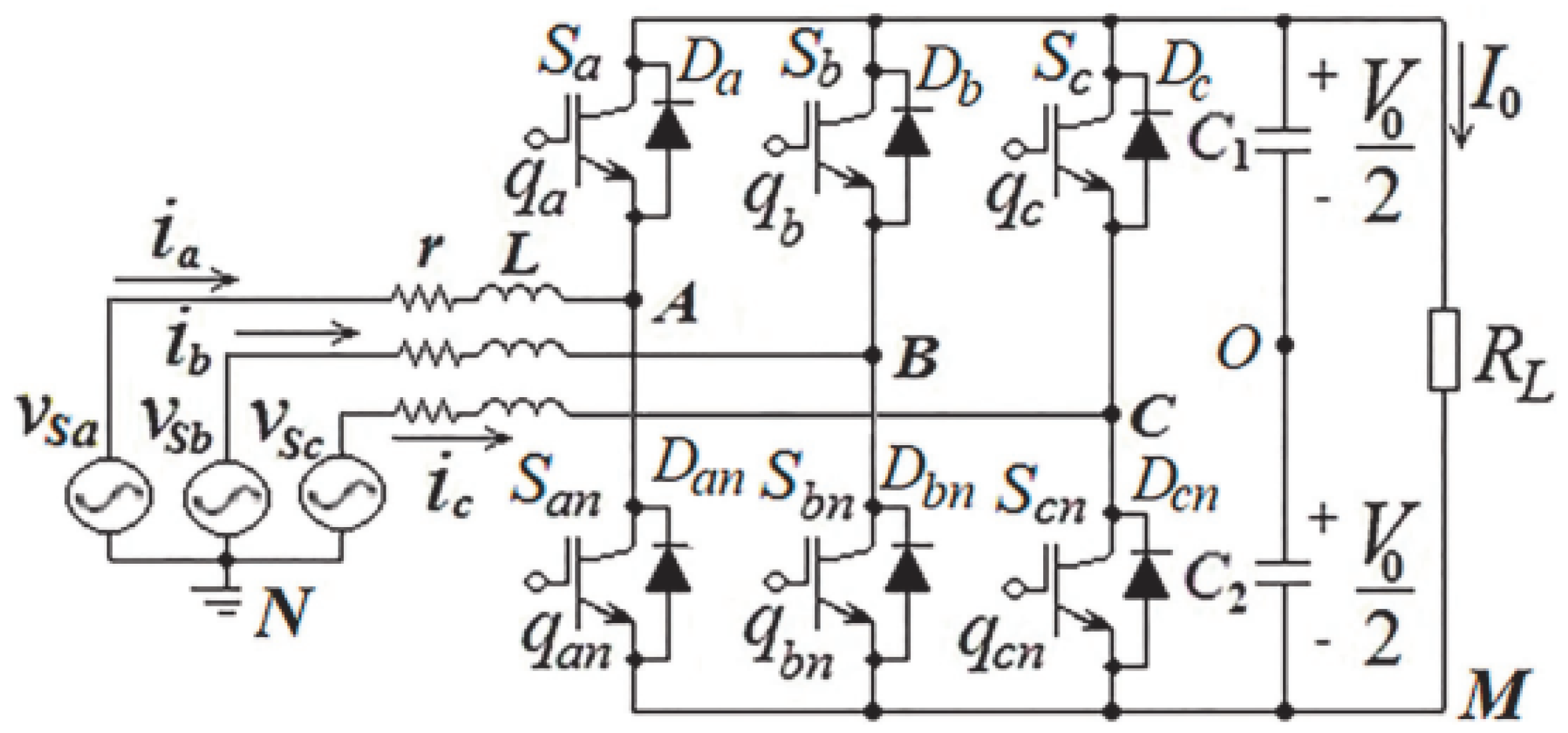

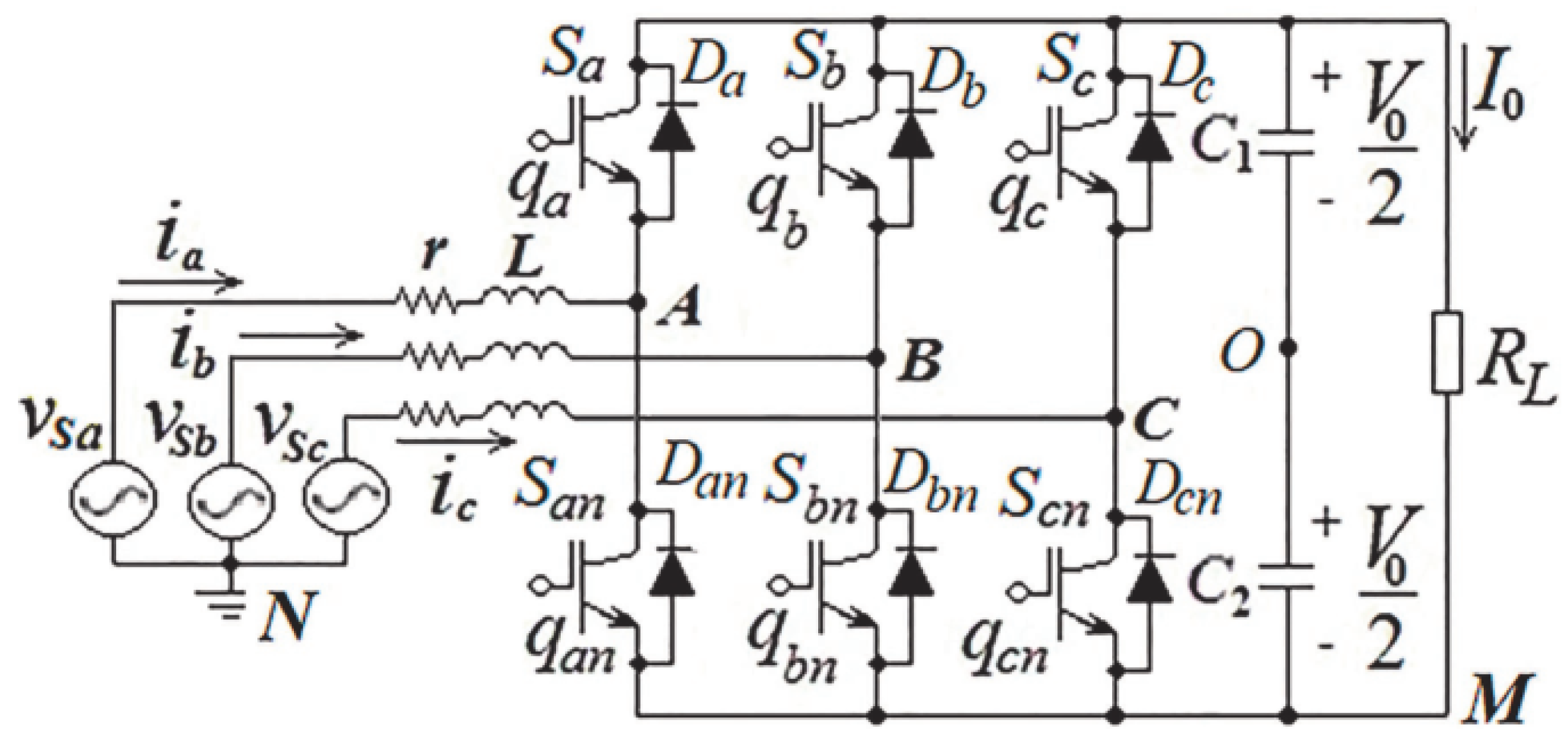

- The switching frequency is much higher than line frequency f, hence the switching period is much lower than the line period T, so and .

- The switches in each leg operate in a complementary fashion, i.e., the duty cycle for the upper and bottom switch is and , respectively (), .

- (i)

- Multipliers and dividers presence, as they are not much DSP time-consuming [43].

- (ii)

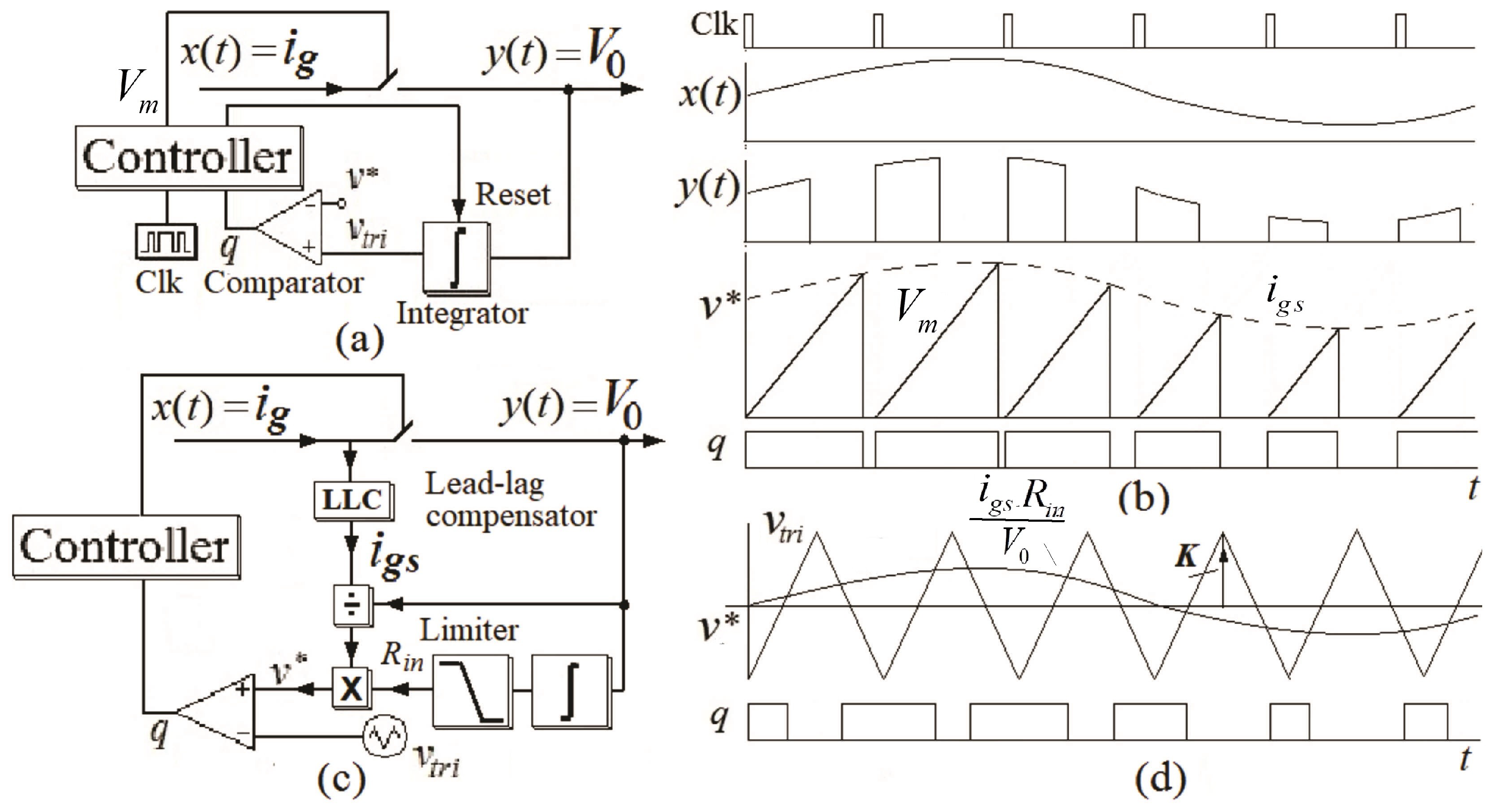

- The average method, i.e., a LLC (Figure 1c) decreases the delay response caused by the lagging part, using a leading constant.

- (iii)

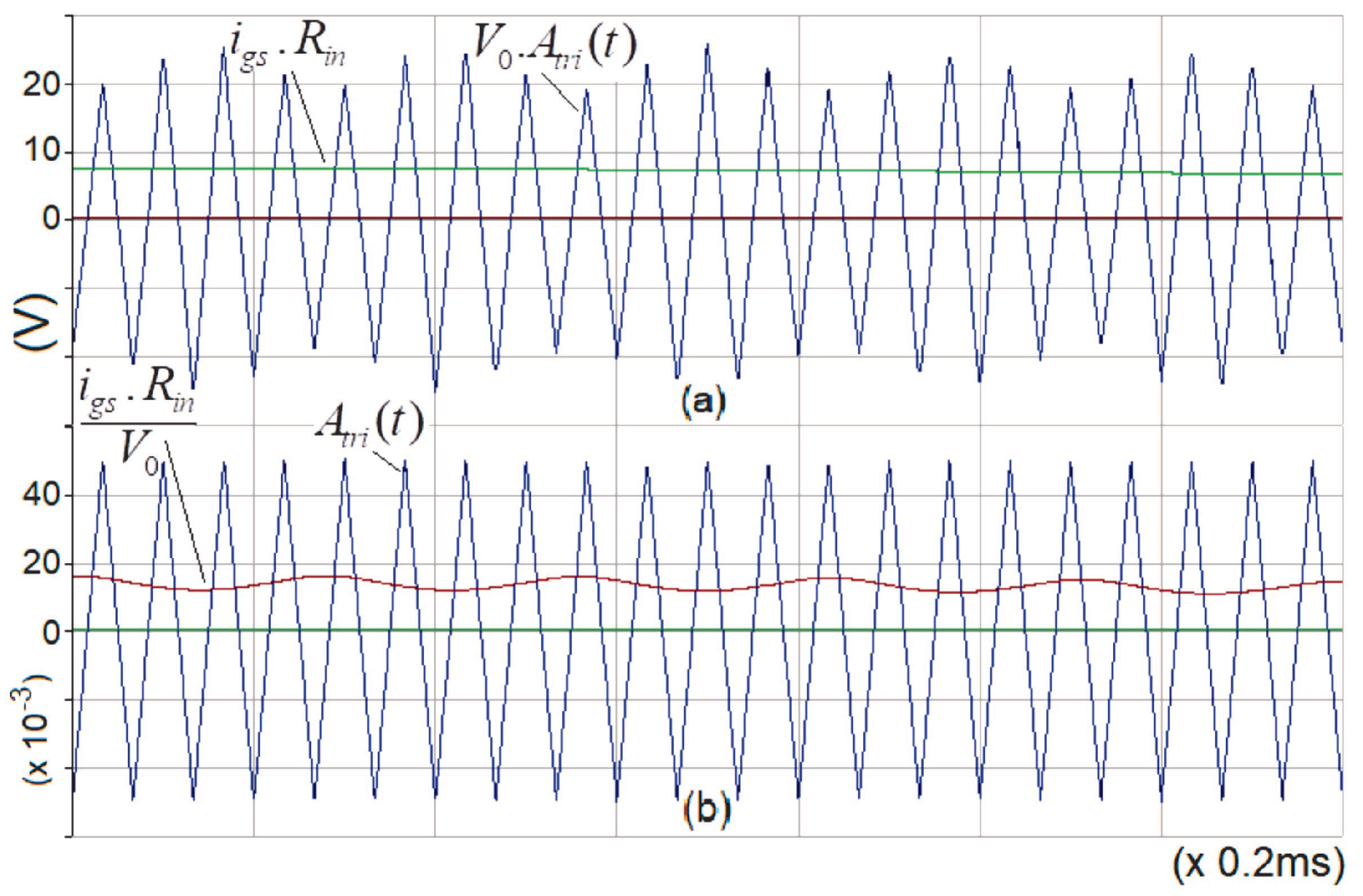

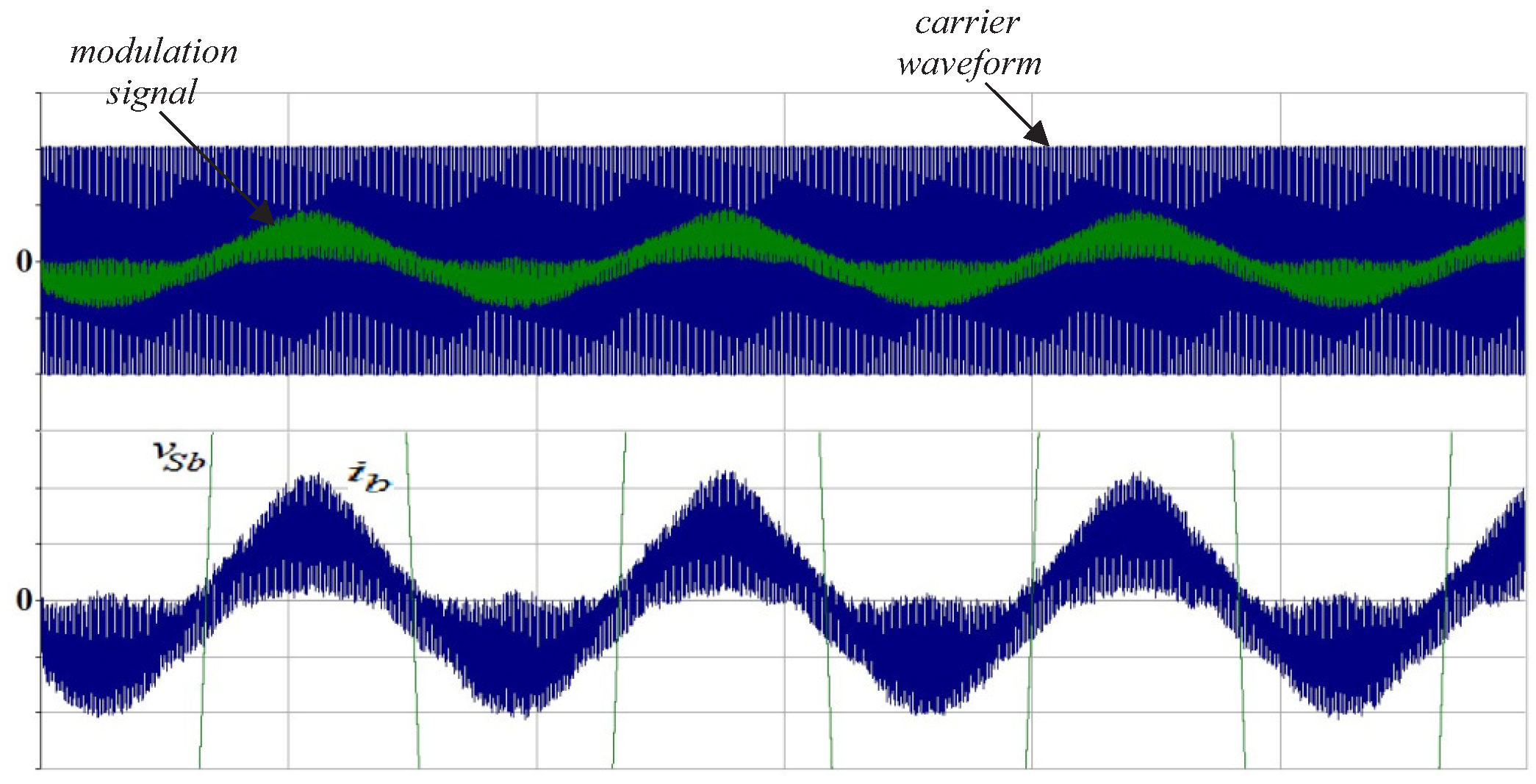

- Carrier generation uses a triangular waveshape, (Figure 1d), instead of a sawtooth carrier in the hardware OCC.

- (iv)

- Fixed amplitude carrier due of a software DSP limitation.

- (v)

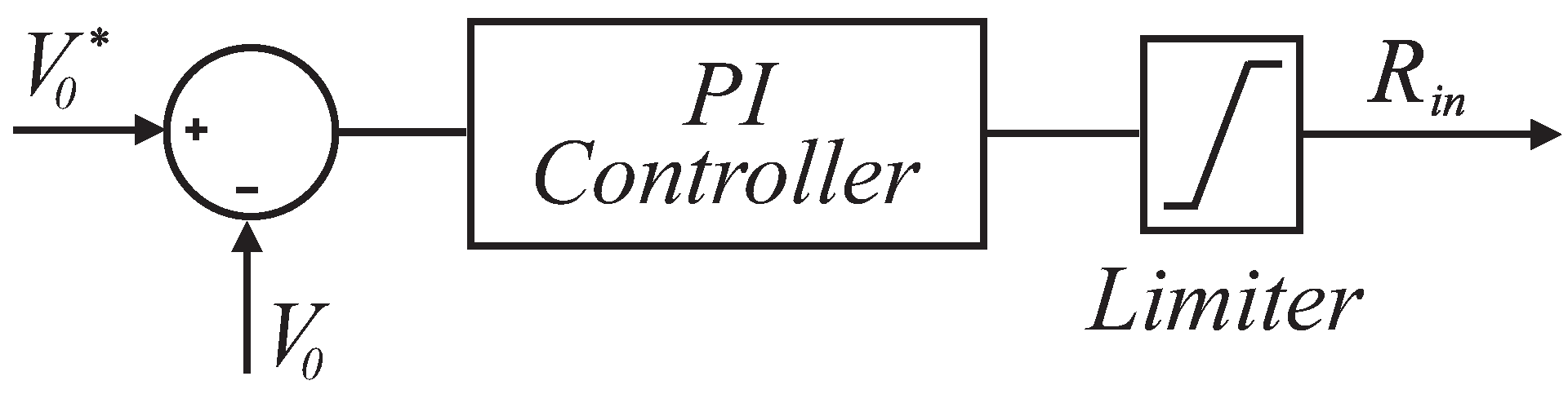

- Closed-loop emulated resistance-control, guaranteeing UPF by feedback.

- (vi)

- Use of limiters at resistance control output.

Analysis of Voltage

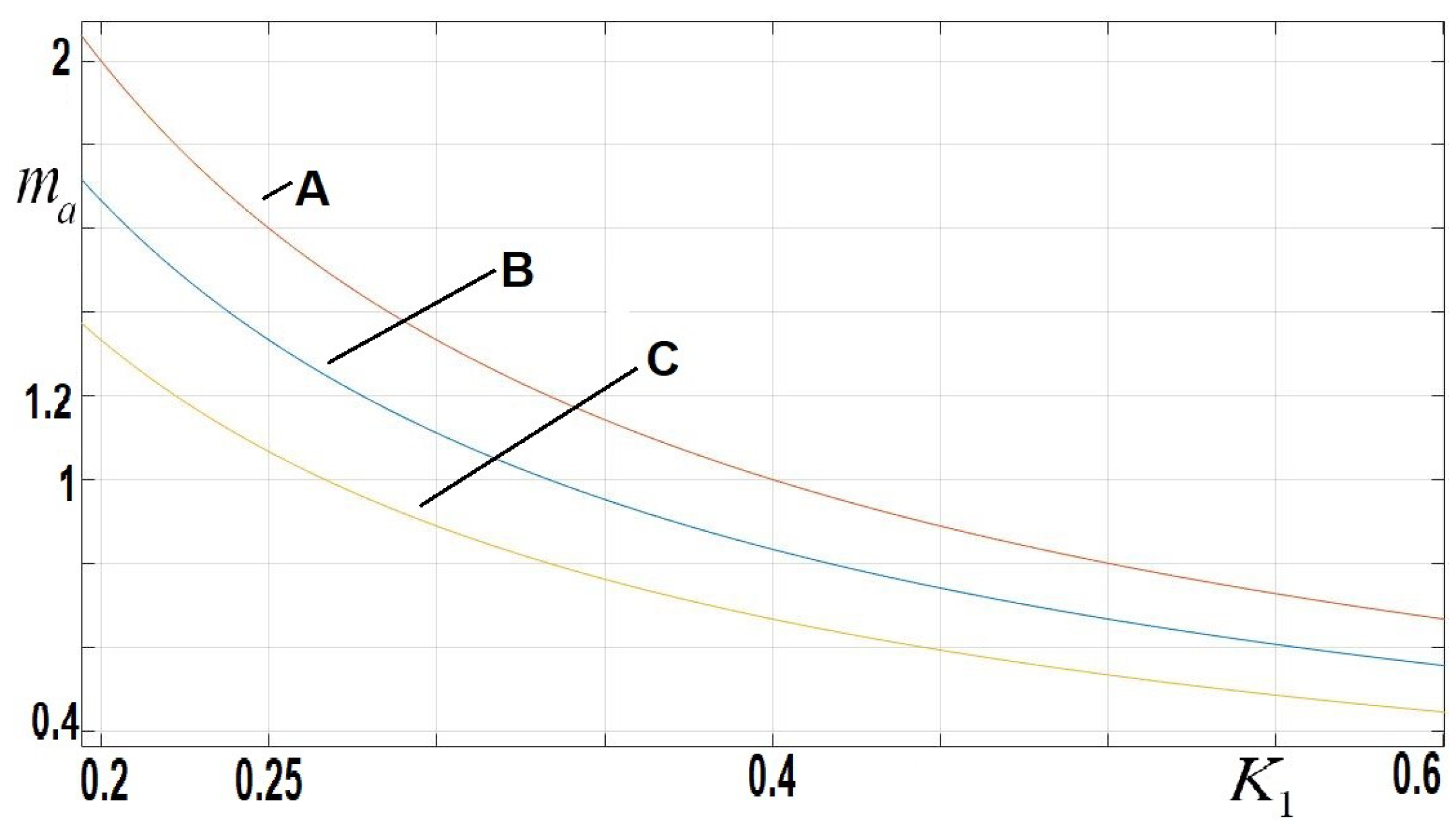

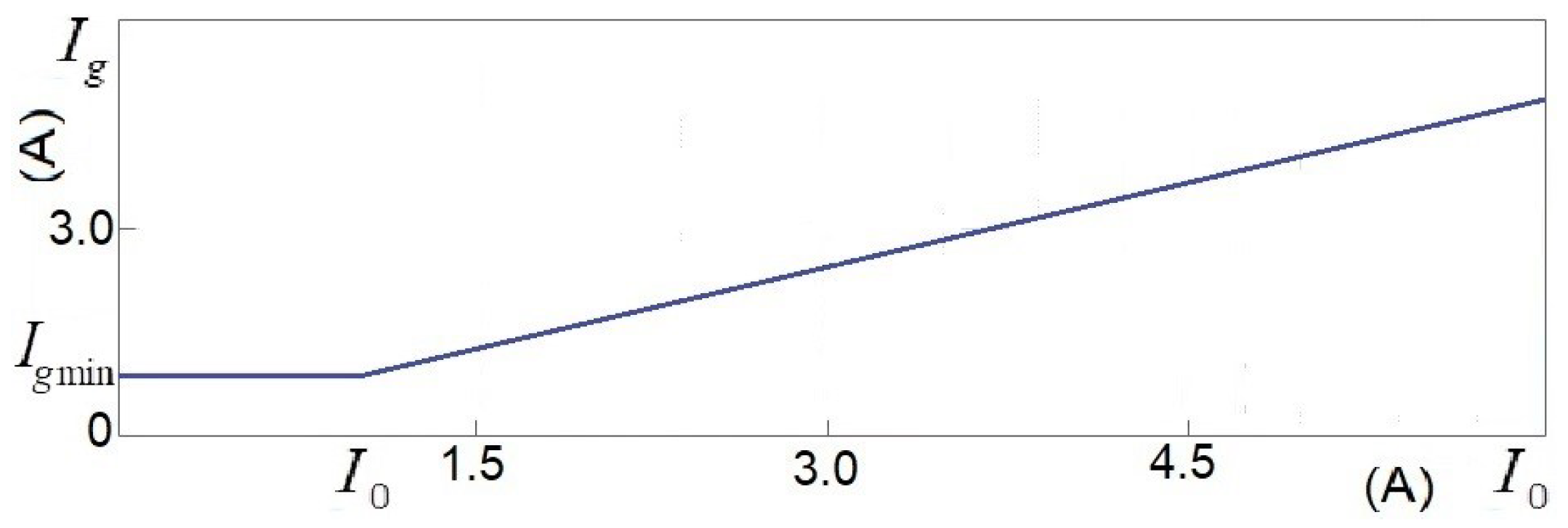

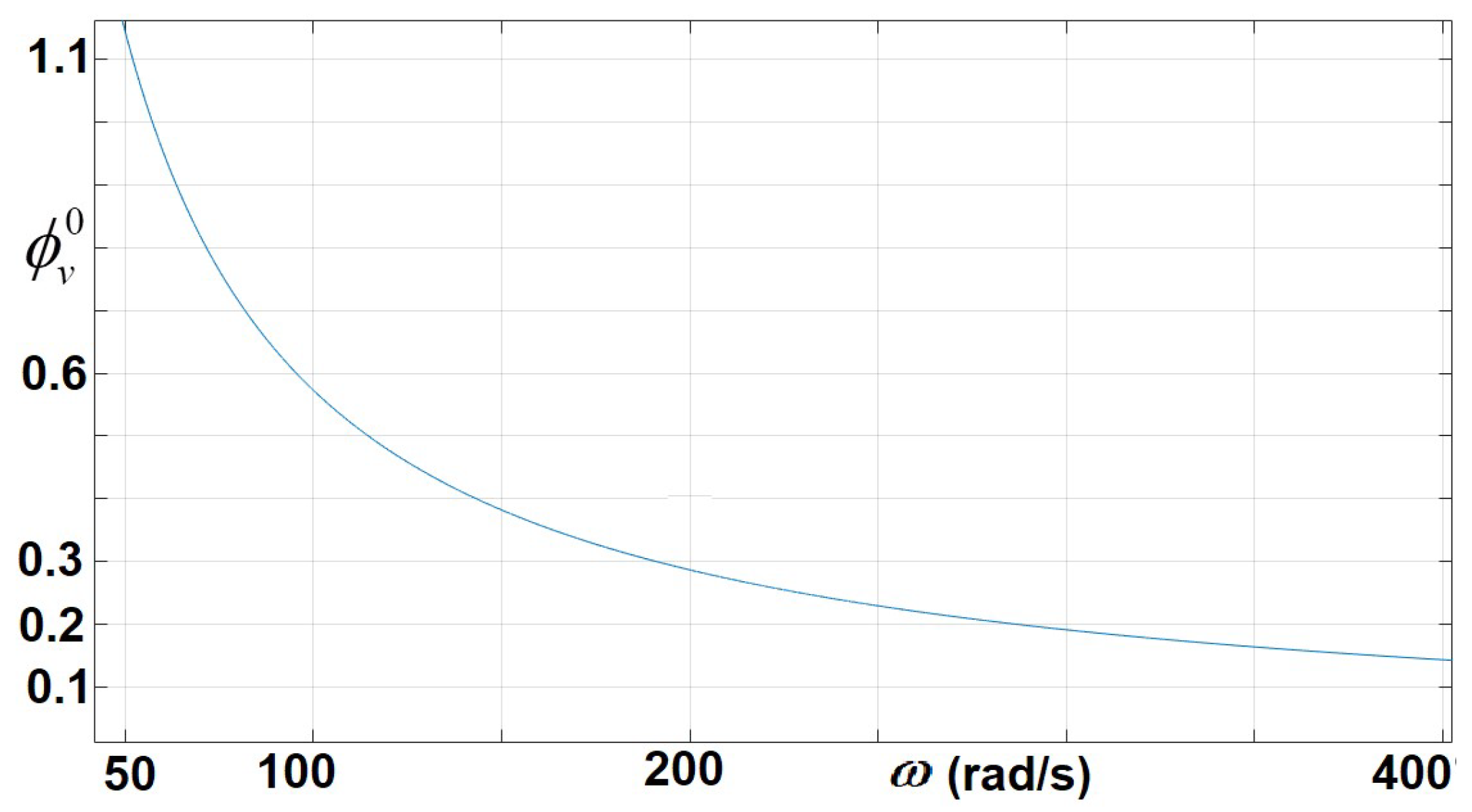

3. Occ Stability Analysis

3.1. Hardware-OCC Theoretical Background

3.2. Hardware-OCC Issues

3.3. Software-OCC Solutions

4. DSP Implementation

Cost-Effectiveness Software-OCC Discussion

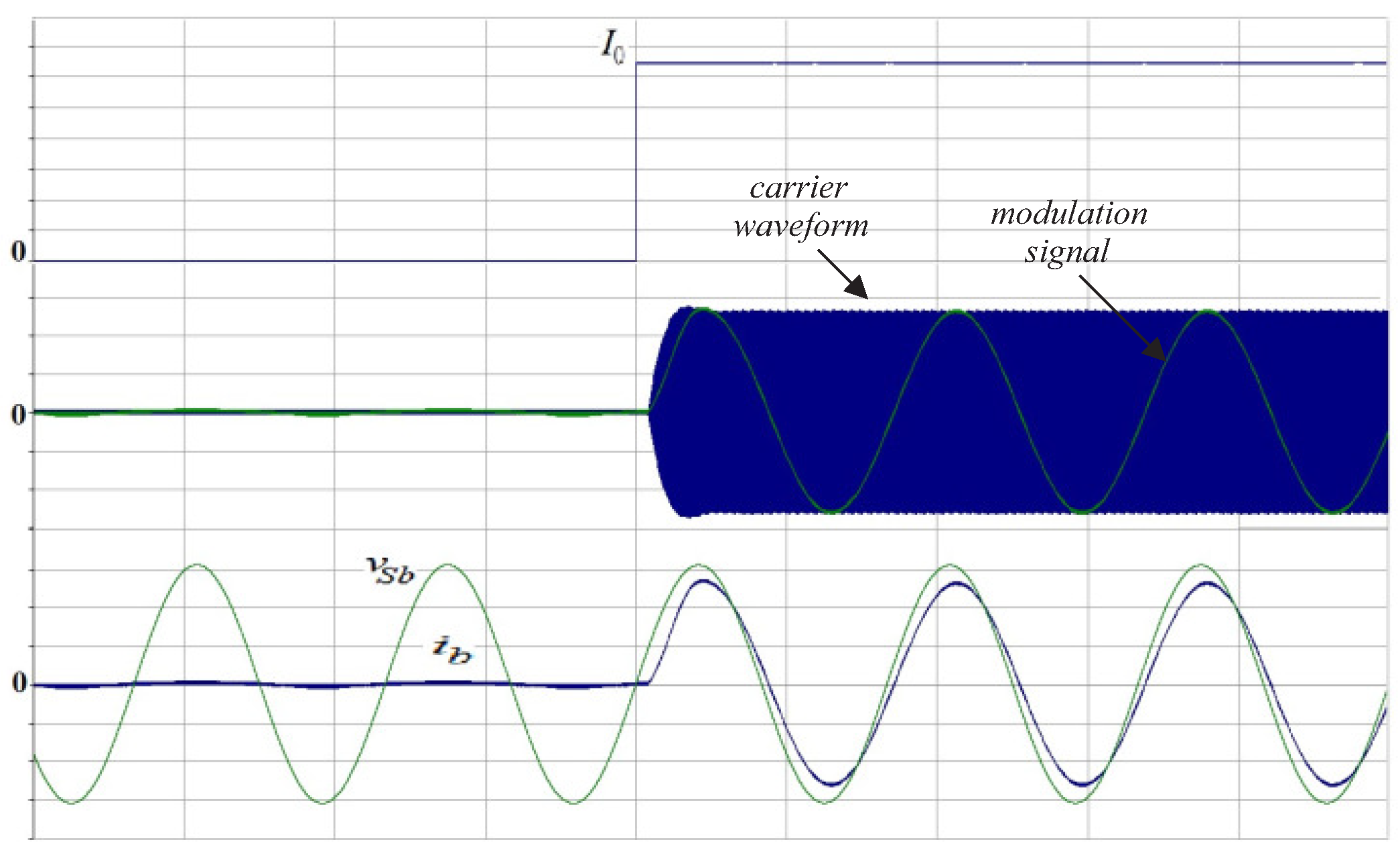

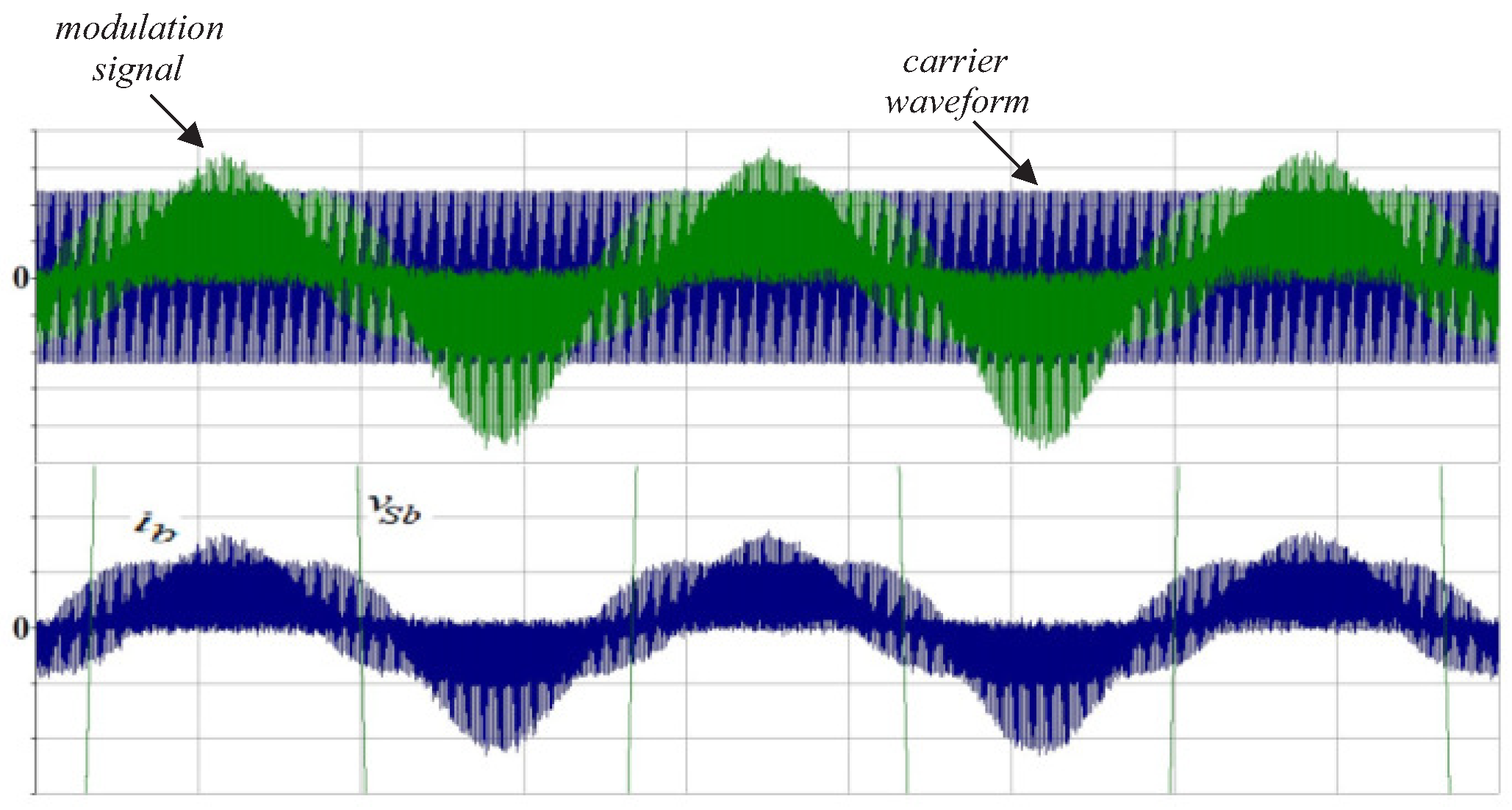

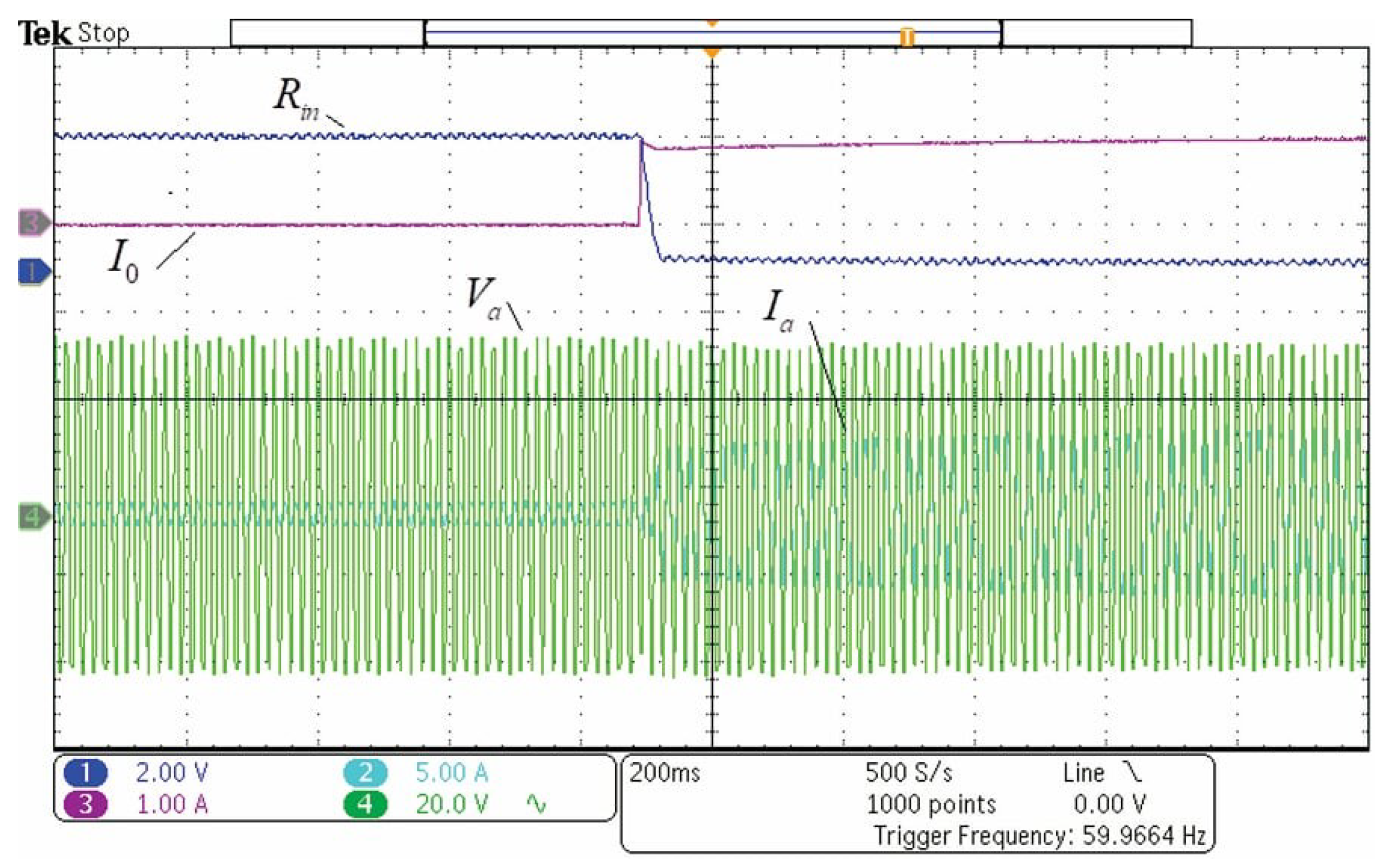

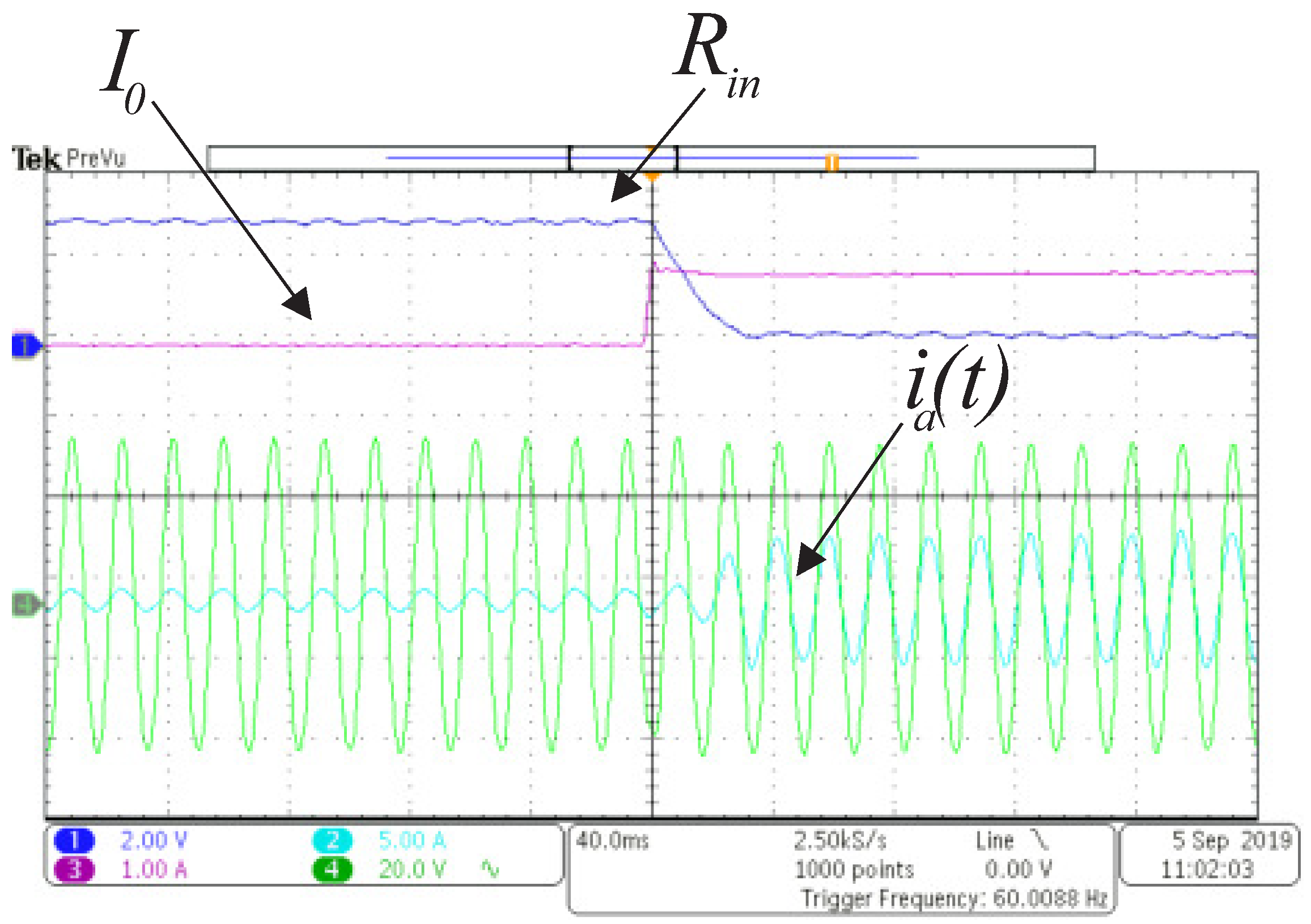

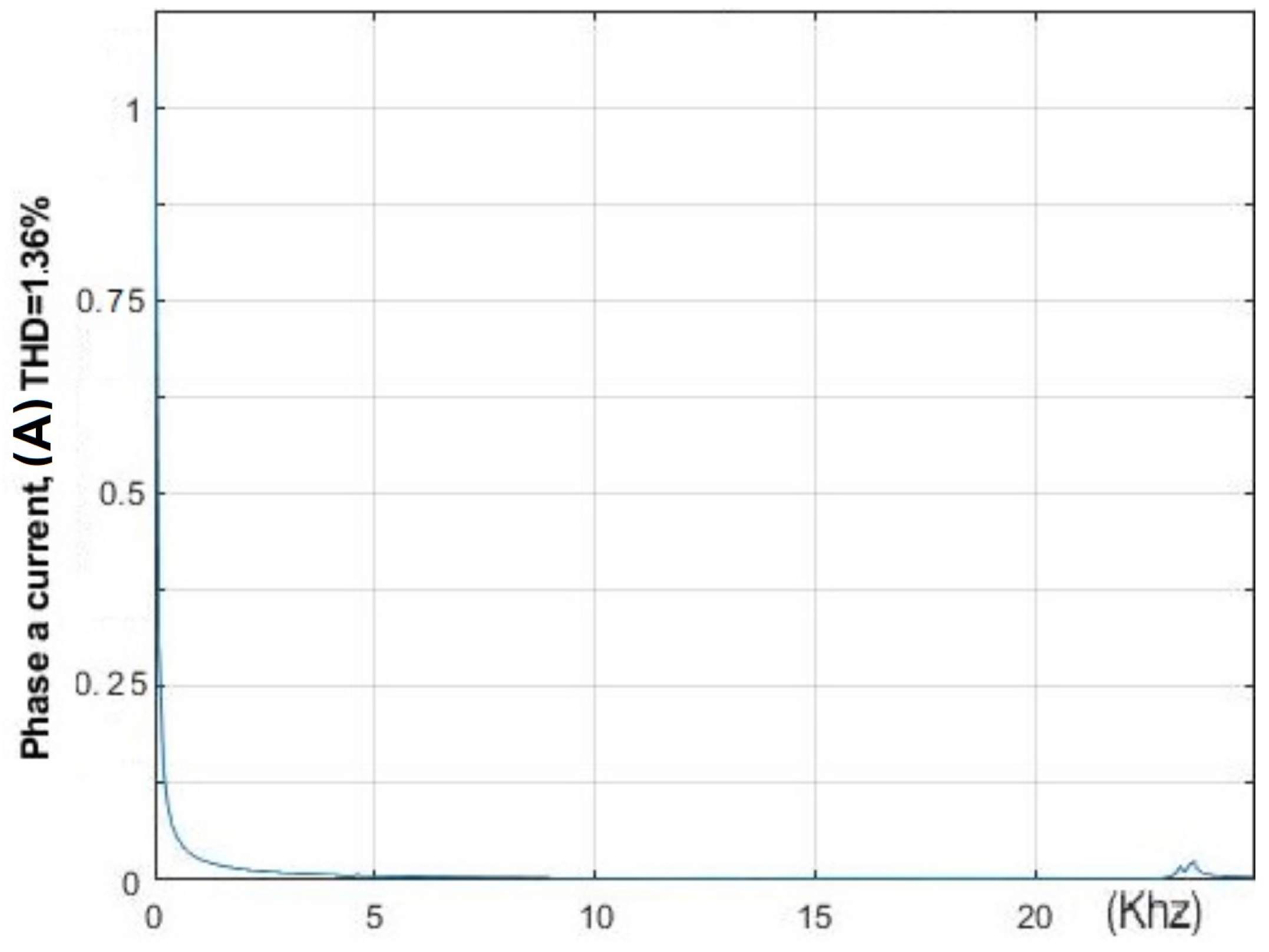

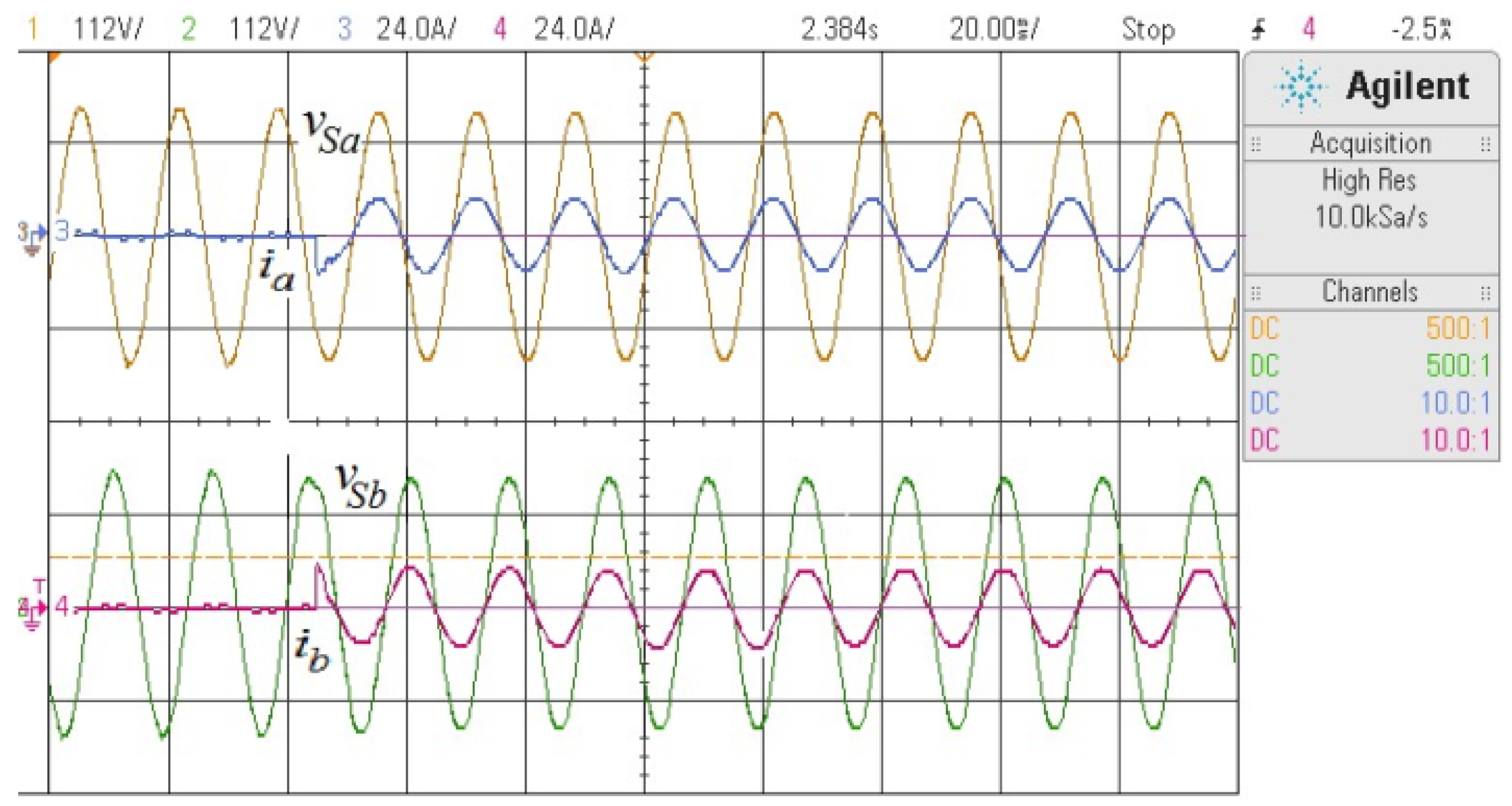

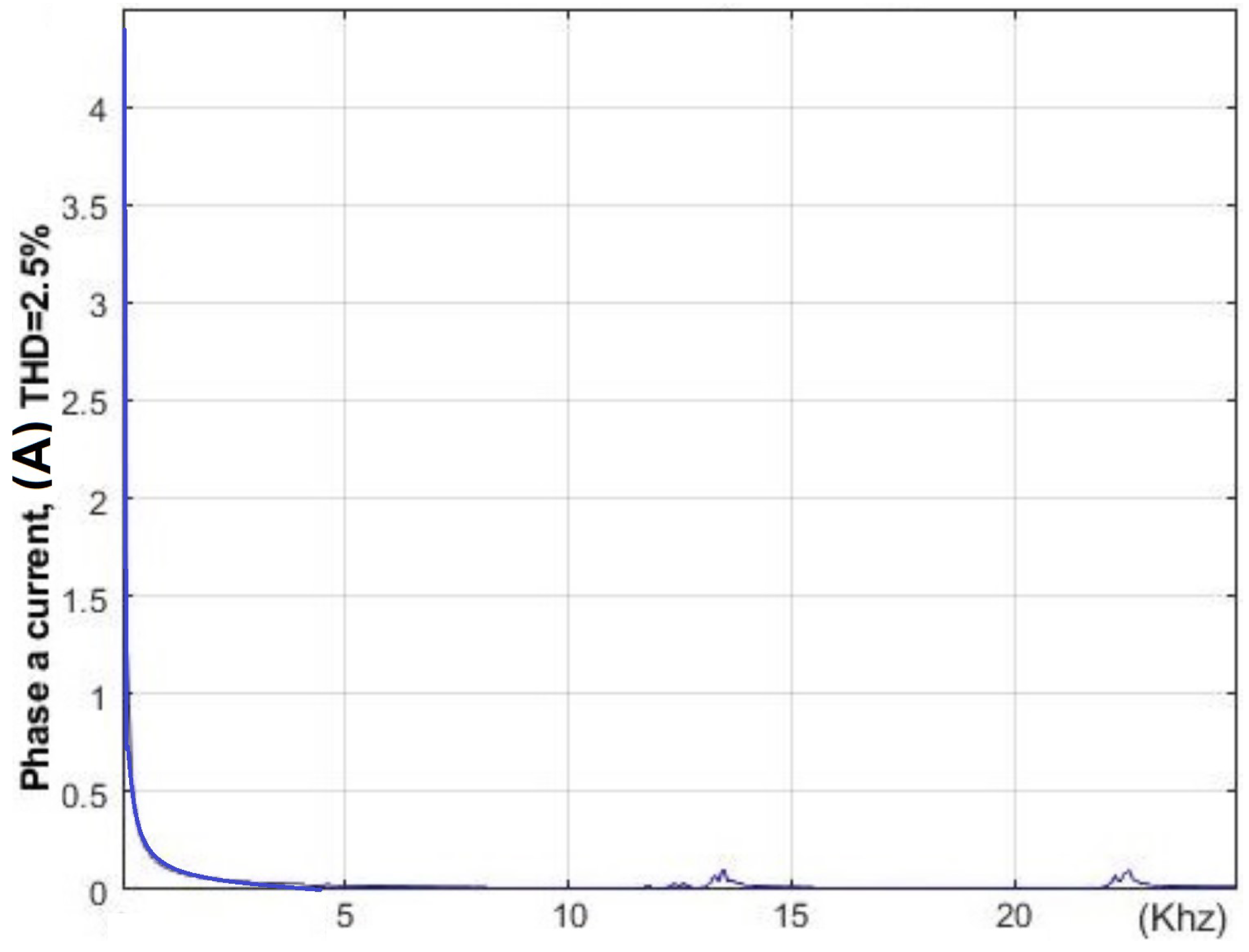

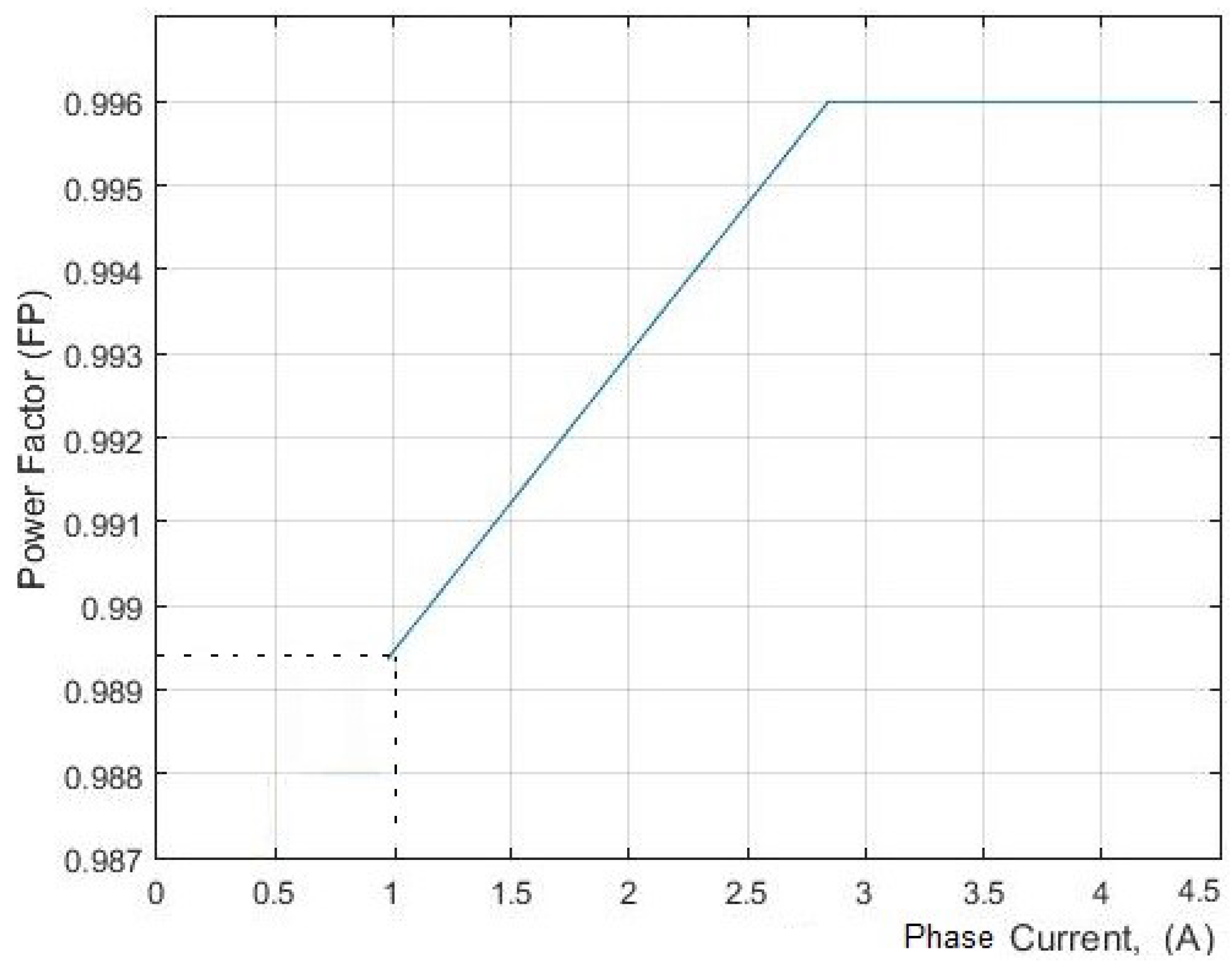

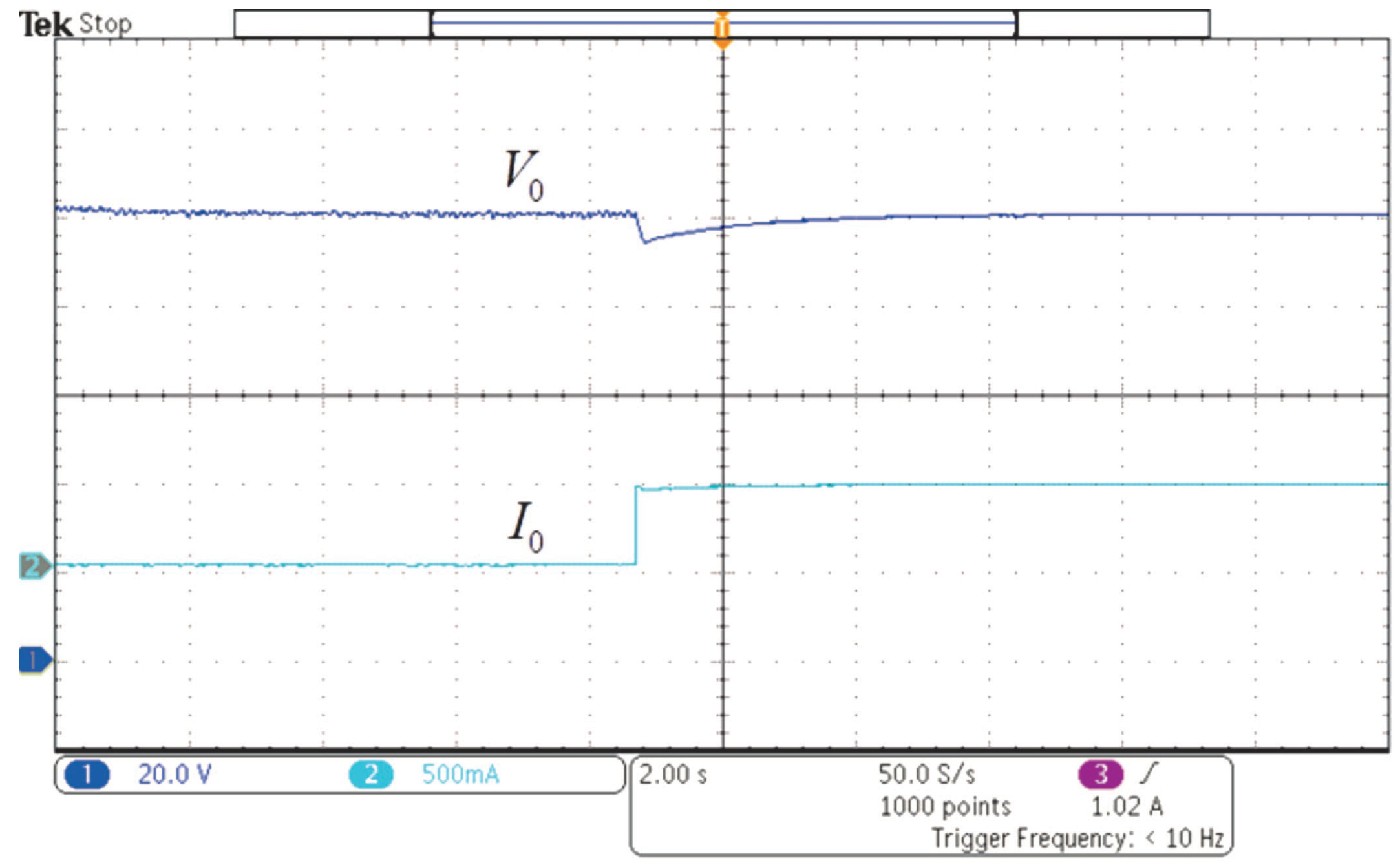

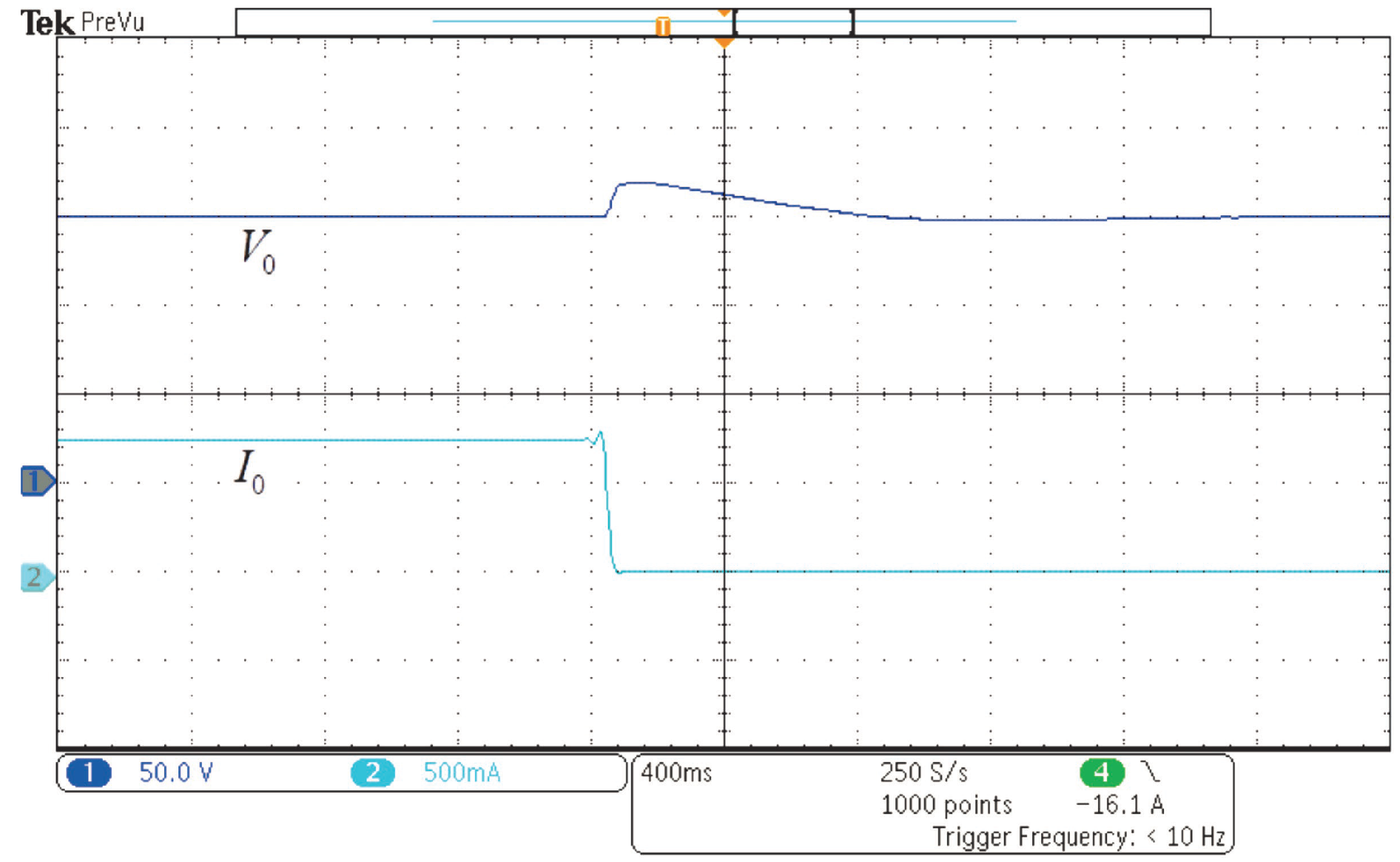

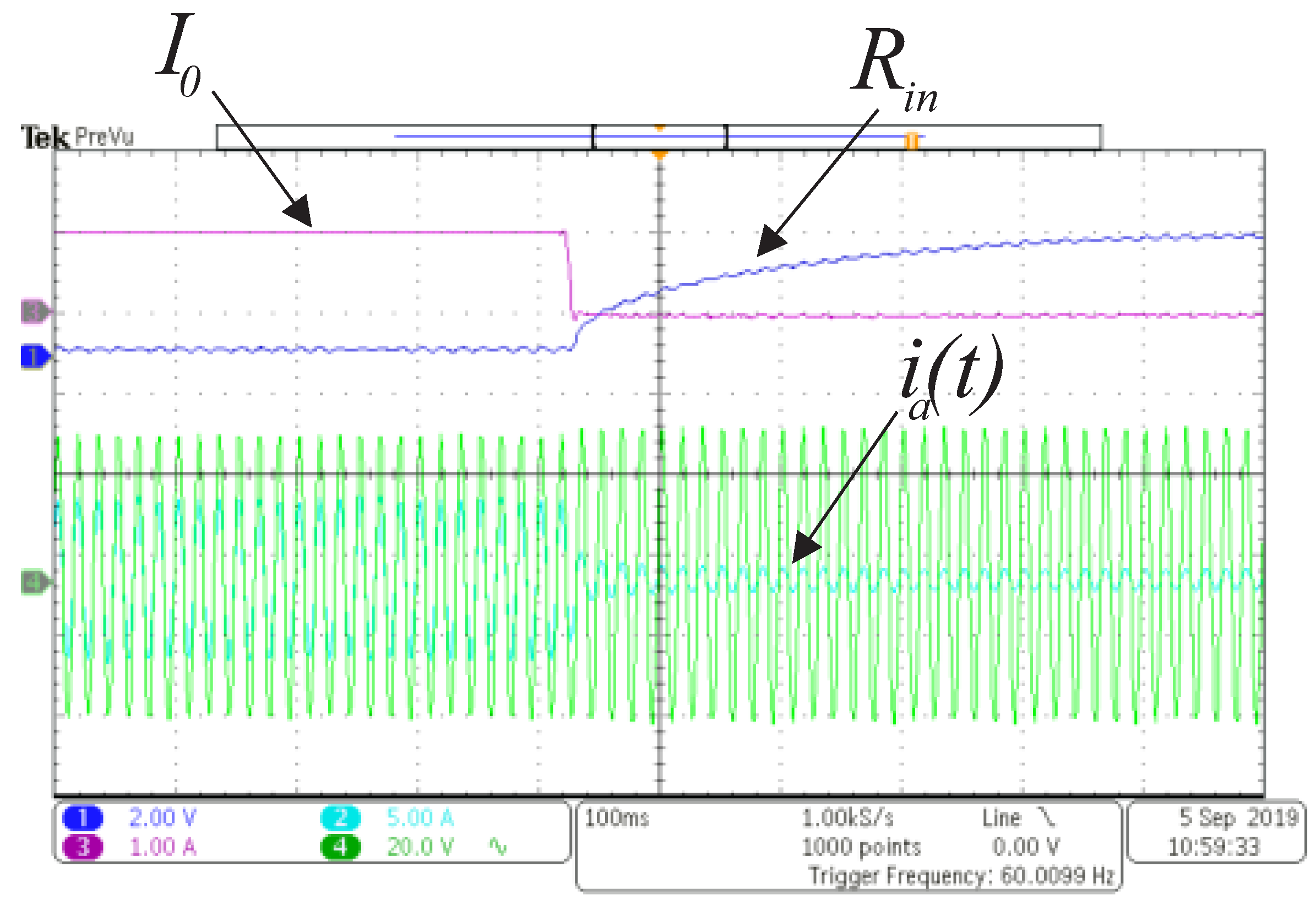

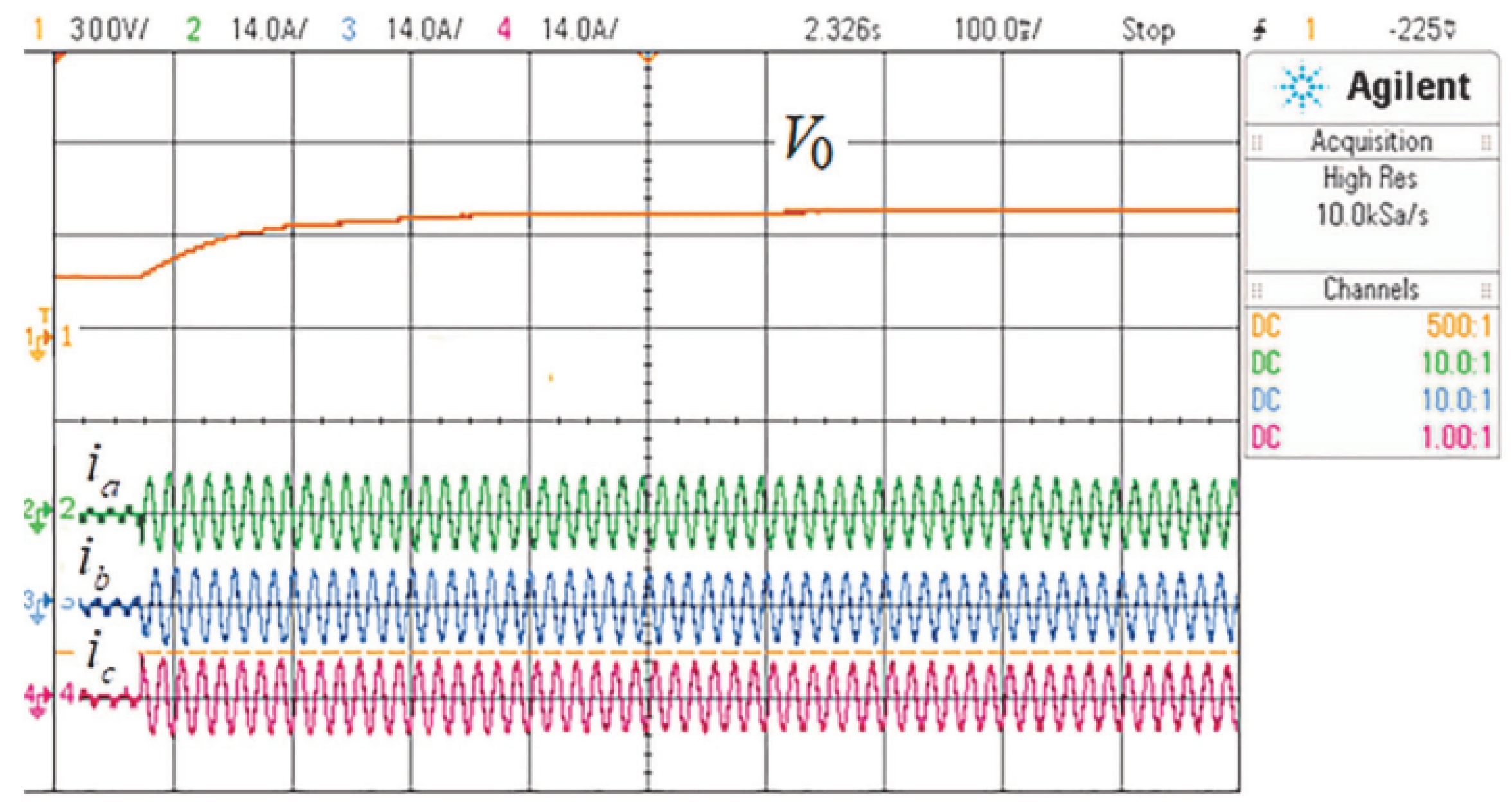

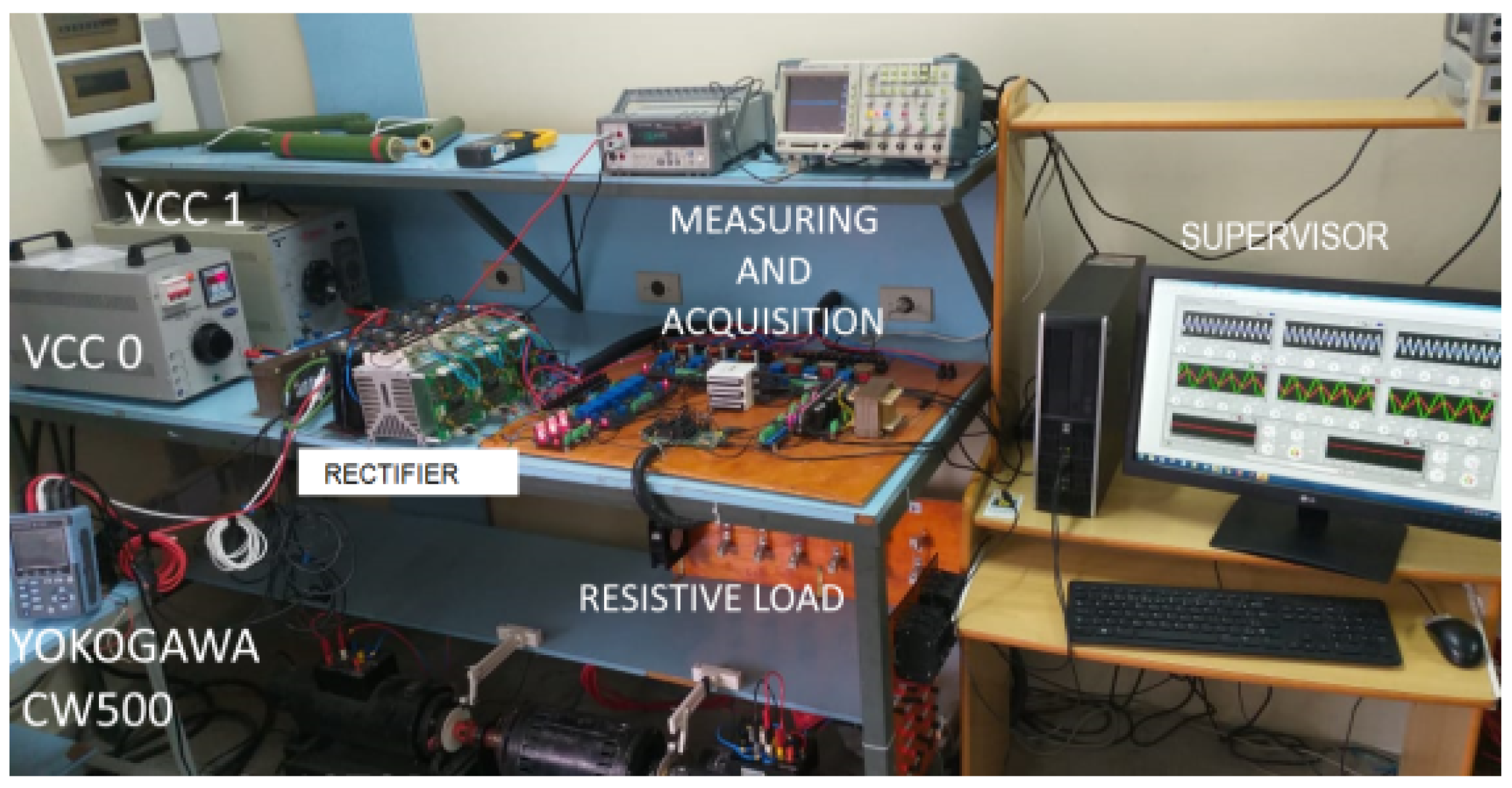

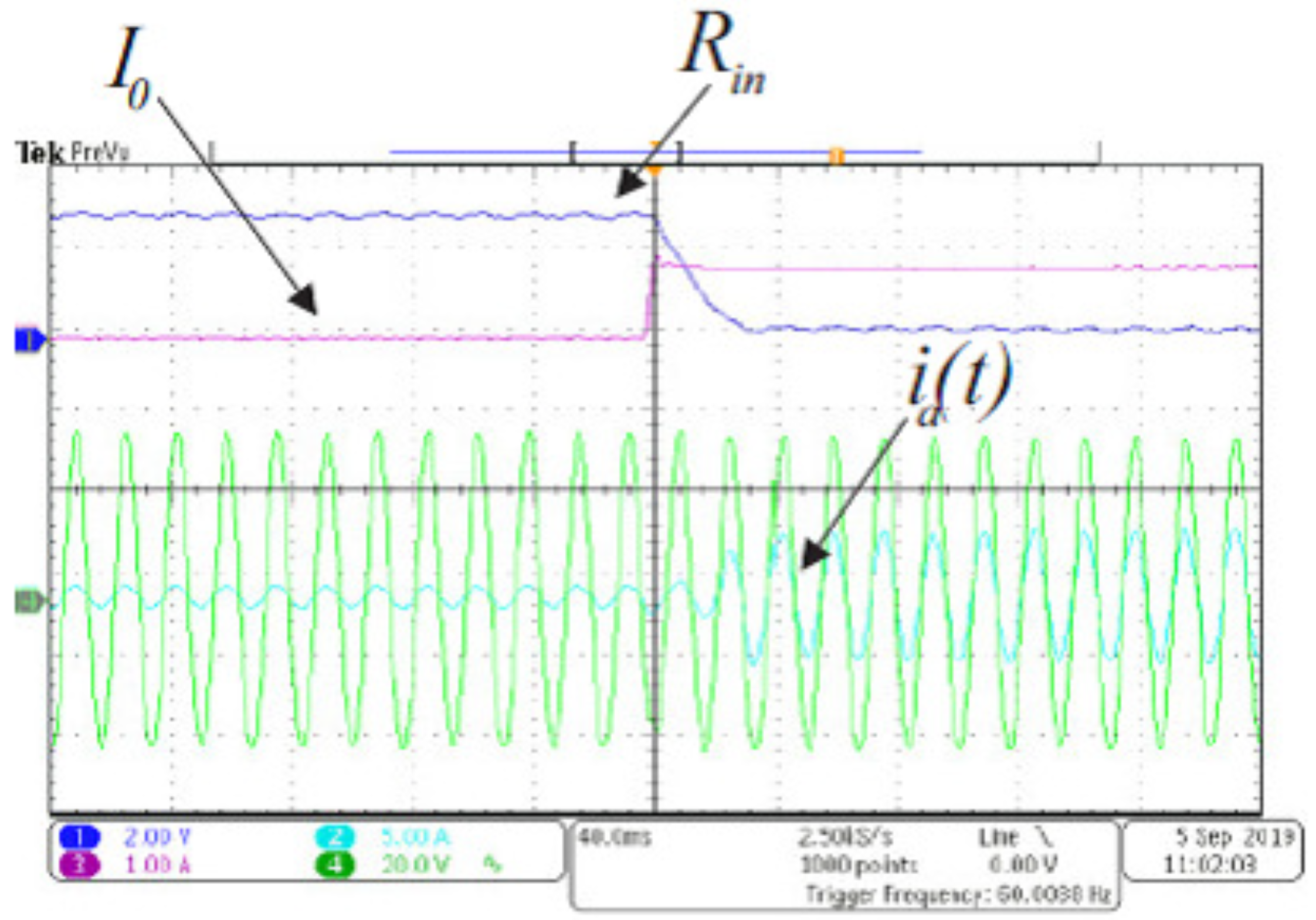

5. Simulation and Experimental Results

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| DSP | Digital Signal Processor |

| OCC | One Cycle Control |

| CMV | Common-mode Voltage |

| LLC | lead-lag compensator |

| UPF | unity power factor |

| APF | active power filters |

| FACTs | flexible ac transmission systems |

| GCI | photo-voltaic grid-connected inverters. |

References

- Smedley, K.M.; Cuk, S. One-cycle control of switching converte. In Proceedings of the 22nd Annual IEEE Power Electronics Specialists Conference (PESC ’91), Cambridge, UK, 24–27 June 1991; pp. 888–896. [Google Scholar]

- Zhao, B.; Huangfu, Y.; Abramovitz, A. Derivation of OCC Modulator for Grid-Tied Single-Stage Buck-Boost Inverter Operating in the Discontinuous Conduction Mode. Energies 2020, 13, 3168. [Google Scholar] [CrossRef]

- Tian, X.; Ma, Y.; Yu, J.; Wang, C.; Cheng, H. A Modified One-Cycle-Control Method for Modular Multilevel Converters. Energies 2019, 12, 157. [Google Scholar] [CrossRef]

- Wang, C.; Liu, J.; Cheng, H.; Zhuang, Y.; Zhao, Z. A Modified One-Cycle Control for Vienna Rectifiers with Functionality of Input Power Factor Regulation and Input Current Distortion Mitigation. Energies 2019, 12, 3375. [Google Scholar] [CrossRef]

- Yang, B.; Liu, K.; Zhang, S.; Zhao, J. Design and Implementation of Novel Multi-Converter-Based Unified Power Quality Conditioner for Low-Voltage High-Current Distribution System. Energies 2018, 11, 3150. [Google Scholar] [CrossRef]

- Phannil, N.; Jettanasen, C.; Ngaopitakkul, A. Harmonics and Reduction of Energy Consumption in Lighting Systems by Using LED Lamps. Energies 2018, 11, 3169. [Google Scholar] [CrossRef]

- Cai, K.; Alalibo, B.P.; Cao, W.; Liu, Z.; Wang, Z.; Li, G. Hybrid Approach for Detecting and Classifying Power Quality Disturbances Based on the Variational Mode Decomposition and Deep Stochastic Configuration Network. Energies 2018, 11, 3040. [Google Scholar] [CrossRef]

- IEEE Standard 519-1992. Recommended Practice and Requirements for Harmonic Control in Electric Power Systems; IEEE: Piscataway, NJ, USA, 1992. [Google Scholar]

- Erickson, R.W. Fundamentals of Power Electronics; Kluwer Academic Publishers: Dordrecht, The Netherlands, 2000. [Google Scholar]

- Rodriguez, J.R.; Dixon, J.W.; Espinoza, J.R.; Pontt, J.; Lezana, P. PWM regenerative rectifiers: State of the art. IEEE Trans. Ind. Electron. 2005, 52, 5–22. [Google Scholar] [CrossRef]

- Hartman, M.; Ertl, H.; Kolar, J.W. Current control of three phase rectifier system using three independent current controllers. IEEE Trans. Power Electron. 2013, 28, 2088–3000. [Google Scholar] [CrossRef]

- Chung, S.K. Phase-locked loop for grid-connected three-phase power conversion systems. IEE Proc.-Electr. Power Appl. 2000, 147, 213–219. [Google Scholar] [CrossRef]

- Kazmierkowski, M.; Malesani, L. Current control techniques for three-phase voltage-source PWM converters: A survey. IEEE Trans. Ind. Electron. 1998, 45, 691–703. [Google Scholar] [CrossRef]

- Monfared, M.; Rastegar, H.; Kojabadi, H.M. High performance direct instantaneous power control of PWM rectifiers. Energy Convers. Manag. 2010, 51, 947–954. [Google Scholar] [CrossRef]

- Bouafia, A.; Gaubert, J.; Krim, F. Design and implementation of predictive current control of three-phase PWM rectifier using space-vector modulation (SVM). Energy Convers. Manag. 2010, 51, 2473–2481. [Google Scholar] [CrossRef]

- Malesani, L.; Mattavelli, P.; Buso, S. Robust dead-beat current control for PWM rectifier and active filters. IEEE Trans. Ind. Appl. 1999, 35, 613–620. [Google Scholar] [CrossRef]

- Dixon, J.; Contardo, J.; Moran, L. A Fuzzy-Controlled Active Front-End Rectifier with Current Harmonic Filtering Characteristics and Minimum Sensing Variables. IEEE Trans. Power Electron. 1999, 14, 724–729. [Google Scholar] [CrossRef]

- Coteli, R.; Acikgoz, H.; Ucar, F.; Dandil, B. Design and implementation of Type-2 fuzzy neural system controller for PWM rectifiers. Int. J. Hydrogen Energy 2017, 42, 20759–20771. [Google Scholar] [CrossRef]

- Chattopadhyay, S.; Ramanarayanan, V. Digital Implementation of a Line Current Shaping Algorithm for Three Phase High Power Factor Boost Rectifier Without Input Voltage Sensing. IEEE Trans. Power Electron. 2004, 19, 709–711. [Google Scholar] [CrossRef]

- Maksimovic, D.; Jang, Y.; Erickson, R.W. Nonlinear-carrier control for high-power-factor boost rectifiers. IEEE Trans. Power Electron. 1996, 11, 578–584. [Google Scholar] [CrossRef]

- Qiao, C.; Smedley, K.M. Unified constant-frequency integration control of three-phase standard bridge boost rectifiers with power-factor correction. IEEE Trans. Ind. Electron. 2003, 50, 100–107. [Google Scholar] [CrossRef]

- Qiao, C.; Smedley, K.M. Three-Phase Bipolar Mode Active Power Filters. IEEE Trans. Ind. Appl. 2002, 38, 149–158. [Google Scholar] [CrossRef]

- Qiao, C.; Jin, T.; Smedley, K.M. One-cycle control of three-phase active power filter with vector operation. IEEE Trans. Ind. Electron. 2004, 51, 455–463. [Google Scholar] [CrossRef]

- Jin, T.; Li, L.; Smedley, K.M. A Universal Vector Controller for Four-Quadrant Three-Phase Power Converters. IEEE Trans. Circuits Syst. Regul. Pap. 2007, 54, 377–390. [Google Scholar] [CrossRef]

- Chen, Y.; Smedley, K.M. A cost-effective single-stage inverter with maximum power point tracking. IEEE Trans. Power Electron. 2004, 45, 1289–1294. [Google Scholar] [CrossRef]

- Chen, Y.; Smedley, K.M. Three-Phase Boost-Type Grid-Connected Inverter. IEEE Trans. Power Electron. 2008, 23, 2301–2309. [Google Scholar] [CrossRef]

- Fortunato, M.; Giustiniani, A.; Petrone, G.; Spagnuolo, G.; Vitelli, M. Maximum Power Point Tracking in a One-Cycle-Controlled Single-Stage Photovoltaic Inverter. IEEE Trans. Ind. Electron. 2008, 55, 2684–2693. [Google Scholar] [CrossRef]

- Ghodke, D.V.; Sreeraj, E.S.; Chatterjee, K.; Fernandes, B.G. One-Cycle-Controlled Bidirectional AC-to-DC Converter with Constant Power Factor. IEEE Trans. Ind. Electron. 2009, 56, 1499–1519. [Google Scholar] [CrossRef]

- Smedley, K.; Zhou, L.; Qiao, C. Unified constant-frequency integration control of active power filters-steady-state and dynamics. IEEE Trans. Power Electron. 2001, 16, 428–436. [Google Scholar] [CrossRef]

- Lock, A.S.; Da Silva, E.R.C.; Elbuluk, M.E.; Fernandes, D.A. A hybrid current control for a controlled rectifier. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Atlanta, GA, USA, 12–16 September 2010; pp. 920–926. [Google Scholar]

- Lock, A.S.; Da Silva, E.R.C.; Elbuluk, M.E.; Fernandes, D.A. Torque control of induction motor drives based on One-Cycle Control method. In Proceedings of the 2012 IEEE Industry Applications Society Annual Meeting, Las Vegas, NV, USA, 7–11 October 2012; pp. 1–8. [Google Scholar]

- Lock, A.S.; Da Silva, E.R.C.; Elbuluk, M.E.; Fernandes, D.A. An -OCC strategy for common-mode current rejection. IEEE Trans. Ind. Appl. 2016, 52, 4935–4945. [Google Scholar] [CrossRef]

- Bento, A.M.; Lock, A.S.; Da Silva, E.R.C.; Fernandes, D.A. Hybrid one-cycle control technique for three-phase power factor Control. IET Power Electron. 2018, 11, 484–490. [Google Scholar] [CrossRef]

- Primavera, S.; Rella, G.; Maddaleno, F.; Smedley, K.; Abramovitz, A. One-cycle controlled three-phase electronic load. IET Power Electron. 2012, 5, 827–832. [Google Scholar] [CrossRef]

- Niasar, A.H.; Moghbeli, H.; Kashani, E.B. A Low-Cost Sensorless BLDC Motor Drive using One-Cycle Current Control Strategy. In Proceedings of the 2014 22nd Iranian Conference on Electrical Engineering (ICEE), Tehran, Iran, 20–22 May 2014; pp. 659–664. [Google Scholar]

- Vamanan, N.; John, V. Dual comparison One Cycle Control for single phase AC to DC converters. IEEE Trans. Ind. Appl. 2016, 52, 3267–3278. [Google Scholar] [CrossRef]

- Ghodke, D.V.; Chatterjee, K.; Fernandes, B.G. Modified One-Cycle Controlled Bidirectional High-Power-Factor AC-to-DC Converter. IEEE Trans. Ind. Electron. 2008, 55, 2459–2472. [Google Scholar] [CrossRef]

- Chatterjee, K.; Ghodke, D.V.; Chandra, A.; Al-Haddad, K. Modified one cycle controlled load compensator. IET Power Electron. 2011, 4, 481–490. [Google Scholar] [CrossRef]

- Chen, Y.; Smedley, K.M. Parallel operation of one-cycle controlled three-phase PFC rectifiers. IEEE Trans. Ind. Electron. 2007, 54, 3217–3224. [Google Scholar] [CrossRef]

- Chen, G.; Smedley, K.M. Steady-State and Dynamic Study of One-Cycle-Controlled Three-Phase Power-Factor Correction. IEEE Trans. Ind. Electron. 2005, 52, 355–362. [Google Scholar] [CrossRef]

- Jin, T.; Li, L.; Smedley, K. A universal vector controller for three-phase PFC, APF, STATCOM, and grid-connected inverter. In Proceedings of the Nineteenth Annual IEEE Applied Power Electronics Conference and Exposition (APEC ’04), Anaheim, CA, USA, 22–26 February 2004; pp. 594–600. [Google Scholar]

- Ghodke, A.A.; Chatterjee, K. One-cycle-controlled bidirectional three-phase unity power factor ac/dc converter without having voltage sensors. IET Power Electron. 2005, 5, 1944–1955. [Google Scholar] [CrossRef]

- Texas Instruments (2012) SPRS439M: TMS320F28335 Data Manual. Available online: http://www.ti.com (accessed on 29 July 2020).

- Hava, A.M.; Un, E. Performance Analysis of Reduced Common-Mode Voltage PWM Methods and Comparison with Standard PWM Methods for Three-Phase Voltage-Source Inverters. IEEE Trans. Power Electron. 2009, 45, 782–793. [Google Scholar] [CrossRef]

- Lai, R.; Wang, F.; Burgos, R.; Boroyevich, D.; Jiang, D.; Zhang, D. Average Modeling and Control Design for VIENNA-Type Rectifers Considering the DC-Link Voltage Balance. IEEE Trans. Power Electron. 2009, 24, 2509–2521. [Google Scholar]

- Lee, D.; Lim, D. AC Voltage and Current Sensorless Control of Three-Phase PWM Rectifiers. IEEE Trans. Power Electron. 2002, 17, 883–890. [Google Scholar]

- Holmes, D.G.; Lipo, T.A. Pulse Width Modulation for Power Converters; Wiley: New York, NY, USA, 2003. [Google Scholar]

- Singer, S.; Smilovitz, D. Transmission line-based loss free resistor. IEEE Trans. Circuits Syst. Fundam. Theory Appl. 1994, 41, 120–126. [Google Scholar] [CrossRef]

- Blasko, V. A hybrid PWM strategy combining modified space vector and triangle comparison methods. In Proceedings of the PESC Record. 27th Annual IEEE Power Electronics Specialists Conference, Baveno, Italy, 23–27 June 1996; pp. 872–1878. [Google Scholar]

- Hava, A.M.; Kerkman, R.J.; Lipo, T.A. Simple analytical and graphical methods for carrier-based PWM-VSI drives. IEEE Trans. Power Electron. 1999, 14, 49–61. [Google Scholar] [CrossRef]

- Mohan, N.; Undeland, T.M.; Robbins, W.P. Power Electronics Converters, Applications, and Design, 3rd ed.; John Wiley & Sons: Hoboken, NJ, USA, 2002. [Google Scholar]

- Ben-Yaakov, S.; Zeltser, I. The dynamics of a PWM boost converter with resistive input. IEEE Trans. Ind. Appl. 1999, 46, 613–619. [Google Scholar] [CrossRef]

- LEM, Current Sensor LA25-NP. Available online: https://uk.rs-online.com/web/p/current-transducers/0286311/ (accessed on 29 July 2020).

- Sun, J. Pulse-width Modulation in Dynamics and Control of Switched Electronic Systems; Springer: London, UK, 2012. [Google Scholar]

- Texas Instruments, Inc. Using PWM Output as a Digital-to-Analog Converter on a TMS320F28X, Dallas, TX, USA, Appl. Rep. SPAA88A. 2008. Available online: http://www.ti.com (accessed on 29 July 2020).

- Qasim, M.; Kanjiya, P.; Khadkikar, V. Artificial-neural-network-based phase-locking scheme for active power filters. IEEE Trans. Ind. Electron. 2014, 61, 3857–3866. [Google Scholar] [CrossRef]

| Carrier Amplitude (A) | (kHz) |

|---|---|

| 3750 | 20 |

| 5000 | 15 |

| 7500 | 10 |

| Parameter | R () | (r/s) | L (mH) | F) | (F) | (V) | (ms) | (ms) | (kHz) |

|---|---|---|---|---|---|---|---|---|---|

| Simulation | 1 | 377 | 1 | 670 | 670 | 110 | 1 | 0.15 | 20 |

| Experimental | 1 | 377 | 1 | 2200 | 2200 | 110 | 1 | 0.15 | 25 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Teixeira, R.D.A.; Silva, W.L.A.; Pessoa, G.A.P.D.C.A.; Neto, J.T.C.; Villarreal, E.R.L.; Salazar, A.O.; Lock, A.S. One Cycle Control of a PWM Rectifier a New Approach. Energies 2020, 13, 5523. https://doi.org/10.3390/en13205523

Teixeira RDA, Silva WLA, Pessoa GAPDCA, Neto JTC, Villarreal ERL, Salazar AO, Lock AS. One Cycle Control of a PWM Rectifier a New Approach. Energies. 2020; 13(20):5523. https://doi.org/10.3390/en13205523

Chicago/Turabian StyleTeixeira, Rodrigo De A., Werbet L. A. Silva, Guilherme A. P. De C. A. Pessoa, Joao T. Carvalho Neto, Elmer R. L. Villarreal, Andrés O. Salazar, and Alberto S. Lock. 2020. "One Cycle Control of a PWM Rectifier a New Approach" Energies 13, no. 20: 5523. https://doi.org/10.3390/en13205523

APA StyleTeixeira, R. D. A., Silva, W. L. A., Pessoa, G. A. P. D. C. A., Neto, J. T. C., Villarreal, E. R. L., Salazar, A. O., & Lock, A. S. (2020). One Cycle Control of a PWM Rectifier a New Approach. Energies, 13(20), 5523. https://doi.org/10.3390/en13205523